1.本技术涉及半导体电路设计领域,特别涉及一种存储器。

背景技术:

2.动态随机存储器(dynamic random access memory,dram)由于其存储密度高、传输速度快等特点,广泛应用于现代电子系统中。随着半导体技术的发展,dram技术越来越先进,存储单元的集成度越来越高;同时,各种不同的应用对dram的性能、功耗和可靠性等也都要求越来越高,例如ddr5和lpddr5等。

3.而现有具备检错纠错功能(error correcting code,ecc)的存储器数据传输线路在功耗、可靠性等方面仍有改进空间,亟需设计一种能够降低数据传输功耗、提高存储可靠性的ecc存储器,进一步提高现有ecc存储器的综合性能,以面对各种不同应用场景的需求。

技术实现要素:

4.本技术实施例提供一种存储器,以降低数据传输线路的低功耗和提高数据存储的可靠性等。

5.为解决上述技术问题,本技术实施例提供了一种存储器,包括数据存储区和校验码存储区,包括:编码模块,连接外部数据线,用于根据外部数据线中传输的原始数据生成ecc校验码,ecc校验码用于对原始数据在存储过程中发生的错误进行纠正;判断模块,与外部数据线、第一全局数据线连接,用于输出表征原始数据与第一全局数据线当前传输的数据的差异位数是否超过第一预设值的第一控制信号;统计模块,与外部数据线连接,用于输出第二控制信号,第二控制信号用于表征,原始数据中高电平数据所占位数是否超过第二预设值;数据缓冲模块,与编码模块和判断模块连接,用于根据第一控制信号,将原始数据传输至第一全局数据线或将原始数据进行翻转后传输至第一全局数据线;数据缓冲模块还被配置为将ecc校验码传输至第二全局数据线;第一写入模块,连接在第一本地数据线和第一全局数据线之间,控制第一全局数据线中的数据传输至第一本地数据线,且基于第三控制信号,判断第一全局数据线中的数据传输至第一本地数据线的过程中是否进行数据翻转,其中,第三控制信号用于表征第一控制信号的值和第二控制信号的值是否相同;第二写入模块,连接在第二本地数据线和第二全局数据线之间,用于将第二全局数据线的数据传输至第二本地数据线;其中,第一写入模块的驱动能力小于第二写入模块的驱动能力;其中,第一全局数据线、第一本地数据线、第一写入模块与数据存储区对应,第二全局数据线、第二本地数据线、第二写入模块与校验码存储区对应。

6.与相关技术相比,通过对比原始数据和第一全局数据线中的数据差异,获取第一控制信号,判断是否进行第一次数据翻转,以降低在数据传输过程中,传输数据线翻转,节省数据传输的功耗;通过对比原始数据中低电平数据和高电平数据的数量,获取第二控制信号,通过第一控制信号和第二控制信号获取第三控制信号,判断第一全局数据线传输至第一本地数据线是否需要进行第二次数据翻转,以保证数据存储和读出的可靠性,并存入

数据存储区;通过获取第二控制信号,判断在读出时是否需要第三次翻转,以保证读出的数据为原始写入存储器的数据;而ecc校验码通过第二全局数据线,以及第二本地数据线直接存进校验码存储区,且通过设置与校验码存储区对应的第二写入模块的驱动能力比与数据存储区对应的第一写入模块的驱动能力,来提高ecc校验码数据的写入速度,进而可以提高整体的读写速度。

7.另外,第二控制信号作为标记位数据存入校验码存储区中,以在读出数据的过程中,将第二控制信号读出。

8.另外,存储器,还包括:检错模块,用于根据ecc校验码判断原始数据在存储期间是否发生错误,和/或对发生错误的原始数据进行纠错;读出模块,用于根据读出的第二控制信号,控制第一本地数据线的原始数据向后传输时是否需要翻转;若高电平数据所占位数超过第二预设值,则读出模块被配置为将原始数据翻转后最终传输至检错模块;若高电平数据所占位数不超过第二预设值,则读出模块被配置为将原始数据最终传输至检错模块。

9.另外,存储器,还包括:第一感测放大器,用于在读操作时对数据存储区所存储的原始数据进行读取,并传输至第一本地数据线;第二感测放大器,用于在读操作时对校验码存储区所存储的ecc校验码、第二控制信号进行读取,并传输至第二本地数据线;其中,第一感测放大器的驱动能力小于第二感测放大器的驱动能力。由于存储在校验码存储区的ecc校验码没有经过高电平的统计,数据可能出现高电平数量高于低电平数量的情况,因此采用驱动能力更强的感测放大器去读取校验码存储区的ecc校验码,来尽量避免校验码存储区的ecc校验码在读取过程中可能发生的错误。

10.另外,判断模块包括:检测单元,连接外部数据线和第一全局数据线,并逐位检测外部数据线当前传输的原始数据与第一全局数据线当前传输的数据,若当前位原始数据与当前位第一全局数据线传输的数据不同,则生成第一子控制信号,若当前位原始数据与当前位第一全局数据线传输的数据相同,则生成第二子控制信号;获取单元,连接检测单元,用于获取第一子控制信号和第二子控制信号,若第一子控制信号个数超过第一预设值,则生成第一控制信号,第一预设值为第一子控制信号的数量与第二子控制信号的数量和的预设百分比。

11.另外,预设百分比为50%。

12.另外,第二预设值为原始数据的位数的50%。

13.另外,数据缓冲模块包括:转换模块,用于根据第一控制信号,控制原始数据传输至第一全局数据线时是否需要翻转;若差异位数超过第一预设值,则转换模块被配置为将原始数据翻转后传输至第一全局数据线;若差异位数不超过第一预设值,则转换模块被配置为将原始数据传输至第一全局数据线。

14.另外,第一写入模块包括:使能控制模块,用于接收第一控制信号和第二控制信号,并输出用于表征第一控制信号和第二控制信号是否相同的第三控制信号。

15.另外,使能控制模块还用于接收写使能信号,若写使能信号为有效电平,则输出用于表征第一控制信号和第二控制信号是否相同的第三控制信号。

16.另外,第一本地数据线包括互为差分数据传输线的第一本地数据正线和第二本地数据反线;第一全局数据线中的数据传输至第一本地数据线的过程中进行数据翻转,包括:第一写入模块被配置为将第一全局数据线中的数据翻转后传输至第一本地数据正线,和/

或第一写入模块被配置为将第一全局数据线中的数据传输至第一本地数据反线。通过设置用于传输差分数据的第一本地数据正线和第一本地数据反线,保证本地数据线和全局数据线间数据翻转的稳定性。

17.另外,第一写入模块,还包括:包括第一mos管、第二mos管和第三mos管的第一转换电路;第一mos管的栅极接收第三控制信号,源极连接第一全局数据线,漏极连接第一本地数据正线;第二mos管的栅极连接第一全局数据线,漏极连接第一本地数据反线,源极连接第三mos管的漏极;第三mos管的栅极接收第三控制信号,源极接地。

18.另外,第一写入模块,还包括:包括第四mos管、第五mos管和第六mos管的第二转换电路;第四mos管的栅极接收第四控制信号,源极连接第一全局数据线,漏极连接第一本地数据反线,第三控制信号和第四控制信号互为反相信号;第五mos管的栅极连接第一全局数据线,漏极连接第一本地数据正线,源极连接第六mos管的漏极;第六mos管的栅极接收第四控制信号,源极接地。

19.另外,第一全局数据线包括互为差分数据传输线的第一全局数据正线和第二全局数据反线;第一写入模块还包括:第一写入电路被配置为,控制第一全局数据正线中的数据传输至第一本地数据正线,或将第一全局数据反线中的数据传输至第一本地数据正线;第二写入电路被配置为,控制第一全局数据正线中的数据传输至第一本地数据反线,或将第一全局数据反线中的数据传输至第一本地数据反线。通过设置用于传输差分数据的第一全局数据正线和第一全局数据反线,保证第一本地数据正线、第一本地数据反线、第一全局数据正线和第一全局数据反线间数据翻转的稳定性。

20.另外,第一写入电路,包括:第一mos管和第二mos管;第一mos管的栅极接收第三控制信号,源极连接第一全局数据正线,漏极连接第一本地数据正线;第二mos管的栅极接收第三控制信号,源极连接第一全局数据反线,漏极连接第一本地数据反线。

21.另外,第二写入电路,包括:第三mos管和第四mos管;第三mos管的栅极接收第四控制信号,源极连接第一全局数据正线,漏极连接第一本地数据反线,第三控制信号和第四控制信号互为反相信号;第四mos管的栅极接收第四控制信号,源极连接第一全局数据反线,漏极连接第一本地数据正线。

22.另外,读出模块连接在第一本地数据线与第一全局数据线之间,用于根据第二控制信号,控制第一本地数据线和第一全局数据线之间的数据传输,若高电平数据所占位数超过第二预设值,则读出模块被配置为将第一本地数据线中的数据的相反值传输至第一全局数据线;若高电平数据所占位数不超过第二预设值,则读出模块被配置为将第一本地数据线中的数据传输至第一全局数据线。

23.另外,读出模块连接第一全局数据线与检错模块,用于根据第二控制信号,控制第一全局数据线和检错模块之间的数据传输,若高电平数据所占位数超过第二预设值,则读出模块被配置为将第一全局数据线中的数据翻转后传输至检错模块;若高电平数据所占位数不超过第二预设值,则读出模块被配置为将第一全局数据线中的数据传输至检错模块。

24.另外,第二写入模块,包括:第七mos管,栅极接收写使能信号,源极连接第二全局数据线,漏极连接第二本地数据正线;第八mos管,栅极连接第二全局数据线,漏极连接第二本地数据反线,源极连接第九mos管的漏极;第九mos管的栅极接收写使能信号,源极接地。

附图说明

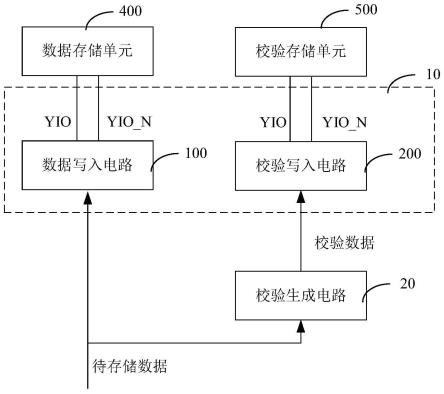

25.图1为本技术实施例提供的存储器的结构示意图;

26.图2为本技术实施例提供的判断模块的结构示意图;

27.图3为本技术实施例提供的转换模块的电路示意图;

28.图4为本技术实施例提供的使能控制模块的电路示意图;

29.图5为本技术实施例提供的第一转换电路的电路示意图;

30.图6为本技术实施例提供的第二转换电路的电路示意图;

31.图7为本技术实施例提供的第二写入模块的电路示意图;

32.图8为本技术实施例提供的对应于图1的一种读出模块的电路示意图;

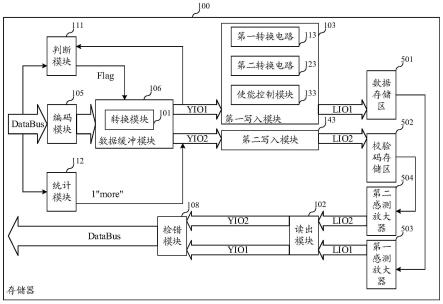

33.图9为本技术实施例提供的存储器的结构示意图;

34.图10为本技术实施例提供的对应于图9的一种读出模块的电路示意图;

35.图11为本技术实施例提供的第一感测放大器的电路示意图;

36.图12和图13为本技术实施例提供的存储器的结构示意图;

37.图14为本技术实施例提供的第一写入电路的电路示意图;

38.图15为本技术实施例提供的第二写入电路的电路示意图;

39.图16为本技术实施例提供的对应于图12的一种读出模块的电路示意图;

40.图17为本技术实施例提供的对应于图13的一种读出模块的电路示意图。

具体实施方式

41.随着技术的进步,存储器中存储单元的集成度越来越高,存储单元阵列中数据传输线路的长度越来越大。在向存储器的存储单元中存储数据和读出数据的过程中,应用了省电算法在存储单元阵列中的数据传输线路,由于存储单元阵列中数据传输线路的长度越来越大,向存储单元中写入数据和读出数据的耗电量越来越高;另外,申请人发现,dram(dynamic random access memory,dram)感测高电平的能力低于感测低电平的能力;同时,向dram的存储单元中存取高电平数据,相比于存取低电平数据的漏电情况更加严重。

42.为解决上述问题,本技术实施例提供了一种存储器,包括数据存储区和校验码存储区,包括:编码模块,连接外部数据线,用于根据外部数据线中传输的原始数据生成ecc校验码,ecc校验码用于对原始数据在存储过程中发生的错误进行纠正;判断模块,与外部数据线、第一全局数据线连接,用于输出表征原始数据与第一全局数据线当前传输的数据的差异位数是否超过第一预设值的第一控制信号;统计模块,与外部数据线连接,用于输出第二控制信号,第二控制信号用于表征,原始数据中高电平数据所占位数是否超过第二预设值;数据缓冲模块,与编码模块和判断模块连接,用于根据第一控制信号,将原始数据传输至第一全局数据线或将原始数据进行翻转后传输至第一全局数据线;数据缓冲模块还被配置为将ecc校验码传输至第二全局数据线;第一写入模块,连接在第一本地数据线和第一全局数据线之间,控制第一全局数据线中的数据传输至第一本地数据线,且基于第三控制信号,判断第一全局数据线中的数据传输至第一本地数据线的过程中是否进行数据翻转,其中,第三控制信号用于表征第一控制信号的值和第二控制信号的值是否相同;第二写入模块,连接在第二本地数据线和第二全局数据线之间,用于将第二全局数据线的数据传输至第二本地数据线;其中,第一写入模块的驱动能力小于第二写入模块的驱动能力;其中,第

一全局数据线、第一本地数据线、第一写入模块与数据存储区对应,第二全局数据线、第二本地数据线、第二写入模块与校验码存储区对应。

43.为使本技术实施例的目的、技术方案和优点更加清楚,下面将结合附图对本技术的各实施例进行详细的阐述。然而,本领域的普通技术人员可以理解,在本技术各实施例中,为了使读者更好地理解本技术而提出了许多技术细节。但是,即使没有这些技术细节和基于以下各实施例的种种变化和修改,也可以实现本技术所要求保护的技术方案。以下各个实施例的划分是为了描述方便,不应对本技术的具体实现方式构成任何限定,各个实施例在不矛盾的前提下可以相互结合,相互引用。

44.图1为本实施例提供的存储器的结构示意图,图2为本实施例提供的判断模块的结构示意图,图3为本实施例提供的转换模块的电路示意图,图4为本实施例提供的使能控制模块的电路示意图,图5为本实施例提供的第一转换电路的电路示意图,图6为本实施例提供的第二转换电路的电路示意图,图7为本实施例提供的第二写入模块的电路示意图,图8为本实施例提供的对应于图1的一种读出模块的电路示意图,图9为本实施例提供的存储器的结构示意图,图10为本实施例提供的对应于图9的一种读出模块的电路示意图,图11为本实施例提供的第一感测放大器的电路示意图,图12和图13为本实施例提供的存储器的结构示意图,图14为本实施例提供的第一写入电路的电路示意图,图15为本实施例提供的第二写入电路的电路示意图,图16为本实施例提供的对应于图12的一种读出模块的电路示意图,图17为本实施例提供的对应于图13的一种读出模块的电路示意图;以下结合附图对本实施例提供的存储器作进一步详细说明。

45.参考图1,存储器100,包括数据存储区501和校验码存储区502,其中,数据存储区501用于存储原始数据,校验码存储区502用于存储原始数据的ecc校验码,还包括:

46.编码模块105,连接外部数据线databus,用于根据外部数据线databus中传输的原始数据生成ecc校验码,ecc校验码用于对原始数据在存储过程中发生的错误进行纠正。

47.需要说明的是,本实施例中提到的外部数据线databus仅是为了区分与第一全局数据线yio1、第二全局数据线yio2并非同一传输线路,外部数据线databus中的“外部”是相对于第一全局数据线yio1、第二全局数据线yio2和存储器100中数据存储区501和校验码存储区502的外部,并非芯片外部的数据线。

48.判断模块111,与外部数据线databus和第一全局数据线yio1连接,用于输出表征原始数据与第一全局数据线yio1当前传输的数据的差异位数是否超过第一预设值的第一控制信号。

49.具体地,参考图2,判断模块111包括:

50.检测单元201,连接外部数据线databus和第一全局数据线yio1,并逐位检测外部数据线databus当前传输的原始数据与第一全局数据线yio1当前传输的数据。若当前位原始数据与当前位第一全局数据线yio1传输的数据不同,则生成第一子控制信号;若当前位原始数据与当前位第一全局数据线yio1传输的数据相同,则传输第二子控制信号。具体地,生成第一子控制信号和第二子控制信号的方式参考如下表格:

[0051] 原始数据第一全局数据线yio1数据产生第一位01第一子控制信号第二位00第二子控制信号

第三位11第二子控制信号第四位10第一子控制信号

[0052]

获取单元202,连接检测单元201,用于获取第一子控制信号和第二子控制信号。若第一子控制信号个数超过第一预设值,则生成第一控制信号flag,第一预设值为第一子控制信号的数量与第二子控制信号的数量和的预设百分比。具体地,生成第一控制信号flag方式参考如下表格(以第一子控制信号和第二子控制信号的数量和为40为例,仅为示意):

[0053]

预设百分比第一子控制信号数量第二子控制信号数量第一控制信号flag401822150231716022180

[0054]

需要说明的是,在本示例中,预设百分比为50%,通过设置预设百分比为50%,保证原始数据和第一全局数据线yio1当前传输的数据的差异位数大于相同位数时产生第一控制信号,将原始数据翻转后传入第一全局数据线yio1,从而避免第一全局数据线yio1中的数据翻转,节省数据传输时的能耗。

[0055]

继续参考图1,存储器100,包括:数据缓冲模块106,与编码模块105、判断模块111连接,用于根据第一控制信号flag,将原始数据传输至第一全局数据线yio1或将原始数据进行翻转后传输至第一全局数据线yio1;数据缓冲模块106还被配置为将ecc校验码传输至第二全局数据线yio2。

[0056]

具体地,数据缓冲模块106,包括:

[0057]

转换模块101,用于根据第一控制信号flag,控制原始数据传输至第一全局数据线yio1时是否需要翻转。

[0058]

对于转换模块101,若原始数据与第一全局数据线yio1当前传输的数据的差异位数超过第一预设值,则转换模块101被配置为将原始数据翻转后传输至第一全局数据线yio1;若原始数据与第一全局数据线yio1当前传输的数据的差异位数不超过第一预设值,则转换模块101被配置为将原始数据传输至第一全局数据线yio1。

[0059]

在一个例子中,参考图3,转换模块101包括:第三传输元件303,一端通过反相器连接编码模块105,另一端连接第一全局数据线yio1;第四传输元件304,一端连接编码模块105,另一端连接第一全局数据线yio1;其中,第三传输元件303和第四传输元件304还用于接收第一控制信号flag,用于根据第一控制信号flag选择导通第三传输元件303或第四传输元件304。

[0060]

本实施例以低电平控制第三传输元件303和第四传输元件304导通为例进行说明,具体如下:

[0061]

当第一控制信号flag为“1”时,第三传输元件303导通所在信号传输线,此时编码模块105通过反相器连接第一全局数据线yio1,从而实现将原始数据翻转后传入第一全局数据线yio1;第四传输元件304关断所在信号传输线。当控制信号flag为“0”时,第三传输元件303关断所在信号传输线,第四传输元件304导通所在信号传输线,此时编码模块105直接连接第一全局数据线yio1,从而实现将原始数据直接传入第一全局数据线yio1。

[0062]

需要说明的是,在其他实施例中,同样可以采用不同控制方法来控制第三传输元件和第四传输元件导通,只要原始数据与第一全局数据线yio1当前传输的数据的差异位数

超过第一预设值时,将原始数据翻转后传入第一全局数据线yio1;原始数据与第一全局数据线yio1当前传输的数据的差异位数未超过第一预设值时,将原始数据直接传入第一全局数据线yio1。

[0063]

继续参考图1,存储器100,还包括:统计模块112,与外部数据线databus连接,用于输出第二控制信号1“more”,第二控制信号1“more”用于表征,原始数据中高电平数据所占位数是否超过第二预设值,具体地,生成第二控制信号1“more”方式参考如下表格(以第二预设值为外部数据线传输的数据的位数的50%为例说明):

[0064]

原始数据中高电平数量原始数据中低电平数量第二控制信号1“more”2218119210

[0065]

需要说明的是,在其他实施例中,同样可以配置当原始数据中高电平数据数量大于原始数据中低电平数据数量,第二控制信号为0;当原始数据中高电平数据数量小于原始数据中低电平数据数量,第二控制信号为1。

[0066]

另外,第二控制信号1“more”作为标记位数据存入校验码存储区502中,以在读出数据的过程中,将第二控制信号1“more”读出。

[0067]

在一个例子中,参考图2,统计模块112用于逐位检测原始数据,并基于高电平数据所占位数是否超过第二预设值,获取第二控制信号1“more”。

[0068]

需要说明的是,在本示例中,第二预设值为50%,通过设置第二预设值为50%,保证将原始数据存入数据存储区501时,存入低电平的数据量不小于存入高电平的数据量,从而提高原始数据存储和读出的可靠性。

[0069]

继续参考图1,存储器100,还包括:第一写入模块103,连接在第一本地数据线lio1和第一全局数据线yio1之间,控制第一全局数据线yio1中的数据传输至第一本地数据线lio1,且基于第三控制信号wren,判断第一全局数据线yio1中的数据传输至第一本地数据线lio1的过程中是否进行数据翻转,其中,第三控制信号wren用于表征第一控制信号flag的值和第二控制信号1“more”的值是否相同。具体地,第三控制信号wren用于控制存入低电平的数据数量不小于存入高电平的数据数量。

[0070]

本实施例以第一控制信号flag为1时,表征原始数据在传输至第一全局数据线yio1时需要进行数据翻转;第二控制信号1“more”为1时,表征原始数据在最终读出时需要进行数据翻转;此时,数据在传输至第一全局数据线yio1时已做翻转,则数据最终读出时无需再做翻转,即第三控制信号wren为1时,表征数据无需翻转。相应地,当第一控制信号flag为1时,表征原始数据在传输至第一全局数据线yio1时需要进行数据翻转;第二控制信号1“more”为0时,表征数据在最终读出时不需要进行数据翻转;此时,数据在传输至第一全局数据线yio1时已做翻转,则数据最终读出时需要再翻转回来,即第三控制信号wren为0时,表征数据需翻转。第三控制信号wren的配置参考如下表格:

[0071]

第一控制信号flag第二控制信号1“more”第三控制信号wren翻转翻转不翻转翻转不翻转翻转不翻转翻转翻转不翻转不翻转不翻转

[0072]

需要说明的是,当第一控制信号flag和第二控制信号1“more”的设置方式发生改变时,第三控制信号wren的设置方式需适应于第一控制信号flag和第二控制信号1“more”的设置方式改变,以保证最终存入数据存储区501的低电平的数据数量不小于存入入数据存储区501的高电平的数据数量。

[0073]

继续参考图1,第一写入模块103包括:使能控制模块133,用于根据第一控制信号flag和第二控制信号1“more”生成第三控制信号wren。

[0074]

另外,在本实施例中,使能控制模块133还用于接收写使能信号writeenable(参考图4),若写使能信号writeenable为有效电平,则输出用于表征第一控制信号和第二控制信号是否相同的第三控制信号wren。

[0075]

在一个例子中,参考图4,第一控制信号flag和第二控制信号1“more”通过一个异或门xor连接,异或门xor的输出端与写使能信号writeenable的反相信号writeenable-连接在同一个或非门上。

[0076]

在本示例中,使能控制模块133还用于接收第一控制信号flag、第二控制信号1“more”和写使能信号的反相信号writeenable-,写使能信号writeenable为有效电平,则产生第四控制信号wren-,第三控制信号wren和第四控制信号wren-互为反相信号。

[0077]

具体地,第一控制信号flag和第二控制信号1“more”通过一个异或门xor连接,异或门xor的输出端连接一反相器,且与写使能信号writeenable的反相信号writeenable-连接在同一个或非门上。

[0078]

对于上述第三控制信号wren和第四控制信号wren-的生成电路,当写使能信号writeenable为0时,写使能信号的反相信号writeenable-为1,此时第三控制信号wren和第四控制信号wren-一定都为0,存储器无法执行写入操作,说明此时存储器并不处于写操作阶段;当写使能信号writeenable为1时,写使能信号的反相信号writeenable-为0,此时该电路的功能如下:

[0079]

若第一控制信号flag为1,第二控制信号1“more”为1,由于异或门xor的工作原理为“相同为0,不同为1”,此时异或门xor的输出信号为0,此时,生成的第三控制信号wren为1,第四控制信号wren-为0。

[0080]

若第一控制信号flag为1,第二控制信号1“more”为0,由于异或门xor的工作原理为“相同为0,不同为1”,此时异或门xor的输出信号为1,此时,生成的第三控制信号wren为0,第四控制信号wren-为1。

[0081]

若第一控制信号flag为0,第二控制信号1“more”为1,由于异或门xor的工作原理为“相同为0,不同为1”,此时异或门xor的输出信号为1,此时,生成的第三控制信号wren为0,第四控制信号wren-为1。

[0082]

若第一控制信号flag为0,第二控制信号1“more”为0,由于异或门xor的工作原理为“相同为0,不同为1”,此时异或门xor的输出信号为0,此时,生成的第三控制信号wren为1,第四控制信号wren-为0。

[0083]

继续参考图1,在本实施例中,第一本地数据线lio1包括互为差分数据传输线的第一本地数据正线lio1和第一本地数据反线lio1-;通过设置用于传输差分数据的第一本地数据正线lio1和第一本地数据反线lio1-,保证第一本地数据线lio1和第一全局数据线yio1间数据翻转的稳定性。

[0084]

第一全局数据线yio1中的数据传输至第一本地数据线lio1的过程中进行数据翻转,包括:第一写入模块103被配置为将第一全局数据线yio1中的数据翻转后传输至第一本地数据正线lio1,和/或第一写入模块103被配置为将第一全局数据线yio1中的数据传输至第一本地数据反线lio1-。

[0085]

具体地,第一写入模块103包括:第一转换电路113和第二转换电路123。

[0086]

第一转换电路113被配置为,控制第一全局数据线yio1中的数据传输至第一本地数据正线lio1,和/或控制第一全局数据线yio1中的数据的相反值传输至第一本地数据反线lio1-。

[0087]

在一个例子中,参考图5,第一转换电路113包括:第一mos管401、第二mos管402和第三mos管403。

[0088]

其中,第一mos管401的栅极接收第三控制信号wren,源极连接第一全局数据线yio1,漏极连接第一本地数据正线lio1;第二mos管402的栅极连接第一全局数据线yio1,漏极连接第一本地数据反线lio1-,源极连接第三mos管403的漏极;第三mos管403的栅极接收第三控制信号wren,源极接地gnd(未图示)。

[0089]

需要说明的是,第一mos管401、第二mos管402和第三mos管403中所称的“源极”或“漏极”只是用于区分mos管的端口,并不做任何限定,即源极和漏极的概念可以互换。

[0090]

第二转换电路123被配置为,控制第一全局数据线yio1中的数据传输至第一本地数据反线lio1-,和/或控制第一全局数据线yio1中的数据的相反值传输至第一本地数据正线lio1。

[0091]

在一个例子中,参考图6,第二转换电路123包括:第四mos管404、第五mos管405和第六mos管406。

[0092]

第四mos管404的栅极接收第四控制信号wren-,源极连接第一全局数据线yio1,漏极连接第一本地数据反线lio1-;第五mos管405的栅极连接第一全局数据线yio1,漏极连接第一本地数据正线lio1,源极连接第六mos管406的漏极;第六mos管406的栅极接收第四控制信号wren-,源极接地(未图示)。

[0093]

需要说明的是,第四mos管404、第五mos管405和第六mos管406中所称的“源极”或“漏极”只是用于区分mos管的端口,并不做任何限定,即源极和漏极的概念可以互换。

[0094]

对于第一转换电路113和第二转换电路123,其工作原理如下:

[0095]

当第三控制信号wren为1时,第四控制信号wren为0,此时第一全局数据线yio1和第一本地数据正线lio1、第一本地数据反线lio1-之间的数据传输通过第一转换电路113调控。具体地,当yio1为1时,此时第一mos管401、第二mos管402和第三mos管403的栅极都导通,第一全局数据线yio1和第一本地数据正线lio1通过第一mos管401相连,第一本地数据正线lio1同第一全局数据线yio1为1;第一本地数据反线lio1-通过第二mos管402和第三mos管403接地,即第一本地数据反线lio1-为0;当yio1为0时,第一全局数据线yio1和第一本地数据正线lio1通过第一mos管401相连,第一本地数据正线lio1同第一全局数据线yio1为0;由于第一全局数据线yio1为0,第二mos管402的源漏不导通,第一本地数据反线lio1-并未接地,由于预充电的影响(即在写入之前lio1和lio1-均会被预充到高电平),第一本地数据反线lio1-为1。

[0096]

当第三控制信号wren为0时,第四控制信号wren为1,此时第一全局数据线yio1和

第一本地数据正线lio1、第一本地数据反线lio1-之间的数据传输通过第二转换电路123调控。具体地,当yio1为1时,此时第四mos管404、第五mos管405和第六mos管406的栅极都导通,第一全局数据线yio1和第一本地数据反线lio1-通过第四mos管404相连,第一本地数据反线lio1-同第一全局数据线yio1为1;第一本地数据正线lio1通过第五mos管405和第六mos管406接地,即第一本地数据正线lio1为0;当yio1为0时,第一全局数据线yio1和第一本地数据反线lio1-通过第四mos管404相连,第一本地数据反线lio1-同第一全局数据线yio1为0;由于第一全局数据线yio1为0,第五mos管405的源漏不导通,第一本地数据正线lio1并未接地,由于预充电的影响(即在写入之前lio1和lio1-均会被预充到高电平),第一本地数据正线lio1为1。

[0097]

继续参考图1,存储器100,还包括:第二写入模块143,连接在第二本地数据线lio2和第二全局数据线yio2之间,用于将第二全局数据线yio2的数据传输至第二本地数据线lio2。

[0098]

具体地,参考图7,第二写入模块143,包括:第七mos管407、第八mos管408和第九mos管409。

[0099]

其中,第七mos管407的栅极接收写使能信号writeenable,源极连接第二全局数据线yio2,漏极连接第二本地数据正线lio2;第八mos管408的栅极连接第二全局数据线yio2,漏极连接第二本地数据反线lio2-,源极连接第九mos管409的漏极;第九mos管409的栅极接收写使能信号writeenable,源极接地gnd(未图示)。

[0100]

需要说明的是,第七mos管407、第八mos管408和第九mos管409中所称的“源极”或“漏极”只是用于区分mos管的端口,并不做任何限定,即源极和漏极的概念可以互换。

[0101]

对于第二写入模块143,当写入使能信号为0时,存储器无法执行写入操作,说明此时存储器并不处于写操作阶段;当写入使能信号为1时,存储器执行写入操作,其工作原理如下:

[0102]

当yio2为1时,此时第七mos管407、第八mos管408和第九mos管409的栅极都导通,第二全局数据线yio2和第二本地数据正线lio2通过第七mos管407相连,第二本地数据正线lio2同第二全局数据线yio2为1;第二本地数据反线lio2-通过第八mos管408和第九mos管409接地,即第二本地数据反线lio2-为0;当yio2为0时,第二全局数据线yio2和第二本地数据正线lio2通过第七mos管407相连,第二本地数据正线lio2同第二全局数据线yio2为0;由于第二全局数据线yio2为0,第八mos管408的源漏不导通,第二本地数据反线lio2-并未接地,由于预充电的影响(即在写入之前lio2和lio2-均会被预充到高电平),第二本地数据反线lio2-为1。

[0103]

需要说明的是,由于第一写入模块103的驱动能力小于第二写入模块143的驱动能力,即第二写入模块143中mos管的宽长比大于第一写入模块103中mos管的宽长比,或第二写入模块143中mos管的阈值电压小于第一写入模块103中mos管的阈值电压。

[0104]

在一个实施例中,第七mos管407的宽长比大于第四mos管404和第一mos管401的宽长比,和/或第八mos管408的宽长比大于第五mos管405和第二mos管402的宽长比,和/或第九mos管409的宽长比大于第六mos管406和第三mos管403的宽长比。在其他实施例中,也可以是这些mos管的阈值电压不同。

[0105]

通过第一写入模块103和第二写入模块143分别进行原始数据和ecc校验码的存

储,提高了存储器100的数据存入速率。需要说明的是,在本实施例中,第一写入模块103的驱动能力小于第二写入模块143的驱动能力。由于ecc校验码是原始数据在编码模块105进行ecc检测后产生,即ecc校验码传输至第二写入模块143的时间相较于原始数据传输至第一写入模块103的时间存在写入延迟,存储器在存储原始数据时是对原始数据和ecc校验码一并存储,本实施例通过第一写入模块103的驱动能力小于第二写入模块143的驱动能力,加快ecc校验码从第二全局数据线yio2到第二本地数据线lio2的写入速率,以缩短写入延时,进一步提高存储器100的数据存入速率。

[0106]

需要说明的是,上述提到的“驱动能力”具体为晶体管的尺寸、掺杂离子、掺杂浓度、阈值电压等不同导致的驱动能力的不同。在一些实施例中,所称的“驱动能力”可以是在相同电压条件下,用流过晶体管的电流大小来表征。

[0107]

还需要说明的是,在本实施例中,第一全局数据线yio1、第一本地数据线lio1、第一写入模块103与数据存储区501对应,用于向数据存储区501存入原始数据和第二控制信号1“more”;第二全局数据线yio2、第二本地数据线lio2、第二写入模块143与检验码存储区502对应,用于向检验码存储区502存入原始数据的ecc校验码。

[0108]

继续参考图1,存储器100,还包括:

[0109]

检错模块108,用于根据ecc校验码判断原始数据在存储期间是否发生错误,和/或对发生错误的原始数据进行纠错。

[0110]

读出模块102,用于根据读出的第二控制信号1“more”,控制第一本地数据线lio1的原始数据向后传输时是否需要翻转;若高电平数据所占位数超过第二预设值,则读出模块102被配置为将原始数据翻转后最终传输至检错模块108;若高电平数据所占位数不超过第二预设值,读出模块102被配置为将原始数据最终传输至检错模块108。

[0111]

另外,读出模块102还用于将第二本地数据线lio2的数据传输至第二全局数据线yio2,或将第二全局数据线yio2的数据传输至检错模块108。

[0112]

需要说明的是,在本实施例中,读出模块102与检错模块108之间还包括数据缓冲模块106(附图中未给出),由于数据读出时的数据缓冲并不涉及本技术的核心方案,因此不做赘述,本领域技术人员理解存储器在将数据读出时,需要数据同样需要经过数据缓冲模块。

[0113]

在一个例子中,参考图1,在本实施例中,读出模块102连接在第一本地数据线lio1和第一全局数据线yio1之间,用于根据第二控制信号1“more”控制第一本地数据线lio1和第一全局数据线yio1之间的数据传输。

[0114]

若高电平数据所占位数超过第二预设值,则读出模块102被配置为将第一本地数据线lio1中的数据翻转后传输至第一全局数据线yio1;若高电平数据所占位数不超过第二预设值,读出模块102被配置为将第一本地数据线lio1中的数据传输至第一全局数据线yio1。

[0115]

具体地,第一本地数据线lio1包括互为差分数据传输线的第一本地数据正线lio1和第一本地数据反线lio1-;通过设置用于传输差分数据的第一本地数据正线lio1和第一本地数据反线lio1-,保证第一本地数据线lio1和第一全局数据线yio1间数据翻转的稳定性。

[0116]

将第一本地数据线lio1中的数据翻转后传输至第一全局数据线yio1,包括:读出

模块102被配置为将第一本地数据正线lio1中的数据的相反值传输至第一全局数据线yio1,和/或读出模块102被配置为将第一本地数据反线lio1-中的数据传输至第一全局数据线yio1。

[0117]

参考图8,读出模块102包括:第十mos管410、第十一mos管411、第十二mos管412、第十三mos管413和第十四mos管414。

[0118]

其中,第十mos管410的栅极连接第一本地数据正线lio1,漏极连接第一全局数据线yio1,源极连接第十二mos管412的漏极;第十一mos管411的栅极连接第一本地数据反线lio1-,漏极连接第一全局数据线yio1,源极连接第十三mos管413的漏极;第十二mos管412的栅极接收第二控制信号1“more”,源极连接第十四mos管414的漏极;第十三mos管413的栅极接收第五控制信号1“more

”‑

,源极连接第十四mos管414的漏极,第二控制信号1“more”和第五控制信号1“more

”‑

互为反相信号;第十四mos管414的栅极接收读使能信号readenable,源极接地gnd(未图示)。

[0119]

对于上述转换电路,当读使能信号readenable是0时,存储器无法执行读取操作,表示此时存储器并不处于读取操作阶段;当读使能信号readenable是1,其工作原理如下:

[0120]

当第二控制信号1“more”为1时,第五控制信号1“more

”‑

为0,相当于仅导通左侧电路,表征将第一本地数据正线lio1中的数据的相反值传输至第一全局数据线yio1。当第一本地数据正线lio1为1时,导通第十mos管410,此时第一全局数据线yio1接地,第一全局数据线yio1为0,实现将第一本地数据正线lio1中的数据的相反值传输至第一全局数据线yio1;当第一本地数据正线lio1为0时,关断第十mos管410,此时由于预充电的影响(即在读出之前yio1会被预充到高电平),第一全局数据线yio1为1,实现将第一本地数据正线lio1中的数据的相反值传输至第一全局数据线yio1。

[0121]

当第二控制信号1“more”为0时,第五控制信号1“more

”‑

为1,相当于仅导通左侧电路,表征将第一本地数据反线lio1-中的数据的相反值传输至第一全局数据线yio1。当第一本地数据反线lio1-为1时,导通第十二mos管412,此时第一全局数据线yio1接地,第一全局数据线yio1为0,实现将第一本地数据反线lio1-中的数据的相反值传输至第一全局数据线yio1;当第一本地数据反线lio1-为0时,关断第十二mos管412,此时由于预充电的影响(即在读出之前yio1会被预充到高电平),第一全局数据线yio1为1,实现将第一本地数据反线lio1-中的数据的相反值传输至第一全局数据线yio1。

[0122]

需要说明的是,第十mos管410、第十一mos管411、第十二mos管412、第十三mos管413和第十四mos管414中所称的“源极”或“漏极”只是用于区分mos管的端口,并不做任何限定,即源极和漏极的概念可以互换。

[0123]

在另一个例子中,参考图9,在本实施例中,读出模块102连接第一全局数据线yio1和检错模块108,用于根据第二控制信号1“more”控制第一全局数据线yio1和检错模块108之间的数据传输。

[0124]

具体地,若高电平数据所占位数超过第二预设值,则读出模块102被配置为将第一全局数据线yio1中的数据翻转后传输至检错模块108;若高电平数据所占位数不超过第二预设值,则读出模块102被配置为将第一全局数据线yio1中的数据传输至检错模块108。

[0125]

更具体地,参考图10,本实施例以低电平控制第一传输元件301和第二传输元件302导通为例进行说明,具体如下:当第二控制信号1“more”为1时,第一传输元件导通所在

信号传输线,此时第一全局数据线yio1通过反相器连接检错模块108,从而实现第一全局数据线yio1将传输的数据翻转后传入检错模块108;第二传输元件302关断所在信号传输线。当第二控制信号1“more”为0时,第一传输元件301关断所在信号传输线,第二传输元件302导通所在信号传输线,此时第一全局数据线yio1直接连接检错模块108,从而实现第一全局数据线yio1将传输的数据直接传入检错模块108。

[0126]

需要注意的是,针对第二全局数据线yio2与第二本地数据线lio2之间读出电路则无需进行第二控制信号1“more”的判断。在一些实施例中,第二本地数据线lio2包括第二本地数据正线lio2和第二本地数据反线lio2-,第二全局数据线yio2与第二本地数据正线lio2和第二本地数据反线lio2-之间的读出电路与图8所示的电路类似,但没有图中受第二控制信号1“more”控制的第十二mos管412和第十三mos管413,在此不再赘述。

[0127]

继续参考图1,在本实施例中,还包括:第一感测放大器503和第二感测放大器504,其中,第一感测放大器503,用于在读操作时对数据存储区501所存储的原始数据进行读取,并传输至第一本地数据线lio1;第二感测放大器504,用于在读操作时对校验码存储区502所存储的ecc校验码、第二控制信号1“more”进行读取,并传输至第二本地数据线lio2;其中,第一感测放大器503的驱动能力小于第二感测放大器503的驱动能力。

[0128]

第二感测放大器504的电路结构与第一感测放大器503的电路结构相同,由于第一感测放大器503的驱动能力小于第二感测放大器503的驱动能力,即第一感测放大器503中mos管的宽长比小于第二感测放大器504中mos管的宽长比,或第一感测放大器503中mos管的阈值电压的大于第二感测放大器504中mos管的阈值电压。具体地,参考图11,本实施例以第一感测放大器503的电路结构为例进行详细说明:

[0129]

第一感测放大器503包括一组nmos管(511和512)和一组pmos管(521和522),其中位线bl连接第一nmos管511和第一pmos管的栅极,互补位线blb连接第二nmos管512和第二pmos管522的栅极,另外,第一pmos管521的漏极和第二pmos管的漏极连接电源,第一pmos管521的源极连接互补位线blb,第二pmos管522的源极连接位线bl,第一nmos管511的漏极和第一nmos管的漏极接地,第一nmos管511的源极连接互补位线blb,第二nmos管512的源极连接位线bl。

[0130]

需要说明的是,在其他实施例中,第一感测放大器也可以是其他具备失调电压补偿的感测放大器结构。

[0131]

由于第一本地数据线lio1中传输的原始数据通过第二控制信号1“more”进行了高电平数据的统计,保证原始数据在存入时低电平数据量大于高电平数据量,从而保证数据读取的稳定性,

[0132]

ecc校验码和第二控制信号1“more”在存入时并未进行第二控制信号1“more”的统计,此时存入的数据可能存在较多的高电平数据,通过设置第二感测放大器504的驱动能力大于第一感测放大器503的驱动能力,来尽量避免校验码存储区的ecc校验码在读取过程中可能发生的错误,以保证ecc校验码和第二控制信号1“more”的准确性。在一些实施例中,所称的“驱动能力”可以是在相同电压条件下,用流过晶体管的电流大小来表征。

[0133]

参考图12和图13,第一全局数据线yio1包括互为差分数据传输线的第一全局数据正线yio1和第一全局数据反线yio1-,通过设置用于传输差分数据的第一全局数据正线yio1和第一全局数据反线yio1-,保证第一本地数据正线lio1、第一本地数据反线lio1-和

第一全局数据正线yio1、第一全局数据反线yio1-间数据翻转的稳定性。

[0134]

在一个例子中,编码模块105与第一全局数据反线yio1-也同样设置有与转换模块101类似的数据转换电路,其控制过程与转换模块101相反,即,控制在第一控制信号flag为“1”时导通将原始数据直接传输至第一全局数据反线yio1-,在第一控制信号flag为“0”时导通将原始数据通过反相器传输至第一全局数据反线yio1-。

[0135]

在一些实施例中,第一全局数据正线yio1和第一全局数据反线yio1-之间可以设置有放大电路,以实现第一全局数据正线yio1和第一全局数据反线yio-传输互为反相的信号。

[0136]

第一写入模块103包括:使能控制模块113、第一写入电路213和第二写入电路223

[0137]

第一写入电路213被配置为,控制第一全局数据正线yio1中的数据传输至第一本地数据正线lio1,或将第一全局数据反线yio1-中的数据传输至第一本地数据正线lio1。

[0138]

在一个例子中,参考图14,第一写入电路213,包括:第1mos管601和第2mos管602。

[0139]

其中,第1mos管601的栅极接收第三控制信号wren,源极连接第一全局数据正线yio1,漏极连接第一本地数据正线lio1;第2mos管602的栅极接收第三控制信号wren,源极连接第一全局数据反线yio1-,漏极连接第一本地数据正线lio1。

[0140]

需要说明的是,第1mos管601和第2mos管602中所称的“源极”或“漏极”只是用于区分mos管的端口,并不做任何限定,即源极和漏极的概念可以互换。

[0141]

第二写入电路223被配置为,控制第一全局数据正线yio1中的数据传输至第一本地数据反线lio1-,或将第一全局数据反线yio1-中的数据传输至第一本地数据反线lio1-。

[0142]

在一个例子中,参考图15,第二写入电路223,包括:第3mos管603和第4mos管604。

[0143]

其中,第3mos管603的栅极接收第四控制信号wren-,源极连接第一全局数据正线yio1,漏极连接第一本地数据反线lio1-,第三控制信号wren和第四控制信号wren-互为反相信号;第4mos管604的栅极接收第三控制信号wren-,源极连接第一全局数据反线yio1-,漏极连接第一本地数据反线lio1-。

[0144]

需要说明的是,第3mos管603和第4mos管604中所称的“源极”或“漏极”只是用于区分mos管的端口,并不做任何限定,即源极和漏极的概念可以互换。

[0145]

对于第一写入电路213和第二写入电路223,其工作原理如下:

[0146]

当第三控制信号wren为1,第四控制信号wren-为0,此时第一全局数据正线yio1、第一全局数据反线yio1-和第一本地数据正线lio1、第一本地数据反线lio1-之间的数据传输通过第一写入电路213和第二写入电路223调控。具体地,当yio1为1时,此时第1mos管601和第4mos管604的栅极导通,第一全局数据正线yio1和第一本地数据正线lio1通过第1mos管601相连,第一本地数据正线lio1同第一全局数据正线yio1为1;第一全局数据反线yio1-和第一本地数据反线lio1-通过第4mos管604相连,第一本地数据反线lio1-同第一全局数据反线yio1-为0。当yio1为0时,此时第1mos管601和第4mos管604的栅极导通,第一全局数据正线yio1和第一本地数据正线lio1通过第1mos管601相连,第一本地数据正线lio1同第一全局数据正线yio1为0;第一全局数据反线yio1-和第一本地数据反线lio1-通过第4mos管604相连,第一本地数据反线lio1-同第一全局数据反线yio1-为1。

[0147]

当第三控制信号wren为0,第四控制信号wren-为1,此时第一全局数据正线yio1、第一全局数据反线yio1-和第一本地数据正线lio1、第一本地数据反线lio1-之间的数据传

输通过第一写入电路213和第二写入电路223调控。具体地,当yio1为1时,此时第2mos管602和第3mos管603的栅极导通,第一全局数据反线yio1-和第一本地数据正线lio1通过第2mos管602相连,第一本地数据正线lio1同第一全局数据反线yio1-为0;第一全局数据正线yio1和第一本地数据反线lio1-通过第3mos管603相连,第一本地数据反线lio1-同第一全局数据正线yio1为1。当yio1为0时,此时第2mos管602和第3mos管603的栅极导通,第一全局数据反线yio1-和第一本地数据正线lio1通过第2mos管602相连,第一本地数据正线lio1同第一全局数据反线yio1-为1;第一全局数据正线yio1和第一本地数据反线lio1-通过第3mos管603相连,第一本地数据反线lio1-同第一全局数据正线yio1为0。

[0148]

在一个例子中,参考图12,读出模块102连接在第一本地数据正线lio1、第一本地数据反线lio1-、第一全局数据正线yio1和第一全局数据反线yio1-之间,用于根据第二控制信号1“more”控制第一本地数据正线lio1、第一本地数据反线lio1-与第一全局数据正线yio1、第一全局数据反线yio1-之间的数据传输。

[0149]

具体地,若高电平数据所占位数超过第二预设值,则读出模块102被配置为将第一本地数据正线lio1中的数据的相反值传输至第一全局数据正线yio1,和/或将第一本地数据反线lio1-中的数据的相反值传输至第一全局数据反线yio1-;若高电平数据所占位数不超过第二预设值,则读出模块102被配置为将第一本地数据正线lio1中的数据的相反值传输至第一全局数据反线yio1-,和/或将第一本地数据反线lio1-中的数据的相反值传输至第一全局数据正线yio1。

[0150]

更具体地,参考图16,读出模块102包括:第5mos管605、第6mos管606、第7mos管607、第8mos管608、第9mos管609、第10mos管610、第11mos管611、第12mos管612、第13mos管613和第14mos管614。

[0151]

其中,第13mos管613的栅极连接第一本地数据正线lio1,漏极连接第一全局数据反线yio1-,源极连接第7mos管607的漏极;第5mos管605的栅极连接第一本地数据反线lio1-,漏极连接第一全局数据反线yio1-,源极连接第8mos管608的漏极;第7mos管607的栅极连接第五控制信号1“more

”‑

,源极连接第11mos管611的漏极,第二控制信号1“more”和第五控制信号1“more

”‑

互为反相信号;第8mos管608的栅极连接第二控制信号1“more”,源极连接第11mos管611的漏极;第11mos管611的栅极接收读使能信号readenable,源极接地gnd(未图示);第14mos管614的栅极连接第一本地数据反线lio1-,漏极连接第一全局数据正线yio1,源极连接第9mos管609的漏极;第6mos管606的栅极连接第一本地数据正线lio1,漏极连接第一全局数据正线yio1,源极连接第10mos管610的漏极;第9mos管609的栅极连接第五控制信号1“more

”‑

,源极连接第12mos管612的漏极;第10mos管610的栅极连接第二控制信号1“more”,源极连接第12mos管612的漏极;第12mos管612的栅极接收读使能信号readenable,源极接地gnd(未图示)。

[0152]

对于上述转换电路,当读使能信号readenable是0时,存储器无法执行读取操作,表示此时存储器并不处于读取操作阶段;当读使能信号readenable是1,其工作原理如下:

[0153]

当第二控制信号1“more”为1时,第五控制信号1“more

”‑

为0,相当于仅导通中间电路,表征将第一本地数据正线lio1中的数据的相反值传输至第一全局数据正线yio1,并将第一本地数据反线lio1-中的数据的相反值传输至第一全局数据反线yio1-。当第一本地数据正线lio1为1时,导通第6mos管606,此时第一全局数据正线yio1接地,第一全局数据正线

yio1为0,实现将第一本地数据正线lio1中的数据的相反值传输至第一全局数据正线yio1;当第一本地数据反线lio1-为1时,导通第5mos管605,此时第一全局数据反线yio1-接地,第一全局数据反线yio1-为0,实现将第一本地数据反线lio1-中的数据的相反值传输至第一全局数据反线yio1-。

[0154]

当第二控制信号1“more”为0时,第五控制信号1“more

”‑

为1,相当于仅导通边缘电路,表征将第一本地数据正线lio1中的数据的相反值传输至第一全局数据反线yio1-,并将第一本地数据反线lio1-中的数据的相反值传输至第一全局数据正线yio1。当第一本地数据正线lio1为1时,导通第13mos管613,此时第一全局数据反线yio1-接地,第一全局数据反线yio1-为0,实现将第一本地数据正线lio1中的数据的相反值传输至第一全局数据反线yio1-;当第一本地数据反线lio1-为1时,导通第14mos管614,此时第一全局数据正线yio1接地,第一全局数据正线yio1为0,实现将第一本地数据反线lio1-中的数据的相反值传输至第一全局数据正线yio1。

[0155]

需要说明的是,第5mos管605、第6mos管606、第7mos管607、第8mos管608、第9mos管609、第10mos管610、第11mos管611、第12mos管612、第13mos管613和第14mos管614中所称的“源极”或“漏极”只是用于区分mos管的端口,并不做任何限定,即源极和漏极的概念可以互换。

[0156]

在另一个例子中,参考图13,读出模块102连接第一全局数据正线yio1、第一全局数据反线yio1-和检错模块108,用于根据第二控制信号1“more”,控制第一全局数据正线yio1、第一全局数据反线yio1-和检错模块108之间的数据传输。

[0157]

具体地,参考图17,读出模块102包括:第一传输元件301,一端连接第一全局数据反线yio1-,另一端连接检错模块108;第二传输元件302,一端连接第一全局数据正线yio1,另一端连接检错模块108;第一传输元件301和第二传输元件302还用于接收第二控制信号1“more”,用于根据第二控制信号1“more”导通第一传输元件301或第二传输元件302。

[0158]

本实施例以低电平控制第一传输元件301和第二传输元件302导通为例进行说明,具体如下:当第二控制信号1“more”为1时,第一传输元件导通所在信号传输线,此时第一全局数据反线yio1-连接检错模块108,从而实现第一全局数据反线yio1-将传输的数据传入检错模块108;第二传输元件302关断所在信号传输线。当第二控制信号1“more”为0时,第一传输元件301关断所在信号传输线,第二传输元件302导通所在信号传输线,此时第一全局数据正线yio1连接检错模块108,从而实现第一全局数据正线yio1将传输的数据传入检错模块108。

[0159]

与相关技术相比,通过对比原始数据和第一全局数据线中的数据差异,获取第一控制信号,判断是否进行第一次数据翻转,以降低在数据传输过程中,传输数据线翻转,节省数据传输的功耗;通过对比原始数据中低电平数据和高电平数据的数量,获取第二控制信号,通过第一控制信号和第二控制信号获取第三控制信号,判断第一全局数据线传输至第一本地数据线是否需要进行第二次数据翻转,以保证数据存储和读出的可靠性,并存入数据存储区;通过获取第二控制信号,判断在读出时是否需要第三次翻转,以保证读出的数据为原始写入存储器的数据;而ecc校验码通过第二全局数据线,以及第二本地数据线直接存进校验码存储区,且通过设置与校验码存储区对应的第二写入模块的驱动能力比与数据存储区对应的第一写入模块的驱动能力,来提高ecc校验码数据的写入速度,进而可以提高

整体的读写速度。

[0160]

值得一提的是,本实施例中所涉及到的各单元均为逻辑单元,在实际应用中,一个逻辑单元可以是一个物理单元,也可以是一个物理单元的一部分,还可以以多个物理单元的组合实现。此外,为了突出本技术的创新部分,本实施例中并没有将与解决本技术所提出的技术问题关系不太密切的单元引入,但这并不表明本实施例中不存在其它的单元。

[0161]

本领域的普通技术人员可以理解,上述各实施例是实现本技术的具体实施例,而在实际应用中,可以在形式上和细节上对其作各种改变,而不偏离本技术的精神和范围。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。