一种高耐压、低导通电阻igzo薄膜晶体管及其制备方法

技术领域

1.本发明涉及薄膜晶体管及其制造领域,特别是涉及一种创新型高耐压、低导通电阻igzo薄膜晶体管及其制备方法。

背景技术:

2.柔性电子,是将金属氧化物、有机材料、碳纳米管等电子器件制作在柔性、可延展基板上的新兴电子技术,获得了学术界和产业界的广泛关注。其应用涉及射频识别、信息显示、生物医疗、以及国防等技术领域。已有柔性电子产品仍大量使用传统固态器件,致使“全柔性”无法实现,其主要原因之一是柔性功率薄膜晶体管的缺失。铟镓锌氧化物(indium gallium zinc oxide,igzo)半导体具有高迁移率、低关态电流、宽带隙(~3.5ev)等优点,是制备柔性功率薄膜晶体管的理想沟道材料。至今已有大量针对igzo薄膜晶体管的迁移率、亚阈值摆幅、开关比等电学性能优化的工作,鲜有关于高性能的高压igzo薄膜晶体管的报道。传统igzo薄膜晶体管耐压能力与电流能力两者无法同时兼顾,其原因在于其击穿薄弱点位于栅极与源区电极、漏区电极交叠的栅介质层内,提升耐压必然意味着导通电阻的显著降低。因此,高耐压、低导通电阻的igzo功率薄膜晶体管的缺失问题亟待解决。

3.截至目前,提升igzo薄膜晶体管耐压的方法主要包括两种方法。其一是采用高介电常数栅极介电层材料并提升其厚度,以提升igzo薄膜晶体管耐压;其二是偏移栅电极和漏电极间的水平距离,引入漂移区结构,通过调节漂移区尺寸提升igzo薄膜晶体管的耐压。上述两种方法显著增加igzo薄膜晶体管的导通电阻,难以实现优异的导通电阻和击穿电压的折中关系。因此,制备一种具有高耐压、低导通电阻的igzo薄膜晶体管具有重要的意义。

技术实现要素:

4.本发明的目的在于克服现有技术不足,解决在提升igzo薄膜晶体管耐压同时,导致电流能力损失的问题。因此本发明提供了一种具有高耐压、低导通电阻的igzo薄膜晶体管及其制备工艺,通过在器件中引入漂移区结构提升耐压,并对漂移区进行氢离子掺杂以降低其导通电阻,有效提升igzo薄膜晶体管的功率

5.密度。

6.为了实现上述目的,本发明采用如下的技术方案:

7.一种igzo薄膜晶体管的制备方法,包括如下步骤:

8.获得基底;

9.在所述基底上形成栅电极层;

10.在所述栅电极层上覆盖栅极介电层;

11.在所述栅极介电层上形成igzo有源层;

12.在所述igzo有源层上相对两侧间隔的形成源区电极层和漏区电极层,通过偏移所述漏区电极层与栅电极层水平方向上的非交叠区距离形成漂移区,并通过氢离子注入降低所述漂移区电阻。

13.作为本发明的一个实施例,所述栅电极层为导电性优异的钼(mo)金属层,制作时采用磁控溅射工艺,栅电极厚度为100nm,水平长度为105μm。

14.作为本发明的一个实施例,所述栅极介电层材料为氧化硅,制作时采用pecvd工艺,制备的栅极介电层厚度为100nm。

15.作为本发明的一个实施例,所述igzo有源层采用磁控溅射工艺制备,厚度为20nm。

16.作为本发明的一个实施例,所述igzo有源层在ar气环境下350℃退火1h。

17.作为本发明的一个实施例,所述源区电极层、漏区电极层为导电性优异的铝(al)金属层,制作时采用电子束蒸发工艺。

18.作为本发明的一个实施例,所述的igzo低阻漂移区通过氢离子注入实现,氢等离子流量为170sccm,工艺温度为30℃,功率为100w,腔室压强为1200mtorr,处理时间为200s。

19.以及,一种igzo薄膜晶体管,包括基底、栅电极层、栅极介电层、igzo有源层、源区电极层、漏区电极层和低阻漂移区。所述栅电极层设于所述基底之上,所述栅极介电层覆盖于所述栅电极层上,所述igzo有源层设于所述栅极介电层上,所述源区电极层、漏区电极层间隔的设于所述igzo有源层表面上相对的两侧,所述低阻漂移区形成于所述漏区电极层与栅电极层水平位置上的非交叠区的igzo有源层内。

20.作为其中一种实施方式,所述衬底采用刚性半导体衬底。

21.作为其中一种实施方式,所述栅电极层与源区电极有5μm的交叠长度,与漏区电极有2μm的非交叠长度。

22.作为其中一种实施方式,所述igzo低阻漂移区长度为2μm。

23.作为其中一种实施方式,采用氢等离子体处理所述低阻漂移区,形成施主掺杂。

24.与现有技术相比,比发明的有益效果是:本发明通过在器件igzo低阻漂移区部分进行氢离子掺杂,提高igzo低阻漂移区内的载流子浓度,降低igzo沟道导通电阻,显著降低因非栅控漂移区提升器件耐压而牺牲的电流密度,获得了更为优异的导通电阻与击穿电压间的关系,同时相比传统砷离子掺杂、双栅结构等工艺,本发明降低了实验温度、简化了工艺步骤,极大地提升漂移区电流能力。

附图说明

25.为了更清晰、简洁地说明本发明的实施例和/或示例,本发明提供了多幅附图。用于描述附图的附加细节或示例不应当被认为是对所公开的发明、目前描述的实施例和/或示例以及目前理解的这些发明的最佳模式中的任何一者的范围的限制。

26.图1是现有的传统底栅交错结构igzo薄膜晶体管的示意图;其中110为基底,120为栅电极层,130为栅极介电层,140为igzo有源层,150为源区电极层,152为漏区电极层;

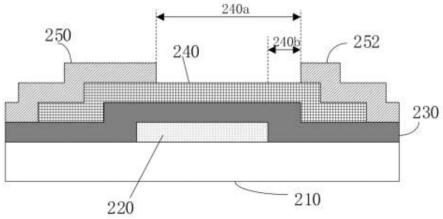

27.图2是存在漂移区的igzo薄膜晶体管的示意图;其中210为基底,220为栅电极层,230为栅极介电层,240为igzo有源层,其中240a为源、漏电极之间载流子输运的igzo沟道,240b为igzo漂移区,250为源区电极层,252为漏区电极层;

28.图3是本发明实施例中igzo薄膜晶体管的示意图;其中310为基底,320为栅电极层,330为栅极介电层,340为igzo有源层,其中340a为源、漏电极之间载流子输运的igzo沟道,342为igzo低阻漂移区,350为源区电极层,352为漏区电极层;

29.图4是本发明实施例中igzo薄膜晶体管的制造方法的流程图;

30.图5是本发明实施例与对比例的igzo薄膜晶体管击穿电压图;

31.图6是本发明实施例与对比例的igzo薄膜晶体管电流曲线图。

具体实施方式

32.为了便于理解本发明,下面将参照相关附图对本发明进行更全面的描述。

33.附图3中给出了本发明的实施例。但是,本发明可以以许多不同的形式来实现,并不限于本文所描述的实施例。相反地,提供这些实施例的目的是使读者对本发明的公开内容理解得更加透彻全面。除非另有定义,本文所使用的所有的技术和科学术语与属于本发明的技术领域的技术人员通常理解的含义相同。

34.图1是对比例1传统结构igzo薄膜晶体管的示意图,图2是对比例2带有漂移区的igzo薄膜晶体管的示意图,图3是本发明的一个实施例中带有低阻漂移区的igzo薄膜晶体管的示意图,图4是一个实施例中igzo薄膜晶体管的制造方法的流程图,该方法可以用于制造图3所示的igzo薄膜晶体管,包括如下步骤:

35.s10,获取基底。

36.基底可以是本领域习知的刚性基底(例如玻璃)或柔性基底。在本发明的一个实施例中,基底为半导体衬底,例如硅/氧化硅衬底。以去离子水、丙酮、无水乙醇、去离子水的顺序,在100w的功率下各对基底超声清洗五分钟,可获得供后续操作的基底。

37.s20,在所述基底(s10)上形成栅电极层。

38.在本发明的一个实施例中,通过在所述基底(s10)表面进行匀胶、光刻、烘干、曝光和显影处理,获得图案化的光刻胶,采用德国去胶机处理图形区域可能存在的残胶,利用磁控溅射工艺在基底(此时基底表面存在图案化光刻胶)上形成mo金属层,进一步采用lift-off工艺得到图案化的栅电极层。也可以采用本领域习知的其他材质/结构作为栅电极层。在本实施例中,制备的栅电极层厚度为100nm,水平长度为105μm。

39.s30,在所述栅电极层(s20)上形成栅极介电层。

40.在本实施例中,通过pecvd工艺在所述栅电极层(s20)上覆盖栅极介电层,栅极介电层材质为二氧化硅。本实施例中采用的pecvd工艺参数如下:工作压强1000mtorr,通入n2o和5%浓度的sih4的比例为710:170,功率为100w,反应温度30℃。在本实施例中,制备的栅介电层厚度为100nm。

41.s40,在所述栅极介电层(s30)上形成igzo有源层。

42.在本实施例中,通过磁控溅射工艺在所述栅极介电层(s30)上形成igzo有源层,本实施例中采用的反应条件如下:溅射压力0.5pa,通入ar和o2的比例为45:5,溅射功率为80w,溅射时长为1000s。通过在igzo有源层表面进行匀胶、光刻、烘干、曝光和显影处理,获得图案化的光刻胶,采用稀释的盐酸(~1%)刻蚀igzo有源层(此时的igzo有源层表面存在图案化光刻胶),经过去胶处理可得到图案化igzo有源层,随即进行退火处理,本实施例中的退火条件如下:温度为350℃,退火氛围为ar,退火时间为1h。在本实施例中,制备的igzo有源层厚度为20nm。

43.s50,在所述igzo有源层(s40)上形成源区电极层、漏区电极层,并通过偏移所述漏区电极层和栅电极层在水平位置上的非交叠距离形成igzo漂移区。

44.在本实施例中,在所述igzo有源层(s40)表面利用电子束蒸发工艺在igzo有源层

上覆盖al金属层,通过匀胶、光刻、烘干、曝光和显影处理,在al金属层表面获得图案化的光刻胶,采用al刻蚀液刻蚀al金属层(此时的al金属层表面存在图案化光刻胶),经过去胶处理即可在igzo有源层表面形成源区电极层和漏区电极层,两者材质皆为al,同时获得漂移区。在其他实施例中,也可以采用其他本领域习知的材质作为源区电极层/漏区电极层的材料。在本实施例中,制备的源区电极层、漏区电极厚度为100nm,源区电极层、漏区电极层之间间距为100um,源区电极层与栅电极层水平位置上存在5um交叠区,漏区电极层和栅电极层在水平方向上的非交叠区水平长度为2um,以形成igzo漂移区。

45.s60,对所述igzo漂移区进行氢离子掺杂,形成igzo低阻漂移区。

46.本实施例中,通过匀胶、光刻、烘干、曝光和显影处理在igzo有源层的局部区域获得以供氢掺杂的窗口,通过对igzo漂移区进行氢离子掺杂处理,形成igzo低阻漂移区。本实施例中采用的氢等离子处理工艺如:功率为100w,腔室压强为1200mtorr,氢流量为170sccm,处理温度为30℃,处理时间为200s。

47.本技术还提供了一种带有漂移区的igzo薄膜晶体管作为对比例2,如图2所示,igzo薄膜晶体管包括基底210、栅电极层220、栅极介电层230、igzo有源层240、igzo漂移区240b、源区电极层250以及漏区电极层252。需要指出的是,各膜层在图2中的尺寸只是一个示意,并不代表其实际尺寸。

48.在图2所示的对比例中:

49.所述栅电极层220设于所述基底210之上,材质为mo金属膜层。

50.所述栅极介电层230形成于所述栅电极层220之上并完全覆盖所述栅电极层220,材质为氧化硅。

51.所述igzo有源层240形成于所述栅介电层230之上。

52.所述源区电极层250和漏区电极层间隔的设于所述igzo有源层240表面相对两侧,源区电极层250和漏区电极层252同为al金属膜层,源区电极层250和栅电极层220在水平方向上存在5um交叠区,漏区电极层252和栅电极层220在水平方向上存在2um非交叠区。

53.所述igzo漂移区240b形成于所述栅电极层220和漏区电极层252在水平方向上非交叠区内的igzo有源层240内。

54.在图2所示的实施例中,所述栅电极层220的厚度为100nm,长度为105μm,所述栅极介电层230厚度为100nm,所述源区电极层250和漏区电极层252的厚度同为100nm,所述igzo有源层240的厚度为20nm,所述源区电极层250和漏区电极层252水平方向上的距离240a为100μm,所述igzo漂移区240b长度为2μm。

55.图5是本技术实施例与对比例1和对比例2的击穿电曲线图,其中对比例为1为传统结构igzo薄膜晶体管和对比例2为带有漂移区的igzo薄膜晶体管。图5纵坐标为漏区电极层电流的数值大小,横坐标为所施加的漏区电极层电压大小。可以看出,对比例1的击穿电压约为78v,而本实施例和对比例2的击穿电压一致,约为256v,相较于对比例1而言耐压能力显著提升。图6是本技术实施例与对比例1和2的电流曲线图。图6纵坐标为漏区电极层电流的数值大小,横坐标为所施加的栅电极层电压大小。可以看出,相较于对比例1,对比例2电流显著降低,牺牲了igzo薄膜晶体管的导通电阻;而本实施例相较于对比例1传统igzo薄膜晶体管,在提升晶体管耐压的同时,明显降低了电流能力的损失。在栅电极层电压大于5v时,本实施例和对比例1的电流相比,降低幅度在一个数量级之内,而本实施例的电流与对

比例2相比提升了4个数量级,降低电流能力损失的成效显著。

56.以上所述实施例仅表达了本发明的几种实施方式,其描述较为具体和详细,但并不能因此而理解为对发明专利范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本发明构思的前提下,还可以做出若干变形和改进,这些都属于本发明的保护范围。因此,本发明专利的保护范围应以所附权利要求为准。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。