1.本发明涉及一种显示装置及其驱动方法。

背景技术:

2.随着信息化技术的发展,作为用户与信息之间的连接介质的显示装置的重要性正在增加。响应于此,诸如液晶显示装置(liquid crystal display device)、有机发光显示装置(organic light emitting display device)等的显示装置的使用正在增加。

3.显示装置可以包括用于显示图像的显示部和用于感测触摸位置的传感器部。通常,传感器部可以在平面上与显示部重叠而布置。据此,在传感器部的传感器与显示部的像素之间可能存在无意的寄生电容。

4.此时,由于寄生电容,传感器部的感测信号及显示部的显示信号可能彼此干扰,因此存在无法容易改变感测信号及显示信号的时序的问题。

技术实现要素:

5.期望解决的技术问题在于提供一种能够利用现有的控制信号来最小化干扰的同时改变感测信号及显示信号的时序的显示装置及其驱动方法。

6.根据本发明的一实施例的一种显示装置包括:像素;数据驱动部,在水平时段中的第一时间点开始输出针对所述像素中的至少一部分的数据电压,并在所述水平时段中的第二时间点结束所述数据电压的输出;传感器;以及传感器驱动部,在所述水平时段中与所述第一时间点及所述第二时间点不同的第三时间点改变针对所述传感器中的至少一部分的感测信号的逻辑电平,其中,所述第一时间点、所述第二时间点及所述第三时间点中的至少一个根据在水平同步信号保持在特定逻辑电平的期间的垂直同步信号的逻辑电平改变次数而变化。

7.所述水平时段可以是从所述水平同步信号从第一逻辑电平改变为第二逻辑电平的时间点到所述水平同步信号从所述第一逻辑电平改变为所述第二逻辑电平的下一个时间点为止,所述水平同步信号的所述特定逻辑电平可以是所述第二逻辑电平。

8.在所述水平时段内,在所述水平同步信号保持所述第二逻辑电平的期间,所述垂直同步信号可以从第三逻辑电平改变为第四逻辑电平至少一次,在所述水平时段内,在所述垂直同步信号保持所述第四逻辑电平的时段可以比所述水平同步信号保持所述第二逻辑电平的时段短。

9.在所述水平时段内,在所述水平同步信号保持所述第一逻辑电平的期间,所述垂直同步信号可以保持所述第三逻辑电平。

10.所述显示装置还可以包括:扫描驱动部,在所述水平时段中的从第四时间点到第五时间点为止输出针对所述像素中的至少一部分的导通电平的扫描信号,其中,可以从所述第二时间点到所述第五时间点为止保持所述感测信号的逻辑电平。

11.当所述逻辑电平改变次数为n次时的所述数据电压的输出时段与当所述逻辑电平

改变次数为m次时的所述数据电压的输出时段可以以所述水平时段为基准长度彼此相同且相位彼此不同,所述n及所述m可以是彼此不同的正整数。

12.当所述逻辑电平改变次数为所述n次时的所述感测信号的电平保持时段与当所述逻辑电平改变次数为所述m次时的所述感测信号的电平保持时段可以以所述水平时段为基准长度彼此相同且相位彼此不同。

13.当所述逻辑电平改变次数为n次时的所述数据电压的输出时段与当所述逻辑电平改变次数为m次时的所述数据电压的输出时段可以以所述水平时段为基准长度彼此不同,所述n及所述m可以是彼此不同的正整数。

14.当所述逻辑电平改变次数为所述n次时的所述感测信号的电平保持时段与当所述逻辑电平改变次数为所述m次时的所述感测信号的电平保持时段可以以所述水平时段为基准长度彼此不同。

15.所述垂直同步信号可以具有第三逻辑电平或第四逻辑电平,帧时段可以以所述水平同步信号为所述第一逻辑电平且所述垂直同步信号为所述第四逻辑电平时为基准而改变。

16.根据本发明的一实施例的一种显示装置的驱动方法包括如下步骤:数据驱动部在水平时段中的第一时间点开始输出针对所述像素中的至少一部分的数据电压,并在所述水平时段中的第二时间点结束所述数据电压的输出;以及传感器驱动部在所述水平时段中与所述第一时间点及所述第二时间点不同的第三时间点改变针对所述传感器中的至少一部分的感测信号的逻辑电平,其中,所述第一时间点、所述第二时间点及所述第三时间点中的至少一个根据在水平同步信号保持在特定逻辑电平的期间的垂直同步信号的逻辑电平改变次数而变化。

17.所述水平时段可以是从所述水平同步信号从第一逻辑电平改变为第二逻辑电平的时间点到所述水平同步信号从所述第一逻辑电平改变为所述第二逻辑电平的下一个时间点为止,所述水平同步信号的所述特定逻辑电平可以是所述第二逻辑电平。

18.在所述水平时段内,在所述水平同步信号保持所述第二逻辑电平的期间,所述垂直同步信号可以从第三逻辑电平改变为第四逻辑电平至少一次,在所述水平时段内,在所述垂直同步信号保持所述第四逻辑电平的时段可以比所述水平同步信号保持所述第二逻辑电平的时段短。

19.在所述水平时段内,在所述水平同步信号保持所述第一逻辑电平的期间,所述垂直同步信号可以保持所述第三逻辑电平。

20.所述驱动方法还可以包括如下步骤:在所述水平时段中的从第四时间点到第五时间点为止输出针对所述像素中的至少一部分的导通电平的扫描信号,其中,可以从所述第二时间点到所述第五时间点为止保持所述感测信号的逻辑电平。

21.当所述逻辑电平改变次数为n次时的所述数据电压的输出时段与当所述逻辑电平改变次数为m次时的所述数据电压的输出时段可以以所述水平时段为基准长度彼此相同且相位彼此不同,所述n及所述m可以是彼此不同的正整数。

22.当所述逻辑电平改变次数为所述n次时的所述感测信号的电平保持时段与当所述逻辑电平改变次数为所述m次时的所述感测信号的电平保持时段可以以所述水平时段为基准长度彼此相同且相位彼此不同。

23.当所述逻辑电平改变次数为n次时的所述数据电压的输出时段与当所述逻辑电平改变次数为m次时的所述数据电压的输出时段可以以所述水平时段为基准长度彼此不同,所述n及所述m可以是彼此不同的正整数。

24.当所述逻辑电平改变次数为所述n次时的所述感测信号的电平保持时段与当所述逻辑电平改变次数为所述m次时的所述感测信号的电平保持时段可以以所述水平时段为基准长度彼此不同。

25.所述垂直同步信号可以具有第三逻辑电平或第四逻辑电平,帧时段可以以所述水平同步信号为所述第一逻辑电平且所述垂直同步信号为所述第四逻辑电平时为基准而改变。

26.根据本发明的显示装置及其驱动方法可以利用现有的控制信号来最小化干扰的同时改变感测信号及显示信号的时序。

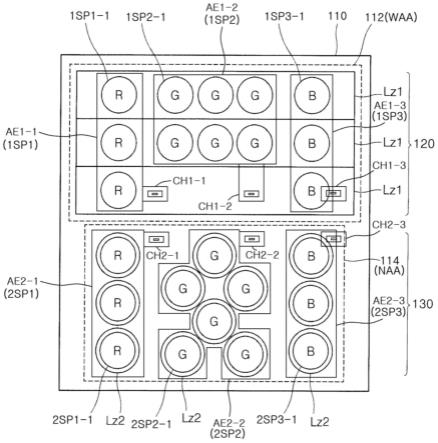

附图说明

27.图1是用于说明根据本发明的一实施例的显示装置的图。

28.图2是用于说明图1的显示装置的示例性的堆叠结构的图。

29.图3是用于说明根据本发明的一实施例的第一传感器及第二传感器的图。

30.图4及图5是用于说明根据本发明的一实施例的互感时段的图。

31.图6至图8是用于说明根据本发明的一实施例的第一自感时段及第二自感时段的图。

32.图9是用于说明根据本发明的一实施例的显示部及显示驱动部的图。

33.图10是用于说明根据本发明的一实施例的像素的图。

34.图11是用于说明根据本发明的一实施例的帧时段的图。

35.图12至图14是用于说明根据本发明的一实施例的水平时段的图。

36.图15是用于说明根据本发明的一实施例的显示装置的驱动方法的图。

37.图16及图17是用于说明根据本发明的另一实施例的水平时段的示图。

38.图18至图24是用于说明显示装置的示例性的构成的图。

39.图25至图27是用于说明根据本发明的另一实施例的包括像素的显示装置的图。

具体实施方式

40.以下,参照附图对本发明的若干实施例进行详细说明,以使本发明所属技术领域中具有普通知识的人员能够容易地实施。本发明能够以多种不同的形态实现,且不限于在此说明的实施例。

41.为了明确地说明本发明,省略了与说明无关的部分,在整个说明书中,对相同或类似的构成要素赋予相同的附图标记。因此,前面说明的附图标记也可以在其他附图中使用。

42.并且,为了便于说明,任意示出了附图中示出的各构成的大小及厚度,因此本发明并非必须限定于所图示的内容。在附图中,为了明确地表示多个层及区域,可以夸张地表示厚度。

43.并且,在说明中,表述“相同”可以意味着“实质上相同”。即,可以是具有普通知识的人员能够理解为相同的程度的相同。此外的表述也可以是省略了“实质上”的表述。

44.图1是用于说明根据本发明的一实施例的显示装置的图。

45.参照图1,根据本发明的一实施例的显示装置1可以包括面板10及用于驱动面板10的驱动电路部20。

46.例如,面板10可以包括用于显示图像的显示部110及用于感测触摸、压力、指纹、悬停(hovering)等的传感器部120。例如,面板10可以包括像素px及与像素px中的至少一部分重叠而布置的传感器sc。在一实施例中,传感器sc可以包括第一传感器tx及第二传感器rx。在另一实施例(例如,自电容方式)中,传感器sc可以利用一种类型的传感器构成,而不区分第一传感器及第二传感器。驱动电路部20可以包括用于驱动显示部110的显示驱动部210及用于驱动传感器部120的传感器驱动部220。例如,像素px可以以显示帧时段为单位显示图像。例如,传感器sc可以以比显示帧时段短的感测帧时段为单位感测用户的输入。

47.根据实施例,显示部110及传感器部120可以在彼此单独地制造之后以至少一区域彼此重叠的方式布置和/或结合。或者,在另一实施例中,显示部110及传感器部120可以制造成一体。例如,传感器部120可以直接形成在构成显示部110的至少一个基板(作为一示例,显示面板的上部基板和/或下部基板或者薄膜封装层(thin film encapsulation))上或者除此之外的其他绝缘层或各种功能膜(作为一示例,光学层或保护层)上。

48.另外,图1示出了传感器部120布置于显示部110的前面(例如,显示图像的上部面)侧的情形,但是传感器部120的位置不限于此。例如,在另一实施例中,传感器部120也可以布置于显示部110的背面或双面。在又一实施例中,传感器部120也可以布置于显示部110的至少一侧的边缘区域。

49.显示部110可以包括显示基板111及形成于显示基板111的多个像素px。像素px可以布置于显示基板111的显示区域da。

50.显示基板111可以包括显示图像的显示区域da和显示区域da外围的非显示区域nda。根据实施例,显示区域da可以布置于显示部110的中心区域,非显示区域nda可以以围绕显示区域da的方式布置于显示部110的边缘区域。

51.显示基板111可以是刚性基板或柔性基板,其材料或物性不受特别的限制。例如,显示基板111可以是利用玻璃或钢化玻璃构成的刚性基板或利用塑料或金属材质的薄膜构成的柔性基板。

52.在显示区域da布置有扫描线sl和数据线dl以及连接到扫描线sl和数据线dl的像素px。像素px借由从扫描线sl供应的导通电平的扫描信号而被选择,并从数据线dl接收数据信号,并发出对应于数据信号的亮度的光。由此,在显示区域da中显示出对应于数据信号的图像。在本发明中,像素px的结构及驱动方法等不受特别的限制。例如,像素px中的每一个可以体现为目前公知的多样的结构和/或驱动方法的像素。

53.在非显示区域nda可以布置有连接到显示区域da的像素px的各种布线和/或内置电路部。作为一示例,在非显示区域nda可以布置有用于向显示区域da供应各种电源及控制信号的多条布线,除此之外,还可以布置有扫描驱动部(scan driver)等。

54.在本发明中,显示部110的类型不受特别的限制。例如,显示部110可以实现为诸如有机发光显示面板(organic light emitting display panel)等的自发光型的显示面板。然而,当显示部110实现为自发光型时,各个像素并非一定限于仅包括有机发光元件的情况。例如,各个像素的发光元件可以利用有机发光元件(organic light emitting diode)、

无机发光元件(inorganic light emitting diode)、量子点/阱发光元件(quantum dot/well light emitting diode)等构成。在各个像素也可以配备有多个发光元件。此时,多个发光元件可以以串联、并联、串并联等方式连接。或者,显示部110可以实现为诸如液晶显示面板(liquid crystal display panel)等的非发光型的显示面板。在显示部110实现为非发光型的情况下,显示装置1可以进一步配备有诸如背光单元(back-light unit)之类的光源。

55.传感器部120包括传感器基板121及形成于传感器基板121上的多个传感器sc。传感器sc可以布置于传感器基板121上的感测区域sa。

56.传感器基板121可以包括可感测触摸输入等的感测区域sa和感测区域sa的外围的周围区域nsa。根据实施例,感测区域sa可以布置成与显示区域da的至少一区域重叠。作为一示例,感测区域sa可以设定为对应于显示区域da的区域(例如,与显示区域da重叠的区域),并且周围区域nsa可以设定为对应于非显示区域nda的区域(例如,与非显示区域nda重叠的区域)。在此情况下,当在显示区域da上提供触摸输入等时,可以通过传感器部120检测触摸输入。

57.传感器基板121可以是刚性或柔性基板,除此之外,可以利用至少一层的绝缘膜构成。并且,传感器基板121可以是透明或半透明的透光性基板,但不限于此。即,在本发明中,传感器基板121的材料及其物性不受特别的限制。例如,传感器基板121可以是利用玻璃或钢化玻璃构成的刚性基板或利用塑料或金属材质的薄膜构成的柔性基板。并且,根据实施例,构成显示部110的至少一个基板(例如,显示基板111、封装基板及/或薄膜封装层)或布置于显示部110的内部和/或外面的至少一层绝缘膜或功能膜等也可以用作传感器基板121。

58.感测区域sa设定为可对触摸输入作出反应的区域(即,传感器的有效区域)。为此,在感测区域sa可以布置有用于感测触摸输入等的传感器sc。根据实施例,传感器sc可以包括第一传感器tx及第二传感器rx。

59.例如,各个第一传感器tx可以沿第一方向dr1延伸。第一传感器tx可以沿第二方向dr2排列。第二方向dr2可以与第一方向dr1不同。例如,第二方向dr2可以是与第一方向dr1垂直的方向。在另一实施例中,第一传感器tx的延伸方向及排列方向可以基于现有的其他构成。各个第一传感器tx可以是面积较宽的第一单元(first cells)和面积较窄的第一桥(first bridges)相连接的形态。在图1中,各个第一单元以菱形的形态示出,但也可以以圆形、四边形、三角形、网格形态(mesh form)等现有的多样的形态构成。例如,第一桥与第一单元可以在同一层上形成为一体。在另一实施例中,第一桥与第一单元可以形成于不同的层,从而电连接相邻的第一单元。

60.例如,各个第二传感器rx可以沿第二方向dr2延伸。第二传感器rx可以沿第一方向dr1排列。在另一实施例中,第二传感器rx的延伸方向及排列方向可以基于现有的其他构成。各个第二传感器rx可以是面积较宽的第二单元和面积较窄的第二桥相连接的形态。在图1中,各个第二单元以菱形的形态示出,但也可以以圆形、四边形、三角形、网格形态等现有的多样的形态构成。例如,第二桥与第二单元可以在同一层上形成为一体。在另一实施例中,第二桥与第二单元可以形成于不同的层,从而电连接相邻的第二单元。

61.根据实施例,第一传感器tx及第二传感器rx中的每一个可以通过包括金属物质、

透明导电性物质及除此之外的多样的导电性物质中的至少一种而具有导电性。作为一示例,第一传感器tx及第二传感器rx可以包括包含金(au)、银(ag)、铝(al)、钼(mo)、铬(cr)、钛(ti)、镍(ni)、钕(nd)、铜(cu)、铂(pt)等在内的多样的金属物质中的至少一种或它们的合金。此时,第一传感器tx及第二传感器rx可以利用网格形态构成。并且,第一传感器tx及第二传感器rx可以包括包含银纳米线(agnw)、铟锡氧化物(ito,indium tin oxide)、铟锌氧化物(izo,indium zinc oxide)、铟镓锌氧化物(igzo,indium gallium zinc oxide)、锑锌氧化物(azo,antimony zinc oxide)、铟锡锌氧化物(itzo,indium tin zinc oxide)、锌氧化物(zno,zinc oxide)、锡氧化物(sno2,tin oxide)、碳纳米管(carbon nano tube)、石墨烯(graphene)等在内的多样的透明导电性物质中的至少一种。除此之外,第一传感器tx及第二传感器rx也可以通过包括多样的导电性物质中的至少一种,从而具有导电性。并且,第一传感器tx及第二传感器rx中的每一个可以构成为单层或多层,并且其剖面结构不受特别的限制。

62.另外,在传感器部120的周围区域nsa可以集中地布置有用于将传感器tx、rx电连接到传感器驱动部220等的传感器线。

63.驱动电路部20可以包括用于驱动显示部110的显示驱动部210及用于驱动传感器部120的传感器驱动部220。在一实施例中,显示驱动部210及传感器驱动部220可以利用彼此单独的集成芯片(ic,integrated chips)构成。在另一实施例中,显示驱动部210及传感器驱动部220的至少一部分可以一起集成在一个ic内。

64.显示驱动部210电连接于显示部110而驱动像素px。例如,显示驱动部210可以包括数据驱动部12及时序控制部11,扫描驱动部13可以单独地安装(mount)于显示部110的非显示区域nda(参照图9)。在另一实施例中,显示驱动部210也可以包括数据驱动部12、时序控制部11及扫描驱动部13的全部或其中的至少一部分。

65.传感器驱动部220电连接于传感器部120而驱动传感器部120。传感器驱动部220可以包括传感器发送部及传感器接收部。根据实施例,传感器发送部及传感器接收部可以集成在一个ic的内部,但不限于此。

66.图2是用于说明图1的显示装置的示例性的堆叠结构的图。

67.参照图2,例如,在显示部110的上部可以堆叠有传感器部120,并且在传感器部120的上部可以堆叠有窗口win。

68.显示部110可以包括显示基板111、形成于显示基板111上的电路元件层bpl以及形成于电路元件层bpl上的发光元件ld。电路元件层bpl可以包括用于驱动像素pxl的发光元件ld的像素电路及扫描线sl、数据线dl等。

69.传感器部120可以包括传感器基板121、形成于传感器基板121上的传感器sc及覆盖传感器sc的保护膜122。在图2的实施例中,传感器基板121以覆盖像素pxl的封装膜形态示出。在另一实施例中,传感器基板121也可以独立于覆盖像素pxl的封装膜而存在。

70.窗口win是布置于显示装置1的模块最上端的保护部件,可以是实质上透明的透光性基板。这样的窗口win可以具有选自玻璃基板、塑料膜及塑料基板的多层结构。窗口win可以包括刚性或柔性的基材,并且窗口win的构成物质不受特别的限制。

71.尽管未示出,但是显示装置1还可以在窗口win与传感器部120之间包括用于防止外部光反射的偏光板(或反射防止层)。

72.图3是用于说明根据本发明的一实施例的第一传感器及第二传感器的图。

73.参照图3,示例性地示出位于感测区域sa的第一传感器tx1、tx2、tx3、tx4及第二传感器rx1、rx2、rx3、rx4。为了便于说明,假设在感测区域sa布置有4个第一传感器tx1至tx4且布置有4个第二传感器rx1至rx4。

74.对第一传感器tx1至tx4及第二传感器rx1至rx4的说明与对图1的第一传感器tx及第二传感器rx的说明相同,因此省略重复的说明。

75.图4及图5是用于说明根据本发明的一实施例的互感时段的图。

76.互感时段msp可以是传感器部120及传感器驱动部220以互电容模式(mutual capacitance mode)驱动的时段。在图7中,以任意一个传感器通道222为中心示出了传感器部120及传感器驱动部220的构成。

77.传感器驱动部220可以包括传感器接收部tsc及传感器发送部tdc。在互感时段msp中,传感器发送部tdc可以与第一传感器tx连接,且传感器接收部tsc可以与第二传感器rx连接。

78.传感器接收部tsc可以包括运算放大器amp、模数转换器224及处理器226。作为一示例,各个传感器通道222可以实现为包括至少一个运算放大器amp的模拟前端(afe:analog front end)。模数转换器224及处理器226可以针对每个传感器通道222配备,也可以被多个传感器通道222共享。

79.运算放大器amp的第一输入端子in1可以与对应的第二传感器连接,且第二输入端子in2可以与基准电源gnd连接。例如,第一输入端子in1可以是反相端子,并且第二输入端子in2可以是非反相端子。基准电源gnd可以是接地电压或特定大小的电压。

80.模数转换器224可以与运算放大器amp的输出端子out1连接。电容器ca与开关swr可以并联连接在第一输入端子in1与输出端子out1之间。

81.参照图5,在互感时段msp期间,传感器驱动部220(例如,传感器发送部tdc)可以向第一传感器tx1至tx4依序供应第一转换信号。即,第一传感器tx1至tx4的感测信号可以包括第一转换信号。例如,可以将第一转换信号供应到第一传感器tx1两次(t1b、t2b),将第一转换信号供应到第一传感器tx2两次(t3b、t4b),将第一转换信号供应到第一传感器tx3两次(t5b、t6b),且将第一转换信号供应到第一传感器tx4两次(t7b、t8b)。根据实施例,向各个第一传感器tx1至tx4供应第一转换信号的次数也可以多于两次。

82.各个第一转换信号可以对应于上升转换(rising transition)和/或下降转换(falling transition)。例如,时间点t1b的第一转换信号可以对应于上升转换。即,在时间点t1b,第一转换信号可以从低电平上升到高电平。时间点t2b的第一转换信号可以对应于下降转换。即,在时间点t2b,第一转换信号可以从高电平下降到低电平。

83.传感器接收部tsc可以包括连接到多个第二传感器rx的多个传感器通道222。各个传感器通道222可以从对应的第二传感器rx接收对应于第一转换信号的第一采样信号。例如,对应于在时间点t1b施加到第一传感器tx1的第一转换信号,连接到第二传感器rx1至rx4的传感器通道222可以独立地接收第一采样信号。并且,对应于在时间点t2b施加到第一传感器tx1的第一转换信号,连接到第二传感器rx1至rx4的传感器通道222可以独立地接收第一采样信号。

84.在感测区域sa中,第一传感器tx1至tx4与第二传感器rx1至rx4之间的互电容可以

根据用户手指等的对象obj的位置而彼此不同,据此传感器通道222所接收的第一采样信号也可以彼此不同。可以利用这样的第一采样信号的差异来检测出对象obj的触摸位置。

85.传感器通道222可以产生对应于第一输入端子in1与第二输入端子in2之间的电压差的输出信号。例如,传感器通道222可以将第一输入端子in1与第二输入端子in2之间的差电压放大为对应于预定的增益(gain)的程度并输出。

86.根据实施例,传感器通道222可以体现为积分器。在此情况下,电容器ca和开关swr可以彼此并联地连接在运算放大器amp的第一输入端子in1与输出端子out1之间。例如,可以通过在接收第一采样信号之前导通开关swr来初始化电容器ca的电荷。在接收第一采样信号的时间点,开关swr可以处于断开状态。

87.模数转换器224将从各个传感器通道222输入的模拟信号转换为数字信号。处理器226可以分析这样的数字信号来检测出用户输入。

88.图6至图8是用于说明根据本发明的一实施例的第一自感时段及第二自感时段的图。

89.在图6中以任意一个传感器通道222为中心示出了传感器部120及传感器驱动部220的构成。传感器接收部tsc及传感器发送部tdc的内部构成可以与图3的情况实质上相同。省略对此的重复说明,以下以不同之处为主进行说明。

90.参照图7,第一自感时段stp可以是传感器部120及传感器驱动部220以自电容模式(self-capacitance mode)驱动的时段。在第一自感时段stp中,在各个传感器通道222的第二输入端子in2可以连接有传感器发送部tdc,在各个传感器通道222的第一输入端子in1可以连接有对应的第一传感器。在另一实施例中,传感器发送部tdc也可以连接到第一输入端子in1。此时,第二输入端子in2可以被施加基准电压或接地电压。

91.例如,在第一自感时段stp期间,传感器发送部tdc可以向各个传感器通道222的第二输入端子in2供应第二转换信号。此时,根据运算放大器amp的特性,连接到第一输入端子in1的第一传感器可以被供应第二转换信号。即,第一传感器tx1至tx4的感测信号可以包括第二转换信号。在一实施例中,传感器驱动部220可以在第一自感时段stp期间向第一传感器tx1至tx4同时供应第二转换信号。例如,参照图7,在各个时间点t1c、t2c、t3c、t4c、t5c、t6c、t7c、t8c,第二转换信号可以同时被供应到第一传感器tx1至tx4。此时,第二传感器rx1至rx4可以接收单独的基准电压,或者可以处于浮置状态。各个第二转换信号可以对应于上升转换和/或下降转换。

92.第一传感器tx1至tx4可以具有自电容。此时,在用户手指等的对象obj接近第一传感器tx1至tx4的情况下,第一传感器tx1至tx4的自电容可以根据其与对象表面oe形成的电容而变化。反映这样的自电容的第二转换信号可以称为第二采样信号。可以利用第一传感器tx1至tx4的第二采样信号之差来检测出相对于第二方向dr2的对象obj的触摸位置(参照图3)。

93.参照图8,第二自感时段srp可以是传感器部120及传感器驱动部220以自电容模式驱动的时段。在第二自感时段srp中,在各个传感器通道222的第二输入端子in2可以连接有传感器发送部tdc,并且在各个传感器通道222的第一输入端子in1可以连接有对应的第二传感器。

94.例如,在第二自感时段srp期间,传感器发送部tdc可以向各个传感器通道222的第

二输入端子in2供应第三转换信号。此时,根据运算放大器amp的特性,连接到第一输入端子in1的第二传感器可以被供应第三转换信号。即,第一传感器tx1至tx4的感测信号可以包括第三转换信号。在一实施例中,传感器驱动部220可以在第二自感时段srp期间向第二传感器rx1至rx4同时供应第三转换信号。例如,参照图8,在各个时间点t1d、t2d、t3d、t4d、t5d、t6d、t7d、t8d,第三转换信号可以同时被供应到第二传感器rx1至rx4。此时,第一传感器tx1至tx4可以接收单独的基准电压,或者可以处于浮置状态。各个第三转换信号可以对应于上升转换或下降转换。

95.第二传感器rx1至rx4可以具有自电容。此时,在用户手指等的对象obj接近第二传感器rx1至rx4的情况下,第二传感器rx1至rx4的自电容可以根据其与对象表面oe形成的电容而变化。反映这样的自电容的第三转换信号可以称为第三采样信号。可以利用第二传感器rx1至rx4的第三采样信号之差来检测出相对于第一方向dr1的对象obj的触摸位置(参照图3)。

96.图9是用于说明根据本发明的一实施例的显示部及显示驱动部的图。

97.参照图9,显示驱动部210可以包括数据驱动部12及时序控制部11,显示部110可以包括扫描驱动部13。但是,如上所述,各个功能部可以根据显示装置1的规格(specification)而多样地构成。即,可以集成于一个ic,也可以集成于多个ic,或者也可以安装于显示基板111。

98.时序控制部11可以从处理器9接收针对各个帧时段(frame period)的灰度及控制信号。在此,处理器可以对应于图形处理单元(gpu:graphics processing unit)、中央处理单元(cpu:central processing unit)、应用处理器(ap:application processor)等中的至少一个。控制信号可以包括垂直同步信号(vertical synchronization signal)、水平同步信号(horizontal synchronization signal)、数据使能信号(data enable signal)等。数据使能信号可以在从处理器供应灰阶的期间处于使能电平(例如,逻辑高电平),并可以在不供应灰阶的期间处于禁用电平(例如,逻辑低电平)。将参照图11对垂直同步信号及水平同步信号进行后述。

99.时序控制部11可以与显示装置1的规格对应地渲染(rendering)灰度。例如,处理器9可以针对各个单位点(unit dot)提供红色灰度、绿色灰度、蓝色灰度。例如,在像素部14为rgb条纹(stripe)结构的情况下,像素可以一对一地对应于各个灰度。在这种情况下,可能不需要渲染灰度。但是,例如,在像素部14为五片瓦(pentile)结构的情况下,由于相邻的单位点之间共享像素,因此像素可能不一对一地对应于各个灰度。在这种情况下,可能需要渲染灰度。被渲染或未被渲染的灰度可以提供到数据驱动部12。并且,时序控制部11可以向数据驱动部12提供数据控制信号。并且,时序控制部11可以向扫描驱动部13提供扫描控制信号。

100.数据驱动部12可以利用从时序控制部11接收的灰度及数据控制信号来生成要提供给数据线dl1、dl2、dl3、dl4的数据电压。

101.扫描驱动部13可以利用从时序控制部11接收的时钟信号、扫描开始信号等来生成要提供给扫描线sl1、sl2的扫描信号。扫描驱动部13可以向扫描线sl1、sl2依次供应具有导通电平的脉冲的扫描信号。例如,扫描驱动部13在被供应灰度的有效时段(active period)中,可以以与水平同步信号的周期(cycle)对应的周期向扫描线供应导通电平的扫描信号。

扫描驱动部13可以包括以移位寄存器(shift register)形态构成的扫描级。扫描驱动部13可以根据时钟信号的控制,以将作为导通电平的脉冲形态的扫描开始信号依次传递给下一个扫描级的方式生成扫描信号。

102.像素部14包括像素。各个像素可以连接到对应的数据线及扫描线。例如,像素pxij可以连接到第i条扫描线及第j条数据线。像素可以包括发出第一颜色的光的像素、发出第二颜色的光的像素以及发出第三颜色的光的像素。第一颜色、第二颜色及第三颜色可以是彼此不同的颜色。例如,第一颜色可以是红色、绿色及蓝色中的一种颜色,第二颜色可以是红色、绿色及蓝色中的不是第一颜色的一种颜色,第三颜色可以是红色、绿色及蓝色中的不是第一颜色及第二颜色的剩余颜色。并且,作为第一颜色至第三颜色,也可以使用品红色(magenta)、青色(cyan)及黄色(yellow)来代替红色、绿色及蓝色。

103.图10是用于说明根据本发明的一实施例的像素的图。

104.参照图10,示出了示例性的像素pxij。其他像素也可以具有实质上相同的构成,因此省略重复的说明。

105.晶体管t1的栅极电极可以连接到存储电容器cst的第二电极,晶体管t1的第一电极可以连接到第一电源线elvddl,并且晶体管t1的第二电极可以连接到发光元件ld的阳极。晶体管t1可以命名为驱动晶体管。

106.晶体管t2的栅极电极可以连接到第i条扫描线sli,晶体管t2的第一电极可以连接到第j条数据线dlj,并且晶体管t2的第二电极可以连接到存储电容器cst的第二电极。晶体管t2可以命名为扫描晶体管。

107.存储电容器cst的第一电极可以连接到第一电源线elvddl,并且第二电极可以连接到晶体管t1的栅极电极。

108.发光元件ld的阳极可以连接到晶体管t1的第二电极,并且阴极可以连接到第二电源线elvssl。发光元件ld可以是发光二极管。如上所述,各个像素的发光元件可以利用有机发光元件、无机发光元件、量子点/阱发光元件等构成。并且,在各个像素也可以配备有多个发光元件。此时,多个发光元件可以以串联、并联、串并联等方式连接。在发光元件ld的发光时段期间,施加到第一电源线elvddl的第一电源电压可以大于施加到第二电源线elvssl的第二电源电压。

109.在此,晶体管t1、t2被示出为p型晶体管,但是本领域技术人员也可以通过反转信号的极性来用n型晶体管代替至少一个晶体管而使用。

110.当导通电平的扫描信号施加到第i条扫描线sli时,晶体管t2可以导通。此时,在第j条数据线dlj充电的数据电压可以存储于存储电容器cst。晶体管t1可以对应于借助存储电容器cst来保持的栅极-源极电压差而使驱动电流流动。驱动电流可以以第一电源线elvddl、晶体管t1、发光元件ld及第二电源线elvssl的路径流动。发光元件ld可以以对应于驱动电流量的亮度而发光。

111.图11是用于说明根据本发明的一实施例的帧时段的图。

112.参照图11,示例性地示出了连续的帧时段fp1、fp2、fp3。各个帧时段fp1、fp2、fp3可以包括第一时段sp1及第二时段sp2。第一时段sp1可以是从处理器9供应对应于一帧的灰度的时段(例如,有效时段)。第二时段sp2是未从处理器9供应灰度的时段(例如,空白时段(blank period)),可以对应于当前帧与下一帧之间的过渡时段。

113.在图11中,在帧时段fp1、fp2、fp3中,在第一时段sp1之后设置第二时段sp2。但是,在另一实施例中,各个帧时段fp1、fp2、fp3也可以定义为在第二时段sp2之后设置第一时段sp1。另外,在又一实施例中,各个帧时段fp1、fp2、fp3也可以定义为在第二时段sp2的后半部之后设置第一时段sp1,并且在第一时段sp1之后设置下一个第二时段sp2的前半部。

114.水平同步信号hsync可以具有第一逻辑电平lv1或第二逻辑电平lv2。垂直同步信号vsync可以具有第三逻辑电平lv3或第四逻辑电平lv4。在附图中,第一逻辑电平lv1及第三逻辑电平lv3示出为逻辑低电平(logic low level),第二逻辑电平lv2及第四逻辑电平lv4示出为逻辑高电平(logic high level)。但是,在另一实施例中,各个逻辑电平lv1、lv2、lv3、lv4也可以被不同地定义。

115.可以通过垂直同步信号vsync及水平同步信号hsync的逻辑电平来区分第一时段sp1及第二时段sp2。例如,在第二时段sp2中,水平同步信号hsync可以是第一逻辑电平lv1,并且垂直同步信号vsync可以是第四逻辑电平lv4。即,帧时段可以以水平同步信号hsync为第一逻辑电平lv1且垂直同步信号vsync为第四逻辑电平lv4时为基准而改变。在第二时段sp2中,垂直同步信号vysnc及水平同步信号hsync的逻辑电平可以保持不变。第二时段sp2的长度可以比第一时段sp1短。第二时段sp2的长度可以比第一时段sp1中的水平同步信号hsync的一周期(one cycle)长。

116.在第一时段sp1中,水平同步信号hsync的逻辑电平可以改变。例如,水平同步信号hsync的逻辑电平可以以预定的周期改变。水平同步信号hsync的一周期(one cycle)可以对应于一水平时段(one horizontal period)。

117.在第一时段sp1中,垂直同步信号vsync的逻辑电平可以改变,也可以不改变。例如,在第一帧时段fp1的第一时段sp1中,垂直同步信号vsync的逻辑电平可以不改变且保持。在垂直同步信号vsync的逻辑电平在第一时段sp1中不改变的情况下,垂直同步信号vsync可以保持第三逻辑电平lv3。

118.例如,在第二帧时段fp2的第一时段sp1中,垂直同步信号vysnc的逻辑电平可以改变。在垂直同步信号vsync的逻辑电平在第一时段sp1中改变的情况下,垂直同步信号vsync的逻辑电平可以在第一时段sp1中的第三时段sp3改变。此时,第三时段sp3可以对应于水平同步信号hsync为第二逻辑电平lv2的时段。

119.第三时段sp3可以是指示显示装置1的当前模式的时段。例如,在显示装置1的模式改变的情况下,如图11的实施例所示,可以在第一时段sp1中插入第三时段sp3。另外,与图11的实施例不同,也可以在每一水平时段存在第三时段sp3。在这种情况下,即使显示装置1的模式不改变,也可以在每一水平时段连续地提供当前模式信息。以下,参照图12至图14对包括第三时段sp3的一个水平时段进行说明。

120.图12至图14是用于说明根据本发明的一实施例的水平时段的图。

121.在图12至图14中示例性地示出了连接到像素pxij的第i条扫描线sli及第j条数据线dlj的信号。并且,示例性地示出了第k个第一传感器txk的信号。图12至图14中的水平时段1h可以包括连接到第i条扫描线sli的像素(第i个像素行)的数据写入时段(即,数据电压存储时段)。

122.如上所述,处理器9可以将垂直同步信号vsync及水平同步信号hsync提供到时序控制部11(或者,显示驱动部210)。另外,传感器驱动部220可以接收垂直同步信号vsync及

水平同步信号hsync。传感器驱动部220可以从处理器9直接接收垂直同步信号vsync及水平同步信号hsync,或者也可以从时序控制部11(或者,显示驱动器210)接收垂直同步信号vsync及水平同步信号hsync。

123.水平时段1h可以是从水平同步信号hsync由第一逻辑电平lv1改变为第二逻辑电平lv2的时间点t1e到水平同步信号hsync由第一逻辑电平lv1改变为第二逻辑电平lv2的下一个时间点t8e为止。

124.在水平时段1h内,在水平同步信号hsync保持第二逻辑电平lv2的期间,垂直同步信号vsync可以从第三逻辑电平lv3改变为第四逻辑电平lv4至少一次。在水平时段1h内,垂直同步信号vsync保持第四逻辑电平lv4的时段可以比水平同步信号hsync保持第二逻辑电平lv2的时段sp3短。在水平时段1h内,在水平同步信号hsync保持第一逻辑电平lv1的期间,垂直同步信号vsync可以保持第三逻辑电平lv3。

125.参照图12,示例性地示出了显示装置1以第一模式驱动的情况。例如,在第一模式中的第三时段sp3期间,垂直同步信号vsync的逻辑电平改变次数可以为4次(2次上升转换及2次下降转换)。由于显示驱动部210及传感器驱动部220处于接收垂直同步信号vsync及水平同步信号hsync的状态,因此可知当前水平时段1h的模式为第一模式。

126.在第一模式中,数据驱动部12(或者,显示驱动部210)可以在水平时段1h中的第一时间点t1e开始输出针对像素pxij中的至少一部分(例如,第i个像素行)的数据电压dataij、

……

,并在水平时段1h的第二时间点t6e结束数据电压dataij、

……

的输出。例如,数据驱动部12可以在时段t1e至t6e期间向第j条数据线dlj输出数据电压dataij。

127.在第一模式中,传感器驱动部220(或者,传感器发送部tdc)可以在水平时段1h中的与第一时间点t1e及第二时间点t6e不同的第三时间点t2e改变针对传感器中的至少一部分传感器txk的感测信号的逻辑电平。例如,传感器驱动部220可以在第三时间点t2e向第k个第一传感器txk供应上升转换信号。在一水平时段1h中,第三时间点可以是一个以上。例如,传感器驱动部220可以在第三时间点t5e向第k个第一传感器txk供应下降转换信号。

128.数据电压dataij改变的第一时间点t1e可以对应于传感器脆弱时段wp1。如上所述,在传感器txk与像素pxij之间可能存在无意的寄生电容,并且在第一时间点t1e,数据电压dataij的改变可能作为感测噪声而作用于传感器部120。因此,优选地,传感器驱动部220优选避开传感器脆弱时段wp1而进行感测。

129.并且,在数据电压dataij的供应结束且数据线dlj浮置的状态下,扫描晶体管t2导通的时段t6e-t7e可以对应于显示脆弱时段wp2。在显示脆弱时段wp2中进行感测信号的转换的情况下,可能将错误的数据电压被写入像素pxij。因此,优选地,传感器驱动部220避开显示脆弱时段wp2而进行感测。

130.根据一实施例,在水平时段1h中的第四时间点t4e至第五时间点t7e为止,扫描驱动部13可以输出针对像素中的至少一部分像素pxij的导通电平的扫描信号。此时,可以从第二时间点t6e至第五时间点t7e为止保持感测信号的逻辑电平(逻辑低电平)。

131.参照图13,示例性地示出了显示装置1以第二模式驱动的情况。例如,在第二模式下的第三时段sp3期间,垂直同步信号vsync的逻辑电平改变次数可以为6次(3次上升转换及3次下降转换)。由于显示驱动部210及传感器驱动部220处于接收垂直同步信号vsync及水平同步信号hsync的状态,因此可知当前水平时段1h的模式为第二模式。

132.在第二模式中,数据驱动部12(或者,显示驱动部210)可以在水平时段1h中的第一时间点t1.1e开始输出针对像素pxij中的至少一部分(例如,第i个像素行)的数据电压dataij、

……

,并在水平时段1h中的第二时间点t6.1e结束数据电压dataij、

……

的输出。例如,数据驱动部12可以在时段t1.1e至t6.1e期间向第j条数据线dlj输出数据电压dataij。

133.在第二模式中,传感器驱动部220(或者,传感器发送部tdc)可以在水平时段1h中的与第一时间点t1.1e及第二时间点t6.1e不同的第三时间点t5.1e改变针对传感器中的至少一部分传感器txk的感测信号的逻辑电平。例如,传感器驱动部220可以在第三时间点t5.1e向第k个第一传感器txk供应上升转换信号。在一水平时段1h中,第三时间点可以是一个以上。例如,传感器驱动部220可以在第三时间点t7.1e向第k个第一传感器txk供应下降转换信号。

134.根据一实施例,在水平时段1h中的第四时间点t4e至第五时间点t7e为止,扫描驱动部13可以输出针对像素中的至少一部分像素pxij的导通电平的扫描信号。此时,可以从第二时间点t6.1e至第五时间点t7e为止保持感测信号的逻辑电平(逻辑高电平)。

135.参照图12及图13,当逻辑电平改变次数为n次(例如,4次)时的数据电压的输出时段t1e至t6e与当逻辑电平改变次数为m次(例如,6次)时的数据电压的输出时段t1.1e至t6.1e可以以水平时段1h为基准而长度彼此相同且相位彼此不同。此时,n及m可以是彼此不同的正整数。因此,在图12的第一模式及图13的第二模式中,传感器脆弱时段wp1及显示脆弱时段wp2可以变得不同。

136.根据一实施例,当逻辑电平改变次数为n次时的感测信号的电平保持时段t2e至t5e与当逻辑电平改变次数为m次时的感测信号的电平保持时段t5.1e至t7.1e可以以水平时段1h为基准而长度彼此相同且相位彼此不同。

137.根据本实施例,第一时间点、第二时间点及第三时间点中的至少一个可以根据在水平同步信号hsync保持在特定逻辑电平(例如,第二逻辑电平lv2)的期间的垂直同步信号vsync的逻辑电平改变次数而变化。因此,对应于按模式而变化的传感器脆弱时段wp1及显示脆弱时段wp2,可以供应数据电压dataij及感测信号。

138.另外,参照图14,示例性地示出了显示装置1以第三模式驱动的情况。例如,在第三模式下的第三时段sp3期间,垂直同步信号vsync的逻辑电平改变次数可以是2次(1次上升转换及1次下降转换)。由于显示驱动部210及传感器驱动部220处于接收垂直同步信号vsync及水平同步信号hsync的状态,因此可知当前水平时段1h的模式为第三模式。

139.在第三模式中,数据驱动部12(或者,显示驱动部210)可以在水平时段1h中的第一时间点t1e开始输出针对像素pxij中的至少一部分(例如,第i个像素行)的数据电压dataij、

……

,并在水平时段1h中的第二时间点t6.3e结束数据电压dataij、

……

的输出。例如,数据驱动部12可以在时段t1e至t6.3e期间向第j条数据线dlj输出数据电压dataij。

140.在第三模式中,传感器驱动部220(或者,传感器发送部tdc)可以在水平时段1h中的与第一时间点t1e及第二时间点t6.3e不同的第三时间点t2e改变针对传感器中的至少一部分传感器txk的感测信号的逻辑电平。例如,传感器驱动部220可以在第三时间点t2e向第k个第一传感器txk供应上升转换信号。在一水平时段1h中,第三时间点可以是一个以上。例如,传感器驱动部220可以在第三时间点t6.2e向第k个第一传感器txk供应下降转换信号。

141.根据一实施例,在水平时段1h的从第四时间点t4e至第五时间点t7e为止,扫描驱

动部13可以输出针对像素中的至少一部分像素pxij的导通电平的扫描信号。此时,可以从第二时间点t6.3e至第五时间点t7e为止保持感测信号的逻辑电平(逻辑低电平)。

142.参照图12及图14,当逻辑电平改变次数为n次(例如,4次)时的数据电压的输出时段t1e至t6e与当逻辑电平改变次数为m次(例如,2次)时的数据电压的输出时段t1e至t6.3e可以以水平时段1h为基准而长度彼此不同。此时,n及m可以是彼此不同的正整数。例如,图12的第一模式可以有利于单色图案的图像显示,图14的第三模式可以有利于条纹图案(stripe pattern)的图像显示。在图12的第一模式及图14的第三模式中,传感器脆弱时段wp1及显示脆弱时段wp2可以变得不同。

143.根据一实施例,当逻辑电平改变次数为n次时的感测信号的电平保持时段t2e至t5e和当逻辑电平改变次数为m次时的感测信号的电平保持时段t2e至t6.2e可以以水平时段1h为基准而长度彼此不同。

144.根据本实施例,第一时间点、第二时间点及第三时间点中的至少一个可以根据在水平同步信号hsync保持在特定逻辑电平(例如,第二逻辑电平lv2)的期间的垂直同步信号vsync的逻辑电平改变次数而变化。因此,对应于按模式而变化的传感器脆弱时段wp1及显示脆弱时段wp2,可以供应数据电压dataij及感测信号。

145.根据上述的实施例,可以提供一种能够利用现有的控制信号vsync、hsync而在最小化干扰的同时改变感测信号及显示信号的时序的显示装置1及其驱动方法。

146.图15是用于说明根据本发明的一实施例的显示装置的驱动方法的图。

147.在说明图15时,省略关于与图12至图14重复的内容的说明。

148.首先,传感器驱动部220可以接收垂直同步信号vsync及水平同步信号hsync(s101)。接下来,当水平同步信号hsync为特定逻辑电平(例如,第二逻辑电平lv2)时(s102),传感器驱动部220可以对垂直同步信号vsync的逻辑电平改变次数进行计数(s103)。

149.在垂直同步信号vsync的逻辑电平改变次数为n次的情况下(s104),传感器驱动部220可以以第一模式驱动(s105)。另外,在垂直同步信号vsync的逻辑电平改变次数为m次的情况下(s106),传感器驱动部220可以以第二模式驱动(s107)。

150.图16及图17是用于说明根据本发明的另一实施例的水平时段的图。

151.参照图16,示出了在第三时段sp3期间利用垂直同步信号vsync的占空比(duty ratio)来提供模式信息的示例。在图12至图15的实施例中,利用垂直同步信号vsync的逻辑电平变更次数来向传感器驱动部220提供了模式信息,但在图16的实施例中,可以利用垂直同步信号vsync的占空比来向传感器驱动部220提供模式信息。在此,垂直同步信号vsync的占空比是指在第三时段sp3期间垂直同步信号vsync保持在第三逻辑电平lv3的时段与垂直同步信号vsync保持在第四逻辑电平lv4的时段的比率。在图16的实施例中,垂直同步信号vsync的逻辑电平改变次数(例如,2次)可以在各个模式的第三时段sp3中彼此相同。

152.参照图17,示出了在第三时段sp3期间利用水平同步信号hsync的占空比来提供模式信息的示例。在图12至图15的实施例中,利用垂直同步信号vsync的逻辑电平变化次数来向传感器驱动部220提供了模式信息,但是在图17的实施例中,可以利用水平同步信号hsync的占空比来向传感器驱动部220提供模式信息。在此,水平同步信号hsync的占空比是指在第三时段sp3期间水平同步信号hsync保持在第一逻辑电平lv1的时段与水平同步信号

hsync保持在第二逻辑电平lv2的时段的比率。在图17的实施例中,垂直同步信号vsync的逻辑电平可以在各个模式的第三时段sp3中保持为相同的第三逻辑电平lv3。

153.图18至图24是用于说明显示装置的示例性的构成的图。图18至图24的附图标记与图1至图17的附图标记彼此独立。

154.图18是用于说明根据本发明的一实施例的基板的图,图19是用于说明根据本发明的一实施例的显示装置的图。

155.在以下实施例中,平面可以在第一方向dr1及第二方向dr2上定义位置,高度可以在第三方向dr3上定义位置(参照图20)。第一方向dr1、第二方向dr2及第三方向dr3可以是彼此正交的方向。

156.基板sub可以包括显示区域da、非显示区域nda、第一附加区域ada1及第二附加区域ada2。

157.显示区域da可以具有矩形的形态。显示区域da的各个边角部可以是形成角度的形态或曲面形态。并且,在圆形显示器的情况下,显示区域da可以具有圆的形态。并且,显示区域da可以构成为不是四边形的其他多边形、椭圆形等。如此,可以根据产品而不同地设定显示区域da的形状。

158.像素可以位于显示区域da。根据显示装置dp的种类,各个像素可以包括发光二极管,或者包括液晶层。

159.非显示区域nda可以围绕显示区域da的外围。例如,非显示区域nda可以具有矩形的形态。非显示区域nda的各个边角部(corner)可以是形成角度的形态或曲面形态。假设非显示区域nda的各个边角部具有曲面形态的情况并在图19中示出。非显示区域nda可以具有圆的形态。由于最小化非显示区域nda有利于窄边框(narrow bezel)结构,因此非显示区域nda的形状可以与显示区域da的形状相似。

160.第一附加区域ada1可以位于非显示区域nda与第二附加区域ada2之间。第一附加区域ada1与非显示区域nda可以在第一边界ed1连接。第一附加区域ada1与第二附加区域ada2可以在第二边界ed2连接。第一边界ed1及第二边界ed2可以各自沿第一方向dr1延伸。

161.第一附加区域ada1的宽度可以从第一边界ed1朝向第二边界ed2而逐渐变窄。即,第一附加区域ada1的沿第一方向dr1上的宽度可以朝向第二方向dr2而逐渐变窄。据此,第一附加区域ada1可以包括弯曲的第一侧表面rc1及第二侧表面rc2。侧表面rc1、rc2可以朝向基板的内部(例如,基板的中心)凸出。

162.在图19中,第一附加区域ada1被示出为在第一方向dr1及其相反方向上包括两个侧表面rc1、rc2。在另一实施例中,第一附加区域ada1也可以由于其位于第一方向dr1的边界与非显示区域nda的边界重合,从而仅包括第一侧表面rc1。在又一实施例中,第一附加区域ada1也可以由于其位于与第一方向dr1相反的方向的边界与非显示区域nda的边界重合而仅包括第二侧表面rc2。

163.第二附加区域ada2可以具有矩形的形态。第二附加区域ada2的位于第二方向dr2的各个边角部可以是形成角度的形态或曲面形态。假设位于第二附加区域ada2的第二方向dr2的各个边角部为形成角度的形态的情况并在图19中示出。

164.封装膜tfe可以位于像素上。例如,封装膜tfe可以在显示区域da覆盖像素,并且封装膜tfe的边界可以位于非显示区域nda。由于封装膜tfe覆盖显示区域da的像素的发光元

件及电路元件,因此可以防止因外部湿气或冲击导致的破损。

165.感测电极sc1、sc2可以位于封装膜tfe上。感测电极sc1、sc2可以感测用户的身体的触摸(touch)、悬停(hovering)、手势(gesture)、接近与否等。感测电极sc1、sc2可以根据电阻膜方式(resistive type)、电容方式(capacitive type)、电磁感应方式(em:electro-magnetic type)、光感测方式(optical type)等的多样的方式而构成为其他形状。例如,在感测电极sc1、sc2以电容方式构成的情况下,感测电极sc1、sc2可以以自电容方式(self-capacitive type)、互电容方式(mutual-capacitive type)等构成。以下,为了便于说明,将感测电极sc1、sc2以互电容方式构成的情况作为示例。

166.在感测电极sc1、sc2以互电容方式构成的情况下,可以通过对应于第一感测电极sc1的感测布线来发送驱动信号,并且可以通过对应于与第一感测电极sc1形成互电容的第二感测电极sc2的感测布线来接收感测信号。在用户的身体接近的情况下,第一感测电极sc1与第二感测电极sc2之间的互电容可以变化,并可以根据据此的感测信号的差异来检测出用户的触摸与否。在另一实施例中,可以通过对应于第二感测电极sc2的感测布线来发送驱动信号,并可以通过对应于与第二感测电极sc2形成互电容的第一感测电极sc1的感测布线来接收感测信号。

167.垫pde1、pde2、pde3可以位于第二附加区域ada2上。垫pde1、pde3可以通过感测布线ist1、ist2而与位于封装膜上部的感测电极sc1、sc2连接。垫pde1、pde3可以连接到外部的触摸集成电路芯片(ic,integrated chip)。并且,垫pde2可以通过显示布线dst而与位于封装膜tfe下部的像素或像素的驱动部连接。驱动部可以包括扫描驱动部、发光驱动部、数据驱动部等。驱动部可以位于封装膜tfe的下部,也可以位于通过垫pde2连接的外部的显示ic。

168.在显示装置dp为互电容方式的情况下,触摸ic可以通过第一感测布线ist1发送驱动信号,并通过第二感测布线ist2接收感测信号。在另一实施例中,也可以通过第二感测布线ist2发送驱动信号,并通过第一感测布线ist1接收感测信号。作为参考,在显示装置dp为自电容方式的情况下,第一感测布线ist1与第二感测布线ist2的驱动方式可以没有差异。显示布线dst可以包括控制线、数据线、电源线等,并且可以提供信号使得像素能够显示图像。这些信号可以由与显示布线dst连接的驱动部来提供。

169.图18是基板sub被弯曲的状态,图19是基板sub未被弯曲的状态。显示装置dp可以在如图19所示地未被弯曲的状态下将元件堆叠在基板sub之后如图18所示地弯曲。

170.基板sub可以包括从第一附加区域ada1的第一侧表面rc1以与非显示区域nda重叠的方式延伸的第一弯曲区域ba1。另外,第一弯曲区域ba1可以以与显示区域da重叠的方式延伸。即,各个显示区域da、非显示区域nda及第一附加区域ada1可以与第一弯曲区域ba1局部重叠。第一弯曲区域ba1可以具有沿第一方向dr1的宽度,并且长度可以沿第二方向dr2延伸。第一弯曲轴bx1可以定义为从第一弯曲区域ba1的中心沿第二方向dr2延伸的折叠线(folding line)。根据实施例,与周围的其他部分不同,第一弯曲区域ba1可以是一部分绝缘膜等被去除而应力减小的部分。根据实施例,第一弯曲区域ba1也可以具有与周围的其他部分相同的构成。

171.基板sub可以包括从第一附加区域ada1的第二侧表面rc2以与非显示区域nda重叠的方式延伸的第三弯曲区域ba3。另外,第三弯曲区域ba3可以以与显示区域da重叠的方式

延伸。即,各个显示区域da、非显示区域nda及第一附加区域ada1可以与第三弯曲区域ba3局部重叠。第三弯曲区域ba3可以具有沿第一方向dr1的宽度,并且长度可以沿第二方向dr2延伸。第三弯曲轴bx3可以定义为从第三弯曲区域ba3的中心沿第二方向dr2延伸的折叠线。根据实施例,与周围的其他部分不同,第三弯曲区域ba3可以是一部分绝缘膜等被去除而应力减小的部分。根据实施例,第三弯曲区域ba3也可以具有与周围的其他部分相同的构成。

172.第二附加区域ada2可以包括第二弯曲区域ba2。第二弯曲区域ba2可以具有沿第二方向dr2的宽度,并且长度可以沿第一方向dr1延伸。第二弯曲轴bx2可以定义为从第二弯曲区域ba2的中心沿第一方向dr1延伸的折叠线。根据实施例,与周围的其他部分不同,第二弯曲区域ba2可以是一部分绝缘膜等被去除而应力减小的部分。根据实施例,第二弯曲区域ba2也可以具有与周围的其他部分相同的构成。

173.第一弯曲区域ba1、第二弯曲区域ba2、第三弯曲区域ba3可以彼此不重叠。

174.在此,术语“折叠”表示形态不固定而能够从原来的形态变形为其他形态,其包括沿一个以上的弯曲轴折叠(folded)或弯曲(curved)或卷曲(rolled)成卷状的情形。借由第一弯曲区域ba1及第三弯曲区域ba3,可以减小显示装置dp的沿第一方向dr1的相反方向及第一方向dr1的侧表面边框的宽度。并且,借由第二弯曲区域ba2,可以减小显示装置dp的沿第二方向dr2的侧表面边框的宽度。

175.图20是对应于图19的i-i'线的剖面的一实施例。假设图19的i-i'线经过第一垫pde1及第一感测布线ist1。

176.首先,对显示区域da进行说明。在本发明的一实施例中,在显示区域da设置有像素px。各个像素px可以包括连接到显示布线dst中的对应的布线的晶体管、连接到晶体管的发光元件以及电容器cst。在图20中,为了便于说明,针对一个像素px示例性地示出了一个晶体管、一个发光元件以及一个电容器cst。

177.基板sub可以利用诸如玻璃、树脂(resin)等的绝缘性材料构成。并且,基板sub可以利用具有柔性(flexibility)的材料构成,以便能够弯曲或折叠,并且可以具有单层结构或多层结构。

178.例如,基板sub可以包括聚苯乙烯(polystyrene)、聚乙烯醇(polyvinyl alcohol)、聚甲基丙烯酸甲酯(polymethyl methacrylate)、聚醚砜(polyethersulfone)、聚丙烯酸酯(polyacrylate)、聚醚酰亚胺(polyetherimide)、聚萘二甲酸乙二醇酯(polyethylene naphthalate)、聚对苯二甲酸乙二醇酯(polyethylene terephthalate)、聚苯硫醚(polyphenylene sulfide)、聚芳酯(polyarylate)、聚酰亚胺(polyimide)、聚碳酸酯(polycarbonate)、三醋酸纤维素(triacetate cellulose)、醋酸丙酸纤维素(cellulose acetate propionate)中的至少任意一种。然而,构成基板sub的材料可以多样地变化,也可以利用纤维增强塑料(frp:fiber reinforced plastic)等构成。

179.例如,在基板sub具有多层结构的情况下,可以在多个层之间以单层或多层的形式夹设有硅氮化物、硅氧化物、硅氮氧化物等的无机物。

180.缓冲膜bf可以覆盖基板sub。缓冲膜bf可以防止杂质扩散到晶体管的沟道。缓冲膜bf可以是利用无机材料构成的无机绝缘膜。例如,缓冲膜bf可以利用硅氮化物、硅氧化物、硅氮氧化物等形成,也可以根据基板sub的材料及工艺条件而省略。根据实施例,还可以提供屏障膜(barrier layer)。

181.有源膜act可以位于缓冲膜bf上。有源膜act可以被图案化而构成晶体管的沟道、源极电极及漏极电极,或者可以构成布线。有源膜act可以利用半导体材料形成。有源膜act可以是利用多晶硅、非晶硅、氧化物半导体等构成的半导体图案。晶体管的沟道是未掺杂有杂质的半导体图案,可以是本征半导体。源极电极、漏极电极及布线可以是掺杂有杂质的半导体图案。作为杂质,可以使用诸如n型杂质、p型杂质、其他金属之类的杂质。

182.第一栅极绝缘膜gi1可以覆盖有源膜act。第一栅极绝缘膜gi可以是利用无机材料构成的无机绝缘膜。作为无机材料,可以利用诸如聚硅氧烷、硅氮化物、硅氧化物、硅氮氧化物等的无机绝缘物质。

183.晶体管的栅极电极ge及电容器cst的下部电极le可以位于第一栅极绝缘膜gi1上。栅极电极ge可以与对应于沟道的区域重叠。

184.栅极电极ge及下部电极le可以利用金属构成。例如,栅极电极ge可以利用诸如金(au)、银(ag)、铝(al)、钼(mo)、铬(cr)、钛(ti)、镍(ni)、钕(nd)、铜(cu)之类的金属中的至少一种或者上述的金属的合金构成。并且,栅极电极ge可以形成为单膜,但不限于此,可以形成为金属及合金中的两种以上的物质堆叠的多膜。

185.第二栅极绝缘膜gi2可以覆盖栅极电极ge及下部电极le。第二栅极绝缘膜gi2可以是利用无机材料构成的无机绝缘膜。作为无机材料,可以利用聚硅氧烷、硅氮化物、硅氧化物、硅氮氧化物等。

186.电容器cst的上部电极ue可以位于第二栅极绝缘膜gi2上。电容器上部电极ue可以利用金属构成。例如,上部电极ue可以利用诸如金(au)、银(ag)、铝(al)、钼(mo)、铬(cr)、钛(ti)、镍(ni)、钕(nd)、铜(cu)之类的金属中的至少一种或金属的合金构成。并且,上部电极ue可以形成为单膜,但不限于此,可以形成为金属及合金中的两种以上的物质堆叠的多膜。

187.下部电极le和上部电极ue可以将第二栅极绝缘膜gi2置于之间而构成电容器cst。在图20中,电容器cst被示出为下部电极le和上部电极ue的两层电极结构,但在其他实施例中,电容器cst可以利用有源膜act而构成为三层电极结构,或者可以利用与第一连接图案cnp1相同的层的电极而构成为三层电极结构,或者也可以构成为四层以上的电极结构。

188.层间绝缘膜ild可以覆盖上部电极ue。层间绝缘膜ild可以是利用无机材料构成的无机绝缘膜。作为无机材料,可以利用聚硅氧烷、硅氮化物、硅氧化物、硅氮氧化物等。

189.在本实施例中,为了便于说明,可以将第一栅极绝缘膜gi1、第二栅极绝缘膜gi2及层间绝缘膜ild称为第一绝缘膜组ing1。第一绝缘膜组ing1可以覆盖晶体管的一部分。根据实施例,第一绝缘膜组ing1也可以进一步包括缓冲膜bf。

190.第一连接图案cnp1可以位于层间绝缘膜ild上。第一连接图案cnp1可以通过形成在层间绝缘膜ild、第二栅极绝缘膜gi2、第一栅极绝缘膜gi1的接触孔而分别接触于有源膜act的源极电极和漏极电极。

191.第一连接图案cnp1可以利用金属构成。例如,源极电极se和漏极电极de可以利用诸如金(au)、银(ag)、铝(al)、钼(mo)、铬(cr)、钛(ti)、镍(ni)、钕(nd)、铜(cu)之类的金属中的至少一种或金属的合金构成。

192.尽管未示出,但是根据实施例,钝化膜可以覆盖第一连接图案cnp1。钝化膜可以是利用无机材料构成的无机绝缘膜。作为无机材料,可以利用聚硅氧烷、硅氮化物、硅氧化物、硅氮氧化物等。

193.第一过孔膜via1可以覆盖钝化膜或晶体管。第一过孔膜via1可以是利用有机材料构成的有机绝缘膜。作为有机材料,可以利用诸如聚丙烯酸系化合物、聚酰亚胺系化合物、如特氟龙之类的氟系碳化合物、苯并环丁烯化合物等的有机绝缘物质。有机膜可以通过蒸发(evaporation)等方法沉积。

194.第二连接图案cnp2可以通过第一过孔膜via1的开口部而与第一连接图案cnp1连接。第二连接图案cnp2可以利用诸如金(au)、银(ag)、铝(al)、钼(mo)、铬(cr)、钛(ti)、镍(ni)、钕(nd)、铜(cu)之类的金属中的至少一种或金属的合金构成。

195.第二过孔膜via2可以覆盖第一过孔膜via1及第二连接图案cnp2。第二过孔膜via2可以是利用有机材料构成的有机绝缘膜。作为有机材料,可以利用诸如聚丙烯酸系化合物、聚酰亚胺系化合物、如特氟龙之类的氟系碳化合物、苯并环丁烯化合物等的有机绝缘物质。

196.第一发光元件电极lde1可以通过第二过孔膜via2的开口部而与第二连接图案cnp2连接。在此,根据实施例,第一发光元件电极lde1可以是发光元件的阳极。

197.根据实施例,可以省略第二过孔膜via2及第二连接图案cnp2的构成,并且第一发光元件电极lde1可以通过第一过孔膜via1的开口部而与第一连接图案cnp1直接连接。

198.第一发光元件电极lde1可以利用ag、mg、al、pt、pd、au、ni、nd、ir、cr、它们的合金等的金属膜和/或铟锡氧化物(ito:indiumtin oxide)、铟锌氧化物(izo:indium zinc oxide)、锌氧化物(zno:zinc oxide)、铟锡锌氧化物(itzo:indium tin zinc oxide)等构成。第一发光元件电极lde1可以利用一种金属构成,但不限于此,也可以利用两种以上的金属(例如,ag和mg的合金)构成。

199.在要向基板sub的下部方向提供图像的情况下,第一发光元件电极lde1可以利用透明导电膜形成,在要向基板sub的上部方向提供图像的情况下,第一发光元件电极lde1可以利用金属反射膜和/或透明导电膜形成。

200.在形成有第一发光元件电极lde1等的基板sub上设置有划分各个像素px的发光区域的像素定义膜pdl。像素定义膜pdl可以是利用有机材料构成的有机绝缘膜。作为有机材料,可以利用诸如聚丙烯酸系化合物、聚酰亚胺系化合物、如特氟龙之类的氟系碳化合物、苯并环丁烯化合物等的有机绝缘物质。

201.像素定义膜pdl可以暴露第一发光元件电极lde1的上表面,并沿着像素px的外周从基板sub突出。在被像素定义膜pdl围绕的像素px区域可以设置有发光膜eml。

202.发光膜eml可以包括低分子或高分子物质。作为低分子物质,可以包括铜酞菁(cupc:copper phthalocyanine)、n,n'-二(萘-1-基)-n,n'-二苯基-联苯胺(npb:n,n'-di(naphthalene-l-yl)-n,n'-diphenyl-benzidine)、三-8-羟基喹啉铝(tris-8-hydroxyquinoline aluminum)(alq3)等。这些物质可以通过真空沉积的方法形成。作为所述高分子物质,可以包括pedot、聚对亚苯基亚乙烯基(ppv:poly-phenylenevinylene)系及聚芴(polyfluorene)系等。

203.发光膜eml可以被提供为单层,但是也可以被提供为包括多样的功能层的多层。在发光膜eml被提供为多层的情况下,空穴注入层(hil:hole injection layer)、空穴传输层(htl:hole transport layer)、发光层(eml:emission layer)、电子传输层(etl:electron transport layer)、电子注入层(eil:electron injection layer)等可以具有以单一或复合的结构堆叠的结构。这样的发光膜eml可以通过丝网印刷或喷墨印刷方法、激光诱导热成

像方法(liti:laser induced thermal imaging)等形成。

204.根据实施例,发光膜eml的至少一部分可以跨过多个第一发光元件电极lde1而形成为一体,也可以以与多个第一发光元件电极lde1分别对应的方式被单独设置。

205.在发光膜eml上可以设置有第二发光元件电极lde2。第二发光元件电极lde2可以按各个像素px而设置,但是可以设置为覆盖大部分显示区域da,并且可以被多个像素px共享。

206.根据实施例,第二发光元件电极lde2可以用作阴极或者阳极,在第一发光元件电极lde1为阳极的情况下,第二发光元件电极lde2可以用作阴极,在第一发光元件电极lde1为阴极的情况下,第二发光元件电极lde2可以用作阳极。

207.第二发光元件电极lde2可以利用ag、mg、al、pt、pd、au、ni、nd、ir、cr等的金属膜和/或铟锡氧化物(ito:indium tin oxide)、铟锌氧化物(izo:indium zinc oxide)、锌氧化物(zno:zinc oxide)、铟锡锌氧化物(itzo:indium tin zinc oxide)等的透明导电膜构成。在本发明的一实施例中,第二发光元件电极lde2可以构成为包括金属薄膜的双膜以上的多膜,例如,也可以构成为ito/ag/ito的三膜。

208.在要向基板sub的下部方向提供图像的情况下,第二发光元件电极lde2可以利用金属反射膜和/或透明导电膜形成,在要向基板sub的上部方向提供图像的情况下,第二发光元件电极lde2可以利用透明导电膜形成。

209.上述的第一发光元件电极lde1、发光膜eml及第二发光元件电极lde2的集合可以称为发光元件。

210.在第二发光元件电极lde2上可以设置有封装膜tfe。封装膜tfe可以构成为单层,但是也可以构成为多层。在本实施例中,封装膜tfe可以用第一封装膜enc1、第二封装膜enc2、第三封装膜enc3构成。第一封装膜enc1、第二封装膜enc2、第三封装膜enc3可以利用有机材料和/或无机材料构成。位于最外围的第三封装膜enc3可以利用无机材料构成。例如,第一封装膜enc1可以是利用无机材料构成的无机膜,第二封装膜enc2可以是利用有机材料构成的有机膜,第三封装膜enc3可以是利用无机材料构成的无机膜。对无机材料的情况而言,与有机材料相比,虽然水分或氧气的渗透较少,但由于弹性或柔性较小,因此易受裂纹的影响。通过利用无机材料形成第一封装膜enc1和第三封装膜enc3且利用有机材料形成第二封装膜enc2,能够防止裂纹的扩散。在此,利用有机材料构成的层(即,第二封装膜enc2)可以被第三封装膜enc3完全覆盖,以使端部不暴露于外部。作为有机材料,可以利用诸如聚丙烯酸系化合物、聚酰亚胺系化合物、如特氟龙之类的氟系碳化合物、苯并环丁烯化合物等的有机绝缘物质,作为无机材料,可以利用聚硅氧烷、硅氮化物、硅氧化物、硅氮氧化物等。

211.构成发光元件的发光膜eml可能容易被来自外部的水分或氧气等损坏。封装膜tfe通过覆盖发光膜eml来保护发光膜eml。封装膜tfe覆盖显示区域da,并可以延伸至作为显示区域da的外侧的非显示区域nda。但是,对利用有机材料构成的绝缘膜的情况而言,虽然在柔性及弹性等的方面有利,但是与利用无机材料构成的绝缘膜相比,水分或氧气容易渗透。在本发明的一实施例中,为了防止水分或氧气通过利用有机材料构成的绝缘膜渗透,利用有机材料构成的绝缘膜的端部可以以不暴露于外部的方式被利用无机材料构成的绝缘膜覆盖。例如,利用有机材料构成的第一过孔膜via1、第二过孔膜via2及像素定义膜pdl可以

不连续地延伸至非显示区域nda,并且可以被第一封装膜enc1覆盖。据此,像素定义膜pdl的上表面、第一过孔膜via1、第二过孔膜via2及像素定义膜pdl的侧表面被包括无机材料的封装膜tfe封装,从而能够防止被暴露于外部。

212.但是,封装膜tfe的多层与否或者封装膜tfe的材料不限于此,可以多样地改变。例如,封装膜tfe可以包括彼此交替堆叠的多个有机材料层和多个无机材料层。

213.第一感测电极层ism1可以位于封装膜tfe上。根据实施例,附加缓冲膜可以位于第一感测电极层ism1与封装膜tfe之间。第一感测电极层ism1可以利用ag、mg、al、pt、pd、au、ni、nd、ir、cr等的金属膜和/或铟锡氧化物(ito:indium tin oxide)、铟锌氧化物(izo:indium zinc oxide)、锌氧化物(zno:zinc oxide)、铟锡锌氧化物(itzo:indium tin zinc oxide)等的透明导电膜构成。

214.第一感测绝缘膜isi1可以存在于第一感测电极层ims1上。第一感测绝缘膜isi1可以是利用无机材料构成的无机绝缘膜。作为无机材料,可以利用聚硅氧烷、硅氮化物、硅氧化物、硅氮氧化物等的无机绝缘物质。

215.第二感测电极层ism2可以存在于第一感测绝缘膜isi1上。第二感测电极层ism2可以利用ag、mg、al、pt、pd、au、ni、nd、ir、cr等的金属膜和/或铟锡氧化物(ito:indium tin oxide)、铟锌氧化物(izo:indium zinc oxide)、锌氧化物(zno:zinc oxide)、铟锡锌氧化物(itzo:indium tin zinc oxide)等的透明导电膜构成。

216.可以利用第一感测电极层ism1、第一感测绝缘膜isi1及第二感测电极层ism2来构成多样的输入感测部,这将参照图22至图24进行后述。

217.在图20的实施例中,第二感测电极层ism2可以被图案化而构成第一感测布线ist1的第一图案ist1a。

218.第二感测绝缘膜isi2可以位于第二感测电极层ism2上。第二感测绝缘膜isi2可以利用有机膜构成。例如,作为有机材料,可以利用诸如聚丙烯酸系化合物、聚酰亚胺系化合物、如特氟龙之类的氟系碳化合物、苯并环丁烯化合物等的有机绝缘物质。例如,第二感测绝缘膜isi2也可以利用聚甲基丙烯酸甲酯(polymethyl methacrylate)、聚二甲基硅氧烷(polydimethylsiloxane)、聚酰亚胺(polyimide)、丙烯酸酯(acrylate)、聚对苯二甲酸乙二醇酯(polyethylene terephthalate)、聚萘二甲酸乙二醇酯(polyethylene naphthalate)等构成。

219.接下来,对非显示区域nda、第一附加区域ada1及第二附加区域ada2进行说明。在图20的剖面图中,由于非显示区域nda和第一附加区域ada1的区别不是特征,因此将不区分非显示区域nda和第一附加区域ada1而进行说明。以下,在说明非显示区域nda及第二附加区域ada2时,为了避免重复说明,省略或简单地说明已经说明过的内容。

220.坝dam可以位于第二封装膜enc2的边界。例如,坝dam可以位于平坦化膜flt与第二封装膜enc2之间。坝dam可以是多层结构物,例如,可以包括第一坝dam1及第二坝dam2。例如,第一坝dam1及第二坝dam2可以利用有机材料构成。第一坝dam1及第二坝dam2可以分别对应于第一过孔膜via1、第二过孔膜via2及像素定义膜pdl中的任意一个。例如,在第一坝dam1与第一过孔膜via1通过相同的工艺而利用相同的物质构成的情况下,第二坝dam2可以与第二过孔膜via2或像素定义膜pdl通过相同的工艺而利用相同的物质构成。作为另一例,在第一坝dam1与第二过孔膜via2通过相同的工艺而利用相同的物质构成的情况下,第二坝

dam2可以与像素定义膜pdl通过相同的工艺而利用相同的物质构成。除此之外,在显示区域da的像素定义膜pdl上形成间隔件(spacer)的情况下,也可以利用与间隔件相同的物质来构成坝dam。

221.坝dam在工艺过程中防止流动性强的第二封装膜enc2的有机材料向坝dam的外部泛滥。利用无机材料构成的第一封装膜enc1及第三封装膜enc3覆盖坝dam而延伸,从而能够强化与基板sub或基板sub上部的其他膜之间的粘合力。

222.第一垫pde1可以位于基板sub上,并可以与平坦化膜flt隔开。第一垫pde1可以被第二绝缘膜组ing2支撑。第二绝缘膜组ing2的各个绝缘膜可以对应于第一绝缘膜组ing1的各个绝缘膜。第一垫pde1可以包括第一垫电极pde1a及第二垫电极pde1b。第一垫电极pde1a可以利用与第一连接图案cnp1相同的物质构成。第二垫电极pde1b可以利用与第二连接图案cnp2相同的物质构成。

223.平坦化膜flt可以位于基板sub上,且可以与封装膜tfe所覆盖的区域隔开。平坦化膜flt可以是利用有机材料构成的有机绝缘膜。作为有机材料,可以利用诸如聚丙烯酸系化合物、聚酰亚胺系化合物、如特氟龙之类的氟系碳化合物、苯并环丁烯化合物等的有机绝缘物质。

224.在本实施例中,可以在形成层间绝缘膜ild之后并且在形成第一连接图案cnp1之前形成平坦化膜flt。因此,平坦化膜flt和第一过孔膜via1可以通过彼此不同的工艺形成。根据实施例,平坦化膜flt和第一过孔膜via1也可以包括彼此不同的有机材料。

225.平坦化膜flt的一端可以覆盖第一绝缘膜组ing1。并且,对应于第二弯曲区域ba2的平坦化膜flt的一部分可以填充第一绝缘膜组ing1与第二绝缘膜组ing2之间的第一沟槽tch1。

226.无机绝缘膜与有机绝缘膜相比,硬度较高且柔性较小,因此产生裂纹的概率相对较高。在无机绝缘膜产生裂纹的情况下,裂纹可能传播到无机绝缘膜上的布线,结果可能发生布线断线等的不良。

227.因此,如图20所示,通过从第二弯曲区域ba2去除无机绝缘膜,可以形成第一沟槽tch1,并可以区分第一绝缘膜组ing1及第二绝缘膜组ing2。在本实施例中,示出了对应于第一沟槽tch1的区域的所有无机绝缘膜被去除的情形,但是在另一实施例中,也可以残留一部分无机绝缘膜。在这种情况下,残留的一部分无机绝缘膜也可以包括狭缝,从而分散弯曲应力。

228.第一感测布线ist1的第二图案ist1b可以在平坦化膜flt上延伸,并可以与第一垫pde1电连接。在本实施例中,第二图案ist1b可以与第一连接图案cnp1通过相同的工艺利用相同的物质构成。

229.第一布线保护膜lpl1可以覆盖平坦化膜flt及第二图案ist1b。并且,第二布线保护膜lpl2可以覆盖第一布线保护膜lpl1。根据实施例,也可以省略第二布线保护膜lpl2的构成。第一布线保护膜lpl1及第二布线保护膜lpl2可以利用有机材料构成。第一布线保护膜lpl1及第二布线保护膜lpl2可以分别对应于第一过孔膜via1、第二过孔膜via2及像素定义膜pdl中的任意一个。例如,在第一布线保护膜lpl1与第一过孔膜via1通过相同的工艺利用相同的物质构成的情况下,第二布线保护膜lpl2可以与第二过孔膜via2或像素定义膜pdl通过相同的工艺利用相同的物质构成。作为另一例,在第一布线保护膜lpl1与第二过孔

膜via2通过相同的工艺利用相同的物质构成的情况下,第二布线保护膜lpl2可以与像素定义膜pdl通过相同的工艺利用相同的物质构成。

230.第一布线保护膜lpl1、第二布线保护膜lpl2及第一感测绝缘膜isi1可以包括暴露第二图案ist1b的第一开口部opn1。

231.第一图案ist1a可以通过第一开口部opn1与第二图案ist1b连接。根据本实施例,位于第一绝缘膜组ing1及平坦化膜flt的一端上的第二图案ist1b的高度可以大于位于与第一沟槽tch1对应的平坦化膜flt上的第二图案ist1b的高度。

232.因此,第一图案ist1a及第二图案ist1b可以在没有其他桥接布线的情况下直接连接,并且由于没有桥接布线,因此会提高第一图案ist1a与第二图案ist1b之间的连接可靠性。并且,由于非显示区域nda的长度可以缩短相当于桥接布线的长度,因此会减小死区(dead space),并且容易地实现薄边框。

233.第一感测布线ist1的第三图案ist1c可以连接第一垫pde1与第二图案istb。第三图案ist1c可以与晶体管的栅极电极ge通过相同的工艺利用相同的物质形成。根据实施例,第三图案ist1c也可以与上部电极ue通过相同的工艺利用相同的物质形成。根据实施例,也可以使第奇数个第三图案ist1c与晶体管的栅极电极ge通过相同的工艺利用相同的物质形成,并且使第偶数个第三图案ist1c与上部电极ue通过相同的工艺利用相同的物质形成。相反,也可以使第偶数个第三图案ist1c与晶体管的栅极电极ge通过相同的工艺利用相同的物质形成,并且使第奇数个第三图案ist1c与上部电极ue通过相同的工艺利用相同的物质形成。由此,也可以更有效地防止相邻的布线之间的短路问题。

234.第二绝缘膜组ing2可以包括暴露第三图案ist1c的第二开口部opn2。并且,平坦化膜flt可以包括对应于第二开口部opn2的开口部。第二图案ist1b可以通过第二开口部opn2而与第三图案ist1c连接。

235.图21是对应于图19的ii-ii'线的剖面的一实施例。

236.图19的ii-ii'线可以对应于第一弯曲轴bx1。然而,相同的实施例不仅可以应用于第一侧表面rc1,而且可以应用于第二侧表面rc2。

237.显示布线dst可以利用布线g1l、g2l、sdl中的至少一条而构成为单层布线或多层布线。布线g1l可以与栅极电极ge通过相同的工艺利用相同的物质构成。布线g2l可以与上部电极ue通过相同的工艺利用相同的物质构成。布线sdl可以与第一连接图案cnp1通过相同的工艺利用相同的物质构成。

238.感测布线ist1、ist2的图案ist1a、ist12a可以位于封装膜tfe及第一感测绝缘膜isi1上(以第三方向dr3为基准),且可以位于坝dam与显示区域da之间(以第二方向dr2为基准)。第一感测绝缘膜isi1可以位于封装膜tfe与感测布线ist1、ist2之间。

239.图22及图23是用于说明根据本发明的一实施例的感测电极及桥接电极的图。图23是沿图22的iii-iii'线剖切的剖面图。

240.桥接电极cp1可以通过图案化第一感测电极层ism1而位于封装膜tfe上。

241.第一感测绝缘膜isi1可以覆盖桥接电极cp1,且可以包括暴露桥接电极cp1的一部分的接触孔cnt。

242.第一感测电极sc1及第二感测电极sc2可以通过图案化第二感测电极层ism2而形成在第一感测绝缘膜isi1上。第一感测电极sc1可以通过接触孔cnt而与桥接电极cp1连接。

243.第二感测电极sc2可以通过图案化第二感测电极层ism2而在与第二感测电极sc2相同的层上具有连接图案cp2。因此,在连接第二感测电极sc2时,可以不需要单独的桥接电极。

244.根据实施例,各个感测电极sc1、sc2可以覆盖多个像素px。此时,在各个感测电极sc1、sc2利用不透明导电膜构成的情况下,可以包括能够暴露所覆盖的感测电极sc1、sc2的多个像素px的多个开口部。例如,各个感测电极sc1、sc2可以构成为网格形态。在各个感测电极sc1、sc2利用透明导电膜构成的情况下,各个感测电极sc1、sc2也可以构成为不包括开口部的板(plate)形态。

245.图24是用于说明根据本发明的另一实施例的感测电极及桥接电极的图。

246.图24是沿图22的iii-iii'线剖切的另一剖面图。

247.第一感测电极sc1及第二感测电极sc2可以通过图案化第一感测电极层ism1而构成,从而可以位于封装膜tfe上。

248.第一感测绝缘膜isi1可以覆盖第一感测电极sc1及第二感测电极sc2,且可以包括暴露第一感测电极sc1、sc2的一部分的接触孔cnt。

249.桥接电极cp1可以通过图案化第二感测电极层ism2而构成,从而可以位于第一感测绝缘膜isi1上。桥接电极cp1可以通过接触孔cnt而与第一感测电极sc1连接。

250.图25至图27是用于说明根据本发明的另一实施例的包括像素的显示装置的图。

251.图25是用于说明根据本发明的一实施例的显示部及显示驱动部的图。

252.参照图25,显示驱动部210可以包括时序控制部11及数据驱动部12,显示部110可以包括扫描驱动部13、像素部14及发光驱动部15。但是,如上所述,各个功能部可以根据显示装置1的规格(specification)而多样地构成。即,可以集成于一个ic,也可以集成于多个ic,或者也可以安装于显示基板111。

253.时序控制部11可以从处理器9接收针对各个显示帧时段的灰度及时序信号。在此,处理器可以对应于图形处理单元(gpu:graphics processing unit)、中央处理单元(cpu:centralprocessing unit)、应用处理器(ap:application processor)等中的至少一个。时序信号可以包括垂直同步信号(vertical synchronization signal)、水平同步信号(horizontal synchronization signal)、数据使能信号(data enable signal)等。

254.垂直同步信号的各个周期(cycle)可以对应于各个显示帧时段。水平同步信号的各个周期(cycle)可以对应于各个水平时段(horizontal period)。灰度可以对应于数据使能信号的使能电平的脉冲而在各个水平时段中以水平线(horizontal line)为单位供应。水平线可以指连接到相同的扫描线及发光线的像素(例如,像素行)。

255.时序控制部11可以与显示装置1的规格对应地渲染(rendering)灰度。例如,处理器9可以针对各个单位点(unit dot)提供红色灰度、绿色灰度、蓝色灰度。例如,在像素部14为rgb条纹(stripe)结构的情况下,像素可以一对一地对应于各个灰度。在这种情况下,可能不需要渲染灰度。但是,例如,在像素部14为五片瓦(pentile)结构的情况下,由于相邻的单位点之间共享像素,因此像素可能不一对一地对应于各个灰度。在这种情况下,可能需要渲染灰度。被渲染或未被渲染的灰度可以提供到数据驱动部12。并且,时序控制部11可以向数据驱动部12提供数据控制信号。并且,时序控制部11可以向扫描驱动部13提供扫描控制信号,并可以向发光驱动部15提供发光控制信号。

256.数据驱动部12可以利用从时序控制部11接收的灰度及数据控制信号来生成要提供给数据线dl1、dl2、dl3、dl4、

……

、dln的数据电压(即,数据信号)。n可以是大于0的整数。

257.扫描驱动部13可以利用从时序控制部11接收的扫描控制信号(例如,时钟信号、扫描开始信号等)来生成要提供给扫描线sl0、sl1、sl2、

……

、slm的扫描信号。扫描驱动部13可以向扫描线sl1、sl2依次供应具有导通电平的脉冲的扫描信号。扫描驱动部13可以包括以移位寄存器(shift register)形态构成的扫描级。扫描驱动部13可以根据时钟信号的控制,以将作为导通电平的脉冲形态的扫描开始信号依次传递给下一个扫描级的方式生成扫描信号。m可以是大于0的整数。

258.发光驱动部15可以利用从时序控制部11接收的发光控制信号(例如,时钟信号、发光停止信号等)来生成要提供给发光线el1、el2、el3、

……

、elo的发光信号。发光驱动部15可以向发光线el1至elo依次供应具有截止电平的脉冲的发光信号。发光驱动部15可以包括以移位寄存器形态构成的发光级。发光驱动部15可以根据时钟信号的控制,以将作为截止电平的脉冲形态的发光停止信号依次传递给下一个发光级的方式生成发光信号。o可以是大于0的整数。

259.像素部14包括像素。各个像素pxij可以连接到对应的数据线、扫描线及发光线。像素可以包括发出第一颜色的光的像素、发出第二颜色的光的像素以及发出第三颜色的光的像素。第一颜色、第二颜色及第三颜色可以是彼此不同的颜色。例如,第一颜色可以是红色、绿色及蓝色中的一种颜色,第二颜色可以是红色、绿色及蓝色中的不是第一颜色的一种颜色,第三颜色可以是红色、绿色及蓝色中的不是第一颜色及第二颜色的剩余颜色。并且,作为第一颜色至第三颜色,也可以使用品红色(magenta)、青色(cyan)及黄色(yellow)来代替红色、绿色及蓝色。

260.图26是用于说明根据本发明的一实施例的像素的图。

261.参照图26,像素pxij包括晶体管t1、t2、t3、t4、t5、t6、t7、存储电容器cst及发光元件ld。

262.以下,以利用p型晶体管构成的电路为例进行说明。然而,本领域技术人员将能够通过改变施加到栅极端子的电压的极性来设计利用n型晶体管构成的电路。类似地,本领域技术人员将能够设计利用p型晶体管及n型晶体管的组合构成的电路。将在栅极电极与源极电极之间的电压差沿负方向增加时电流量增加的晶体管统称为p型晶体管。将在栅极电极与源极电极之间的电压差沿正方向增加时电流量增加的晶体管统称为n型晶体管。晶体管可以构成为薄膜晶体管(tft:thin film transistor)、场效应晶体管(fet:field effect transistor)、双极结晶体管(bjt:bipolar junction transistor)等的多样的形态构成。

263.第一晶体管t1的栅极电极可以连接到第一节点n1,第一电极可以连接到第二节点n2,并且第二电极可以连接到第三节点n3。第一晶体管t1可以命名为驱动晶体管。

264.第二晶体管t2的栅极电极可以连接到扫描线sli1,第一电极可以连接到数据线dlj,并且第二电极可以连接到第二节点n2。第二晶体管t2可以命名为扫描晶体管。

265.第三晶体管t3的栅极电极可以连接到扫描线sli2、第一电极可以连接到第一节点n1,并且第二电极可以连接到第三节点n3。第三晶体管t3可以命名为二极管连接晶体管。

266.第四晶体管t4的栅极电极可以连接到扫描线sli3,第一电极可以连接到第一节点n1,并且第二电极可以连接到初始化线intl。第四晶体管t4可以命名为栅极初始化晶体管。

267.第五晶体管t5的栅极电极可以连接到第i条发光线eli,第一电极可以连接到第一电源线elvddl,并且第二电极可以连接到第二节点n2。第五晶体管t5可以命名为发光晶体管。在另一实施例中,第五晶体管t5的栅极电极也可以连接到与连接于第六晶体管t6的栅极电极的发光线不同的发光线。

268.第六晶体管t6的栅极电极可以连接到第i条发光线eli,第一电极可以连接到第三节点n3,并且第二电极可以连接到发光元件ld的阳极。第六晶体管t6可以命名为发光晶体管。在另一实施例中,第六晶体管t6的栅极电极也可以连接到与连接于第五晶体管t5的栅极电极的发光线不同的发光线。

269.第七晶体管t7的栅极电极可以连接到扫描线sli4,第一电极可以连接到初始化线intl,并且第二电极可以连接到发光元件ld的阳极。第七晶体管t7可以命名为发光元件初始化晶体管。

270.存储电容器cst的第一电极可以连接到第一电源线elvddl,且第二电极可以连接到第一节点n1。

271.发光元件ld的阳极可以连接到第六晶体管t6的第二电极,且阴极可以连接到第二电源线elvssl。发光元件ld可以是发光二极管。发光元件ld可以利用有机发光元件(organic light emitting diode)、无机发光元件(inorganic light emitting diode)、量子点/阱发光元件(quantum dot/well light emitting diode)等构成。发光元件ld可以以第一颜色、第二颜色及第三颜色中的任意一种颜色发光。并且,在本实施例中,在各个像素仅配备有一个发光元件ld,但在另一实施例中,也可以在各个像素配备有多个发光元件。此时,多个发光元件可以以串联、并联、串并联等方式连接。

272.第一电源线elvddl可以被施加第一电源电压,第二电源线elvssl可以被施加第二电源电压,初始化线intl可以被施加初始化电压。例如,第一电源电压可以大于第二电源电压。例如,初始化电压可以等于或大于第二电源电压。例如,初始化电压可以对应于可提供的数据电压中最小大小的数据电压。在另一示例中,初始化电压的大小可以小于可提供的数据电压的大小。

273.图27是用于说明图26的像素的示例性的驱动方法的图。

274.以下,为了便于说明,假设扫描线sli1、sli2、sli4为第i条扫描线sli,且扫描线sli3为第i-1条扫描线sl(i-1)的情况。但是,根据实施例,扫描线sli1、sli2、sli3、sli4的连接关系可以多样。例如,扫描线sli4也可以是第i-1条扫描线或第i 1条扫描线。

275.首先,第i条发光线eli被施加截止电平(逻辑高电平(logic high level))的发光信号,数据线dlj被施加针对第i-1个像素的数据电压data(i-1)j,并且扫描线sli3被施加导通电平(逻辑低电平(logic low level))的扫描信号。逻辑电平的高/低可以根据晶体管是p型还是n型而变化。

276.此时,由于扫描线sli1、sli2被施加截止电平的扫描信号,因此第二晶体管t2处于截止状态,并防止针对第i-1个像素的数据电压data(i-1)j引入到像素pxij。

277.此时,由于第四晶体管t4处于导通状态,因此第一节点n1与初始化线intl连接,以初始化第一节点n1的电压。由于发光线eli被施加截止电平的发光信号,因此晶体管t5、t6处于截止状态,并防止由于施加初始化电压的过程而导致的发光元件ld的不必要的发光。

278.接下来,数据线dlj被施加针对第i个像素pxij的数据电压dataij,并且扫描线

sli1、sli2被施加导通电平的扫描信号。据此,晶体管t2、t1、t3处于导通状态,并且数据线dlj与第一节点n1电连接。因此,从数据电压dataij减去第一晶体管t1的阈值电压的补偿电压施加到存储电容器cst的第二电极(即,第一节点n1),并且存储电容器cst保持对应于第一电源电压与补偿电压之差的电压。这样的时段可以命名为阈值电压补偿时段或数据写入时段。

279.并且,在扫描线sli4为第i条扫描线的情况下,由于第七晶体管t7处于导通状态,因此发光元件ld的阳极与初始化线intl连接,并且发光元件ld被初始化为对应于初始化电压与第二电源电压的电压差的电荷量。

280.此后,随着第i条发光线eli被施加导通电平的发光信号,晶体管t5、t6可以导通。因此,形成连接第一电源线elvddl、第五晶体管t5、第一晶体管t1、第六晶体管t6、发光元件ld及第二电源线elvssl的驱动电流路径。

281.根据在存储电容器cst保持的电压,调节在第一晶体管t1的第一电极和第二电极流动的驱动电流量。发光元件ld以对应于驱动电流量的亮度发光。发光元件ld发光至发光线eli被施加截止电平的发光信号为止。

282.当发光信号为导通电平时,接收对应的发光信号的像素可以处于显示状态。因此,可以将发光信号为导通电平的时段称为发光时段ep(或者,发光允许时段)。并且,当发光信号为截止电平时,接收对应的发光信号的像素可以处于非显示状态。因此,可以将发光信号为截止电平的时段称为非发光时段nep(或者,发光不允许时段)。

283.图27中说明的非发光时段nep用于防止像素pxij在经过初始化时段及数据写入时段的期间以不期望的亮度发光。

284.在写入像素pxij的数据被保持的期间(例如,一帧时段),可以追加提供一次以上的非发光时段nep。这可以是为了通过减少像素pxij的发光时段ep来有效地表现出低灰度,或者对图像的运动(motion)进行平滑的模糊(blur)处理。

285.目前为止,所参照的附图和所记载的发明的详细说明仅是本发明的示例性的内容,这仅仅为了说明本发明的目的而使用,并非为了限定含义或限制权利要求书中记载的本发明的范围而使用。因此,本发明所属技术领域中具有普通知识的人员应理解,可以由此而实现多样的变形及等同的其他实施例。因此,本发明的真正的技术保护范围应由权利要求书的技术思想来确定。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。