用于执行测试的电子器件

1.相关申请的交叉引用

2.本技术要求于2021年5月21日向韩国知识产权局提交的申请号为10-2021-0065625的韩国专利申请的优先权,其全部内容通过引用合并于此。

技术领域

3.本公开涉及一种用于执行测试的电子器件。

背景技术:

4.在半导体器件装运出厂之前,应该执行验证半导体器件是否具有故障的测试。就此而言,为了减少测试所需的时间,可以使用同时测试多个半导体器件的方案。

技术实现要素:

5.在一个示例中,一种电子器件可以包括:掩蔽信号生成电路,其通过在执行测试掩蔽模式的时段期间接收熔丝数据来生成测试掩蔽信号;以及测试模式信号生成电路,当输入用于在内部电路中执行测试的测试命令时,其基于所述测试掩蔽信号来执行所述测试。

6.在一个示例中,一种电子器件可以包括:测试码生成电路,当输入用于在内部电路中执行测试的测试命令时,其生成用于设置测试模式的测试码;以及测试控制电路,当在执行测试掩蔽模式的时段期间输入所述测试命令时,其基于熔丝数据对每种测试模式控制所述测试的执行。

附图说明

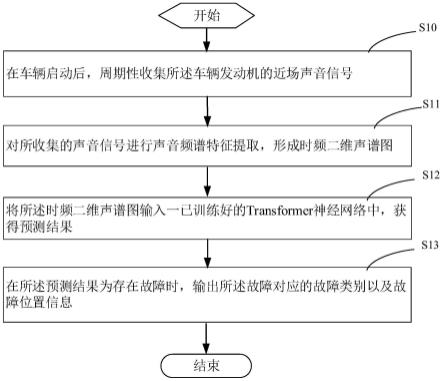

7.图1是图示根据本公开的示例的电子器件的结构的框图。

8.图2是图示图1中所示的掩蔽信号生成电路的示例的电路图。

9.图3是图示图1中所示的测试模式信号生成电路的示例的图。

10.图4是帮助解释图1中所示的电子器件的操作的时序图。

11.图5是图示应用了图1所示的电子器件的系统的示例的结构的框图。

具体实施方式

12.在以下示例的描述中,术语“预设”指示当参数在过程或算法中使用时,参数的数值是预先确定的。根据示例,可以在过程或算法开始时或在过程或算法执行期间设置参数的数值。

13.诸如“第一”和“第二”的术语用于区分各种组件,因此不受组件的限制。例如,第一组件可以称为第二组件,反之亦然。

14.当一个组件称为“耦接”或“连接”到另一个组件时,应该理解的是,这些组件彼此可以直接耦接或连接,或者通过介于它们之间的另一个组件彼此耦接或连接。另一方面,当一个组件称为“直接耦接”或“直接连接”到另一组件时,应当理解的是,这些组件彼此直接

耦接或连接,而无需另一个组件介于它们之间。

[0015]“逻辑高电平”和“逻辑低电平”用于描述信号的逻辑电平。具有“逻辑高电平”的信号与具有“逻辑低电平”的信号相区别。例如,当具有第一电压的信号对应于具有“逻辑高电平”的信号时,具有第二电压的信号可以对应于具有“逻辑低电平”的信号。根据示例,“逻辑高电平”可以设置为高于“逻辑低电平”的电压。根据示例,信号的逻辑电平可以设置为不同的逻辑电平或相反的逻辑电平。例如,根据示例可以将具有逻辑高电平的信号设置为具有逻辑低电平,并且根据示例可以将具有逻辑低电平的信号设置为具有逻辑高电平。

[0016]

在下文中,将通过示例更详细地描述本公开的教导。这些示例仅用于例示本公开的教导,本公开的范围不限于这些示例。

[0017]

本公开的一些示例涉及用于执行测试的电子器件。

[0018]

根据本公开,当在执行测试掩蔽模式的时段期间输入用于执行测试的测试命令时,可以基于熔丝数据来控制是否执行测试。因此,当同时测试多个器件时,可以对各个器件不同地控制是否执行测试,从而提高每个测试的灵活性并减少每次测试所需的时间。

[0019]

图1是图示根据本公开的示例的电子器件100的结构的框图。如图1中所示,电子器件100可以包括:测试命令生成电路(tcmd gen)101、测试码生成电路(tcd gen)103、掩蔽模式信号生成电路(tmm gen)105、区域选择信号生成电路(fz_sel gen)107、熔丝数据存储电路(fzd存储电路)109、测试控制电路111和内部电路117。

[0020]

电子器件100可以利用存储器件来实现,该存储器件基于设置码ca来存储并输出数据dq。电子器件100可以基于设置码ca来执行各种内部操作,例如写入操作和读取操作。设置码ca可以包括关于命令和地址的信息。可以从电子器件100外部的外部设备来应用设置码ca和数据dq的每一个。作为示例,可以从测试设备(图5的1100)应用设置码ca和数据dq的每一个。作为另一示例,可以从存储器控制器(未示出)应用设置码ca和数据dq的每一个。可以基于实施例不同地设置设置码ca和数据dq的每一个的比特位数。

[0021]

测试命令生成电路101可以基于设置码ca来生成测试命令tcmd。测试命令生成电路101可以通过将具有用于执行测试的组合的设置码ca进行解码来激活测试命令tcmd。测试命令tcmd可以被激活以在内部电路117中执行测试。

[0022]

测试码生成电路103可以基于测试命令tcmd从设置码ca生成测试码tcd。当测试命令tcmd被激活时,测试码生成电路103可以提取具有用于设置测试模式的组合的设置码ca,并输出提取的设置码ca作为测试码tcd。可以基于实施例不同地设置测试码tcd的位数。测试码tcd可以具有用于设置在内部电路117中执行的测试模式的组合。例如,测试码tcd的第一组合可以设置为用于在内部电路117中执行第一测试模式的组合,而测试码tcd的第二组合可以设置为用于在内部电路117执行第二测试模式的组合。每种测试模式可以独立地设置施加到内部电路117的应力类型。例如,第一测试模式可以设置为通过调整施加到内部电路117的内部电压的电平来施加应力的测试,而第二测试模式可以设置为通过调整施加到内部电路117信号的脉冲宽度来施加应力的测试。此外,每种测试模式可以不同地设置应力的程度。例如,第一测试模式可以设置为通过将施加到内部电路117的内部电压的电平设置为大于在第二测试模式中的电平来施加应力的测试。在另一示例中,第一测试模式可以设置为通过将施加到内部电路117的信号的脉冲宽度减小得比在第二测试模式中的更多来施加应力的测试。

[0023]

掩蔽模式信号生成电路105可以基于设置码ca来生成测试掩蔽模式信号tmm。掩蔽模式信号生成电路105可以通过将具有用于执行测试掩蔽模式的组合的设置码ca进行解码来激活测试掩蔽模式信号tmm。掩蔽模式信号生成电路105可以通过对具有用于结束测试掩蔽模式的组合的设置码ca进行解码来去激活测试掩蔽模式信号tmm。测试掩蔽模式信号tmm可以在执行测试掩蔽模式的时段期间被激活。

[0024]

区域选择信号生成电路107可以基于设置码ca来生成熔丝区域选择信号fz_sel。区域选择信号生成电路107可以基于用于控制熔丝数据存储电路109的操作的设置码ca来生成熔丝区域选择信号fz_sel。熔丝区域选择信号fz_sel可以具有与熔丝区域109_1至109_n的每一个相对应的组合。例如,熔丝区域选择信号fz_sel可以具有与第一熔丝区域109_1相对应的第一组合和与第二熔丝区域109_2相对应的第二组合。当生成用于在内部电路117中执行测试的测试命令tcmd时,可以生成熔丝区域选择信号fz_sel。

[0025]

熔丝数据存储电路109可以包括多个熔丝区域109_1至109_n,每个熔丝区域存储熔丝数据fzd。可以基于实施例不同地设置熔丝数据fzd的位数。熔丝数据存储电路109可以基于晶圆测试的结果,对每种测试模式将关于是否执行测试的信息作为熔丝数据fzd存储在多个熔丝区域109_1至109_n的每一个中。例如,熔丝数据存储电路109可以基于晶圆测试的结果将关于是否执行第一测试模式的信息作为熔丝数据fzd存储在第一熔丝区域109_1中。熔丝数据存储电路109可以基于晶圆测试的结果,将关于是否执行第二测试模式的信息作为熔丝数据fzd存储在第二熔丝区域109_2中。晶圆测试是指当电子器件100处于晶圆状态时执行的测试。熔丝数据存储电路109可以基于晶圆测试的结果来设置熔丝数据fzd的模式。多个熔丝区域109_1至109_n的每一个可以利用电可编程电熔丝(e-fuse)来实现。熔丝数据存储电路109可以利用其中多个熔丝区域109_1至109_n以阵列形式布置的阵列熔断电熔丝(array rupture e-fuse,are)电路来实现。

[0026]

熔丝数据存储电路109可以基于熔丝区域选择信号fz_sel来输出熔丝数据fzd和熔丝时钟fz_clk。熔丝区域选择信号fz_sel的每个组合可以对应于多个熔丝区域109_1至109_n的每一个。当生成测试命令tcmd时,熔丝数据存储电路109可以基于熔丝区域选择信号fz_sel来输出存储在多个熔丝区域109_1至109_n的一个中的熔丝数据fzd。例如,熔丝数据存储电路109可以基于熔丝区域选择信号fz_sel的第一组合,将熔丝时钟fz_clk连同存储在第一熔丝区域109_1中的熔丝数据fzd一起输出。熔丝数据存储电路109可以基于熔丝区域选择信号fz_sel的第二组合,将熔丝时钟fz_clk连同存储在第二熔丝区域109_2中的熔丝数据fzd一起输出。

[0027]

测试控制电路111可以包括掩蔽信号生成电路(tmsk gen)113和测试模式信号生成电路(tm gen)115。测试控制电路111可以基于测试掩蔽模式信号tmm、熔丝数据fzd、熔丝时钟fz_clk、测试命令tcmd和测试码tcd来生成测试模式信号tm。

[0028]

当用于执行测试掩蔽模式的测试掩蔽模式信号tmm被去激活时,测试控制电路111可以基于测试命令tcmd,根据测试码tcd的组合来生成测试模式信号tm。测试模式信号tm可以被激活以在与测试码tcd的组合相对应的测试模式下执行测试。例如,第一测试模式信号tm1可以被激活以在第一测试模式下执行测试,而第二测试模式信号tm2可以被激活以在第二测试模式下执行测试。

[0029]

当在执行测试掩蔽模式的时段期间输入测试命令tcmd时,测试控制电路111可以

与熔丝时钟fz_clk同步地接收熔丝数据fzd。当在执行测试掩蔽模式的时段期间输入测试命令tcmd时,测试控制电路111可以基于熔丝数据fzd来控制是否执行测试。当在执行测试掩蔽模式期间输入测试命令tcmd时,测试控制电路111可以通过检测熔丝数据fzd的模式是否为预设模式来控制是否执行测试。更详细地,当在执行测试掩蔽模式期间熔丝数据fzd的模式为预设模式时,测试控制电路111可以对测试模式信号tm去激活。相反地,当在执行测试掩蔽模式期间熔丝数据fzd的模式与预设模式不同时,测试控制电路111可以基于测试码tcd的组合来生成测试模式信号tm。当在执行测试掩蔽模式的时段期间输入测试命令tcmd时,测试控制电路111可以基于熔丝数据fzd来控制是否对每种测试模式执行测试。例如,当在执行测试掩蔽模式的时段期间输入测试命令tcmd时,测试控制电路111可以基于存储在第一熔丝区域109_1中的熔丝数据fzd来控制是否执行第一测试模式。当在执行测试掩蔽模式的时段期间输入测试命令tcmd时,测试控制电路111可以基于存储在第二熔丝区域109_2中的熔丝数据fzd来控制是否执行第二测试模式。

[0030]

掩蔽信号生成电路113可以通过基于测试掩蔽模式信号tmm接收熔丝数据fzd和熔丝时钟fz_clk来生成测试掩蔽信号tmsk。可以生成测试掩蔽信号tmsk以控制是否执行测试。在执行测试掩蔽模式的时段期间,掩蔽信号生成电路113可以与熔丝时钟fz_clk同步地接收熔丝数据fzd。掩蔽信号生成电路113可以通过在执行测试掩蔽模式的时段期间检测熔丝数据fzd的模式是否为预设模式来生成测试掩蔽信号tmsk。当在执行测试掩蔽模式的时段期间熔丝数据fzd的模式为预设模式时,掩蔽信号生成电路113可以激活测试掩蔽信号tmsk。例如,当熔丝数据fzd以逻辑高电平输入时,掩蔽信号生成电路113可以激活测试掩蔽信号tmsk。又例如,当熔丝数据fzd的比特位中的至少一比特位以逻辑高电平输入时,掩蔽信号生成电路113可以激活测试掩蔽信号tmsk。当在执行测试掩蔽模式的时段期间熔丝数据fzd的模式与预设模式不同时,掩蔽信号生成电路113可以对测试掩蔽信号tmsk去激活。当测试掩蔽模式信号tmm被去激活时,掩蔽信号生成电路113可以对测试掩蔽信号tmsk去激活。

[0031]

当输入用于执行测试的测试命令tcmd时,测试模式信号生成电路115可以基于测试码tcd和测试掩蔽信号tmsk来生成测试模式信号tm。当输入用于执行测试的测试命令tcmd时,测试模式信号生成电路115可以基于测试掩蔽信号tmsk来执行测试。更详细地,当在测试掩蔽信号tmsk被激活的时段期间输入测试命令tcmd时,测试模式信号生成电路115可以对测试模式信号tm去激活。相反地,当在测试掩蔽信号tmsk被去激活的时段期间输入测试命令tcmd时,测试模式信号生成电路115可以根据测试码tcd的组合来生成测试模式信号tm。例如,当在测试掩蔽信号tmsk被去激活的时段期间输入测试命令tcmd时,测试模式信号生成电路115可以基于测试码tcd的第一组合来激活第一测试模式信号tm1。当在测试掩蔽信号tmsk被去激活的时段期间输入测试命令tcmd时,测试模式信号生成电路115可以基于测试码tcd的第二组合来激活第二测试模式信号tm2。

[0032]

内部电路117可以包括存储并输出数据dq的多个存储单元(未示出)。更详细地,内部电路117可以在执行写入操作时接收数据dq并将接收到的数据dq存储在多个存储单元中,以及可以在执行读取操作时输出存储在多个存储单元中的数据dq。内部电路117可以在与测试模式信号tm相对应的测试模式下执行测试。例如,当激活第一测试模式信号tm1时内部电路117可以在第一测试模式下执行测试,而当激活第二测试模式信号tm2时,内部电路

117可以在第二测试模式下执行测试。

[0033]

图2是图示图1中所示的掩蔽信号生成电路113的示例的电路图。如图2中所示,掩蔽信号生成电路113可以包括检测信号生成电路121和掩蔽信号输出电路123。

[0034]

检测信号生成电路121可以基于熔丝数据fzd、熔丝时钟fz_clk和复位信号rst来生成检测信号det。检测信号生成电路121可以与熔丝时钟fz_clk同步地接收熔丝数据fzd。在本实施例中,检测信号生成电路121可以与熔丝时钟fz_clk同步地逐位来接收熔丝数据fzd。当熔丝数据fzd的模式为预设模式时,检测信号生成电路121可以激活检测信号det。在本实施例中,预设模式可以设置为其中熔丝数据fzd的比特位之中的至少一位设置为逻辑高电平的模式。检测信号生成电路121可以通过基于复位信号rst执行初始化操作来去激活检测信号det。在从检测信号生成电路121接收到熔丝数据fzd的时间点起的预设时段之后,复位信号rst可以被激活以执行初始化操作。可以根据实施例不同地设置预设时段。复位信号rst可以从用于初始化操作的设置码ca(参见见图1)生成。检测信号生成电路121可以包括反相器121_1以及与非门121_2、121_3和121_4。当与非门121_2的输出信号具有逻辑低电平时,检测信号生成电路121可以将检测信号det激活为逻辑高电平。当反相器121_1的输出信号具有逻辑低电平时,检测信号生成电路121可以对检测信号det去激活而为逻辑低电平。

[0035]

掩蔽信号输出电路123可以基于测试掩蔽模式信号tmm、检测信号det和复位信号rst来生成测试掩蔽信号tmsk。当在执行测试掩蔽模式的时段期间检测信号det被激活时,掩蔽信号输出电路123可以激活测试掩蔽信号tmsk。当在执行测试掩蔽模式的时段期间检测信号det被去激活时,掩蔽信号输出电路123可以对测试掩蔽信号tmsk去激活。当测试掩蔽模式信号tmm被去激活时,掩蔽信号输出电路123可以对测试掩蔽信号tmsk去激活。当复位信号rst被激活时,掩蔽信号输出电路123可以通过执行初始化操作来对测试掩蔽信号tmsk去激活。掩蔽信号输出电路123可以包括反相器123_1以及与非门123_2、123_3、123_4和123_5。当与非门123_2的输出信号具有逻辑低电平时,掩蔽信号输出电路123可以将内部节点nd11激活为逻辑高电平。当反相器123_1的输出信号具有逻辑低电平时,掩蔽信号输出电路123可以内部节点nd11去激活为逻辑低电平。与非门123_5可以通过在测试掩蔽模式信号tmm被激活为逻辑高电平的时段期间反相和缓冲内部节点nd11的信号来输出测试掩蔽信号tmsk。与非门123_5可以在测试掩蔽模式信号tmm被去激活到逻辑低电平的时段期间对测试掩蔽信号tmsk去激活到逻辑高电平。

[0036]

图3是图示图1中所示的测试模式信号生成电路115的示例的图。如图3所示,测试模式信号生成电路115可以包括测试使能信号生成电路131和测试模式信号输出电路(tm输出电路)133。

[0037]

当输入测试命令tcmd时,测试使能信号生成电路131可以基于测试掩蔽信号tmsk来生成测试使能信号tmen。测试使能信号生成电路131可以在测试掩蔽信号tmsk被激活的时段期间对测试使能信号tmen去激活。当在测试掩蔽信号tmsk被去激活的时段期间输入测试命令tcmd时,测试使能信号生成电路131可以激活测试使能信号tmen。测试使能信号生成电路131可以包括与门131_1。与门131_1可以在测试掩蔽信号tmsk被激活为逻辑低电平的时段期间来将测试使能信号tmen去激活为逻辑低电平。与门131_1可以通过在测试掩蔽信号tmsk被去激活而为逻辑高电平的时段期间缓冲测试命令tcmd来输出测试使能信号tmen。

[0038]

测试模式信号输出电路133可以基于测试使能信号tmen,根据测试码tcd的组合来生成测试模式信号tm。测试模式信号输出电路133可以在测试使能信号tmen被激活的时段期间,基于测试码tcd的组合来生成测试模式信号tm。例如,在测试使能信号tmen被激活的时段期间,测试模式信号输出电路133可以基于测试码tcd的第一组合来激活用于执行第一测试模式的第一测试模式信号tm1。在测试使能信号tmen被激活的时段期间,测试模式信号输出电路133可以基于测试码tcd的第二组合来激活用于执行第二测试模式的第二测试模式信号tm2。当测试使能信号tmen被去激活时,测试模式信号输出电路133可以去激活测试模式信号tm。

[0039]

图4是用于帮助解释在图1所示的电子器件100中控制是否执行测试的操作的时序图。

[0040]

在时间点t10,掩蔽模式信号生成电路105可以激活用于执行测试掩蔽模式的测试掩蔽模式信号tmm。

[0041]

在时间点t11,熔丝数据存储电路109可以基于熔丝区域选择信号fz_sel,将熔丝时钟fz_clk连同存储在第一熔丝区域109_1中的熔丝数据fzd一起输出。当熔丝数据fzd的模式为预设模式时,检测信号生成电路12(参见图2)可以激活检测信号det。当在测试掩蔽模式信号tmm被激活的时段期间检测信号det被激活到逻辑高电平时,掩蔽信号输出电路123(参见图2)可以激活测试掩蔽信号tmsk。

[0042]

在时间点t12,测试命令生成电路101可以生成测试命令tcmd。测试码生成电路103可以生成用于执行第一测试模式t1的测试码tcd。测试模式信号生成电路115可以基于激活的测试掩蔽信号tmsk来去激活测试使能信号tmen(参见图3)。

[0043]

在时间点t13,检测信号生成电路121(参见图2)可以基于激活的复位信号rst(参见图2)来去激活检测信号det。掩蔽信号输出电路123(参见图2)可以基于激活的复位信号rst来去激活测试掩蔽信号tmsk。

[0044]

在时间点t21,熔丝数据存储电路109可以基于熔丝区域选择信号fz_sel,将熔丝时钟fz_clk连同存储在第二熔丝区域109_2中的熔丝数据fzd一起输出。当熔丝数据fzd的模式不同于预设模式时,检测信号生成电路121(参见图2)可以来去激活检测信号det。当在测试掩蔽模式信号tmm被激活的时段期间检测信号det被去激活时,掩蔽信号输出电路123(参见图2)可以来去激活测试掩蔽信号tmsk。

[0045]

在时间点t22,测试命令生成电路101可以生成测试命令tcmd。测试码生成电路103可以生成用于执行第二测试模式t2的测试码tcd。测试模式信号生成电路115可以基于去激活的测试掩蔽信号tmsk和激活的测试命令tcmd来激活测试使能信号tmen(参见图3)。

[0046]

在时间点t23,检测信号生成电路121(参见图2)可以基于激活的复位信号rst(参见图2)来去激活检测信号det。掩蔽信号输出电路123(参见图2)可以基于激活的复位信号rst来去激活测试掩蔽信号tmsk。

[0047]

图5是图示应用了图1中所示的电子器件100的系统1000的示例的结构的框图。如图5中所示,系统1000可以包括测试设备1100和多个封装件(pkg)1200《1:k》。多个封装件1200《1:k》的每一个可以使用处于封装状态的电子器件100来实现。“k”可以设置为等于或大于2的自然数。多个封装件1200《1:k》的每一个可以处于基于晶圆测试的结果将熔丝数据fzd存储在熔丝数据存储电路109中的状态。

[0048]

测试设备1100可以将设置码ca(参见图1)输出至多个封装件1200《1:k》。多个封装件1200《1:k》可以共享信号线,通过该信号线从测试设备1100来发送设置码ca。测试设备1100可以将数据dq(参见图1)发送至多个封装件1200《1:k》并且从多个封装件1200《1:k》接收数据dq。多个封装件1200《1:k》可以共享信号线,通过该信号线从测试设备1100来发送数据dq。

[0049]

测试设备1100可以输出用于在多个封装件1200《1:k》中执行测试的设置码ca(参见图1)。例如,测试设备1100可以将用于执行第一测试模式的设置码ca输出至多个封装件1200《1:k》。测试设备1100可以将用于执行第二测试模式的设置码ca输出至多个封装件1200《1:k》。

[0050]

多个封装件1200《1:k》的每一个可以基于存储在熔丝数据存储电路109(参见图1)中的熔丝数据fzd(参见图1)对每种测试模式来控制是否执行测试。例如,第一封装件1200《1》可以执行第一测试模式,而第二封装件1200《2》可以不执行第一测试模式。相反地,第一封装件1200《1》可以不执行第二测试模式,而第二封装件1200《2》可以执行第二测试模式。

[0051]

从以上描述中显而易见是,根据本公开,当在执行测试掩蔽模式的时段期间输入用于执行测试的测试命令时,可以基于熔丝数据来控制是否执行测试。因此,当同时测试多个器件时,可以对各个器件不同地控制是否执行测试,从而提高每个测试的灵活性并减少每个测试所需的时间。

[0052]

尽管已经出于说明的目的公开了本教导的一些示例,但是本领域技术人员将理解的是,可以进行各种修改、添加和替换而不背离所附权利要求所限定的本教导的范围和精神。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。