一种led芯片及其制备方法

技术领域

1.本发明涉及半导体技术领域,特别涉及一种led芯片及其制备方法。

背景技术:

2.发光二极管,简称为led,是一种常用的发光器件,通过电子与空穴复合释放能量发光。在led芯片工艺中通常用透明导电层ito(氧化铟锡)作为电流扩层并提高发光效率。在制作ito层时通常先用icp(电感耦合等离子光谱发生仪)刻蚀出mesa台阶面,露出p型半导体层,然后在上面蒸镀ito层,并通过光刻出ito图形,最后通过ito蚀刻,最终在p型半导体层上形成ito层。因为ito的导电性,当部分ito残留在pn分界处时,将产生漏电,而为了减少漏电需增大腐蚀量来减少ito的面积,影响了整个发光效率且不能有效的避免漏电的产生。

技术实现要素:

3.本发明所要解决的技术问题是:提供一种led芯片及其制备方法,能够增加led芯片的发光效率。

4.为了解决上述技术问题,本发明采用的技术方案为:

5.一种led芯片,包括衬底、n型半导体层、量子阱层、p型半导体层、ito层、绝缘层以及电极;

6.所述衬底的一面设置有所述n型半导体层,所述n型半导体层远离所述衬底的一面的第一预设区域依次层叠有所述量子阱层、所述p型半导体层;

7.所述电极包括n电极和p电极,所述p型半导体层上方依次设置有ito层和p电极;

8.所述n型半导体层远离所述衬底的一面的第二预设区域设置有所述n电极;

9.所述n型半导体层远离所述衬底的一面设置有所述绝缘层,且所述绝缘层围绕所述量子阱层和所述p型半导体层以及所述n电极设置。

10.为了解决上述技术问题,本发明采用的另一种技术方案为:

11.一种led芯片制备方法,包括步骤:

12.在衬底上依次生长n型半导体层、量子阱层和p型半导体层;

13.刻蚀所述量子阱层和所述p型半导体层,保留第一预设区域的所述量子阱层和所述p型半导体层;

14.在所述n型半导体层远离所述衬底的一面沉积绝缘层,所述绝缘层围绕所述第一预设区域和第二预设区域设置;

15.在所述p型半导体层远离所述量子阱层的一面溅射ito层,并在所述ito层远离所述p型半导体层的一面蒸镀p电极;

16.在所述n型半导体层远离所述衬底的一面的第二预设区域蒸镀n电极。

17.本发明的有益效果在于:在n型半导体层远离衬底的一面沉积绝缘层,且绝缘层围绕量子阱层、p型半导体层以及n电极设置,因此在pn分界处优先覆盖绝缘材料,能够在mesa

刻蚀之后ito层溅射之前生成绝缘层,减少pn分界处因ito导电物质产生的微漏电;并且通过设置绝缘层,相较于现有技术能够提高ito层的面积,增加发光效率并提高芯片亮度,同时在应用端也能充分避免pn分界处的其他导电杂质驻留。

附图说明

18.图1为本发明实施例的一种led芯片的示意图;

19.图2为本发明实施例的一种led芯片制备方法的流程图;

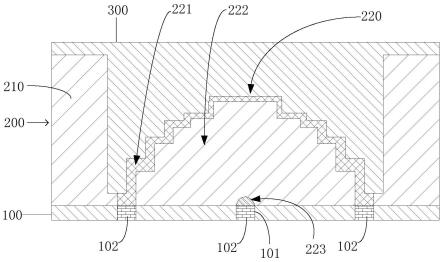

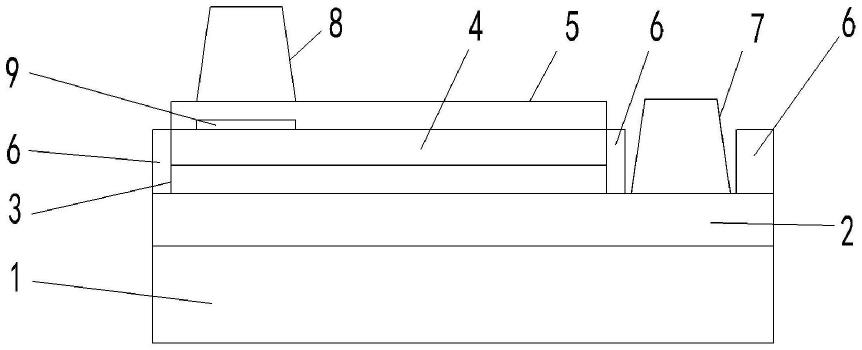

20.图3为现有技术中led芯片制备ito层时腐蚀前的示意图;

21.图4为现有技术中led芯片制备ito层时腐蚀后的示意图;

22.标号说明:

23.1、衬底;2、n型半导体层;3、量子阱层;4、p型半导体层;5、ito层;6、绝缘层;7、n电极;8、p电极;9、电流阻挡层。

具体实施方式

24.为详细说明本发明的技术内容、所实现目的及效果,以下结合实施方式并配合附图予以说明。

25.请参照图1,本发明实施例提供了一种led芯片,包括衬底、n型半导体层、量子阱层、p型半导体层、ito层、绝缘层以及电极;

26.所述衬底的一面设置有所述n型半导体层,所述n型半导体层远离所述衬底的一面的第一预设区域依次层叠有所述量子阱层、所述p型半导体层;

27.所述电极包括n电极和p电极,所述p型半导体层上方依次设置有ito层和p电极;

28.所述n型半导体层远离所述衬底的一面的第二预设区域设置有所述n电极;

29.所述n型半导体层远离所述衬底的一面设置有所述绝缘层,且所述绝缘层围绕所述量子阱层和所述p型半导体层以及所述n电极设置。

30.从上述描述可知,本发明的有益效果在于:在n型半导体层远离衬底的一面沉积绝缘层,且绝缘层围绕量子阱层、p型半导体层以及n电极设置,因此在pn分界处优先覆盖绝缘材料,能够在mesa刻蚀之后ito层溅射之前生成绝缘层,减少pn分界处因ito导电物质产生的微漏电;并且通过设置绝缘层,相较于现有技术能够提高ito层的面积,增加发光效率并提高芯片亮度,同时在应用端也能充分避免pn分界处的其他导电杂质驻留。

31.进一步地,所述绝缘层远离所述n型半导体层的一面与所述p型半导体层远离所述量子阱层的一面齐平。

32.由上述描述可知,n型半导体层上沉积顶面高度与p型半导体顶面高度相近的绝缘层,进一步减少pn分界处因ito导电物质产生的微漏电,并且便于ito层的制备,增加ito的面积,从而提高发光效率。

33.进一步地,还包括电流阻挡层;

34.所述ito层靠近所述p型半导体层的一面内嵌有所述电流阻挡层;

35.所述电流阻挡层的位置与所述p电极相对应。

36.由上述描述可知,在与p电极对应的ito层中设置电流阻挡层,能够保证芯片的正常运行。

37.进一步地,所述绝缘层的厚度为

38.进一步地,所述电极的厚度为

39.请参照图2,本发明另一实施例提供了一种led芯片制备方法,包括步骤:

40.在衬底上依次生长n型半导体层、量子阱层和p型半导体层;

41.刻蚀所述量子阱层和所述p型半导体层,保留第一预设区域的所述量子阱层和所述p型半导体层;

42.在所述n型半导体层远离所述衬底的一面沉积绝缘层,所述绝缘层围绕所述第一预设区域和第二预设区域设置;

43.在所述p型半导体层远离所述量子阱层的一面溅射ito层,并在所述ito层远离所述p型半导体层的一面蒸镀p电极;

44.在所述n型半导体层远离所述衬底的一面的所述第二预设区域蒸镀n电极。

45.由上述描述可知,在n型半导体层远离衬底的一面沉积绝缘层,且绝缘层围绕量子阱层、p型半导体层以及n电极设置,因此在pn分界处优先覆盖绝缘材料,能够在mesa刻蚀之后ito层溅射之前生成绝缘层,减少pn分界处因ito导电物质产生的微漏电;并且通过设置绝缘层,相较于现有技术能够提高ito层的面积,增加发光效率并提高芯片亮度,同时在应用端也能充分避免pn分界处的其他导电杂质驻留。

46.进一步地,在所述n型半导体层远离所述衬底的一面沉积绝缘层之后包括:

47.使用缓冲氧化物腐蚀所述绝缘层。

48.由上述描述可知,采用腐蚀法使绝缘层的腐蚀面产生粗糙度,从而提高p极侧壁出光效率。

49.进一步地,在所述n型半导体层远离所述衬底的一面沉积绝缘层还包括:

50.将所述绝缘层的高度沉积至与所述p型半导体层远离所述量子阱层的一面齐平的位置。

51.由上述描述可知,n型半导体上沉积顶面高度与p型半导体顶面高度相近的绝缘层,进一步减少pn分界处因ito导电物质产生的微漏电,并且便于ito层的制备,增加ito的面积,从而提高发光效率。

52.进一步地,在所述p型半导体层远离所述量子阱层的一面溅射ito层包括:

53.在所述p型半导体层远离所述量子阱层的一面的预设位置生长电流阻挡层;

54.在所述电流阻挡层和所述p型半导体层上方溅射ito层;

55.在所述ito层远离所述p型半导体层的一面蒸镀p电极包括:

56.在所述ito层远离所述p型半导体层的一面且与所述电流阻挡层对应的位置上蒸镀p电极。

57.由上述描述可知,在与p电极对应的ito层中设置电流阻挡层,能够保证芯片的正常运行。

58.进一步地,在所述n型半导体层远离所述衬底的一面沉积绝缘层还包括:沉积厚度为的绝缘层。

59.本发明上述的一种led芯片及其制备方法,适用于led芯片的制备,提高led芯片的发光效率,以下通过具体的实施方式进行说明:

60.实施例一

61.请参照图1,一种led芯片,包括衬底1、n型半导体层2、量子阱层3、p型半导体层4、ito层5、绝缘层6以及电极;

62.衬底1的一面设置有n型半导体层2,n型半导体层2远离衬底1的一面的第一预设区域依次层叠有量子阱层3和p型半导体层4;

63.具体的,在本实施例中,衬底1具体为蓝宝石衬底1;其中,蓝宝石衬底1的厚度为130-150μm,n型半导体层2的厚度为量子阱层3的厚度为

64.电极包括n电极7和p电极8,在本实施例中电极的厚度为

65.p型半导体层4上方依次设置有ito层5和p电极8,在本实施例中ito层5的厚度为

66.n型半导体层2远离衬底1的一面的第二预设区域设置有n电极7;

67.n型半导体层2远离衬底1的一面设置有绝缘层6,且绝缘层6围绕量子阱层3和p型半导体层4以及n电极7设置。

68.在一些实施例中,绝缘层6远离n型半导体层2的一面与p型半导体层4远离量子阱层3的一面齐平;在本实施例中,绝缘层6的厚度为量子阱层4的厚度加上p型半导体层3的厚度还加上n型半导体层2被icp刻蚀的厚度的总和,p型半导体层4的厚度为绝缘层的厚度为

69.在一些实施例中,led芯片中还包括电流阻挡层9,在本实施例中,电流阻挡层9的厚度为

70.ito层5靠近p型半导体层4的一面内嵌有电流阻挡层9,电流阻挡层9的位置与p电极8相对应。

71.因此,本实施例中的led芯片使pn结产生绝缘层,使ito导电层处于其上方,减少漏电并提高ito面积。

72.实施例二

73.请参照图2,一种led芯片制备方法,包括步骤:

74.s1、在衬底1上依次生长n型半导体层2、量子阱层3和p型半导体层4。

75.具体的,采用金属有机化学气相沉积方法及制备在蓝宝石衬底1上生长氮化镓基的n型半导体层2、量子阱层3,以及p型半导体层。

76.s2、刻蚀所述量子阱层3和所述p型半导体层4,保留第一预设区域的所述量子阱层3和所述p型半导体层4。

77.具体的,采用反应耦合等离子体方式进行mesa台阶面的刻蚀,深度达到n型半导体层2,保留光刻胶,此时p型半导体层4在光刻胶的保护下。

78.之后,进行清洗甩干工序,去除刻蚀后产生的残留,并充分保证n型半导体层2表面的清洁度:

79.(1)晶片放入清洗槽,鼓泡清洗120s后排放,加强对刻蚀槽内的浸润。

80.(2)甩干机设定转速500r/min,冲水维持100s,中速离子水冲水下将孔状结构中的水进进行置换,甩离残留物。

81.(3)甩干机设定转速2000r/min,并关闭冲水,打开吹气阀门,维持360s吹气,保证表面完全干燥。

82.s3、在所述n型半导体层2远离所述衬底1的一面沉积绝缘层6,所述绝缘层6分别围绕所述第一预设区域和第二预设区域设置。

83.其中,将所述绝缘层的高度沉积至与所述p型半导体层4远离所述量子阱层3的一面齐平的位置。

84.具体的,在n型半导体层2上沉积一层高致密绝缘层,厚度与icp刻蚀深度一致为之后去除光刻胶,此时pn结覆盖一层绝缘层,能够将pn分界面做绝缘保护,防止微漏电。

85.在本实施例中,所沉积的高致密绝缘层采用si02,沉积温度为300℃,调整硅烷100sccm,n2o 1000sccm,沉积厚度为保证此膜层的绝缘性。

86.在一些实施例中,使用缓冲氧化物腐蚀所述绝缘层6。

87.具体的,调整绝缘层光刻版图形,利用缓冲氧化物刻蚀液腐蚀绝缘层,采用二步腐蚀法使腐蚀面产生粗糙度,提高p极侧壁出光效率,去除光刻胶,露出n型半导体层2。

88.在本实施例中,可采用缓冲氢氟酸作为缓冲氧化物刻蚀液,缓冲氧化物刻蚀液具体由氢氟酸及氟化铵按比例配比1:12或1:6,根据腐蚀速率快慢的要求确定配备,1:6腐蚀更快。其中的二步腐蚀法是使用同样溶液,为了使用n电极9上方的绝缘层腐蚀干净,方便蒸镀电极,只保留pn分界处的绝缘层。

89.s4、在所述p型半导体层4远离所述量子阱层3的一面溅射ito层5,并在所述ito层5远离所述p型半导体层4的一面蒸镀p电极8。

90.具体的,在p型半导体层4远离量子阱层3的一面的预设位置生长电流阻挡层9,在电流阻挡层9和p型半导体层4上方溅射ito层5,并在ito层5远离p型半导体层4的一面且与电流阻挡层9对应的位置上蒸镀p电极8。

91.在本实施例中,可调整ito光刻版图形面积及曝光能量,将ito到mesa面4.0-5.0μm的间距调整为0μm,本实施例中改进前的ito面积为99500μm2,本实施例的ito面积为105000μm2,ito面积增大5.53%,用曝光方式对光刻版掩模进行图形转移复制出ito图形,用ito腐蚀液腐蚀显影后的ito,去除光刻胶,最终在p型半导体上形成ito层5。

92.s5、在所述n型半导体层2远离所述衬底1的一面的第二预设区域蒸镀n电极7。

93.具体的,本实施例中,用蒸镀机进行p、n孔金属蒸镀,形成p电极8和n电极7。

94.请参照图3和图4,在现有的方法中,ito层位于pn分界处上方进行全覆盖,采用ito蚀刻的方法除导电物质,因p、n有较垂直的刻蚀角度,残留的ito较难去除,增加ito腐蚀时间后,ito面积变小,影响发光效率。相较于现有的方法,本实施例中的led芯片制造方法,能在pn分界处优先覆盖绝缘材料,使mesa刻蚀后及ito前形成电流绝缘层,减少pn分界处因ito导电物质产生的微漏电,提高0.5%良率,并通过光刻工艺及图形工艺的改进,提高ito面积5%,增加发光效率,提高芯片亮度,同时在应用端也能充分避免pn分界处的其他导电杂质驻留。

95.综上所述,本发明提供的一种led芯片及其制备方法,在n型半导体层远离衬底的一面沉积绝缘层,且绝缘层围绕量子阱层、p型半导体层以及n电极设置,因此在pn分界处优先覆盖绝缘材料,能够在mesa刻蚀之后ito层溅射之前生成绝缘层,减少pn分界处因ito导电物质产生的微漏电;并且通过设置绝缘层,相较于现有技术能够提高ito层的面积,增加发光效率并提高芯片亮度,同时在应用端也能充分避免pn分界处的其他导电杂质驻留。

96.以上所述仅为本发明的实施例,并非因此限制本发明的专利范围,凡是利用本发明说明书及附图内容所作的等同变换,或直接或间接运用在相关的技术领域,均同理包括在本发明的专利保护范围内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。