用于制造微电子设备的方法

背景技术:

1.已经提出一种用于制造微电子设备、尤其是mems芯片设备的方法,所述微电子设备具有至少一个载体衬底,其中,在至少一个方法步骤中,将至少一个由金属导体制成的电动力学(elektrodynamischer)致动器施加到所述载体衬底上,所述金属导体至少大部分由铜构造。

技术实现要素:

2.本发明的出发点是一种用于制造微电子设备、尤其是mems芯片设备的方法,所述微电子设备具有至少一个载体衬底,其中,在至少一个方法步骤中,将由金属导体制成的至少一个电动力学致动器施加到所述载体衬底上,所述金属导体至少大部分由铜构造。

3.提出,在至少一个另外的方法步骤中,将至少一个压电致动器施加到所述载体衬底上。

4.优选,微电子设备构造为mems芯片设备、尤其是汽车电子mems芯片设备和/或消费电子mems芯片设备,其优选具有铜印制导线、尤其是具有低欧的铜印制导线,尤其是具有在0.010和0.020μohm

·

m之间的电阻率。例如,微电子设备构造为mems谐振器设备,尤其是构造为微镜、优选为双轴的微镜。例如,微电子设备构造为传感器、尤其是转速传感器。优选,微镜具有谐振轴和/或准静态轴。优选,在至少一个方法步骤中,硅晶片用作至少一个载体衬底。尤其地,至少一个载体衬底构造为硅晶片。优选,电动力学致动器至少大部分、优选至少80%、特别优选至少90%地由(尤其是低损耗的)铜构造。优选,电动力学致动器构造为铜线圈、尤其是驱动线圈。微电子设备可以具有尤其是与电动力学致动器不同的印制导线(尤其是铜印制导线)和/或通孔(尤其是铜通孔)。优选,至少一个电动力学致动器设置为用于驱动准静态轴。优选,压电致动器设置为用于驱动谐振轴。“设置”尤其应当理解为专门地编程、设计和/或配备。“一个对象设置为用于确定的功能”尤其应当理解为:该对象在至少一个应用状态和/或运行状态下实现和/或执行这个确定的功能。

5.优选,在至少一个方法步骤中,将至少一个电动力学致动器至少部分地引入、尤其是施加到载体衬底上的cmos子结构(unterbau)中的槽口中。优选,在尤其是构造成与至少一个方法步骤和至少一个另外的方法步骤不同的至少一个回火步骤中,至少一个电动力学致动器在至少400℃、优选至少450℃、特别优选至少500℃并且完全特别优选在至少530℃的情况下在载体衬底上、尤其是cmos子结构上被回火。优选,在所述至少一个另外的方法步骤中,至少将至少一个压电致动器施加到至少一个载体衬底上,所述至少一个压电致动器由压电陶瓷构造(尤其是构造成具有化学总式(summenformel)a

xby

o3)并且尤其可以掺杂有不同的材料(例如镧和/或铌),在所述至少一个载体衬底上尤其至少施加有所述至少一个电动力学致动器。优选,在至少一个另外的方法步骤中,在至少450℃、尤其是至少480℃的温度下至少将压电致动器施加到至少一个载体衬底上,尤其是至少将至少一个电动力学致动器施加到所述至少一个载体衬底上。优选,在至少一个另外的方法步骤中,至少一个压电致动器沉积到至少一个载体衬底上。

6.通过根据本发明的方法、尤其是根据本发明的方法的根据本发明的方法步骤顺序可以提供有利地成本低的且功能强大的微电子单元,该微电子单元尤其将电动力学致动器的固有导电特性和压电致动器的有利的压电特性相结合。

7.此外提出,至少一个压电致动器由pzt材料或knn材料构造。优选,在至少一个另外的方法步骤中,将至少一个压电致动器施加到至少一个载体衬底上,所述压电致动器由knn材料(尤其是铌酸钾钠)和/或pzt材料(尤其是锆钛酸铅)构造,在所述至少一个载体衬底上尤其施加有至少一个电动力学致动器,该电动力学致动器优选至少部分地构造为铜线圈并且尤其附加地部分构造为印制导线和/或通孔。可以实现压电致动器的有利大的动态致动器区域,尤其是通过knn材料和/或pzt材料的固有压电特性。尤其地,在压电致动器的动态运行中、尤其是在谐振中,在有利低能耗的情况下可以实现有利大的偏转角。

8.此外提出,所述至少一个另外的方法步骤在所述至少一个方法步骤之后执行。优选,所述至少一个另外的方法步骤在至少一个回火步骤之后、尤其是在至少两个回火步骤之后执行。优选,至少一个回火步骤在所述至少一个方法步骤和所述至少一个另外的方法步骤之间执行。可以构造有利地成本低的微电子设备,尤其是因为在施加电动力学致动器时可以有利地省去对工厂的铜区域的污染保护。

9.此外提出,在至少一个方法步骤中,将尤其是已经提到的cmos子结构施加到至少一个载体衬底上。优选,在至少一个方法步骤中,将由硼硅酸盐玻璃和氮化硅制成的cmos子结构施加到至少一个载体衬底上。优选,在至少一个方法步骤中,将硼硅酸盐玻璃层施加到至少一个载体衬底上,尤其是作为cmos子结构的一部分。优选,在至少一个方法步骤中,将氮化硅层施加到至少一个硼硅酸盐玻璃层上,尤其是作为cmos子结构的一部分。优选,在至少一个方法步骤中,借助于等离子体辅助化学气相沉积将氮化硅层施加到至少一个硼硅酸盐玻璃层上。优选,在至少一个方法步骤中,硼硅酸盐玻璃层设有钨塞(w-plugs)。优选,在至少一个方法步骤中,至少一个载体衬底设有扩散部,尤其是在硼硅酸盐玻璃层的钨塞的附近区域中。优选,在至少一个方法步骤中,尤其是借助于等离子体辅助化学气相沉积,将氧化硅层施加到至少一个氮化硅层上,尤其是作为cmos子结构的一部分。优选,在至少一个方法步骤中,优选借助于等离子体辅助化学气相沉积,将另一个氮化硅层施加到至少一个氧化硅层上,尤其是作为cmos子结构的一部分。优选,在至少一个方法步骤中,将槽口引入到、尤其是蚀刻到载体衬底上的cmos子结构中,尤其是用于接收电动力学致动器和/或印制导线和/或通孔。优选,在至少一个回火步骤之前的至少一个方法步骤中,借助于电镀技术、尤其是借助于电解电镀(elektroplattieren)将至少一个电动力学致动器施加到载体衬底上,尤其是和/或引入到载体衬底上的cmos子结构的槽口中。优选,在至少一个处理步骤中,将至少一个压电致动器施加到具有cmos子结构和至少一个(尤其是低欧的)电动力学致动器的至少一个载体衬底上。可以实现将压电致动器和电动力学致动器有利地集成到具有cmos子结构的载体衬底上。尤其地,可以实现有利地集成mems谐振器与完整的cmos子结构,尤其是用于随后密封的封装。

10.此外提出,在至少一个方法步骤中,在至少一个载体衬底上的cmos子结构上施加至少一个压电堆叠,该至少一个压电堆叠部分地由至少一个压电致动器形成。优选,在至少一个方法步骤中,在至少一个载体衬底上、尤其是在cmos子结构上布置至少一个尤其是金字塔形堆叠的压电堆叠18、尤其是至少一个压电致动器。优选,在至少一个方法步骤中,将

压电堆叠的粘附层施加到cmos子结构上、尤其是直接施加到另一个氮化硅层上。优选,在至少一个方法步骤中,将压电堆叠的电极层、尤其是铂层施加到至少一个粘附层上。优选,在至少一个方法步骤中,将压电堆叠的种子层涂覆到电极层上。优选,在至少一个方法步骤中,将压电堆叠的压电致动器、尤其是压电晶体施加到种子层上。优选,在至少一个方法步骤中,将压电堆叠的另一个电极层、尤其是铂层施加到至少一个压电致动器上。优选,在至少一个方法步骤中,通过压电堆叠的阻挡层和压电堆叠的附加的氮化硅层使压电堆叠钝化,尤其是在压电堆叠的背离载体元件的一侧上使其钝化。优选,在至少一个方法步骤中,电极层和/或另一个电极层构造成能够经由电接触部来电接通,尤其是通过压电堆叠的至少一个阻挡层(尤其是通过在压电堆叠的至少一个阻挡层中的蚀刻出的槽口)和/或通过压电堆叠的至少一个氮化硅层。优选,在至少一个方法步骤中,至少一个电动力学致动器构造成能够经由电接触部来电接通。

11.优选,在至少一个方法步骤中,另一个电接触部和附加的电接触部彼此间隔开地布置,尤其是用于接触压电致动器的不同侧。

12.此外提出,在至少一个方法步骤中使至少一个压电堆叠结构化。优选,在至少一个方法步骤中,使至少一个压电堆叠的至少一个层结构化。优选,在至少一个方法步骤中,使至少一个压电致动器作为压电堆叠的一部分结构化。优选,在至少一个方法步骤中,使压电堆叠的至少一个阻挡层和/或至少一个氮化硅层结构化。优选,在至少一个方法步骤中,将至少一个槽口引入到、尤其是蚀刻到压电堆叠的至少一个阻挡层和/或至少一个氮化硅层中。尤其地,将至少一个槽口设置在至少一个阻挡层和/或至少一个氮化硅层中以接收至少一个电接触部。可以实现压电致动器的、尤其是电动力学致动器的有利地成本低的电可接通性。

13.此外提出,在至少一个方法步骤中,通过镶嵌工艺(damascene-prozess)、优选铜镶嵌工艺将至少一个电动力学致动器施加、尤其是沉积到载体衬底上。优选,在该方法步骤中,通过铜镶嵌工艺将至少一个电动力学致动器至少部分地引入到、尤其是施加到载体衬底上的cmos子结构中的槽口中。优选,在(尤其是在至少一个回火步骤之前的)至少一个方法步骤中,借助于电镀技术、尤其是借助于电解电镀、优选借助于镶嵌工艺将至少一个电动力学致动器施加到载体衬底上,尤其是和/或引入到载体衬底上的槽口中。优选,在(尤其是在至少一个回火步骤之前的)至少一个方法步骤中,将用于至少一个电动力学致动器的至少一个槽口蚀刻到载体衬底中和/或位于该载体衬底上的层中、优选蚀刻到cmos子结构中。优选,在(尤其是在至少一个回火步骤之前的)至少一个方法步骤中,将铜种子层溅射到至少一个载体衬底上、优选cmos结构中的至少一个槽口中。可以实现用于至少一个电动力学致动器的有利大面积的、尤其是成本低的构造过程。

14.此外提出,在至少一个方法步骤中,给至少一个载体衬底开槽。优选,在至少一个方法步骤中,至少一个载体衬底从面向cmos结构的一侧开始被至少部分地开槽。尤其地,在至少一个方法步骤中,将至少一个槽口引入到、尤其是开槽到至少一个载体衬底中,例如通过湿化学蚀刻和/或干化学去除和/或物理去除载体衬底的材料。尤其地,在至少一个方法步骤中,至少一个载体衬底可以通过开槽分成可运动的部分、尤其是mems结构。尤其地,在至少一个方法步骤中,至少一个载体衬底可以完全地、尤其是垂直于最大的衬底表面地被开槽、尤其是贯穿开槽(durchtrencht)。可以实现有利可运动的微电子设备、尤其是mems芯

片设备。

15.此外,提出一种微电子设备、尤其是mems芯片设备,其通过根据本发明的方法来制造。

16.此外提出,微电子设备包括至少一个载体衬底,在该载体衬底上布置至少一个压电致动器,该压电致动器由压电钙钛矿材料构造,并且,其中,在载体衬底上布置由金属导体制成的至少一个电动力学致动器,该金属导体至少大部分地由铜构造。

17.在此,根据本发明的方法和/或根据本发明的微电子设备不应限于上述应用和实施方式。尤其地,根据本发明的方法和/或根据本发明的微电子设备为了实现本文中描述的功能方式而可具有与各个元件、构件和单元以及方法步骤的本文提及的数量不同的数量。此外,在本公开中说明的值域的情况下,在所提及的极限内的值也应视为已公开且能任意使用的。

附图说明

18.另外的优点从以下附图描述中得出。在附图中示出本发明的实施例。附图、说明书和权利要求书包含许多组合的特征。本领域技术人员也合乎目的地单独考虑这些特征并且将它们组合成有意义的其他组合。

19.附图示出:

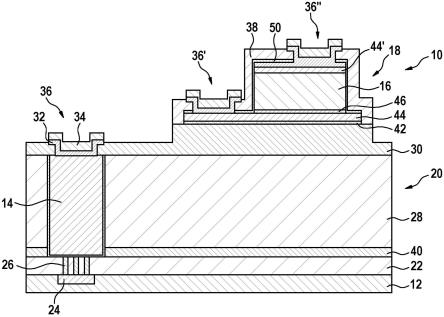

20.图1在示意性图示中的根据本发明的微电子设备,

21.图2在示意性图示中的根据本发明的微电子设备,以及

22.图3在示意性图示中的根据本发明的方法。

具体实施方式

23.图1示出微电子设备10、尤其是mems芯片设备。微电子设备10包括载体衬底12。在载体衬底12上布置压电致动器16。压电致动器16由压电钙钛矿材料构造。在载体衬底12上布置电动力学致动器14。电动力学致动器14由金属导体构造,该金属导体至少大部分由铜构造。

24.在载体衬底12中布置扩散部24,尤其是n掺杂原子和/或p掺杂原子。微电子设备10包括电动力学致动器14。微电子设备10包括压电致动器16。微电子设备10包括cmos子结构20。

25.cmos子结构20示例性地包括四个层。cmos子结构20可以包括直接布置在载体衬底12上的硼硅酸盐玻璃层22,在该硼硅酸盐玻璃层中布置一个或多个钨塞26。

26.cmos子结构20包括直接布置在硼硅酸盐玻璃层22上的氮化硅层40。cmos子结构20包括直接布置在氮化硅层40上的氧化硅层28,该氧化硅层尤其具有比氮化硅层40和/或硼硅酸盐玻璃层22更大的厚度、尤其是至少三倍于其地大的厚度。cmos子结构20包括直接布置在氧化硅层28上的另一个氮化硅层30。该另一个氮化硅层30尤其使电动力学致动器14在背离载体衬底12的一侧上钝化。

27.电动力学致动器14集成到cmos子结构20中,尤其是布置在氮化硅层40和氧化硅层28中。电动力学致动器14经由一个或多个钨塞26与载体衬底12中的扩散部24连接。电动力学致动器14能够经由另一个氮化硅层30中的电接触部36电连接,尤其是通过另一个氮化硅

层30。电接触部36、36’、36”包括铝层和/或铜层34以及阻挡层32,该阻挡层尤其布置在电动力学致动器14和铝层和/或铜层34之间。

28.在载体衬底12上、尤其是在cmos子结构20上布置压电堆叠18、尤其是压电致动器16。压电致动器16尤其由钙钛矿陶瓷(例如knn或pzt陶瓷)形成。压电致动器16由pzt材料或knn材料构造。压电堆叠18包括粘附层42,尤其是tan层、tin层或氧化钛层,该粘附层尤其是直接布置在另一个氮化硅层30上。压电堆叠18包括电极层44、尤其是铂层,该电极层尤其是直接布置在粘附层42上。压电堆叠18包括种子层46,尤其是lno层、尤其是lanio3层或pbo层,该种子层尤其是直接布置在电极层44上。电极层44、44’尤其是由铂构造。压电堆叠18部分地由压电致动器16形成,该压电致动器尤其是直接布置在种子层46上。压电堆叠18包括另一个电极层44,该另一个电极层尤其是直接布置在压电致动器16上。电极层44能够经由另一个电接触部36’电接通。另一个电极层44’能够通过附加的电接触部36”电接通。另一个电接触部36’和附加的电接触部36”彼此间隔开地布置,尤其是为了接触压电致动器16的不同侧。压电堆叠18通过阻挡层50(尤其是tan层、tin层或氧化钛层)和附加的氮化硅层38被钝化,尤其是在背离载体元件的一侧上被钝化。压电致动器16构造为压电薄层。压电堆叠18可以具有另一个阻挡层50,尤其是tan层、tin层或氧化钛层,该另一个阻挡层尤其是在压电致动器16和另一个电极层44’之间。

29.微电子设备10可以构造为mems扫描仪或mems陀螺仪。

30.图2示出尤其是在开槽状态下的微电子设备10,其具有结构化的cmos子结构20,其中,尤其是给载体衬底12开槽。载体衬底12优选具有沟渠、尤其是沟槽48。沟槽48延伸穿过载体衬底12上的cmos子结构20。

31.图3示出用于制造微电子设备10、尤其是mems芯片设备的方法52。微电子设备10、尤其是mems芯片设备尤其通过图3中示出的用于制造微电子设备10的方法52来制造。

32.在至少一个方法步骤、尤其是cmos步骤54中,将cmos子结构20施加、尤其是沉积到载体衬底12上。在cmos步骤54中,尤其是将金属的区域和/或n掺杂阱和/或p掺杂阱、尤其是扩散部24构造在载体衬底12中。在cmos步骤54中,尤其能够构造印制导线、压敏电阻和/或晶体管。

33.在至少一个方法步骤、尤其是铜施加步骤56中,将由金属导体制成的电动力学致动器14施加到载体衬底12上,该金属导体至少大部分由铜构造。在至少一个方法步骤、尤其是铜施加步骤56中,通过镶嵌工艺、尤其是通过电镀技术将电动力学致动器14施加到载体衬底12上。尤其地,在cmos步骤54之后执行铜施加步骤56。尤其地,在铜施加步骤56中,将槽口、尤其是沟渠蚀刻到cmos子结构20中。尤其地,在铜施加步骤56中,槽口内衬有阻挡层和种子层(例如ta层和/或tan层)。尤其地,在铜施加步骤56中,借助于电镀技术、尤其是铜镶嵌工艺给经内衬的槽口填充铜,尤其是用于构造电动力学致动器14。尤其地,在铜施加步骤56中,将电动力学致动器14平面化至cmos子结构20的高度上。

34.在至少一个方法步骤、尤其是铜调节步骤(kupferkonditionierschritt)58中,电动力学致动器14在载体衬底12上被加工,尤其是在高于400℃、优选在高于500℃、特别优选在至少530℃的情况下被回火。在铜调节步骤58中,利用绝缘体、尤其是利用绝缘体层(例如另一个氮化硅层30)使电动力学致动器14钝化。铜调节步骤58尤其在铜施加步骤56之后执行。

35.在至少一个另外的方法步骤、尤其是处理步骤60中,将压电致动器16施加、尤其是沉积到载体衬底12上。在至少一个另外的方法步骤、尤其是处理步骤60中,在至少一个载体衬底12上的cmos子结构20上施加、尤其是沉积压电堆叠18,该压电堆叠部分地由压电致动器16形成。在至少一个另外的方法步骤、尤其是处理步骤60中,利用绝缘体使压电堆叠18钝化。

36.至少一个另外的方法步骤、尤其是处理步骤60尤其在至少一个方法步骤、尤其是至少一个铜施加步骤56和/或铜调节步骤58之后执行。

37.在至少一个方法步骤、尤其是结构化步骤62中,压电堆叠18被结构化、尤其是设有槽口。尤其地,在结构化步骤62中,将槽口引入到、优选蚀刻到附加的氮化硅层38和/或阻挡层50中。尤其地,在结构化步骤62中可以将至少一个槽口引入到、优选蚀刻到另一个氮化硅层30中。尤其地,结构化步骤62中的蚀刻部在面积方面可以比载体衬底12中的沟槽48更大。结构化步骤62尤其在处理步骤60之后执行。在一个方法步骤、尤其是结构化步骤62中,压电堆叠18可以设有金字塔形的构造,尤其是通过去除各个层的材料。

38.在至少一个方法步骤、尤其是接通步骤64中,通过电接触部36、36’、36”电地接通、尤其是重新布线至少一个压电堆叠18和/或至少一个电动力学致动器14。在接通步骤64中,压电堆叠18例如可以与cmos子结构20电连接。接通步骤64尤其在结构化步骤62之后执行。

39.在至少一个方法步骤、尤其是封装步骤66中,压电致动器16可以与电动力学致动器14一起密封地封装在至少一个载体衬底12上,尤其是在至少400℃、优选至少430℃的情况下。封装步骤66尤其在接通步骤64之后执行。

40.在至少一个方法步骤、尤其是开槽步骤68中,可以给至少一个载体衬底12开槽、尤其是完全贯穿开槽,尤其是用于产生可运动的mems结构。尤其地,在开槽步骤68中,可以从两侧、尤其是在两侧给载体衬底12部分开槽或完全开槽,尤其是用于构造可运动的mems结构。尤其地,开槽步骤68可以在封装步骤66之前和/或之后执行。

41.在一个可选方法步骤、尤其是开槽步骤68之前的可选方法步骤中,可以蚀刻、尤其是局部蚀刻绝缘体层(尤其是另一个氮化硅层30)和/或氧化硅层28和/或cmos子结构20的其他氧化层。

42.尤其地,处理步骤60可以在铜施加步骤56之前和铜调节步骤58之前执行。在这种情况下,将压电堆叠18施加到cmos子结构20上,并且随后利用该其他氧化层使该压电堆叠钝化。该其他氧化层在一个方法步骤中被平面化。在一个方法步骤中,将用于至少一个电动力学致动器14的至少一个槽口引入到该其他氧化层中。此后,可以从铜施加步骤56开始、尤其是在没有处理步骤60的情况下遍历方法52。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。