1.本发明主要涉及半导体功率器件,更具体地,本发明涉及改进的屏蔽栅沟槽(sgt)式超级结(sj)mosfet(金属氧化物半导体场效应晶体管),其在sgt区和sj区都具有多阶梯外延(mse)层结构。

背景技术:

2.众所周知,sj结构和sgt结构都打破了功率mosfets在击穿电压(bv)和比导通电阻(rsp)之间的传统硅极限。当bv高于300v时,相比sgt mosfet,sj mosfet具有更低的rsp。然而,当bv低于300v时,相比sj mosfet,sgt mosfet具有更多的优势,包括更低的栅-漏电容(cgd)和更低的rsp。

3.因此,对于bv高于300v的功率mosfets而言,仍需要提供一种新型的器件结构以获得更低的rsp和更低的cgd,可通过将sgt结构和sj结构相结合以获得改进的特性来实现。

技术实现要素:

4.本发明公开了新型的sgt sj mosfets,其中,位于氧化层电荷平衡(ocb)区的外延层具有第一类型mse结构,位于sj区的外延层具有第二类型mse结构。与常规的sgt mosfets和sj mosfets相比,本发明公开的这种具有以上两种类型mse结构的器件,其漂移区的平均掺杂浓度更高,因此可在不降低bv的情况下,显著降低器件的rsp。此外,本发明公开的这种具有以上两种类型mse结构的器件,可以避免沟道区发生强电场峰,从而增强器件的雪崩能力。

5.在ocb区内将mse结构与多阶梯氧化层(mso)结构相结合,并在衬底与ocb区之间的缓冲区中引入一层缓冲外延层,可进一步降低器件的rsp。该mso结构是一个场板氧化层,其围绕在位于栅沟槽的屏蔽栅极的周围,并具有自栅沟槽底部至体区方向、厚度呈阶梯式递减的多个阶梯氧化层,其中每个阶梯氧化层的厚度都是均匀的。

6.本发明的一个方面,是公开了一种sgt sj mosfet,所述sgt sj mosfet形成在具有第一导电类型的外延层内,所述外延层位于具有第一导电类型的衬底之上,其进一步包括:多个位于有源区的栅沟槽,其被具有第一导电类型的源区所包围,源区位于具有第二导电类型的体区中,并接近外延层的上表面,其中,每个栅沟槽都包括一个栅极和一个屏蔽栅极;屏蔽栅极与外延层间通过第一绝缘层实现绝缘,栅极与外延层间通过栅氧化层实现绝缘,屏蔽栅极与栅极间通过多晶硅间氧化层(ipo)实现绝缘,栅氧化层围绕栅极,且栅氧化层的厚度小于第一绝缘层;一个ocb区,形成于两相邻的栅沟槽之间、体区下方和屏蔽栅极的底部上方;体区,屏蔽栅极和源区,通过多个沟槽式接触区连至源金属;位于ocb区的外延层,具有第一类型mse层结构,其掺杂浓度沿栅沟槽侧壁、自屏蔽栅极的底部至体区方向呈阶梯式递减,其中每个第一类型mse层都具有均匀的掺杂浓度;所述sgt sj mosfet还进一步包括一个位于ocb区下方的sj区,其包括具有第一导电类型的第一掺杂柱和具有第二导电类型的第二掺杂柱,第一掺杂柱和第二掺杂柱交替平行排列,并从栅沟槽的底部附近延

伸至衬底,其中每个第二掺杂柱都位于两相邻的栅沟槽之间并连接至体区;一个具有第一导电类型的缓冲区(nb),形成于衬底和sj区之间。

7.根据本发明的另一个方面,在一些优选实施例中,位于ocb区和缓冲区之间的sj区具有掺杂浓度均匀的单一外延层,且第一掺杂柱的掺杂浓度与第二掺杂柱相同。

8.根据本发明的另一个方面,在一些优选实施例中,位于ocb区和缓冲区之间的sj区具有第二类型mse层,所述第二类型mse层具有第一导电类型且具有不同的掺杂浓度;位于sj区的第二类型mse层与第一掺杂柱的掺杂浓度,自ocb区底部至缓冲区方向呈阶梯式递减,而第二掺杂柱的掺杂浓度自ocb区底部至缓冲区方向呈阶梯式递增;在sj区底部、缓冲区附近,第一掺杂柱的掺杂浓度低于第二掺杂柱;在sj区顶部、ocb区附近,第一掺杂柱的掺杂浓度高于第二掺杂柱;在sj区的顶部和底部之间、sj区的中间区域,第一掺杂柱的掺杂浓度与第二掺杂柱相同。

9.根据本发明的另一个方面,在一些优选实施例中,位于ocb区和缓冲区之间的sj区具有第二类型mse层,所述第二类型mse层具有第一导电类型且具有不同的掺杂浓度;位于sj区的第二类型mse层与第一掺杂柱的掺杂浓度,自ocb区底部至缓冲区方向呈阶梯式递增,而第二掺杂柱的掺杂浓度自ocb区底部至缓冲区方向呈阶梯式递减;在sj区底部、缓冲区附近,第一掺杂柱的掺杂浓度高于第二掺杂柱;在sj区顶部、ocb区附近,第一掺杂柱的掺杂浓度低于第二掺杂柱;在sj区的顶部和底部之间、sj区的中间区域,第一掺杂柱的掺杂浓度与第二掺杂柱相同。

10.根据本发明的另一个方面,在一些优选实施例中,栅极位于屏蔽栅极之上。在另一些优选实施例中,屏蔽栅极位于沟槽中间,栅极围绕屏蔽栅极的上部两侧形成。

11.根据本发明的另一个方面,在一些优选实施例中,根据击穿电压等级的不同,位于缓冲区的外延层的掺杂浓度等于或低于或高于位于sj区的第二类型mse层的底部外延层的掺杂浓度。

12.根据本发明的另一个方面,在一些优选实施例中,位于ocb区的第一类型mse层包括至少两个具有不同掺杂浓度的阶梯外延层:掺杂浓度为d1的底部外延层以及位于底部外延层之上、掺杂浓度为d2的顶部外延层,其中,d1和d2的关系为d2《d1。在另一些优选实施例中,位于ocb区的第一类型mse层包括至少三个具有不同掺杂浓度的阶梯外延层:掺杂浓度为d1的底部外延层,掺杂浓度为d2的中间外延层以及掺杂浓度为d3的顶部外延层,其中,d1,d2和d3的关系为d3《d2《d1。

13.根据本发明的另一个方面,在一些优选实施例中,位于源区和体区的外延层,其掺杂浓度与位于ocb区、第一类型mse层的顶部外延层相同。

14.根据本发明的另一个方面,在一些优选实施例中,位于sj区的第二掺杂柱的宽度自ocb区底部至缓冲区方向逐渐减小,以解决sj区第一掺杂柱底部jfet(结场效应晶体管)耗尽引起的漏极饱和电流的限制。该实施例可专门应用于具有更窄间距的sj区以获得更低的导通电阻,其中,jfet耗尽区的宽度在第一掺杂柱中变得更明显。

15.根据本发明的另一个方面,在一些优选实施例中,位于ocb区的第二掺杂柱的宽度小于或者等于位于sj区的第二掺杂柱的宽度。

16.根据本发明的另一个方面,还公开了一种sgt sj mosfet,所述sgt sjmosfet形成在具有第一导电类型的外延层内,外延层位于具有第一导电类型的衬底之上,其进一步包

括:多个位于有源区的栅沟槽,其被具有第一导电类型的源区所包围,源区位于具有第二导电类型的体区中,并接近外延层的上表面,其中,每个栅沟槽都包括一个栅极和一个屏蔽栅极;屏蔽栅极与外延层间通过第一绝缘层实现绝缘,栅极与外延层间通过栅氧化层实现绝缘,屏蔽栅极与栅极间通过ipo实现绝缘,栅氧化层围绕栅极,且栅氧化层的厚度小于第一绝缘层;一个ocb区,形成于两相邻的栅沟槽之间、体区下方和屏蔽栅极的底部上方;体区,屏蔽栅极和源区,通过多个沟槽式接触区连至源金属;第一绝缘层具有mso结构,其厚度沿栅沟槽侧壁、自栅沟槽底部至体区方向呈阶梯式递减;所述sgtsj mosfet还进一步包括一个位于ocb区下方的sj区,其包括具有第一导电类型的第一掺杂柱和具有第二导电类型的第二掺杂柱,第一掺杂柱和第二掺杂柱交替平行排列,并从栅沟槽的底部附近延伸至衬底,其中每个第二掺杂柱都位于两相邻的栅沟槽之间并连接至体区;一个缓冲区,形成于衬底和sj区之间。

17.根据本发明的另一个方面,在一些优选实施例中,位于ocb区与缓冲区之间的sj区具有第二类型mse层,所述第二类型mse层具有第一导电类型且具有不同的掺杂浓度;位于sj区的第二类型mse层与第一掺杂柱的掺杂浓度,自ocb区底部至缓冲区方向呈阶梯式递减,而第二掺杂柱的掺杂浓度自ocb区底部至缓冲区方向呈阶梯式递增;在sj区底部、缓冲区附近,第一掺杂柱的掺杂浓度低于第二掺杂柱;在sj区顶部、ocb区附近,第一掺杂柱的掺杂浓度高于第二掺杂柱;在sj区的顶部和底部之间、sj区的中间区域,第一掺杂柱的掺杂浓度与第二掺杂柱相同。

18.在另一些优选实施例中,位于ocb区与缓冲区之间的sj区具有第二类型mse层,所述第二类型mse层具有第一导电类型且具有不同的掺杂浓度;位于sj区的第二类型mse层与第一掺杂柱的掺杂浓度,自ocb区底部至缓冲区方向呈阶梯式递增,而第二掺杂柱的掺杂浓度自ocb区底部至缓冲区方向呈阶梯式递减;在sj区底部、缓冲区附近,第一掺杂柱的掺杂浓度高于第二掺杂柱;在sj区顶部、ocb区附近,第一掺杂柱的掺杂浓度低于第二掺杂柱;在sj区的顶部和底部之间、sj区的中间区域,第一掺杂柱的掺杂浓度与第二掺杂柱相同。

19.根据本发明的另一个方面,在一些优选实施例中,位于ocb区的外延层为具有均匀掺杂浓度的单一外延层。在另一些优选实施例中,位于ocb区的外延层为具有不同掺杂浓度的第一类型mse层,所述第一类型mse层的掺杂浓度沿栅沟槽侧壁、自屏蔽栅极底部至体区方向呈阶梯式递减,其中每个mse层都具有均匀的掺杂浓度。

20.根据本发明的另一个方面,还公开了一种sgt sj mosfet,所述sgt sjmosfet形成在具有第一导电类型的外延层内,外延层位于具有第二导电类型的衬底之上,其进一步包括:多个位于有源区的栅沟槽,其被具有第一导电类型的源区所包围,源区位于具有第二导电类型的体区中,并接近外延层的上表面,其中,每个栅沟槽都包括一个栅极和一个屏蔽栅极;屏蔽栅极与外延层间通过第一绝缘层实现绝缘,栅极与外延层间通过栅氧化层实现绝缘,屏蔽栅极与栅极间通过ipo实现绝缘,栅氧化层围绕栅极,且栅氧化层的厚度小于第一绝缘层;一个ocb区,形成于两相邻的栅沟槽之间、体区下方和屏蔽栅极的底部上方;体区,屏蔽栅极和源区,通过多个沟槽式接触区连至源金属;位于ocb区的外延层为具有不同掺杂浓度的第一类型mse层,所述第一类型mse层的掺杂浓度沿栅沟槽侧壁、自屏蔽栅极底部至体区方向呈阶梯式递减,其中每个mse层都具有均匀的掺杂浓度;所述sgt sj mosfet还进一步包括一个位于ocb区下方的sj区,其包括具有第一导电类型的第一掺杂柱和具有第二

导电类型的第二掺杂柱,第一掺杂柱和第二掺杂柱交替平行排列,并从栅沟槽的底部附近延伸至衬底,其中每个第二掺杂柱都位于两相邻的栅沟槽之间并连接至体区;一个具有第一导电类型的缓冲区,形成于衬底和sj区之间。

21.根据本发明的另一个方面,在一些优选实施例中,还进一步包括多个位于衬底、具有第一导电类型的重掺杂区,以形成多个位于衬底、交替排列的p 区和n 区。

22.通过参考以下各个附图,阅读下文对优选实施例的详细描述,本发明的上述及其他的目的和优点对于本领域的普通技术人员来说无疑是显而易见的。

附图说明

23.本发明的这些和其他实施方式的优点将通过下面结合附图的详细说明如后,其中:

24.图1a是根据本发明的一个优选实施例的横截面图,并揭示了n型外延层掺杂浓度、n柱&p柱掺杂浓度沿垂直方向的变化。

25.图1b是图1a所示的优选实施例的横截面图,并分别揭示了n柱和p柱掺杂浓度沿垂直方向的变化。

26.图1c是根据本发明的另一个优选实施例的横截面图,并揭示了n型外延层掺杂浓度、n柱&p柱掺杂浓度沿垂直方向的变化。

27.图1d是根据本发明的另一个优选实施例的横截面图,并揭示了n型外延层掺杂浓度、n柱&p柱掺杂浓度沿垂直方向的变化。

28.图2a是根据本发明的另一个优选实施例的横截面图,并揭示了n型外延层掺杂浓度、n柱&p柱掺杂浓度沿垂直方向的变化。

29.图2b是图2a所示的优选实施例的横截面图,并分别揭示了n柱和p柱掺杂浓度沿垂直方向的变化。

30.图3a是根据本发明的另一个优选实施例的横截面图,并揭示了n型外延层掺杂浓度、n柱&p柱掺杂浓度沿垂直方向的变化。

31.图3b是图3a所示的优选实施例的横截面图,并分别揭示了n柱和p柱掺杂浓度沿垂直方向的变化。

32.图3c是根据本发明的另一个优选实施例的横截面图,并揭示了n型外延层掺杂浓度、n柱&p柱掺杂浓度沿垂直方向的变化。

33.图3d是根据本发明的另一个优选实施例的横截面图,并揭示了n型外延层掺杂浓度、n柱&p柱掺杂浓度沿垂直方向的变化。

34.图4a是根据本发明的另一个优选实施例的横截面图,并揭示了n型外延层掺杂浓度、n柱&p柱掺杂浓度沿垂直方向的变化。

35.图4b是图4a所示的优选实施例的横截面图,并分别揭示了n柱和p柱掺杂浓度沿垂直方向的变化。

36.图5a是根据本发明的另一个优选实施例的横截面图,并揭示了n型外延层掺杂浓度、n柱&p柱掺杂浓度沿垂直方向的变化。

37.图5b是图5a所示的优选实施例的横截面图,并分别揭示了n柱和p柱掺杂浓度沿垂直方向的变化。

38.图6a是根据本发明的另一个优选实施例的横截面图,并揭示了n型外延层掺杂浓度、n柱&p柱掺杂浓度沿垂直方向的变化。

39.图6b是图6a所示的优选实施例的横截面图,并分别揭示了n柱和p柱掺杂浓度沿垂直方向的变化。

40.图7a是根据本发明的另一个优选实施例的横截面图,并揭示了n型外延层掺杂浓度、n柱&p柱掺杂浓度沿垂直方向的变化。

41.图7b是图7a所示的优选实施例的横截面图,并分别揭示了n柱和p柱掺杂浓度沿垂直方向的变化。

42.图8a是根据本发明的另一个优选实施例的横截面图,并揭示了n型外延层掺杂浓度、n柱&p柱掺杂浓度沿垂直方向的变化。

43.图8b是图8a所示的优选实施例的横截面图,并分别揭示了n柱和p柱掺杂浓度沿垂直方向的变化。

44.图9a是根据本发明的另一个优选实施例的横截面图,并揭示了n型外延层掺杂浓度、n柱&p柱掺杂浓度沿垂直方向的变化。

45.图9b是图9a所示的优选实施例的横截面图,并分别揭示了n柱和p柱掺杂浓度沿垂直方向的变化。

46.图10a是根据本发明的另一个优选实施例的横截面图,并揭示了n型外延层掺杂浓度、n柱&p柱掺杂浓度沿垂直方向的变化。

47.图10b是图10a所示的优选实施例的横截面图,并分别揭示了n柱和p柱掺杂浓度沿垂直方向的变化。

48.图11是根据本发明的另一个优选实施例的横截面图,并揭示了n型外延层掺杂浓度、n柱&p柱掺杂浓度沿垂直方向的变化。

49.图12a是根据本发明的另一个优选实施例的横截面图,并揭示了n型外延层掺杂浓度、n柱&p柱掺杂浓度沿垂直方向的变化。

50.图12b是图12a所示的优选实施例的横截面图,并分别揭示了n柱和p柱掺杂浓度沿垂直方向的变化。

51.图13是根据本发明的另一个优选实施例的横截面图,并揭示了n型外延层掺杂浓度、n柱&p柱掺杂浓度沿垂直方向的变化。

52.图14a是根据本发明的另一个优选实施例的横截面图,并揭示了n型外延层掺杂浓度、n柱&p柱掺杂浓度沿垂直方向的变化。

53.图14b是图14a所示的优选实施例的横截面图,并分别揭示了n柱和p柱掺杂浓度沿垂直方向的变化。

具体实施方式

54.下面参照附图更详细地说明本发明,其中示出了本发明的优选实施例。本发明可以,但是以不同的方式体现,但是不应该局限于在此所述的实施例。例如,这里的说明更多地引用n沟道的半导体集成电路,但是很明显其他器件也是可能的。下文是通过参考各个附图来对实践本发明的优选实施例进行详细描述。一些方向术语,例如“顶部”、“底部”、“前”、“后”、“上方”、“下方”等,是参考各个附图的方向进行描述的。由于实施例中的元件可以被

放置在许多不同的方向,因此,本发明中的方向术语只是用于描述而不能被视为对本发明的限制。应该理解的是,实施例中各种结构或者逻辑上的替代和修改都应该被涵盖在本发明的真正精神和范围内。因此,以下的详细描述不能被视为对本发明的限制,本发明的涵盖范围由附后的权利要求界定。应该理解的是,本发明中所描述的各个优选实施例的发明特征可以相互结合,有特别说明的除外。

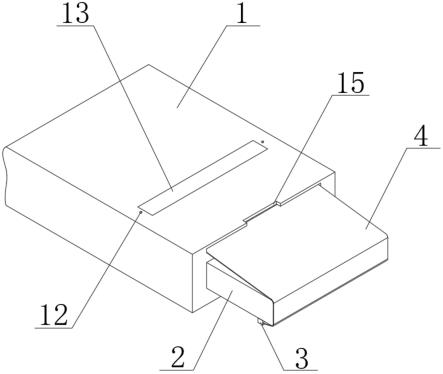

55.图1a是根据本发明的一个优选实施例的横截面图,该实施例具有改进的器件结构,并揭示了n型外延层掺杂浓度、n柱&p柱掺杂浓度沿垂直方向的变化。所述的n沟道沟槽式半导体功率器件包括一个在n型外延层上形成的n沟道sgt sj mosfet,该外延层位于n 衬底100之上,衬底100的背面涂有ti/ni/ag后金属层101用作漏金属。一个ocb区t

ocb

(b-b线与d-d线之间),形成于两相邻的栅沟槽104之间、体区110下方和屏蔽栅极105的底部上方。位于ocb区的外延层为具有两个不同掺杂浓度的第一类型mse层,包括一个掺杂浓度为d1的底部第一外延层(n

ocb

,如图所示,c-c线与d-d线之间)103以及位于底部第一外延层103之上、掺杂浓度为d2的顶部第二外延层(n

oct

,如图所示,b-b线与c-c线之间)123,其中,d1和d2的关系为d2《d1,以提高击穿电压、降低比导通电阻。一个sj区t

sj

(d-d线与e-e线之间),形成于ocb区t

ocb

和缓冲区102之间,其包括交替平行排列的n型掺杂柱(n

sj

,如图所示)124和p型掺杂柱(p

sj

,如图所示)127,其从栅沟槽104的底部附近延伸至缓冲区102,其中,每个p型掺杂柱127都位于两相邻的栅沟槽104之间并连接至体区110。sj区t

sj

具有单一外延层(n

sj

,如图所示)124,其掺杂浓度均匀为dn

sj

,且单一外延层和n型掺杂柱124的掺杂浓度dn

sj

与p型掺杂柱127的掺杂浓度dp

sj

相同(dn

sj

=dp

sj

),且dn

sj

低于ocb区内的顶部第二外延层123的掺杂浓度d2。一个缓冲区tb(nb,如图所示,e-e线与f-f线之间),形成于n 衬底100和sj区之间。缓冲区外延层的掺杂浓度db低于位于sj区的单一外延层124的掺杂浓度dn

sj

。此外,位于ocb区的p型掺杂柱(p

ocb

和p

oct

,如图所示)128和129的宽度与位于sj区的p型掺杂柱127相同,所有的p型掺杂柱128,129和127都具有相同的掺杂浓度dp

sj

,且dp

sj

低于位于ocb区的顶部第二外延层123的掺杂浓度d2。在n型外延层中,多个栅沟槽104从位于ocb区t

ocb

的顶部第二外延层123的上表面向下垂直延伸至位于sj区的单一外延层124中,其中栅沟槽104的底部位于缓冲区102和sj区的公共界面的上方。每个栅沟槽104,都包括位于沟槽较低部分的一个屏蔽栅极(sg,如图所示)105,以及位于沟槽较高部分、屏蔽栅极105之上的单栅极(g,如图所示)107。屏蔽栅极105与相邻外延层间通过第一绝缘层106实现绝缘,栅极107与相邻外延层间通过栅氧化层109实现绝缘,其中栅氧化层109的厚度小于第一绝缘层106,且第一绝缘层106沿沟槽侧壁具有均匀的厚度。同时,屏蔽栅极105与栅极107间通过多晶硅间氧化层(ipo)108实现绝缘。在每两个相邻的沟槽栅104之间,一个具有n 源区111的p体区110从位于ocb区的顶部第二外延层123的上表面附近延伸,形成位于a-a线与b-b线之间的源体区t

sb

。位于源体区t

sb

的外延层的掺杂浓度与位于ocb区的顶部第二外延层123相同。p体区110,n 源区111和屏蔽栅极105,通过多个沟槽式接触区113连至源金属112。多个沟槽式接触区113均填充以金属插塞和势垒层,其穿过绝缘层117延伸至体区中,每个沟槽式接触区113的底部均由位于n 源区111下方的p 重掺杂区120所包围。

56.图1b是图1a所示的优选实施例的横截面图,并分别揭示了n柱和p柱掺杂浓度沿垂直方向的变化。

57.图1c是根据本发明的另一个优选实施例的横截面图,该实施例具有改进的器件结

构,并揭示了n型外延层掺杂浓度、n柱&p柱掺杂浓度沿垂直方向的变化。所述的n沟道沟槽式半导体功率器件与图1a所述的发明具有相似的结构,且n型外延层掺杂浓度、n柱&p柱掺杂浓度与图1a相同,除了在本发明中,位于ocb区的p型掺杂柱的宽度(wp

oc

)窄于位于sj区的p型掺杂柱的宽度(wp

sj

),即wp

oc

《wp

sj

。

58.图1d是根据本发明的另一个优选实施例的横截面图,该实施例具有改进的器件结构,并揭示了n型外延层掺杂浓度、n柱&p柱掺杂浓度沿垂直方向的变化。所述的n沟道沟槽式半导体功率器件与图1a所述的发明具有相似的结构,且n型外延层掺杂浓度、n柱&p柱掺杂浓度与图1a相同,除了在本发明中,位于sj区的p型掺杂柱呈倾斜状,且位于sj区的p型掺杂柱的宽度自ocb区底部至缓冲区102”方向呈线性递减。

59.图2a是根据本发明的另一个优选实施例的横截面图,该实施例具有改进的器件结构,并揭示了n型外延层掺杂浓度、n柱&p柱掺杂浓度沿垂直方向的变化。所述的n沟道沟槽式半导体功率器件与图1a所述的发明具有相似的结构,除了在本发明中,位于ocb区t

ocb

(b-b线与e-e线之间)的n型外延层包括三个具有不同掺杂浓度的阶梯外延层:掺杂浓度为d1的底部第一外延层(n

ocb

,如图所示,d-d线与e-e线之间)203,掺杂浓度为d2的中间第二外延层(n

ocm

,如图所示,c-c线与d-d线之间)223以及掺杂浓度为d3的顶部第三外延层(n

oct

,如图所示,b-b线与c-c线之间)233,其中,d1,d2和d3的关系为d3《d2《d1,以进一步降低比导通电阻。其中,d2可以是d1和d3的平均值。位于源体区t

sb

的外延层的掺杂浓度与位于ocb区的顶部第三外延层233相同,且高于位于sj区的单一外延层和n型掺杂柱(n

sj

,如图所示)224的掺杂浓度dn

sj

。同时,所有的p型掺杂柱,包括位于ocb区的p

oct

,p

ocm

和p

ocb

以及位于sj区的p

sj

都具有相同的掺杂浓度dp

sj

,dp

sj

与位于sj区的单一外延层和n型掺杂柱224的掺杂浓度dn

sj

相同,且dp

sj

低于位于ocb区的顶部第三外延层233的掺杂浓度d3。

60.图2b是图2a所示的优选实施例的横截面图,并分别揭示了n柱和p柱掺杂浓度沿垂直方向的变化。

61.图3a是根据本发明的另一个优选实施例的横截面图,该实施例具有改进的器件结构,并揭示了n型外延层掺杂浓度、n柱&p柱掺杂浓度沿垂直方向的变化。所述的n沟道沟槽式半导体功率器件与图1a所述的发明具有相似的结构,除了在本发明中,sj区t

sj

(d-d线与g-g线之间)具有n型mse外延层,其掺杂浓度自缓冲区302至ocb区底部方向呈阶梯式递增。n型mse层和n型掺杂柱具有三个不同的掺杂浓度,包括掺杂浓度为dn

sjb

的底部第一外延层和第一n型掺杂柱(n

sjb

,如图所示,f-f线与g-g线之间)324,掺杂浓度为dn

sjm

的中间第二外延层和第二n型掺杂柱(n

sjm

,如图所示,e-e线与f-f线之间)325以及掺杂浓度为dn

sjt

的顶部第三外延层和第三n型掺杂柱(n

sjt

,如图所示,d-d线与e-e线之间)326,其中,dn

sjb

,dn

sjm

和dn

sjt

的关系为dn

sjb

《dn

sjm

《dn

sjt

。顶部第三外延层和第三n型掺杂柱326的掺杂浓度dn

sjt

低于位于ocb区的顶部第二外延层(n

oct

,如图所示,b-b线与c-c线之间)323的掺杂浓度d2。同时,位于sj区的p型掺杂柱的掺杂浓度自缓冲区302至ocb区的底部方向呈阶梯式递减,底部第一p型掺杂柱(p

sjb

,如图所示,f-f线与g-g线之间)的掺杂浓度dp

sjb

高于中间第二p型掺杂柱(p

sjm

,如图所示,e-e线与f-f线之间)的掺杂浓度dp

sjm

,且dp

sjm

高于顶部第三p型掺杂柱(p

sjt

,如图所示,d-d线与e-e线之间)的掺杂浓度dp

sjt

,即dp

sjb

》dp

sjm

》dp

sjt

。位于sj区的底部第一外延层和第一n型掺杂柱324的掺杂浓度dn

sjb

低于位于sj区底部、缓冲区302附近的底部第一p型掺杂柱p

sjb

的掺杂浓度dp

sjb

(dn

sjb

《dp

sjb

);中间第二外延层和第二n型掺杂柱325

的掺杂浓度dn

sjm

与位于sj区中间区域的中间第二p型掺杂柱p

sjm

的掺杂浓度dp

sjm

相同(dn

sjm

=dp

sjm

);顶部第三外延层和第三n型掺杂柱326的掺杂浓度dn

sjt

高于位于sj区顶部、ocb区附近的顶部第三p型掺杂柱p

sjt

的掺杂浓度dp

sjt

(dn

sjt

》dp

sjt

)。此外,位于ocb区的所有p型掺杂柱(p

oct

和p

ocb

,如图所示)都具有相同的掺杂浓度dp

oc

,其与位于sj区中间区域的中间第二p型掺杂柱p

sjm

的掺杂浓度dp

sjm

相同。

62.图3b是图3a所示的优选实施例的横截面图,并分别揭示了n柱和p柱掺杂浓度沿垂直方向的变化。

63.图3c是根据本发明的另一个优选实施例的横截面图,该实施例具有改进的器件结构,并揭示了n型外延层掺杂浓度、n柱&p柱掺杂浓度沿垂直方向的变化。所述的n沟道沟槽式半导体功率器件与图3a所述的发明具有相似的结构,除了在本发明中,位于ocb区的p型掺杂柱的宽度(wp

oc

)窄于位于sj区的p型掺杂柱p

sjt

,p

sjm

和p

sjb

的宽度(wp

sj

),即wp

oc

《wp

sj

。

64.图3d是根据本发明的另一个优选实施例的横截面图,该实施例具有改进的器件结构,并揭示了n型外延层掺杂浓度、n柱&p柱掺杂浓度沿垂直方向的变化。所述的n沟道沟槽式半导体功率器件与图3a所述的发明具有相似的结构,且n型外延层掺杂浓度、n柱&p柱掺杂浓度与图3a相同,除了在本发明中,位于sj区的p型掺杂柱呈倾斜状,且位于sj区的p型掺杂柱的宽度自ocb区底部至缓冲区302”方向呈线性递减。

65.图4a是根据本发明的另一个优选实施例的横截面图,该实施例具有改进的器件结构,并揭示了n型外延层掺杂浓度、n柱&p柱掺杂浓度沿垂直方向的变化。所述的n沟道沟槽式半导体功率器件与图3a所述的发明具有相似的结构,除了在本发明中,位于ocb区t

ocb

(b-b线与e-e线之间)的n型外延层包括三个具有不同掺杂浓度的阶梯外延层:掺杂浓度为d1的底部第一外延层(n

ocb

,如图所示,d-d线与e-e线之间)403,掺杂浓度为d2的中间第二外延层(n

ocm

,如图所示,c-c线与d-d线之间)423以及掺杂浓度为d3的顶部第三外延层(n

oct

,如图所示,b-b线与c-c线之间)433,其中,d1,d2和d3的关系为d3《d2《d1,以进一步降低比导通电阻。其中,d2可以是d1和d3的平均值。位于源体区t

sb

的外延层的掺杂浓度与位于ocb区的顶部第三外延层433相同,其高于位于sj区的顶部第三外延层和第三n型掺杂柱(n

sjt

,如图所示)426的掺杂浓度dn

sjt

。此外,所有位于ocb区的p型掺杂柱包括p

oct

,p

ocm

和p

ocb

都具有相同的掺杂浓度dp

oc

,其与位于sj区中间区域的中间第二p型掺杂柱p

sjm

的掺杂浓度dp

sjm

相同。

66.图4b是图4a所示的优选实施例的横截面图,并分别揭示了n柱和p柱掺杂浓度沿垂直方向的变化。

67.图5a是根据本发明的另一个优选实施例的横截面图,该实施例具有改进的器件结构,并揭示了n型外延层掺杂浓度、n柱&p柱掺杂浓度沿垂直方向的变化。所述的n沟道沟槽式半导体功率器件与图3a所述的发明具有相似的结构,除了在本发明中,sj区内具有不同的n型mse层和p型掺杂柱,所述n型mse层和p型掺杂柱具有相反的掺杂浓度变化。位于sj区的n型mse层的掺杂浓度自缓冲区502至ocb区底部方向呈阶梯式递减。在本发明中,位于ocb区t

ocb

和缓冲区502之间的sj区t

sj

包括具有三个不同掺杂浓度的n型mse外延层和n型掺杂柱:掺杂浓度为dn

sjb

的底部第一外延层和第一n型掺杂柱(n

sjb

,如图所示,f-f线与g-g线之间)524,掺杂浓度为dn

sjm

的中间第二外延层和第二n型掺杂柱(n

sjm

,如图所示,e-e线与f-f线之间)525以及掺杂浓度为dn

sjt

的顶部第三外延层和第三n型掺杂柱(n

sjt

,如图所示,d-d线与e-e线之间)526,其中,dn

sjb

,dn

sjm

和dn

sjt

的关系为dn

sjb

》dn

sjm

》dn

sjt

。同时,位于sj区的p

型掺杂柱的掺杂浓度自缓冲区502至ocb区的底部方向呈阶梯式递增,底部第一p型掺杂柱(p

sjb

,如图所示,f-f线与g-g线之间)的掺杂浓度dp

sjb

低于中间第二p型掺杂柱(p

sjm

,如图所示,e-e线与f-f线之间)的掺杂浓度dp

sjm

,且dp

sjm

低于顶部第三p型掺杂柱(p

sjt

,如图所示,d-d线与e-e线之间)的掺杂浓度dp

sjt

,即dp

sjb

《dp

sjm

《dp

sjt

。底部第一外延层和第一n型掺杂柱524的掺杂浓度dn

sjb

高于位于sj区底部、缓冲区502附近的底部第一p型掺杂柱(p

sjb

,如图所示,f-f线与g-g线之间)的掺杂浓度dp

sjb

(dn

sjb

》dp

sjb

);中间第二外延层和第二n型掺杂柱525的掺杂浓度dn

sjm

与位于sj区中间区域的中间第二p型掺杂柱(p

sjm

,如图所示,e-e线与f-f线之间)的掺杂浓度dp

sjm

相同(dn

sjm

=dp

sjm

);顶部第三外延层和第三n型掺杂柱526的掺杂浓度dn

sjt

低于位于sj区顶部、ocb区附近的顶部第三p型掺杂柱(p

sjt

,如图所示,d-d线与e-e线之间)的掺杂浓度dp

sjt

(dn

sjt

《dp

sjt

)。此外,位于ocb区的所有p型掺杂柱p

oct

和p

ocb

都具有相同的掺杂浓度dp

oc

,其与位于sj区中间区域的中间第二p型掺杂柱p

sjm

的掺杂浓度dp

sjm

相同。

68.图5b是图5a所示的优选实施例的横截面图,并分别揭示了n柱和p柱掺杂浓度沿垂直方向的变化。

69.图6a是根据本发明的另一个优选实施例的横截面图,该实施例具有改进的器件结构,并揭示了n型外延层掺杂浓度、n柱&p柱掺杂浓度沿垂直方向的变化。所述的n沟道沟槽式半导体功率器件与图5a所述的发明具有相似的结构,除了在本发明中,位于ocb区t

ocb

(b-b线与e-e线之间)的n型外延层包括三个具有不同掺杂浓度的阶梯外延层:掺杂浓度为d1的底部第一外延层(n

ocb

,如图所示,d-d线与e-e线之间)603,掺杂浓度为d2的中间第二外延层(n

ocm

,如图所示,c-c线与d-d线之间)623以及掺杂浓度为d3的顶部第三外延层(n

oct

,如图所示,b-b线与c-c线之间)633,其中,d1,d2和d3的关系为d3《d2《d1,以进一步降低比导通电阻。其中,d2可以是d1和d3的平均值。位于源体区t

sb

的外延层的掺杂浓度与位于ocb区的顶部第三外延层633相同,其高于位于sj区的中间第二外延层和第二n型掺杂柱(n

sjm

,如图所示)625的掺杂浓度dn

sjm

。此外,位于ocb区的所有的p型掺杂柱p

oct

,p

ocm

和p

ocb

都具有相同的掺杂浓度dp

oc

,其与位于sj区中间区域的中间第二p型掺杂柱p

sjm

的掺杂浓度dp

sjm

相同。

70.图6b是图6a所示的优选实施例的横截面图,并分别揭示了n柱和p柱掺杂浓度沿垂直方向的变化。

71.图7a是根据本发明的另一个优选实施例的横截面图,该实施例具有改进的器件结构,并揭示了n型外延层掺杂浓度、n柱&p柱掺杂浓度沿垂直方向的变化。所述的n沟道沟槽式半导体功率器件与图3a所述的发明具有相似的结构,除了在本发明中,在ocb区t

ocb

中具有不同的外延层和不同的第一绝缘层706。在本发明中,位于ocb区t

ocb

的外延层为具有均匀掺杂浓度d1的单一外延层(n

oc

,如图所示,b-b线与c-c线之间)703,且d1高于位于sj区的顶部第三外延层和第三n型掺杂柱(n

sjt

,如图所示,c-c线与d-d线之间)726的掺杂浓度dn

sjt

。位于源体区t

sb

的外延层的掺杂浓度d

sb

与位于ocb区的单一外延层703的掺杂浓度相同。此外,栅沟槽704内的第一绝缘层706具有两个阶梯氧化层结构:沿栅沟槽704下侧壁和底部的、沿栅沟槽侧壁具有均匀第一厚度tox,b的下氧化层,以及具有均匀第二厚度tox,u的上氧化层,其中,tox,b和tox,u的关系为tox,b》tox,u,以在保持相同击穿电压的同时进一步降低比导通电阻。

72.图7b是图7a所示的优选实施例的横截面图,并分别揭示了n柱和p柱掺杂浓度沿垂

直方向的变化。

73.图8a是根据本发明的另一个优选实施例的横截面图,该实施例具有改进的器件结构,并揭示了n型外延层掺杂浓度、n柱&p柱掺杂浓度沿垂直方向的变化。所述的n沟道沟槽式半导体功率器件与图5a所述的发明具有相似的结构,除了在本发明中,在ocb区t

ocb

中具有不同的外延层和不同的第一绝缘层806。在本发明中,位于ocb区t

ocb

的外延层为具有均匀掺杂浓度d1的单一外延层(n

oc

,如图所示,b-b线与c-c线之间)803,且d1高于位于sj区的底部第一外延层和第一n型掺杂柱(n

sjb

,如图所示,e-e线与f-f线之间)824的掺杂浓度dn

sjb

。位于源体区t

sb

的外延层的掺杂浓度d

sb

与位于ocb区的单一外延层803的掺杂浓度相同。此外,栅沟槽804内的第一绝缘层806具有两个阶梯氧化层结构:沿栅沟槽804下侧壁和底部的、沿栅沟槽侧壁具有均匀第一厚度tox,b的下氧化层,以及具有均匀第二厚度tox,u的上氧化层,其中,tox,b和tox,u的关系为tox,b》tox,u,以在保持相同击穿电压的同时进一步降低比导通电阻。

74.图8b是图8a所示的优选实施例的横截面图,并分别揭示了n柱和p柱掺杂浓度沿垂直方向的变化。

75.图9a是根据本发明的另一个优选实施例的横截面图,该实施例具有改进的器件结构,并揭示了n型外延层掺杂浓度、n柱&p柱掺杂浓度沿垂直方向的变化。所述的n沟道沟槽式半导体功率器件与图3a所述的发明具有相似的结构,除了不同的第一绝缘层906。在本发明中,栅沟槽904内的第一绝缘层906具有两个阶梯氧化层结构:沿栅沟槽904下侧壁和底部的、沿栅沟槽侧壁具有均匀第一厚度tox,b的下氧化层,以及具有均匀第二厚度tox,u的上氧化层,其中,tox,b和tox,u的关系为tox,b》tox,u,以在保持相同击穿电压的同时进一步降低比导通电阻。

76.图9b是图9a所示的优选实施例的横截面图,并分别揭示了n柱和p柱掺杂浓度沿垂直方向的变化。

77.图10a是根据本发明的另一个优选实施例的横截面图,该实施例具有改进的器件结构,并揭示了n型外延层掺杂浓度、n柱&p柱掺杂浓度沿垂直方向的变化。所述的n沟道沟槽式半导体功率器件与图5a所述的发明具有相似的结构,除了不同的第一绝缘层1006。在本发明中,栅沟槽1004内的第一绝缘层1006具有两个阶梯氧化层结构:沿栅沟槽1004下侧壁和底部的、沿栅沟槽侧壁具有均匀第一厚度tox,b的下氧化层,以及具有均匀第二厚度tox,u的上氧化层,其中,tox,b和tox,u的关系为tox,b》tox,u,以在保持相同击穿电压的同时进一步降低比导通电阻。

78.图10b是图10a所示的优选实施例的横截面图,并分别揭示了n柱和p柱掺杂浓度沿垂直方向的变化。

79.图11是根据本发明的另一个优选实施例的横截面图,该实施例具有改进的器件结构,并揭示了n型外延层掺杂浓度、n柱&p柱掺杂浓度沿垂直方向的变化。所述的n沟道沟槽式半导体功率器件与图2a所述的发明具有相似的结构,除了在本发明中,在栅沟槽1104内具有与图2a不同的屏蔽栅结构。在每个栅沟槽1104中,屏蔽栅极(sg,如图所示)1105位于沟槽中间,栅极(g,如图所示)1107围绕屏蔽栅极1105的上部两侧形成。

80.图12a是根据本发明的另一个优选实施例的横截面图,该实施例具有改进的器件结构,并揭示了n型外延层掺杂浓度、n柱&p柱掺杂浓度沿垂直方向的变化。所述的n沟道沟

槽式半导体功率器件为igbt(绝缘栅双极晶体管)器件,本发明与图3a所述的发明具有相似的结构,除了在本发明中,所述igbt器件形成在p 衬底1200之上。

81.图12b是图12a所示的优选实施例的横截面图,并分别揭示了n柱和p柱掺杂浓度沿垂直方向的变化。

82.图13是根据本发明的另一个优选实施例的横截面图,该实施例具有改进的器件结构,并揭示了n型外延层掺杂浓度、n柱&p柱掺杂浓度沿垂直方向的变化。所述的n沟道沟槽式半导体功率器件与图12所述的发明具有相似的结构,除了在本发明所述的igbt器件中,还进一步包括多个位于p 衬底1300的重掺杂n 区1340,用以形成多个位于衬底、交替排列的p 区和n 区。

83.图14a是根据本发明的另一个优选实施例的横截面图,该实施例具有改进的器件结构,并揭示了n型外延层掺杂浓度、n柱&p柱掺杂浓度沿垂直方向的变化。所述的n沟道沟槽式半导体功率器件为另一个igbt器件,本发明与图5a所述的发明具有相似的结构,除了在本发明中,所述igbt器件形成在p 衬底1400之上。

84.图14b是图14a所示的优选实施例的横截面图,并分别揭示了n柱和p柱掺杂浓度沿垂直方向的变化。

85.虽然依照优选实施例对本发明进行了描述,但应该理解的是上述公开不能被视为是对本发明的限制。上述所描述的实施例通常为n沟道器件,通过反转导电类型的极性,实施例也可应用于p沟道器件。在阅读了上述公开的内容之后,各种替代和修改对于本技术领域的技术人员无疑是显而易见的。因此,附后的权利要求应被解释为涵盖落入本发明的真正精神和范围内的所有替代和修改。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。