适用于ldpc译码器的存储寻址方法

技术领域

1.本发明属于通信领域,特别是涉及一种适用于ldpc译码器的存储寻址方法。

背景技术:

2.ldpc码,即低密度奇偶校验码(low density parity check code),于1962年由gallager博士首次提出,并于1996年被mackey和neal重新发现。ldpc码本身拥有优越的纠错性能以及较低的硬件实现复杂度,因此广泛应用于深空通信领域。

3.随着技术的进步,学术界针对ldpc提出了各种译码算法。其中,概率域bp译码算法是ldpc码主流的译码算法之一,但该算法需要大量的乘法运算,很难通过硬件电路实现。对数域llr(log likely rate)bp译码算法将概率域bp译码算法中的乘法运算变为了加法运算,减小了运算复杂度,但由于存在对数运算,硬件电路实现复杂度依然很高。最小和译码算法(msa)是对对数域llr bp译码算法的进一步简化,简化后的msa只需加法和比较运算。乘性修正最小和译码算法(nmsa)是对msa的修正,使其纠错性能进一步地接近对数域llr bp译码算法。nmsa虽然运算复杂度低,极其适合硬件电路实现,但由于其基于两相信息传递(tpmp)的译码机制,因此存在较多的无效等待时间。

4.随着通信技术的发展,对译码速度和效率都进一步提出了要求,如何设计相应的基于fpga的译码器进行ldpc译码并获得并行高速译码效率,是本领域技术人员面临的问题。

技术实现要素:

5.本发明主要解决的技术问题是提供一种适用于ldpc译码器的存储寻址方法,在实现较低运算复杂度的同时获得并行高速译码效率。

6.为解决上述技术问题,本发明采用的技术方案是:

7.提供一种适用于ldpc译码器的存储寻址方法,包括:

8.s201:分配ram阵列;

9.s202:通过位拼接的方式在ram阵列中存储信道初始信息;

10.s203:计算ram阵列中ram的起始读地址和起始偏移地址,并保存;

11.s204:根据起始读地址和起始偏移地址,产生ram的读地址和偏移地址;

12.s205:根据ram的读地址读取ram中的信息,将信息根据偏移地址进行数据位序调整后,送入校验节点更新单元或者变量节点更新单元进行处理;

13.s206:将校验节点更新单元或者变量节点更新单元处理后的信息,按顺序写入对应的ram。

14.进一步地,步骤s201还包括:

15.用于存储信道初始信息的ram阵列为第一存储ram,用于存储中间传递信息的ram阵列为第二存储ram和第三存储ram,其中,中间传递信息包括纵向更新信息和横向更新信息,第二存储ram用于存储纵向更新信息,第三存储ram用于存储横向更新信息;

16.进一步地,步骤s201还包括:

17.给第一存储ram分配16块ram,给第二存储ram分配64块ram,给第三存储ram分配64块ram,其中每块ram可存储511个长度为7比特的数据。

18.进一步地,步骤s202还包括:

19.将ldpc译码器使用的校验矩阵h按照行均匀分成14块,按照列均匀分成112块,分块后的每一块最小子矩阵大小均为73

×

73,对每个最小子矩阵同时进行迭代更新。

20.进一步地,步骤s202还包括:

21.在存储时信道初始信息采用6位量化,中间传递信息采用7位量化,也就是信道初始信息的数据包括1位符号位和5位绝对值,中间传递信息的数据比信道初始信息的数据多一位小数位。

22.进一步地,步骤s202中位拼接的方式还包括:

23.将信道初始信息进行分组,每一组信道初始信息包含511个数据,将每块ram的位宽设置为49,深度设置为73。

24.进一步地,步骤s202还包括:

25.每块ram包含0-72个存储地址,每个存储地址中存储7个数据,每个数据包含7个比特;

26.将7个数据按照从左至右的顺序依次赋以1-7的偏移地址,存储时相邻数据彼此间隔73个位序。

27.进一步地,步骤s203采用以下方法计算第二存储ram中的64块ram的起始读地址和起始偏移地址:

28.第一步,检索校验矩阵h第1行和第512行64个元素1的位置,获得第一位置索引;

29.第二步,将第一位置索引全部归一化至区间(1,511),获得第二位置索引;其中,第二位置索引是将第一位置索引除以511之后获得的余数;

30.第三步,将区间(1,511)再以73为间隔划分为7个子区间,依据第二位置索引所处子区间的不同分别对相应的ram赋以1~7的起始偏移地址;其中起始偏移地址是将第二位置索引整除73之后,再向上取整获得;

31.第四步,将第二位置索引全部归一化至(1,73)区间,获得第三位置索引,再将第三位置索引减去1获得起始读地址,其中第三位置索引是将第二位置索引除以73之后获得的余数。

32.进一步地,步骤s203采用以下方法计算第三存储ram中的64块ram的起始读地址和起始偏移地址:

33.第一步,检索校验矩阵h的第511*n 1列中64个元素1的位置,获得第一位置索引,其中n为整数,依次取值为n=0,1,

…

,15;

34.第二步,将第一位置索引全部归一化至区间(1,511),获得第二位置索引;其中,第二位置索引是将第一位置索引除以511之后获得的余数;

35.第三步,将区间(1,511)再以73为间隔划分为7个子区间,依据第二位置索引所处子区间的不同,分别对相应的ram赋以1~7的起始偏移地址;其中起始偏移地址是将第二位置索引整除73之后,再向上取整获得;

36.第四步,将第二位置索引全部归一化至(1,73)区间,获得第三位置索引,再将第三

位置索引减去1获得起始读地址,其中第三位置索引是将第二位置索引除以73之后获得的余数。

37.进一步地,步骤s204还包括:

38.每次迭代时,读地址从0至72进行循环赋值,每次循环包含73个时钟;

39.每当读地址循环一次,给偏移地址加1。

40.本发明的有益效果是:通过设计一种适用于ldpc译码器的存储寻址方法,通过位拼接方式存储,以及繁读简写的读取和写入,使得译码器在完成ldpc译码时,规避了地址访问冲突问题,并在实现较低运算复杂度的同时获得并行高速译码效率。

附图说明

41.图1是本发明一实施例的校验矩阵h的子循环矩阵a的元素1的轨迹示意图;

42.图2是本发明(8176,7154)ldpc码一实施例的的发送帧结构;

43.图3是本发明交迭的部分并行译码算法一实施例的横向更新和纵向更新示意图;

44.图4是本发明交迭的部分并行译码算法一实施例的计算流程图;

45.图5是本发明的译码器一实施例的架构示意图;

46.图6是本发明的迭代更新单元一实施例的架构示意图;

47.图7是本发明的存储寻址方法一实施例的流程图;

48.图8是本发明一实施例的存储信道初始信息的第一存储ram中ram的阵列分布示意图;

49.图9是本发明一实施例的存储中间传递信息的存储ram的阵列分布示意图;

50.图10是本发明一实施例的一组信道初始信息的存储示意图;

51.图11是本发明一实施例的“繁读简写”存储寻址方式示意图;

52.图12a-12c是本发明一实施例的横向更新过程示意图;

53.图13a-13c是本发明一实施例的纵向更新过程示意图;

54.图14是本发明一实施例的初始化存储单元初始化信道初始信息示意图;

55.图15是本发明的一实施例的初始化信道初始信息写入第一存储ram和第二存储ram的对应关系图;

56.图16是本发明的一实施例的校验节点更新单元的结构示意图;

57.图17是本发明的一实施例的变量节点更新单元的结构示意图;

58.图18是本发明一实施例的译码器迭代过程的时序图;

59.图19是本发明一实施例的校验方法流程图;

60.图20是本发明校验单元一实施例的校验存储示意图;

61.图21是本发明校验方法一实施例的校验子流程图;

62.图22是本发明校验装置一实施例的结构框图;

63.图23是本发明一实施例的量化效果比对图;

64.图24是本发明一实施例的最大迭代次数效果比对图。

具体实施方式

65.为了便于理解本发明,下面结合附图和具体实施例,对本发明进行更详细的说明。

附图中给出了本发明的较佳的实施例。但是,本发明可以以许多不同的形式来实现,并不限于本说明书所描述的实施例。相反地,提供这些实施例的目的是使对本发明的公开内容的理解更加透彻全面。

66.需要说明的是,除非另有定义,本说明书所使用的所有的技术和科学术语与属于本发明的技术领域的技术人员通常理解的含义相同。在本发明的说明书中所使用的术语只是为了描述具体的实施例的目的,不是用于限制本发明。

67.本发明使用的缩写含义定义如下:

68.qc-ldpc:quasi-cyslic-low-density parity-check codes,准循环ldpc码

69.ccsds:consultative committee for space data systems,空间数据系统咨询委员会

70.c2v:check to variable,横向更新

71.v2c:variable to check,纵向更新

72.cnu:check node unit,校验节点更新单元

73.vnu:variable node unit,变量节点更新单元

74.ram:random access memory,寄存器

75.本发明选用的ldpc码为qc-ldpc码,具体是国际空间数据系统咨询委员会ccsds的信道编码标准推荐的(8176,7154)ldpc码,该码本身具有准循环特性,且有较低的硬件实现复杂度。(8176,7154)ldpc码的校验矩阵h为规则的准循环矩阵,大小为1022

×

8176,每行的行重的值为32,每列的列重的值为4。其中,行重为每行“1”的个数,列重为每列“1”的个数。因此,校验矩阵h中只有极少数的“1”,绝大多数矩阵元素为零。校验矩阵h的具体构造如下所示:

[0076][0077]

其中,a代表校验矩阵h的子循环矩阵,a的下标代表其在校验矩阵h中的位置,每个a的大小均为511

×

511,每行的行重及每列的列重的值均为2。a中第l行(l=2,3,

…

,511)的元素1是第l-1行元素1的循环右移,本发明中将a中某个元素1不断循环右移510次后构成的点集合定义为此元素1的轨迹,如图1所示,可以看到a中有两条元素1的轨迹:l1和l2。

[0078]

图2给出了由ccsds规定的(8176,7154)ldpc码的发送帧结构。如图2所示,由于前18位为冻结比特0,不予发送,因此一段完整的发送帧只包含8160位比特,其中前7136位为信息比特,中间的1022位为校验比特,后两位为填充比特0。

[0079]

针对ldpc码的bp译码算法主要包括横向更新和纵向更新两个过程。其中,横向更新完成校验节点向变量节点传递信息(横向更新)的并行更新,负责此更新过程的模块称为校验节点更新单元,本发明简称为cnu。纵向更新完成变量节点向校验节点传递信息(纵向更新)的并行更新,负责此更新过程的模块称为变量节点更新单元,本发明简称为vnu。bp译码算法基于两相信息传递(tpmp)的译码机制,即横向更新过程和纵向更新过程两相交替进行。这种译码机制的优点是校验节点更新单元和变量节点更新单元可以利用到全新的传递信息,缺点是硬件利用率较低,仅为50%,基于bp译码算法优化而来的的nmsa算法依然使用两相信息传递(tpmp)机制,因此依然存在较多的无效等待时间这个问题。

[0080]

为了获取更高的并行译码速率,本发明使用交迭的部分并行译码算法进行ldpc译码。交迭的部分并行译码算法(overlapped nmsa)是针对nmsa算法存在较多的无效等待时间的这一问题,在nmsa的基础上提出的。

[0081]

进一步地,如图3所示,应用交迭的部分并行译码算法时,首先将校验矩阵h分块,对于横向更新过程,h按照行均匀分块;对于纵向更新过程,h按照列均匀分块,分块后的子循环矩阵中包含的行列数相同,设为k,图3中的a1就是一个子循环矩阵,包含k行k列。进行迭代时,每个子循环矩阵同时开始横向和纵向更新。如图中所示,在第1周期,对子循环矩阵a1的第1行进行横向更新,对子循环矩阵a1的第1列进行纵向更新,在第二周期,对子循环矩阵a1的第2行进行横向更新,对子循环矩阵a1的第2列进行纵向更新,这样依次更新到第k周期时,对子循环矩阵a1的第k行进行横向更新,对子循环矩阵a1的第k列进行纵向更新,至此完成了对子循环矩阵a1的一次迭代。同样地,对于其他子循环矩阵,也是在相同的k个周期内进行迭代,在第k周期时完成所有子循环矩阵的一次迭代。

[0082]

这样横向和纵向更新才能在相同的时间里完成迭代,并且同时完成迭代,从而达到在相同的时间内,该算法可以获得比nmsa多一倍的迭代次数。

[0083]

具体地,参考图4,实现交迭的部分并行译码算法的计算过程如下:

[0084]

s101:初始化,将信道初始信息进行存储,获得中间传递信息;

[0085]

s102:迭代更新,同时进行横向更新和纵向更新;

[0086]

s103:判决,根据更新后得到的子循环矩阵进行判决获取对应的译码码字;

[0087]

s104:校验,在每次迭代后进行校验,当校验结果为真,或者迭代次数达到最大值,则停止译码;否则跳转至s102,继续下一次迭代更新;

[0088]

s105:停止译码,输出译码结果。

[0089]

进一步地,步骤s101包括如下计算:

[0090][0091][0092]

l=1。

[0093]

其中,表示的对数似然比,表示的对数似然比,yj为信道初始信息,k为分块后子循环矩阵的行数或列数,q

ji

表示第j个变量节点传递给第i个校验节点的信息(纵向更新信息),r

ij

表示第i个校验节点传递给第j个变量节点的信息(横向更新信息),表示初始化的纵向更新信息,表示初始化的横向更新信息。l表示当前迭代次数,l=1,2,

…

,max,max为最大迭代次数。

[0094]

进一步地,步骤s102包括如下计算:

[0095]

for(j=i=1;j≤k;j ,i )

[0096]

{

[0097]

横向更新,校验节点更新单元计算处理

[0098]

[0099]

其中,j'∈r

i\j

表示在与第i个校验节点相连的变量节点集合中,删除第j个变量节点。η代表修正值,本发明中取值为0.75。

[0100]

纵向更新,变量节点更新单元计算处理如下:

[0101][0102][0103]

其中,i'∈c

j\i

表示在与第j个变量节点相连的校验节点集合中,删除第i个校验节点。

[0104]

};

[0105]

进一步地,步骤s103包括如下计算:

[0106]

若l(qj)《0,则cj=1,否则cj=0。其中,cj代表译码后的码字。

[0107]

进一步地,步骤s104包括如下计算:

[0108]

若h

·ct

=0或l=max,则停止译码,否则l=l 1并返回步骤s102继续迭代。

[0109]

该算法的主要思想是横向和纵向更新过程的同时进行,这种更新方式虽然导致校验节点更新单元和变量节点更新单元无法利用到全新的传递信息,以至于从迭代次数上来看,该算法的收敛速度确实慢于nmsa,但在相同的时间内,该算法可以获得比nmsa多一倍的迭代次数,这足以弥补其收敛速度慢的缺点。

[0110]

实施例一

[0111]

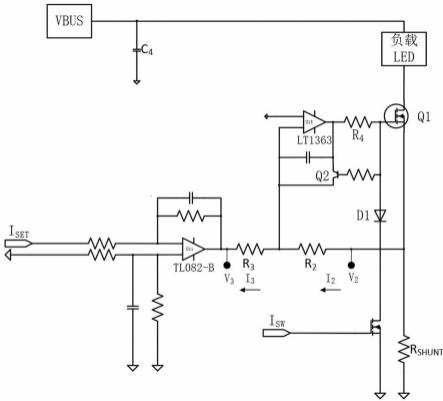

进一步地,如图5、6所示,本发明提供一种基于fpga的ldpc译码器,用于实现以上的qc-ldpc码的交迭的部分并行译码算法,在实现较低运算复杂度的同时获得并行高速译码效率。

[0112]

图5为译码器的架构图,包括:接收单元101、控制单元102、迭代更新单元103和校验单元104。

[0113]

接收单元101负责接收信道初始信息,并送入迭代更新单元103进行存储,同时通知控制单元102启动译码。

[0114]

控制单元102根据接收单元101的通知,控制迭代更新单元103开启迭代更新,并根据校验单元104的校验结果,决定是否进行下一次迭代。

[0115]

迭代更新单元103在收到接收单元101接收的信道初始信息后,进行存储,并根据控制单元102的控制命令启动迭代更新,将每次代更新的结果产生的判决信息输出至校验单元104。

[0116]

校验单元104根据判决信息进行校验,并输出结果至控制单元102。

[0117]

进一步地,参考图6,图6为迭代更新单元103的详细架构图,包括:初始化存储单元1031、寻址单元1032、变量节点更新单元库1033、校验节点更新单元库1034、数据位序调整单元1035以及相应的存储ram。

[0118]

进一步地,存储ram包括用于存储信道初始信息的第一存储ram1036,以及用于存储中间传递信息的第二存储ram1037和第三存储ram1038。

[0119]

进一步地,中间传递信息包括纵向更新信息(纵向更新时产生)和横向更新信息

(横向更新时产生),第二存储ram1037用于存储纵向更新信息,第三存储ram1038用于存储横向更新信息。

[0120]

进一步地,每个变量节点更新单元库1033包含112个变量节点更新单元,每个校验节点更新单元库1034包含14个校验节点更新单元,用于处理中间传递信息。这是由于为了进一步地提升并行度,将子循环矩阵划分为最小子矩阵,其中最小子矩阵大小为73*73,对每个最小子矩阵同时进行迭代更新。相应地,如果每个最小子矩阵要同时进行横向和纵向更新的话,就需要14个校验节点更新单元和112个变量节点更新单元。

[0121]

对每一帧的信道初始信息,会进行n次的迭代译码,直到成功完成本次信道初始信息的译码,结束迭代任务,进入下一帧的信道初始信息信息译码。其中,每一帧的信道初始信息结构如图2所示,前面18比特的冻结比特是不发送的,而最后两位填充比特在迭代时不需要处理,因此在本地存储时需要重新生成18位冻结比特的存储信息,同时丢弃最后两位填充比特。也就是说,在存储时每一帧对应为8176个数据,其中前18个数据为固定值,真正变化的是后面的8158个数据。

[0122]

在每一帧迭代译码的开始,初始化存储单元1031将信道初始信息存入第一存储ram1036,同时也将信道初始信息存入第二存储ram1037。

[0123]

在后续的同一帧的每次迭代初始化时,初始化存储单元1031从第一存储ram1036中读取信道初始信息存入第二存储ram1037,待本次迭代结束时,初始化存储单元1031将第二存储ram1037和第三存储ram1038清零。

[0124]

当属于同一帧的信道初始信息的所有迭代译码结束时,初始化存储单元1031除了将第三存储ram1038和第二存储ram1037清零之外,还将第一存储ram1036清零,以便接收下一帧的信道初始信息,开始新一帧的译码工作。

[0125]

在一次迭代更新过程中,当初始化存储单元1031完成初始化工作以后,控制单元102随即向寻址单元1032发送读使能信号,在读使能信号存在期间,寻址单元1032持续产生ram的读地址,从第二存储ram1037和第三存储ram1038读出的中间传递信息经数据位序调整单元1035处理后,分别送入校验节点更新单元库1034和变量节点更新单元库1033,经校验节点更新单元库1034和变量节点更新单元库1033处理后的中间传递信息再分别送回第三存储ram1038、第二存储ram1037进行存储。

[0126]

当一次迭代更新完成后,变量节点更新单元库1033将产生判决信息,校验单元104根据判决信息进行校验,输出校验结果,控制单元102根据校验单元104的校验结果选择继续迭代或者控制校验单元104输出译码结果。

[0127]

进一步地,为了实现实施例二中的寻址方法,本发明对于初始化存储单元1031、寻址单元1032以及数据位序调整单元1035进行如下优化设计。

[0128]

在信道初始信息到来后,参考图14,初始化存储单元1031从第一存储ram1036中对应ram的0地址开始,依次将地址中的数据读出,每当读至地址72后便返回地址0。读出的数据为原始数据,简记为db,db的低42位赋值给写入寄存器的高42位,相应的在信道初始信息末尾添加一位比特0后赋值给写入寄存器的低7位,之后再将写入寄存器中的值发送至第一存储ram1036和第二存储ram1037进行存储,如此循环7次后,便可实现将1组(511个)信道初始信息在ram中按照图10中所示进行存储。在存储了一帧初始信道信息(8158个数据)后,初始化存储单元1031通知控制单元102初始化存储完成。

[0129]

进一步地,当写入寄存器中的值发送至第一存储ram1036和第二存储ram1037时,二者对应关系如图15所示。其中,we代表写使能。由此,完成了第一存储ram1036和第二存储ram1037的同步初始化存储,注意这里没有将初始信息存入第三存储ram1038,而是在后续的迭代更新过程中,将横向更新的结果存入第三存储ram1038。

[0130]

进一步地,寻址单元1032负责产生第二存储ram1037(第三存储ram1038)中ram的读地址以及数据位序调整单元1035使用的偏移地址,产生的方法采用实施例二中的方法;数据位序调整单元1035采用桶形移位寄存器实现。

[0131]

在一次迭代过程中,偏移地址至多变化一次,若某块ram的起始读地址为0,则其偏移地址在整个迭代过程中都不会发生变化,即始终保持为起始偏移地址。在这种情况下,桶形移位寄存器若对偏移地址(3bit)进行完备的功能描述,对硬件资源是一种极大的浪费。因此,进一步地,本发明将寻址单元1032中产生的偏移地址(3bit)改为了偏移使能变量(1bit),当偏移使能为0时,桶形移位寄存器按照相应的起始偏移地址对输入数据进行循环左移,当偏移使能为1时,代表在原先的起始偏移地址上加一,桶形移位寄存器按照更新后的偏移地址对输入数据进行循环左移。

[0132]

为了配合上述优化调整,本发明将桶形移位寄存器划分为7个模块,sl_1,sl_2,

…

,sl_7。

[0133]

其中,sl_1在偏移使能为0时将输入数据寄存一次后输出,不作循环左移处理,当偏移使能为1时将输入数据循环左移7位后输出;

[0134]

sl_2在偏移使能为0时将输入数据循环左移7位后输出,当偏移使能为1时将输入数据循环左移14位后输出;

[0135]

sl_3在偏移使能为0时将输入数据循环左移14位后输出,当偏移使能为1时将输入数据循环左移21位后输出;

[0136]

sl_4在偏移使能为0时将输入数据循环左移21位后输出,当偏移使能为1时将输入数据循环左移28位后输出;

[0137]

sl_5在偏移使能为0时将输入数据循环左移28位后输出,当偏移使能为1时将输入数据循环左移35位后输出;

[0138]

sl_6在偏移使能为0时将输入数据循环左移35位后输出,当偏移使能为1时将输入数据循环左移42位后输出;

[0139]

sl_7在偏移使能为0时将输入数据循环左移42位后输出,当偏移使能为1时将输入数据循环左移49位后输出。

[0140]

根据第二存储ram1037(或者第三存储ram1038)中ram的起始偏移地址不同,将ram的输出数据与相应的sl_i,i=1,2,

…

,7相连,如某块ram的起始偏移地址为2,则将其输出数据与sl_2相连。这样既可使桶形移位寄存器达到原先电路的功能,也可使其消耗的硬件资源大大减少。

[0141]

进一步地,图16为校验节点更新单元的结构示意图,其中,符号运算单元基于树型运算结构,共分为6级,负责完成横向更新中对于输入数据符号位的计算处理。

[0142]

进一步地,本发明在校验节点更新单元中插入了6级流水线,第一级完成对输入数据取绝对值的操作,第2至5级“伴随次小值比较器”找出输入数据的次小值、最小值以及最小值的位置索引,第六级依据比较器得出的最小值位置索引对32个输出数据的低6位分别

赋以修正后的最小值或次小值,并对32个输出数据的最高位分别赋以符号运算单元的输出比特。这里并行处理32个数据,是因为h矩阵的行重为32。

[0143]

进一步地,图17为变量节点更新单元的结构示意图,本发明在变量节点更新单元中插入了6级流水线,第1级将输入数据转换为有符号数,第2级至第5级完成纵向更新中的内容,第6级对第5级的输出数据限幅并将其输出。这里并行处理4个数据,是因为h矩阵的列重为4。

[0144]

其中,前几级相加运算时,为了防止溢出,会增加位数。例如,从7位符号数增加到了9级符号数,而最终处理完的数据依然要换算成7位符号数输出给存储ram进行存储。因此,限幅运算就是将9位符号数限幅转为7级符号数。也就是说,将数据区间从[-128,127]转为[-32,31]。

[0145]

以上具体2级至5级流水线的计算过程,参考前面所述的交迭的部分并行译码算法中步骤s102中变量节点更新单元计算处理过程。

[0146]

如图18为加入流水线后的译码器迭代过程的完整时序图,其中cnu为校验节点更新单元,vnu为变量节点更新单元。在t0时刻,vnu已经进行到第4级流水线,也就是说,完成了纵向更新中的的计算,因此,满足了判决需要的前提条件,可以进行步骤s103中的判决计算,即:若l(qj)《0,则cj=1,否则cj=0。所以,在t0时刻,开始校验使能,随即就产生了判决比特。

[0147]

在变量节点更新单元的流水线中,第1级将输入数据转换为有符号数本应由校验节点更新单元在最后一级完成,本发明将这部分组合逻辑电路划分至变量节点更新单元,从而平衡校验节点更新单元和变量节点更新单元的时延路径长短,也就是说,变量节点更新单元的流水线与校验节点更新单元的流水线级数相等,使得在相同时钟周期内,可以同步完成各自的迭代更新过程。相反,如果二者流水线级数不相同,例如一个为4级,一个为8级,那么一次迭代就需要等待8级的那个更新单元完成迭代以后,才能完成。本发明将二者的流水线级数设置为相等的设计,不仅可以减少译码器完成一次迭代过程所用的时钟数,还可以使校验节点更新单元和变量节点更新单元的工作速率达到同步,减小控制单元102状态机的设计难度。

[0148]

实施例二

[0149]

进一步地,如图7所示,本发明提供一种更适合于高并行度译码器的存储寻址方法,该存储寻址方法不仅规避了地址访问冲突问题,而且简单高效。

[0150]

如图7所示,该方法包括:

[0151]

s201:分配ram阵列;

[0152]

s202:通过位拼接的方式在所述ram阵列中存储信道初始信息;

[0153]

s203:计算所述ram阵列中ram的起始读地址和起始偏移地址,并保存;

[0154]

s204:产生所述ram的读地址和偏移地址;

[0155]

s205:根据ram的读地址读取ram中的信息,将所述信息根据所述偏移地址进行数据位序调整后,送入校验节点更新单元或者变量节点更新单元进行处理;

[0156]

s206:将校验节点更新单元或者变量节点更新单元处理后的信息,按顺序写入对应的ram。

[0157]

以上步骤s204至步骤s206是每次迭代时按照先后顺序执行的。

[0158]

进一步地,对于步骤s201,包括对信道初始信息分配ram阵列和对中间传递信息分配ram阵列。

[0159]

进一步地,图8所示为存储信道初始信息的第一存储ram1036中ram的阵列分布示意图,图中共有16块ram,参考校验矩阵h中子循环矩阵a的定义,下式中的每列的两个子循环矩阵a共用同一块ram,例如a1,1和a2,1共用同一块ram。

[0160][0161]

其中,每511个信道初始信息划分为一组,一块ram负责存储一组信道初始信息。第一组只包含493个信道初始信息,因为在信息比特之前还有18位冻结比特0,最后两个信道初始信息为填充信息,可以不予接收。

[0162]

进一步地,图9所示为存储中间传递信息的存储ram的阵列分布示意图,由于校验矩阵中元素1代表校验节点和变量节点之间进行信息传递的确定联系,因此本发明中将中间传递信息设置为包括纵向更新信息(纵向更新时产生)和横向更新信息(横向更新时产生),将存储中间传递信息的存储ram分为第二存储ram1037和第三存储ram1038,第二存储ram1037用于存储纵向更新信息,第三存储ram1038用于存储横向更新信息。

[0163]

具体地,根据校验矩阵h的定义,一个子循环矩阵a中有两个元素1的轨迹,因此对每个子循环矩阵a分配四块ram,两块属于第二存储ram1037,用于存储子循环矩阵a在迭代更新中的纵向更新信息,两块属于第三存储ram1038,用于存储子循环矩阵a在迭代更新中的横向更新信息。因此,图9显示的是纵向更新信息或者横向更新信息的存储ram的阵列分布,即存储纵向更新信息的ram阵列包括64块ram,存储横向更新信息的ram阵列也包括64块ram。

[0164]

进一步地,对于步骤s202,还包括:

[0165]

将校验矩阵h按照行均匀分成14块,按照列均匀分成112块,分块后的每一块最小子矩阵大小均为73

×

73,对每个最小子矩阵同时进行迭代更新。这样就可以把大小为511

×

511的子循环矩阵a细化成7个73

×

73最小子矩阵b,,从而进一步提升并行计算速率。当最小子矩阵为73

×

73时,译码器完成一次迭代过程只需73 α个时钟,其中,α与译码器中插入的流水线级数有关。如实施例一中所示,分别在校验节点更新单元和变量节点更新单元中加入6级流水线,那么相应地需要完成一次迭代过程需要73 5=78个时钟。

[0166]

进一步地,对经过解调后输入到ldpc译码器的每一个信道初始信息,还进行限幅量化后再存储,即采用(6,7)量化方式,即信道初始信息采用6位量化,中间传递信息采用7位量化。也就是信道初始信息采用1位符号位和5位绝对值,中间传递信息比初始信息再多一位小数位。例如对于接收到的一帧信道初始信息,其中包含8176位信道初始信息,将每一位待处理的信道初始信息对应量化为6个比特之后,再进行存储。

[0167]

具体地,参考图23,在设计ldpc译码器时,需要将译码过程中的信息变量进行定点量化,因此会带来译码性能的部分损失。显然量化位数越多,译码性能损失越小,但硬件资源消耗也就越大。为确定译码器最终的量化位数,对三种量化方式进行了仿真实验,量化方式表达为(x,y)的形式,其中x代表译码器对信道初始信息的量化位数,y代表译码器对中间

传递信息的量化位数,这是由于横向更新时需要乘一个小于1的修正因子,因此在对信道初始信息的量化位数基础上再添加一位,表示小数位,从而在最大程度上保证译码器的量化精度。

[0168]

从图23可以看出,量化方式(x,y)的三种取值(6,7)、(7,8)及(8,9)对应三条不同的曲线,横轴为比特信噪比eb/n0,纵轴为误比特率(也称为误码率)。

[0169]

当比特信噪比eb/n0取值小于3.0时,三条曲线基本重合,也就是说,当比特信噪比eb/n0《3.0时,这三条曲线的误比特率随比特信噪比eb/n0的增加而下降的幅度是一致的。

[0170]

当比特信噪比eb/n0》3.0时,这三条曲线的误比特率随比特信噪比eb/n0的增加而下降的幅度是不同的。可以看出,此时在任何一个比特信噪比值(例如比特信噪比eb/n0=3.5时),随着量化方式中量化位数的提高,误比特率逐渐递减,即:

[0171]

(8,9)的误比特率《(7,8)的误比特率《(6,7)的误比特率。

[0172]

进一步地,当比特信噪比eb/n0》3.0时,随着比特信噪比eb/n0的增加,(7,8)相对于(6,7)的误比特率下降幅度较小,而(8,9)虽然相对于(6,7)的误比特率下降幅度较大,但量化位数越高也需要更多的硬件资源消耗。因此,本发明选择(6,7)量化方式为最优的方式。

[0173]

进一步地,将多个信道初始信息或中间传递信息通过位拼接的方式存储至ram的一个地址中,具体为首尾相连。如图10所示为对一组信道初始信息的存储示意图,图10中相同灰度的7个方块代表ram的一个存储地址,一个地址中的7个数据按照从左至右的顺序依次赋以1-7的偏移地址,并且相邻数据彼此间隔73个位序,其中每个数据包含7个比特。

[0174]

进一步地,将一块ram的位宽设置为49,深度设置为73,这样可以刚好将一组长度为511的信道初始信息通过位拼接的方式存储进一块ram,其中511代表数据个数,每个数据包含6个比特。通过以上拼接方式的存储,可以提高译码数据处理的并行度,也使得同时进行的横向更新和纵向更新可以更简便地实现。

[0175]

进一步地,步骤s203~s206中,为了更高效地实现校验节点更新单元和变量节点更新单元对中间传递信息的读取和写入,使用了图11所示的“繁读简写”存储寻址方式。该方式在读取时是根据实时生成的读地址进行读取,并根据实时生成的偏移地址进行数据位序调整之后,才输出给变量节点更新单元或者校验节点更新单元;在写入时,直接将变量节点更新单元或者校验节点更新单元处理后的信息进行位拼接后,以0地址为起始地址,依次写入对应的ram,无需进行读取时的读地址和偏移地址计算和寻址操作。

[0176]

具体地,第二存储ram1037和第三存储ram1038中的每块ram都有相应的起始读地址,起始偏移地址以及偏移地址。偏移地址标记为oa(3bit)。

[0177]

进一步地,步骤s203采用以下方法计算起始读地址和起始偏移地址:

[0178]

对于第二存储ram1037中的64块ram:

[0179]

第一步,检索校验矩阵h第1行和第512行64个元素1的位置,获得第一位置索引;

[0180]

第二步,将第一位置索引全部归一化至区间(1,511),获得第二位置索引;其中,第二位置索引是将第一位置索引除以511之后获得的余数,如果第一位置索引小于511,则第二位置索引还是赋以第一位置索引的值。

[0181]

第三步,将区间(1,511)再以73为间隔划分为7个子区间,依据第二位置索引所处子区间的不同分别对相应的ram赋以1~7的起始偏移地址;其中起始偏移地址是将第二位

置索引整除73之后,再向上取整获得。

[0182]

第四步,将第二位置索引全部归一化至(1,73)区间,获得第三位置索引,再将第三位置索引减去1获得起始读地址,其中第三位置索引是将第二位置索引除以73之后获得的余数。

[0183]

对于第三存储ram1038中的64块ram,首先检索h第511*n 1列(n=0,1,

…

,15)中64个元素1的位置索引,其他操作同上述相同,具体如下:

[0184]

第一步,检索校验矩阵h的第511*n 1列中64个元素1的位置,获得第一位置索引,其中n为整数,依次取值为n=0,1,

…

,15;

[0185]

第二步,将第一位置索引全部归一化至区间(1,511),获得第二位置索引;其中,第二位置索引是将第一位置索引除以511之后获得的余数;

[0186]

第三步,将区间(1,511)再以73为间隔划分为7个子区间,依据第二位置索引所处子区间的不同,分别对相应的ram赋以1~7的起始偏移地址;其中起始偏移地址是将第二位置索引整除73之后,再向上取整获得;

[0187]

第四步,将第二位置索引全部归一化至(1,73)区间,获得第三位置索引,再将第三位置索引减去1获得起始读地址,其中第三位置索引是将第二位置索引除以73之后获得的余数。

[0188]

进一步地,以下给出了第二存储ram1037中的64块ram的起始读地址和起始偏移地址的计算过程:

[0189]

其中,将校验矩阵h第1行和第512行元素1的第一索引位置分别记作ra1st

1,j

和ra1st

512,j

,j=1,2,

…

,32,起始偏移地址记作oa1st

1,j

和oa1st

512,j

,j=1,2,

…

,32。

[0190]

第一步,检索校验矩阵h第1行元素1的第一位置索引:

[0191]

p

1,j

=find(h(1,:)==1);j=1,2,

…

,32;

[0192]

第二步,将p

1,j

和p

512,j

归一化至[1~511]区间内:

[0193]

for j=1:32

[0194]

while p

1,j

》511

[0195]

p

1,j

=p

1,j-511;

[0196]

end

[0197]

end

[0198]

第三步,依据p

1,j

所属区间的不同分别赋以不同的起始偏移地址:

[0199]

switch p

1,j

[0200]

case[1,73]

[0201]

oa1st

1,j

=1;

[0202]

case[74,146]

[0203]

oa1st

1,j

=2;

[0204]

case[147,219]

[0205]

oa1st

1,j

=3;

[0206]

case[220,292]

[0207]

oa1st

1,j

=4;

[0208]

case[293,365]

[0209]

oa1st

1,j

=5;

[0210]

case[366,438]

[0211]

oa1st

1,j

=6;

[0212]

case[439,511]

[0213]

oa1st

1,j

=7;

[0214]

end

[0215]

第四步,将p

1,j

和p

512,j

归一化至[0~72]区间内:

[0216]

for j=1:32

[0217]

while p

1,j

》73

[0218]

p

1,j

=p

1,j-73;

[0219]

end

[0220]

while p

512,j

》73

[0221]

p

512,j

=p

512,j-73;

[0222]

end

[0223]

p

1,j

=p

1,j-1;

[0224]

p

512,j

=p

512,j-1;

[0225]

end

[0226]

进一步地,步骤s203中采用以上方法计算获得起始读地址和起始偏移地址之后,将起始读地址和起始偏移地址保存,以供后续多次迭代使用。该起始读地址和起始偏移地址一旦计算完成,将不用修改,也就是说对于本发明中的译码器来说,是唯一不变的常量数据。因此,可以将起始读地址和起始偏移地址保存在译码器能够读取的一个本地文件中,也可以在启动译码器时初始化写入译码器的寻址单元,以供后续迭代中计算新的读地址和偏移地址使用。

[0227]

进一步地,步骤s204包括:每次迭代时,读地址会随着系统时钟上升沿的到来依次加1,当读至地址72时,下一时钟便会返回地址0。偏移地址则会在读地址从地址72返回地址0时加1,其余时刻则保持不变。

[0228]

进一步地,步骤s205包括:数据位序调整使用一种桶形移位寄存器实现,依据偏移地址oa的值将输入数据进行相应地循环左移后输出。例如:oa=1,输入数据保持不变;oa=2,将输入数据循环左移7位;oa=3,将输入数据循环左移14位;以此类推,oa的取值为1~7的整数。这样循环处理后,输出数据发送给变量节点更新单元和校验节点更新单元进行后续计算处理。

[0229]

进一步地,步骤s206包括:将变量节点更新单元或校验节点更新单元的输出数据按照特定的顺序进行位拼接后,以0地址为起始地址,依次写入对应的ram。

[0230]

具体地,下面本发明以图1中的l1轨迹为例,说明该轨迹对应的横向更新和纵向更新的具体的数据读取和写入过程。

[0231]

如图1所示,第1行元素1的位置索引是177,经过计算后得到第二存储ram1037的起始读地址为30,起始偏移地址为3。具体地,这时177小于511,则第二位置索引为177,整除73向上取整,获得起始偏移地址为3。第三位置索引为177除以73之后的余数31,而31-1=30,则30就是起始读地址。

[0232]

具体参考图12a-c中显示的横向更新过程:当迭代过程开始后,读地址会从地址30开始逐一向后滑动,而偏移地址会一直保持不变,直到读地址从地址72返回地址0时,偏移地址才加1变为4。当校验节点更新单元(变量节点更新单元)开始输出数据,校验节点更新单元的输出数据按从上到下的顺序进行位拼接后以地址0为起始地址,依次写入第三存储ram1038即可。

[0233]

图12a为读指针指向第二存储ram的起始读地址30,起始偏移地址oa为3,则由第二存储ram的起始读地址30读出,得到读出的数据,然后对该读出的数据进行调整位序,由于起始偏移地址oa=3,则需要左移两个数据位,例如,可以看出图12a中的输入数据中的“3”是由读出的数据中的“3”循环左移2个数据位得到。然后,该输入数据对应处理为校验节点更新单元输出数据d1d2d3d4d5d6d7,按位拼接为写入数据d1d2d3d4d5d6d7,再写入到第三存储ram中的写指针对应的地址0中进行存储。需要注意的是,这里调整位序是指对数据位进行调整,而每个数据用7个比特表示时,则对应循环左移调整的比特位则是2*7=14个比特位。

[0234]

图12b为读指针指向第二存储ram的读地址72,偏移地址oa为3,则由第二存储ram的读地址72读出,得到读出的数据,然后对该读出的数据进行调整位序,由于偏移地址oa=3,则需要左移两个数据位,同图12a中类似。然后,该输入数据对应处理为校验节点更新单元输出数据d1d2d3d4d5d6d7,按位拼接为写入数据d1d2d3d4d5d6d7,再写入到第三存储ram中的写指针对应的地址42中进行存储。

[0235]

图12c为读指针指向第二存储ram的读地址0,偏移地址oa此时要加1,变为4,则由第二存储ram的读地址0读出,得到读出的数据,然后对该读出的数据进行调整位序,由于偏移地址oa=4,则需要左移三个数据位,也就是3*7=21个比特。然后,该输入数据对应处理为校验节点更新单元输出数据d1d2d3d4d5d6d7,按位拼接为写入数据d1d2d3d4d5d6d7,再写入到第三存储ram中的写指针对应的地址43中进行存储。如图12a-c中所示,写指针分别对应为0,42和43,因此是顺序写入第三存储ram,没有偏移地址。从而实现了繁读简写的过程。

[0236]

进一步地,参考图1,纵向更新时,第1列元素1的位置索引是336,经过计算后得到第三存储ram1038的起始读地址为43,起始偏移地址为5。具体地,这时336小于511,则第二位置索引为336,整除73向上取整,获得起始偏移地址为5。第三位置索引为336除以73之后的余数44,而44-1=43,则43就是起始读地址。

[0237]

具体参考图13a-c中显示的纵向更新过程,同横向更新过程类似,也是繁读简写。

[0238]

图13a为读指针指向第三存储ram的起始读地址43,偏移地址oa为5,则由第三存储ram的起始读地址43读出,得到读出的数据,然后对该读出的数据进行调整位序,由于偏移地址oa=5,则需要左移4个数据位,例如,可以看出图13a中的输入数据中的“5”是由读出的数据中的“5”循环左移4个数据位得到。然后,该输入数据对应处理为变量节点更新单元输出数据d1d2d3d4d5d6d7,按位拼接为写入数据d1d2d3d4d5d6d7,再写入到第二存储ram中的写指针对应的地址0中进行存储。需要注意的是,这里调整位序是指对数据位进行调整,而每个数据用7个比特表示时,则对应循环左移调整的比特位则是2*7=14个比特位。

[0239]

图13b为读指针指向第三存储ram的读地址72,偏移地址oa为5,则由第三存储ram的读地址72读出,得到读出的数据,然后对该读出的数据进行调整位序,由于偏移地址oa=

5,则需要左移4个数据位,同图13a中类似。然后,该输入数据对应处理为变量节点更新单元输出数据d1d2d3d4d5d6d7,按位拼接为写入数据d1d2d3d4d5d6d7,再写入到第二存储ram中的写指针对应的地址29中进行存储。

[0240]

图13c为读指针指向第三存储ram的读地址0,偏移地址oa此时要加1,变为6,则由第三存储ram的读地址0读出,得到读出的数据,然后对该读出的数据进行调整位序,由于偏移地址oa=6,则需要左移5个数据位,也就是5*7=35个比特。然后,该输入数据对应处理为变量节点更新单元输出数据d1d2d3d4d5d6d7,按位拼接为写入数据d1d2d3d4d5d6d7,再写入到第二存储ram中的写指针对应的地址30中进行存储。

[0241]

实施例三

[0242]

进一步地,参考图18-22,本发明对校验单元做出了优化设计。

[0243]

校验单元主要负责对每次迭代后产生的译码结果进行校验以及对迭代次数进行计数,常规的校验方式为h

·ct

=0,即将译码结果代入校验矩阵h中计算校验值,若校验值为0,则译码正确,将判决比特进行输出,否则译码错误,选择继续迭代或退出译码。然而这种校验方式通过硬件电路实现较复杂,且校验过程需要的时钟周期较长,不符合高速译码的设计需求。

[0244]

本发明提出一种更为实用的适用于ldpc译码器的校验方法,如图19所示,包括步骤:

[0245]

s301:在第n次迭代更新时,将迭代更新产生的判决结果存储为第n次判决结果,其中n为大于或等于1的正整数;

[0246]

s302:将第n次判决结果与第n-1次判决结果进行比对校验,获得第n次校验结果,第n次校验结果为相同或者不同;

[0247]

s303:对第n次校验结果进行判断,若第n次校验结果为相同或者n达到最大迭代次数,则跳转至步骤s304;否则,结束本次校验;

[0248]

s304:输出译码结果。

[0249]

具体地,判决结果由取值为1或者0的比特组成,将一次迭代结完成时获得的所有判决结果进行拼接就获得完整的译码结果。

[0250]

以上方法实际上就是对比本次迭代的译码结果和上次迭代的译码结果,如果发现两次译码结果相同则认为译码已经完成,否则继续迭代直到达到最大迭代次数。这种方法是基于译码算法的收敛性,即当译码正确后再次进行迭代其结果也应该是正确的,这样硬件电路实现的复杂度就降低了。

[0251]

进一步地,步骤s302还包括:

[0252]

s3021:第n次判决结果包括多个不同时刻实时生成的第n次判决比特;

[0253]

s3022:将每一时刻新生成的第n次判决比特,与对应时刻的第n-1次判决比特,进行比对校验;

[0254]

s3023:当比对校验结果为不同,则停止比对校验,并确认第n次校验结果为不同。

[0255]

其中,对应时刻的第n-1次判决比特,是指上次迭代更新中对应同一时刻生成的第n-1次判决比特。

[0256]

具体地,设第n次判决结果为比特集合b=[b1,b2,

…

,bm],其中bm为第m时刻新生成的第n次判决比特;

[0257]

相应地,设第n-1次判决结果为比特集合a=[a1,a2,

…

,am],其中am为第m时刻新生成的第n-1次判决比特;

[0258]

则步骤s3022指的是:在第m时刻,将bm与am进行比对校验。

[0259]

具体地,如实施例二中所述,每次迭代更新时间等于一个最小子矩阵的迭代更新时间,例如最小子矩阵为73*73,则需要73个时钟完成一次迭代更新。而对应地,每个最小子矩阵会在73个时刻依次产生判决比特。假设第1时刻至第49时刻,比对结果为相同,则继续进行第50时刻的比对校验。当第50时刻比对校验结果为不同,则停止比对校验,并确认本次迭代更新的校验结果为不同,从而不必等到73个时刻的判决比特都比对一遍才得出结果。

[0260]

由此可以看出,由于本发明采用的ldpc码的码长为8176比特,若是直接进行校验,则需要两个长度为8176比特的寄存器,一个存储上次迭代的译码结果,一个存储本次迭代的译码结果,之后二者进行完整对比。而采用以上每一时刻进行实时对比的方法,可以对连续输入的判决比特进行实时对比,一旦检测到某个判决比特同上次迭代的不一致,则不论后续判决比特相同与否,都将本次译码结果判定为有错。这样可以不需要比对完整的两次迭代生成的ldpc码,而是一旦检测到中间有不同比特位,就确认本次校验结果为不同,从而将本次译码结果判定为有错,从而在获得本次完整译码之前就获得了校验结果,进一步提升了效率,节省了存储资源。

[0261]

进一步地,为了节省存储空间和进一步提升计算效率,本发明采用的校验单元的存储方案,具体阐述如下。

[0262]

进一步地,步骤s301还包括:

[0263]

将ldpc码的校验矩阵h按照行均匀分成14块,按照列均匀分成112块,从而把大小为511

×

511的子循环矩阵a分成7个73

×

73最小子矩阵b,在每次迭代更新时对每个最小子矩阵b同时进行迭代更新;

[0264]

将同一时刻实时产生的一组判决比特的比特个数确定为98;

[0265]

对应设置98个长度为73比特的判决比特寄存器,用于存储判决比特。

[0266]

具体地,图2给出了由ccsds规定的(8176,7154)ldpc码的发送帧结构。如图2所示,由于前18位为冻结比特0,不予发送,因此一段完整的发送帧只包含8160位比特,其中前7136位为信息比特,中间的1022位为校验比特,后两位为填充比特0。而由前面实施例可知,ldpc码的校验矩阵h按照行均匀分成14块,按照列均匀分成112块,从而把大小为511

×

511的子循环矩阵a分成7个73

×

73最小子矩阵b,在每次所述迭代更新时对每个所述最小子矩阵b同时进行迭代更新。

[0267]

7136 18=7154=73*98;

[0268]

由以上计算可以推导出ldpc码的7136位信息比特最多包含98个73

×

73最小子矩阵b,因此将每次迭代更新时,同一时刻产生一组判决比特的个数确定为98。

[0269]

进一步地,步骤s301还包括:

[0270]

将不同时刻产生的判决比特按照由低到高的顺序存入判决比特寄存器;

[0271]

当存入一组判决比特时,先将每个判决比特寄存器中的比特数据左移一位,再将每个判决比特,分别对应存入一个判决比特寄存器的第0位中,每个判决比特寄存器保存一位判决比特,第0位为最低位。

[0272]

当第n次判决结果存储完毕,将覆盖判决比特寄存器中存储的第n-1次判决结果,

从而循环利用判决比特寄存器。

[0273]

进一步地,步骤s302还包括:

[0274]

当存入一组判决比特的同时,判决比特寄存器中的最高位判决比特移出,并组成另一组判决比特,对这两组判决比特进行进行比对校验,并记录比对结果,比对结果为相同或者不同。

[0275]

进一步地,步骤s302还包括:

[0276]

进行比对校验时,将98个本次迭代产生的判决比特,通过位拼接获得本次判决比对信号,将判决比特寄存器左移前的最高位判决比特,通过位拼接获得上次判决比对信号,然后将本次判决比对信号与上次判决比对信号进行比对,获得比对结果。

[0277]

具体实现方式如下:

[0278]

参考图18,其中cnu为校验节点更新单元,vnu为变量节点更新单元。当译码器进行至变量节点更新单元(或校验节点更新单元)第四级,即图18中的t0时刻,开始产生第一组(98个)判决比特,校验使能ce此时被拉高,校验单元开始校验并存储判决比特。

[0279]

具体地,为什么每次产生的一组判决比特为98个,原因如下:

[0280]

参考图2,一帧信道初始信息里面包含的冻结位和信息位为18 7136=7154。因此,只需要对前面这7154个数据进行判决得到真正的信息,后面的校验比特位无需考虑。而本发明中最小子矩阵是73*73,7154=73*98,因此,每次产生的判决比特为98个。

[0281]

图20为校验存储示意图,图中msg_i,i=1,2,

…

,98为负责存储判决比特的寄存器,每个寄存器的长度为73位比特,err为错误标志信号,初始值为0,0表示无错,1表示有错,bin[97:0]是由98个本次迭代产生的判决比特通过位拼接而成的信号,ref_bin[97:0]是由寄存器msg_i,i=1,2,

…

,98的最高位通过位拼接而成的信号。当校验单元检测到校验使能ce为高时,寄存器msg_i左移一位并将相应的判决比特存入第0位中,与此同时bin[97:0]与ref_bin[97:0]进行对比,若二者相同则err信号(错误值)保持不变,否则将err信号(错误值)置为1。经过73个时钟,校验单元便完成了对7154个判决比特的存储以及初步校验。

[0282]

后续校验子流程如图21所示,其中错误值对应前面所述的err信号,本次对应信号bin[97:0],上次对应信号ref_bin[97:0]。首先,将迭代次数赋初值为0,然后进入第一次迭代校验。在每次迭代校验的开始,先将错误值均赋初值为0,然后判断判决比特是否输入完成,由于判决比特会持续产生,因此,在每当输入一组新的判决比特时,都要重新判断判决比特是否输入完成。若判断还存在新输入的判决比特,则将本次判决比特信号与上次判决比特信号进行比对,若比对结果为不同,则将错误值赋值为1,若比对结果为相同,则错误值保持不变为0。当所有的判决比特均输入完成,且完成了比对时,进入错误值和迭代次数的判断。若错误值为0或者已达到最大迭代次数,都将译码结果输出,否则迭代次数加1,等待下一轮校验。其中,本发明的优选最大迭代次数为15。

[0283]

最大迭代次数是影响ldpc译码器性能的一个关键参数,一般来说迭代次数越大,译码性能越好,但译码延时也会加大。因此为了兼顾译码性能和译码延时需要选择合适的最大迭代次数。

[0284]

图24给出了不同的最大迭代次数对应的译码性能曲线,一共包括最大迭代次数为10、15和20三种。图中横轴为比特信噪比eb/n0,纵轴为误比特率(也称为误码率)。

[0285]

当比特信噪比eb/n0取值小于3.5时,三条曲线基本重合,也就是说,当比特信噪比eb/n0《3.5时,这三条曲线的误比特率随比特信噪比eb/n0的增加而下降的幅度是一致的。

[0286]

当比特信噪比eb/n0》3.5时,这三条曲线的误比特率随比特信噪比eb/n0的增加而下降的幅度是不同的。可以看出,此时在任何一个比特信噪比值(例如比特信噪比eb/n0=3.8时),随着最大迭代次数的提高,误比特率逐渐递减,即:

[0287]

20的误比特率《15的误比特率《10的误比特率。

[0288]

进一步地,当比特信噪比eb/n0》3.5时,随着比特信噪比eb/n0的增加,最大迭代次数为15相对于最大迭代次数为10的误比特率下降幅度较大,而最大迭代次数为20相对于最大迭代次数为15的误比特率下降幅度较小,从而说明最大迭代次数从10变为15时译码性能提升较为显著,而最大迭代次数从15变为20时译码性能提升相对较小。因此在保证译码性能的情况下,为获得较高的译码速率(较低的译码延时),本文选择最大迭代次数为15次。

[0289]

以上校验存储方式只需98个长度为73比特的寄存器,参与对比的位向量长度从8176比特降至98比特,大幅度减少了对硬件资源的消耗。更重要的是校验速率的提升,从图18可以看出,它可以在t1时刻,即本次迭代过程结束前就给出校验结果,符合高速译码器的设计需求。

[0290]

进一步地,步骤s302还包括:

[0291]

当存入一组判决比特的同时,读取上一组判决比特的比对结果并判断,当比对结果为相同时,继续进行比对;当比对结果为不同时,不再进行本次比对。

[0292]

具体地,当存入一组判决比特的同时,读取上一组判决比特的比对结果并判断,当所述比对结果为相同时,继续进行比对;当所述比对结果为不同时,不再进行本次比对。这样可以进一步地节省cpu资源,例如在第50个时钟到来时,比对结果为不同,则第51个时钟开始就不再比对,节省了后续23个时钟的对两个98比特序列的23次比对计算。

[0293]

进一步地,步骤s304还包括:

[0294]

译码结果为将迭代更新产生的判决结果进行拼接获得。实际上,译码的码字对应的就是判决结果中的判决比特。

[0295]

另一方面,如图22所示,本发明提供一种适用于ldpc译码器的校验装置201,包括:接收单元2011、存储单元2012、比对单元2013、控制单元2014;

[0296]

接收单元2011接收ldpc译码器中迭代更新产生的判决结果并存入存储单元2012;

[0297]

存储单元2012将不同时刻产生的判决结果中的判决比特,按照由低到高的顺序存入寄存器,每次存入新的比特时,将寄存器左移一位,从而循环利用寄存器;

[0298]

控制单元2014进行判断,确定何时启动比对和停止比对,以及是否输出ldpc译码器中迭代更新产生的译码结果;

[0299]

比对单元2013接收控制单元2014的指令,读取存储单元2012的判决比特进行比对校验。

[0300]

再一方面,本发明提供一种ldpc译码器,包括如上的适用于ldpc译码器的校验装置201。

[0301]

以上仅为本发明的实施例,并非因此限制本发明的专利范围,凡是利用本发明说明书及附图内容所作的等效结构变换,或直接或间接运用在其他相关的技术领域,均包括在本发明的专利保护范围内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。