1.本发明涉及示波器技术领域,特别涉及一种用于高分辨率示波器的眼图生成系统及方法。

背景技术:

2.随着技术的进步,示波器的有效位数(即分辨率)也越来越高,对于高分辨率示波器,串行总线信号的内嵌时钟恢复、眼图分析、抖动分析完全可以实现,这也是高端示波器的一项必不可少的功能。可以为用户提供串行总线信号眼图和抖动分析的手段,不必购买专门的仪器,一台示波器就能搞定。

3.眼图是用余晖方式积累叠加显示采集到的串行信号的比特位的结果,叠加后的图形很像一个眼睛,故名眼图。随着串行数据速率的不断提升,眼图测试是必不可少的一个测试项,已成为衡量高速信号质量的最常用方法。

4.眼图生成方法一般分为传统眼图生成方法(tep)和实时眼图生成方法(rte)。传统眼图生成方法是利用示波器的触发功能和荧光功能,不断地同步触发和叠加显示。该方法不仅会引入示波器的触发抖动,而且效率低,测量100万个ui需要出触发100万次。随着技术的进步,传统眼图生成方法一般不再使用。实时眼图生成方法目前主要是基于硬件时钟恢复方法的眼图和抖动分析。

5.基于硬件时钟和数据恢复(cdr)电路需要外部的时钟信号,这些额外的电子器件增加了系统的噪声或者抖动,进而造成了眼图分析准确性降低。基于硬件时钟恢复实现的眼图的同步切割还会引入抖动,对于高速串行信号来说,这种抖动已经大到无法忽略。而且,硬件时钟和数据恢复(cdr)电路只能侦测连续串行信号才能正常工作,如果被测信号不是连续的,譬如两段连续比特位之间有一段低电平,硬件cdr就不能恢复出正确的时钟。因此,基于硬件时钟和数据恢复(cdr)的眼图分析还存在间歇大的问题。最后,基于硬件时钟和数据恢复(cdr)的眼图分析基于物理层信号的,无法对示波器采样的历史数据进行分析,存在应用局限性。

技术实现要素:

6.为解决上述技术问题,本发明提供了一种用于高分辨率示波器的眼图生成系统及方法,基于软件锁相环进行时钟恢复,并在恢复的时钟基础上实现了眼图的精确切割和叠加,进而进行频度计算和眼图荧光图像生成,该方法具有眼图生成效率高、零触发抖动、时钟恢复的抖动为零、离线分析和能实现跟踪定位的优点。

7.为达到上述目的,本发明的技术方案如下:

8.一种用于高分辨率示波器的眼图生成系统,包括如下组成部分:

9.数据采样模块:用于实现高分辨率示波器的串行总线信号的采集和模数转换以及存储;

10.位速率计算模块:用于计算串行总线信号的位速率;

11.实数倍插值模块:用于对采集的串行总线信号进行实数倍插值,得到实数倍变采样数据;

12.软件锁相环时钟恢复与数据重采样模块:用于对实数倍变采样数据进行软件锁相环时钟恢复与数据重采样,得到重采样波形数据;

13.锁相环锁定判断模块:用于判断锁相环是否处于锁定状态;

14.重采样波形数据叠加模块:当锁相环锁定后,重采样波形数据叠加模块用于对重采样波形数据按照设置的眼图ui个数进行叠加;

15.波形数据统计与频度计算模块:用于根据叠加的波形数据计算波形的最大频度值和波形灰度值;

16.荧光图像生成模块:用于根据计算的灰度值计算出像素点颜色值,并生成荧光图像。

17.上述方案中,所述软件锁相环时钟恢复与数据重采样模块包括插值模块、鉴相器、环路滤波器和插值控制模块。

18.上述方案中,所述鉴相器采用多重采样的bang-bang鉴相器,所述插值模块的插值器采用farrow结构的多项式插值滤波器,所述环路滤波器采用低通滤波器,所述插值控制模块采用mod-1计数的插值控制器。

19.一种用于高分辨率示波器的眼图生成方法,采用如上所述的一种用于高分辨率示波器的眼图生成系统,包括如下步骤:

20.步骤一,数据采样模块通过高分辨率adc对高分辨率示波器的串行总线信号进行采集,并进行模数转换后存储在内存条中;

21.步骤二,位速率计算模块对串行总线信号计算位速率;

22.步骤三,实数倍插值模块对采集的串行总线信号进行实数倍插值,得到实数倍变采样数据;

23.步骤四,软件锁相环时钟恢复与数据重采样模块对实数倍变采样数据进行软件锁相环时钟恢复与数据重采样,得到重采样波形数据;

24.步骤五,锁相环锁定判断模块对锁相环状态进行判断,当锁相环处于锁定状态后,进行步骤六,当锁相环处于失锁状态时,返回步骤四;

25.步骤六,重采样波形数据叠加模块用于对重采样波形数据按照设置的眼图ui个数进行叠加;

26.步骤七,波形数据统计与频度计算模块根据叠加的波形数据计算波形的最大频度值和波形灰度值;

27.步骤八,荧光图像生成模块根据计算的灰度值计算出像素点颜色值,并生成荧光图像。

28.进一步的技术方案中,所述步骤二中,位速率计算模块接受位速率获取方式设置,如果位速率获取方式设置为固定值,则无需再计算;如果位速率获取方式设置为自动,则需要对采集数据做直方图统计,找到最多点数的最大电平和最多点数的最小电平,最大电平和最小电平的均值为串行总线信号的中间电平值,然后根据中间电平值计算出采集数据的最小脉冲值,该值则认为是该串行总线信号的位速率。

29.进一步的技术方案中,所述步骤三中,假设串行总线信号的每一个比特位在眼图

显示时需要n个采样点,示波器的采样率为s,串行总线信号的位速率为r,如果n*r》s,则需要进行l=n*r/s倍的插值,如果n*r《s,则需要进行l=s/n*r倍的抽取;插值和抽取算法采用公式(1)的正弦插值方法;

[0030][0031]

式中,x(t)表示插值或抽取后的采样值,xn表示第n个采样周期的原采样值,sa为sinc函数,f

s1

表示原采样值的角速度,t

s1

表示原采样值的周期,n表示第n个采样周期。

[0032]

进一步的技术方案中,所述步骤四中,软件锁相环时钟恢复与数据重采样在一个流程中实现,所述鉴相器通过计算插值模块的重采样数据获取相位误差,经过环路滤波器后送入插值控制模块,所述插值控制模块产生插值控制因子送入插值模块,插值模块根据插值控制因子对实数倍变采样数据进行重采样,产生重采样数据。

[0033]

进一步的技术方案中,所述鉴相器首先对实数倍变采样数据进行符号位判断,大于中间电平为1,小于中间电平为-1,通过公式(2)获取相位误差:

[0034][0035]

式中,e表示相位误差,a1表示第1个符号位的值,a

l

表示第l个符号位的值,a

2l 1

表示第2l 1个符号位的值,l表示第l符号位,l表示插值的倍数。

[0036]

进一步的技术方案中,所述步骤五中,锁相环锁定判断模块通过滑动方式计算一定长度的鉴相器计算的相位误差的均值和均值的方差,当均值的方差小于设定值时,认为锁相环处于锁定状态,当均值的方差大于设定值时认为锁相环处于失锁状态。

[0037]

进一步的技术方案中,所述步骤七中,波形灰度值的计算方法如公式(3)所示:

[0038][0039]

式中,p代表频度值,p

max

代表最大频度值。

[0040]

通过上述技术方案,本发明提供的一种用于高分辨率示波器的眼图生成系统及方法具有如下有益效果:

[0041]

本发明基于软件锁相环(pll)进行时钟恢复,并在恢复的时钟基础上实现了眼图的精确切割和叠加,进而进行频度计算和眼图荧光图像生成。通过软件锁相环(pll)恢复的时钟是对高分辨率示波器的采样数据进行计算得到的,没有硬件电路引入的抖动或者噪声,没有时钟和数据恢复(cdr)电路的触发抖动,即触发抖动为零。软件锁相环(pll)的时钟恢复方法在采样数据连续无变化时也能正常输出时钟,也能实现波形叠加,死区时间短。该方法既能实时分析高分辨率示波器的串行总线采样数据,也能基于历史采集数据做离线分析。

[0042]

因此,本发明的方法采用使用软件锁相环输出时钟同步切割和叠加显示的方式,该方法具有眼图生成效率高、零触发抖动、时钟恢复的抖动为零、离线分析和能实现跟踪定位的优点。

附图说明

[0043]

为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍。

[0044]

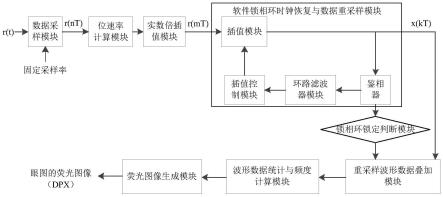

图1为本发明实施例所公开的一种用于高分辨率示波器的眼图生成方法流程示意图;

[0045]

图2为本发明实施例所公开的软件锁相环时钟恢复与数据重采样模块示意图;

[0046]

图3为本发明实施例所公开的一种用于高分辨率示波器的眼图生成系统示意图。

具体实施方式

[0047]

下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述。

[0048]

本发明提供了一种用于高分辨率示波器的眼图生成系统,如图3所示,包括如下组成部分:

[0049]

数据采样模块:用于实现高分辨率示波器的串行总线信号的采集和模数转换以及存储;

[0050]

位速率计算模块:用于计算串行总线信号的位速率;

[0051]

实数倍插值模块:用于对采集的串行总线信号进行实数倍插值,得到实数倍变采样数据;

[0052]

软件锁相环时钟恢复与数据重采样模块:用于对实数倍变采样数据进行软件锁相环时钟恢复与数据重采样,得到重采样波形数据;

[0053]

锁相环锁定判断模块:用于判断锁相环是否处于锁定状态;

[0054]

重采样波形数据叠加模块:当锁相环锁定后,重采样波形数据叠加模块用于对重采样波形数据按照设置的眼图ui个数进行叠加;

[0055]

波形数据统计与频度计算模块:用于根据叠加的波形数据计算波形的最大频度值和波形灰度值;

[0056]

荧光图像生成模块:用于根据计算的灰度值计算出像素点颜色值,并生成荧光图像。

[0057]

本实施例中,软件锁相环时钟恢复与数据重采样模块包括插值模块、鉴相器、环路滤波器和插值控制模块。鉴相器采用多重采样的bang-bang鉴相器,插值模块的插值器采用farrow结构的多项式插值滤波器,环路滤波器采用低通滤波器,插值控制模块采用mod-1计数的插值控制器。

[0058]

一种用于高分辨率示波器的眼图生成方法,如图1所示,采用如上的一种用于高分辨率示波器的眼图生成系统,包括如下步骤:

[0059]

步骤一,数据采样模块通过高分辨率adc对高分辨率示波器的串行总线信号进行采集,并进行模数转换后存储在内存条中;

[0060]

步骤二,位速率计算模块对串行总线信号计算位速率;

[0061]

位速率计算模块接受位速率获取方式设置,如果位速率获取方式设置为固定值,则无需再计算;如果位速率获取方式设置为自动,则需要对采集数据做直方图统计,找到最多点数的最大电平和最多点数的最小电平,最大电平和最小电平的均值为串行总线信号的

中间电平值,然后根据中间电平值计算出采集数据的最小脉冲值,该值则认为是该串行总线信号的位速率。

[0062]

步骤三,实数倍插值模块对采集的串行总线信号进行实数倍插值,得到实数倍变采样数据;

[0063]

由于根据步骤二计算得到的位速率和高分辨率示波器的采样率不一定成整数倍关系,需要对采集数据实数倍插值。假设串行总线信号的每一个比特位在眼图显示时需要n个采样点,示波器的采样率为s,串行总线信号的位速率为r,如果n*r》s,则需要进行l=n*r/s倍的插值,如果n*r《s,则需要进行l=s/n*r倍的抽取;插值和抽取算法采用公式(1)的正弦插值方法;

[0064][0065]

式中,x(t)表示插值或抽取后的采样值,xn表示第n个采样周期的原采样值,sa为sinc函数,f

s1

表示原采样值的角速度,t

s1

表示原采样值的周期,n表示第n个采样周期。

[0066]

步骤四,软件锁相环时钟恢复与数据重采样模块对实数倍变采样数据进行软件锁相环时钟恢复与数据重采样,得到重采样波形数据;

[0067]

如图2所示,软件锁相环时钟恢复与数据重采样在一个流程中实现,鉴相器通过计算插值模块的重采样数据获取相位误差,经过环路滤波器后送入插值控制模块,插值控制模块产生插值控制因子送入插值模块,插值模块根据插值控制因子对实数倍变采样数据进行重采样,产生重采样数据。插值控制模块产生插值控制因子的过程即进行了时钟恢复,不需要外接时钟。

[0068]

鉴相器首先对实数倍变采样数据进行符号位判断,大于中间电平为1,小于中间电平为-1,通过公式(2)获取相位误差:

[0069][0070]

式中,e表示相位误差,a1表示第1个符号位的值,a

l

表示第l个符号位的值,a

2l 1

表示第2l 1个符号位的值,l表示第l符号位,l表示插值的倍数。

[0071]

步骤五,锁相环锁定判断模块对锁相环状态进行判断,当锁相环处于锁定状态后,进行步骤六,当锁相环处于失锁状态时,返回步骤四;

[0072]

锁相环锁定判断模块通过滑动方式计算一定长度的鉴相器计算的相位误差的均值和均值的方差,当均值的方差小于设定值时,认为锁相环处于锁定状态,当均值的方差大于设定值时认为锁相环处于失锁状态。

[0073]

步骤六,重采样波形数据叠加模块用于对重采样波形数据按照设置的眼图ui个数进行叠加;

[0074]

步骤七,波形数据统计与频度计算模块根据叠加的波形数据计算波形的最大频度值和波形灰度值;

[0075]

波形灰度值的计算方法如公式(3)所示:

[0076][0077]

式中,p代表频度值,p

max

代表最大频度值。

[0078]

步骤八,荧光图像生成模块根据计算的灰度值计算出像素点颜色值,并生成荧光图像。

[0079]

经过图2和图3所示的流程后便得到了眼图的荧光图像,用户通过该图像还可以统计出眼图的一些参数,可以观察图像的亮暗判定串行总线的物理层信号的轨迹等。

[0080]

对所公开的实施例的上述说明,使本领域专业技术人员能够实现或使用本发明。对这些实施例的多种修改对本领域的专业技术人员来说将是显而易见的,本文中所定义的一般原理可以在不脱离本发明的精神或范围的情况下,在其它实施例中实现。因此,本发明将不会被限制于本文所示的这些实施例,而是要符合与本文所公开的原理和新颖特点相一致的最宽的范围。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。