1.本发明涉及半导体膜及其制造方法。

背景技术:

2.以往,已知通过hvpe(halide vapor phase epitaxy:卤化物气相外延)法来生长β-ga2o3系单晶膜的技术(例如,参照专利文献1)。根据专利文献1所记载的技术,是向气相生长装置的反应腔内的设置有ga2o3系基板的区域流入镓的原料气体、氧的原料气体以及掺杂物的原料气体,在ga2o3系基板上使β-ga2o3系单晶膜外延生长。

3.现有技术文献

4.专利文献

5.专利文献1:日本专利第5984069号公报

技术实现要素:

6.发明要解决的问题

7.然而,在通过hvpe法来生长β-ga2o3系单晶膜的情况下,与通过hvpe法来生长gan等其它氮化物半导体的单晶膜的情况相比,存在容易产生致使器件特性显著下降的严重缺陷即致命缺陷的问题,以往,尚不明确致命缺陷的原因及其减少方法。

8.因此,本发明的目的在于,提供一种致命缺陷少的包括β-ga2o3系单晶的半导体膜及其制造方法。

9.用于解决问题的方案

10.为了达到上述目的,本发明的一个方面提供下述[1]~[4]的半导体膜的制造方法、下述[5]的半导体膜。

[0011]

[1]一种半导体膜的制造方法,包含:将包括β-ga2o3系单晶的半导体基板以生长基底面朝向上方或下方的方式设置到hvpe装置的反应腔内的工序;以及向所述反应腔内的设置有所述半导体基板的空间流入ga氯化物气体、含氧气体以及含掺杂物气体,在所述半导体基板的生长基底面上使包括β-ga2o3系单晶的半导体膜外延生长的工序,在所述半导体基板以所述生长基底面朝向上方的方式设置的情况下,使所述含掺杂物气体向所述空间的流入口的位置高于所述含氧气体向所述空间的流入口的位置,并且使所述ga氯化物气体向所述空间的流入口的位置高于所述含掺杂物气体向所述空间的流入口的位置,在所述半导体基板以所述生长基底面朝向下方的方式设置的情况下,使所述含掺杂物气体向所述空间的流入口的位置高于所述ga氯化物气体向所述空间的流入口的位置,并且使所述含氧气体向所述空间的流入口的位置高于所述含掺杂物气体向所述空间的流入口的位置。

[0012]

[2]根据上述[1]所述的半导体膜的制造方法,其中,所述ga氯化物气体为gacl气体,所述含氧气体为o2气体,所述含掺杂物气体为sicl4气体。

[0013]

[3]根据上述[1]或[2]所述的半导体膜的制造方法,其中,在设置所述半导体基板的工序中,将所述半导体基板以所述生长基底面朝向下方的方式设置到所述反应腔内。

[0014]

[4]根据上述[3]所述的半导体膜的制造方法,其中,在使所述半导体膜外延生长的工序中,使所述ga氯化物气体、所述含氧气体以及所述含掺杂物气体以110cm/s以上的流速流入所述空间。

[0015]

[5]一种半导体膜,包括含有cl的β-ga2o3系单晶,在厚度方向上从正面连续至背面的缺陷的面内密度为10个/cm2以下。

[0016]

发明效果

[0017]

根据本发明,能够提供一种致命缺陷少的包括β-ga2o3系单晶的半导体膜及其制造方法。

附图说明

[0018]

图1是本发明的第1实施方式的晶体层叠结构体的垂直截面图。

[0019]

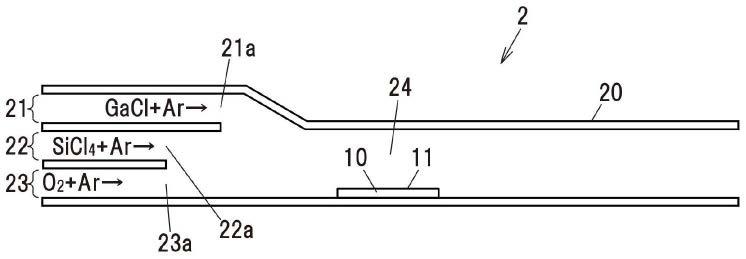

图2a是示出本发明的第1实施方式的半导体基板10的设置状态与原料气体的导入位置的示意图。

[0020]

图2b是示出比较例的半导体基板10的设置状态与原料气体的导入位置的示意图。

[0021]

图3是示出本发明的第2实施方式的半导体基板10的设置状态与原料气体的导入位置的示意图。

[0022]

图4a是通过第2实施方式的方法形成的半导体膜的发射显微镜观察像。

[0023]

图4b是通过以往的方法形成的作为比较例的半导体膜的发射显微镜观察像。

[0024]

图5a是通过第2实施方式的方法形成的半导体膜的出现了蚀刻坑的表面的光学显微镜观察像。

[0025]

图5b是通过以往的方法形成的作为比较例的半导体膜的出现了蚀刻坑的表面的光学显微镜观察像。

[0026]

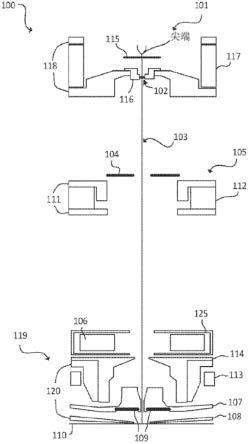

图6是为了进行后述的肖特基势垒二极管的特性的评价而使用的肖特基势垒二极管的垂直截面图。

[0027]

图7a是示出具备通过第1实施方式的方法形成的半导体膜的肖特基势垒二极管的反向泄漏特性的坐标图。

[0028]

图7b是示出具备通过第2实施方式的方法形成的半导体膜的肖特基势垒二极管的反向泄漏特性的坐标图。

[0029]

图8是示出具备通过以往的方法形成的作为比较例的半导体膜的肖特基势垒二极管的反向泄漏特性的坐标图。

[0030]

图9a是示出将具备通过第2实施方式的方法形成的半导体膜的肖特基势垒二极管单片化之前的2英寸的晶片中的、肖特基势垒二极管的耐压特性的分布的图。

[0031]

图9b是示出将具备通过第2实施方式的方法形成的半导体膜的肖特基势垒二极管单片化之前的2英寸的晶片中的、肖特基势垒二极管的耐压特性的分布的图。

[0032]

图9c是示出将具备通过第2实施方式的方法形成的半导体膜的肖特基势垒二极管单片化之前的2英寸的晶片中的、肖特基势垒二极管的耐压特性的分布的图。

[0033]

图10a是示出具备通过第2实施方式的方法形成的半导体膜和2.3mm见方的正方形的阳极电极的肖特基势垒二极管的反向特性的坐标图。

[0034]

图10b是示出具备通过第2实施方式的方法形成的半导体膜和2.3mm见方的正方形

film fed growth:限边馈膜生长)法等熔体生长法培育出的ga2o3系单晶的块状晶体切片,并对表面进行研磨来形成。

[0047]

半导体膜12含有与晶体生长并行地掺杂的li、na、k、rb、cs、be、mg、ca、sr、ba、sc、y、ti、zr、hf、v、nb、ta、cr、mo、w、mn、re、fe、ru、os、co、rh、ir、ni、pd、pt、cu、ag、au、zn、cd、hg、b、al、in、tl、c、si、ge、sn、pb、n、p、as、sb、bi、s、se、te等作为掺杂物。

[0048]

半导体膜12所含的掺杂物的浓度例如为1

×

10

13

atoms/cm3以上、5

×

10

20

atoms/cm3以下,优选为6.5

×

10

15

atoms/cm3以上、2.1

×

10

20

atoms/cm3以下。另外,通过掺杂物的添加而产生的载流子密度例如为1

×

10

15

cm-3

以上、1

×

10

20

cm-3

以下。

[0049]

另外,半导体膜12含有浓度为5

×

10

16

atoms/cm3以下的cl。这是因为,半导体膜12是通过使用含cl气体的hvpe法来形成。通常,在通过hvpe法以外的方法形成β-ga2o3系单晶膜的情况下,由于不使用含cl气体,因此,β-ga2o3系单晶膜中不会含有cl,至少不会含有1

×

10

16

cm-3

以上的cl。

[0050]

另外,半导体膜12由于是通过晶体生长速度快的hvpe(halide vapor phase epitaxy:卤化物气相外延)法来形成,因此能够形成得厚,例如能够形成为1000nm以上的厚度。另外,利用工业用hvpe的β-ga2o3系单晶膜的生长速度一般为200μm/h,在该情况下,如果是至1000μm为止的厚度,则能够在现实的时间内成膜。即,能够形成厚度为1000nm以上、1000μm以下的半导体膜12。此外,使用mbe法的情况下的β-ga2o3系单晶膜的晶体生长速度为120nm/h左右,为了形成1000nm以上的厚度而需要8小时以上的时间,因此,在生产现场是不现实的。

[0051]

另外,根据后述的半导体膜12的制造方法,能够使在半导体膜12的厚度方向上从正面连续至背面的致命缺陷的面内密度为10个/cm2以下。半导体膜12所含的致命缺陷的面内密度能够通过在阳极偏压为-200v的条件下利用发射显微镜实施观察来进行测定。

[0052]

(hvpe装置的结构)

[0053]

以下,对本发明的第1实施方式的半导体膜12的生长所使用的hvpe装置的结构的一个例子进行说明。

[0054]

本发明的第1实施方式的半导体膜的制造方法使用在图2a、图2b中示出了垂直截面的hvpe装置2。hvpe装置2是hvpe法用的气相生长装置,具有:空间24,其中设置半导体基板10;以及反应腔20,其具有用于向空间24导入为使半导体膜12生长的原料气体的第1气体导入端口21、第2气体导入端口22、第3气体导入端口23。反应腔20例如包括石英玻璃。

[0055]

另外,hvpe装置2具有未图示的加热单元,该加热单元设置在反应腔20的周围,用于对反应腔20内的空间24进行加热。该加热单元例如是电阻加热式或辐射加热式的加热装置。

[0056]

在反应腔20中,用于使半导体膜12生长的原料气体从第1气体导入端口21、第2气体导入端口22、第3气体导入端口23向空间24内导入。

[0057]

第1气体导入端口21向空间24的流入口21a、第2气体导入端口22向空间24的流入口22a以及第3气体导入端口23向空间24的流入口23a的高度(与所设置的半导体基板10的生长基底面11垂直的方向上的位置)不同,在流入口23a的上方配置有流入口22a,在流入口22a的上方配置有流入口21a。另外,为了防止生长基底面11的面内方向的半导体膜12的状态的偏差,流入口21a、22a、23a的与原料气体的行进方向正交的水平方向上的位置(图2a、

图2b的与纸面垂直的方向上的位置)大致相同。

[0058]

用于使半导体膜12生长的原料气体包含:镓的原料气体,其是gacl气体、gacl2气体、gacl3气体、(gacl3)2气体等ga氯化物气体;氧的原料气体,其是o2气体、h2o气体等含氧气体;以及掺杂物的原料气体,其是sicl4气体、gecl4气体、sncl4气体、pbcl2气体等含掺杂物气体。

[0059]

每种原料气体使用ar气体、n2气体等惰性气体作为载气而流入反应腔20内。

[0060]

(半导体膜的制造方法)

[0061]

本发明的第1实施方式的半导体膜12的制造方法包含:将包括β-ga2o3系单晶的半导体基板10设置到hvpe装置2的反应腔20内的工序;以及向反应腔20内的设置有半导体基板10的空间24流入ga氯化物气体、含氧气体以及含掺杂物气体,在半导体基板10的生长基底面11上使包括β-ga2o3系单晶的半导体膜12外延生长的工序。

[0062]

在本实施方式中,半导体基板10以生长基底面11朝向上方的方式设置到反应腔20内的空间24的底表面侧。在此,生长基底面11朝向上方是指:生长基底面11朝向地表的相反侧,生长基底面11与水平面所成的角度处于-5~ 5

°

的范围的状态。

[0063]

从流入口21a、22a、23a流入的ga氯化物气体、含氧气体以及含掺杂物气体在空间24中混合。然后,半导体基板10的生长基底面11暴露在该混合气体中,半导体膜12进行外延生长。

[0064]

在使半导体膜12外延生长的工序中,将空间24内的压力例如保持为1atm。另外,为了使半导体膜12生长,要求生长温度在900℃以上。在低于900℃的情况下,有可能得不到单晶。

[0065]

在此,作为镓的原料气体的ga氯化物气体优选使用gacl气体。gacl气体是ga氯化物气体之中能够将ga2o3晶体的生长驱动力保持至最高温度的气体。为了得到高纯度、高质量的ga2o3晶体,以高的生长温度进行生长是有效的,因此,优选使用在高温中生长驱动力高的gacl气体。

[0066]

另外,作为掺杂物的原料气体的含掺杂物气体,为了抑制无意中混入其它杂质而优选使用氯化物系气体,例如在如前述的掺杂物中,将作为14族元素的si、ge、sn或pb设为掺杂物的情况下,分别使用sicl4、gecl4、sncl4、pbcl2等氯化物系气体。另外,氯化物系气体不限于仅与氯的化合物,例如也可以使用sihcl3等硅烷系气体。

[0067]

si等掺杂物是与β-ga2o3系单晶的生长并行地掺杂的。

[0068]

另外,如果在使半导体膜12生长时的气氛中含有氢,则半导体膜12的表面的平坦性和晶体生长驱动力会下降,因此,作为氧的原料气体的含氧气体优选使用不含氢的o2气体。

[0069]

本发明的第1实施方式的半导体膜12的制造方法在hvpe装置2的反应腔20内的、镓的原料气体、氧的原料气体、掺杂物的原料气体各自的导入口与半导体基板10的位置关系上具有特征。

[0070]

图2a是示出本发明的第1实施方式的半导体基板10的设置状态与原料气体的导入位置的示意图。图2b是示出比较例的半导体基板10的设置状态与原料气体的导入位置的示意图。

[0071]

在本发明的第1实施方式中,如图2a所示,使ga氯化物气体和载气(作为例子,标示

为gacl气体和ar气体)从第1气体导入端口21流入,使含掺杂物气体和载气(作为例子,标示为sicl4气体和ar气体)从第2气体导入端口22流入,使含氧气体和载气(作为例子,标示为o2气体和ar气体)从第3气体导入端口23流入。

[0072]

另一方面,在图2b所示的比较例中,与基于以往的hvpe法的β-ga2o3系单晶的生长方法同样,使含氧气体和载气(作为例子,标示为o2气体和ar气体)从第1气体导入端口21流入,使含掺杂物气体和载气(作为例子,标示为sicl4气体和ar气体)从第2气体导入端口22流入,使ga氯化物气体和载气(作为例子,标示为gacl气体和ar气体)从第3气体导入端口23流入。

[0073]

本发明的发明人们进行了锐意研究,结果发现通过将原料气体的导入位置设定为图2a所示的位置,与设定为图2b所示的位置的情况相比,生长的半导体膜12所含的致命缺陷的数量减少。认为这是由于:通过使含氧气体最容易到达生长基底面11,使ga氯化物气体最难以到达生长基底面11,从而出于某些原因,在气相中生成并附着到生长基底面11的ga氧化物的颗粒的量减少。

[0074]

即,在半导体基板10以生长基底面11朝向上方的方式设置的情况下,通过使含掺杂物气体向空间24的流入口的位置高于含氧气体向空间24的流入口的位置,并且使ga氯化物气体向空间24的流入口的位置高于含掺杂物气体向空间24的流入口的位置,生长的半导体膜12所含的致命缺陷的数量减少。

[0075]

〔第2实施方式〕

[0076]

本发明的第2实施方式在设置到hvpe装置2的反应腔20内的半导体基板10的朝向上与第1实施方式不同。此外,对于与第1实施方式相同之处,有时省略或简化说明。

[0077]

(半导体膜的制造方法)

[0078]

在本发明的第2实施方式的半导体膜12的制造方法中,半导体基板10以生长基底面11朝向下方的方式设置到反应腔20内的空间24的上表面侧。在此,生长基底面11朝向下方是指:生长基底面11朝向地表侧,生长基底面11与水平面所成的角度处于-5~ 5

°

的范围的状态。

[0079]

图3是示出本发明的第2实施方式的半导体基板10的设置状态与原料气体的导入位置的示意图。

[0080]

在本发明的第2实施方式中,如图3所示,半导体基板10是以生长基底面11朝向下方的方式设置的,因此,使含氧气体和载气(作为例子,标示为o2气体和ar气体)从第1气体导入端口21流入,使含掺杂物气体和载气(作为例子,标示为sicl4气体和ar气体)从第2气体导入端口22流入,使ga氯化物气体和载气(作为例子,标示为gacl气体和ar气体)从第3气体导入端口23流入。

[0081]

即,使含掺杂物气体向空间24的流入口的位置高于ga氯化物气体向空间24的流入口的位置,并且使含氧气体向空间24的流入口的位置高于含掺杂物气体向空间24的流入口的位置。由此,含氧气体最容易到达生长基底面11,ga氯化物气体最难以到达生长基底面11,生长的半导体膜12所含的致命缺陷的数量减少。

[0082]

而且,在气相中生成的ga氧化物的颗粒会由于重力而向下方移动,因此,通过以生长基底面11朝向下方的方式设置半导体基板10,ga氧化物的颗粒更难以附着于生长基底面11。所以,根据本实施方式的半导体膜的制造方法,与第1实施方式的半导体膜的制造方法

相比,能够进一步减少半导体膜12所含的致命缺陷的数量。

[0083]

此外,如上所述,在通过hvpe法来生长gan系晶体膜的情况下,氨气与ga氯化物气体的反应速度比较慢,因此几乎不会在气相中发生gan系化合物的颗粒的生成。所以,在生长gan系晶体膜的情况下,不会如生长β-ga2o3系晶体膜的情况那样产生许多的致命缺陷,另外,基本上没有由使基板的生长基底面朝向下方带来的减少致命缺陷的效果。虽然通过hvpe法在使基板的生长基底面朝向下方的状态下生长gan系晶体膜的技术是已知的(日本专利第3376809号公报),但其目的是抑制在基板附近发生原料气体的热对流来生长均匀的薄膜。

[0084]

另外已经确认,在以生长基底面11朝向下方的方式设置半导体基板10的情况下,与以生长基底面11朝向上方的方式设置半导体基板10的情况相比,掺杂物的取入率高。通过以生长基底面11朝向下方的方式设置半导体基板10,半导体膜12中的施主浓度变得与掺杂物的加入量大致相等,因此,施主浓度的控制变得容易。

[0085]

另外,通过使ga氯化物气体、含氧气体以及含掺杂物气体的流速增加,容易利用这些原料气体将在气相中生成的ga氧化物的颗粒冲走,因此,能够减少ga氧化物的颗粒向生长基底面11的附着量。

[0086]

例如,在直径为2英寸的圆形的半导体基板10上生长半导体膜12的情况下,通过使ga氯化物气体、含氧气体以及含掺杂物气体以110cm/s以上的流速流入空间24,能够显著地减少半导体膜12所含的致命缺陷的数量,通过使ga氯化物气体、含氧气体以及含掺杂物气体以165cm/s以上的流速流入空间24,能够进一步减少半导体膜12所含的致命缺陷的数量。

[0087]

(实施方式的效果)

[0088]

根据上述实施方式,能够减少在hvpe装置的反应腔内在气相中形成并附着到半导体基板10上的ga氧化物的颗粒的量,减少包括β-ga2o3系单晶的半导体膜12的致命缺陷。通过使用该致命缺陷少的半导体膜12,能够以高成品率制造具有优异特性的半导体器件、例如正向电流特性或反向漏电流特性优异的肖特基势垒二极管。

[0089]

实施例

[0090]

图4a是通过图3中说明的第2实施方式的方法形成的半导体膜12的发射显微镜观察像。图4b是通过图2b中说明的以往的方法形成的作为比较例的半导体膜的发射显微镜观察像。

[0091]

图4a、图4b的发射显微镜观察像是在半导体膜12的表面与半导体基板10的表面都以互不重叠的方式形成阳极电极与阴极电极,通过ccd相机从半导体基板10侧对形成有阳极电极的区域进行拍摄而成的,是将在未对两个电极之间施加电压的状态下照射光而拍摄到的直径为500μm的圆形的阳极电极的图案像与在对两个电极之间施加了200v的反向电压(阴极电极侧为正且阳极电极侧为负的电压)的状态下拍摄到的发光像叠加而成的。

[0092]

图4b的圆中可见的黑点是通过施加反向电压而发出了光的泄漏路径,表示出成为泄漏路径的致命缺陷的位置。在图4a的发射显微镜观察像中,观察不到如图4b的发射显微镜观察像那么醒目的发光点,使用多个阳极电极对发光点的密度进行了推定,结果为10个/cm2以下。即,第2实施方式的半导体膜12的致命缺陷的密度为10个/cm2以下。

[0093]

图5a是通过图3中说明的第2实施方式的方法形成的半导体膜12的出现了蚀刻坑的表面的光学显微镜的观察像。图5b是通过图2b中说明的以往的方法形成的作为比较例的

半导体膜的出现了蚀刻坑的表面的光学显微镜的观察像。

[0094]

蚀刻坑是在对晶体表面实施了蚀刻时由于缺陷部分与其它部分的蚀刻速度之差而产生的凹陷,通过观察蚀刻坑,能够获知缺陷的位置、密度。图5a、图5b的蚀刻坑是通过将在半导体基板10上生长的半导体膜12在热磷酸中浸泡1小时而形成的。

[0095]

根据图5b的观察像,比较例的半导体膜的蚀刻坑密度为大约10000/cm2。另一方面,根据图5a的观察像,半导体膜12的蚀刻坑密度为大约2500/cm2,与比较例的半导体膜的蚀刻坑密度相比较,大约为1/4。

[0096]

图6是为了进行后述的肖特基势垒二极管的特性的评价而使用的肖特基势垒二极管3的垂直截面图。

[0097]

肖特基势垒二极管3具备:半导体基板10,其包括β-ga2o3单晶,有效载流子浓度(从施主浓度nd减去受主浓度na所得的值)为大约1

×

10

18

/cm3,厚度为大约600μm;半导体膜12,其包括β-ga2o3单晶,有效载流子浓度为大约1

×

10

16

/cm3,厚度为大约6μm;阳极电极31,其形成于半导体膜12的表面,具有ni/au层叠结构;以及阴极电极32,其形成于半导体基板10的表面的整个面,具有ti/ni/au层叠结构。

[0098]

图7a是示出具备通过图2a中说明的第1实施方式的方法形成的半导体膜12的肖特基势垒二极管3的反向泄漏特性的坐标图。图7b是示出具备通过图3中说明的第2实施方式的方法形成的半导体膜12的肖特基势垒二极管3的反向泄漏特性的坐标图。图8是示出具备通过图2b中说明的以往的方法形成的作为比较例的半导体膜来取代半导体膜12的肖特基势垒二极管3的反向泄漏特性的坐标图。

[0099]

这些图7a、图7b、图8的肖特基势垒二极管3的阳极电极31是直径为500μm的圆形的电极。

[0100]

在图7a、图7b、图8中,在对阳极电极施加了-200v的电压时,若漏电流的大小为1

×

10-4

a/cm2以下,则表示为“良好”,若超过1

×

10-4

a/cm2,则表示为“低劣”。

[0101]

若将全体之中的“良好”的比例定义为成品率,则具备通过图2a中说明的第1实施方式的方法形成的半导体膜12的肖特基势垒二极管3的成品率为78%,具备通过图3中说明的第2实施方式的方法形成的半导体膜12的肖特基势垒二极管3的成品率为89%,具备通过图2b中说明的以往的方法形成的作为比较例的半导体膜的肖特基势垒二极管3的成品率为11%。

[0102]

图9a~图9c是示出将具备通过图3中说明的第2实施方式的方法形成的半导体膜12的肖特基势垒二极管3单片化之前的2英寸的晶片(形成有多个阳极电极31和阴极电极32的晶体层叠结构体1)中的、肖特基势垒二极管3的耐压特性的分布的图。

[0103]

图9a~图9c是从竖直上方观看晶片的半导体膜12的图,所记载的数值表示出该部位的肖特基势垒二极管3的耐压(流过1μa的漏电流时的电压),负的值表示是反向的电压。此外,由于耐压的测定极限是-200v,因此,图中的

“‑

200”的部位的肖特基势垒二极管3的耐压为-200v以下。能够判断为图中的

“‑

200”的部位的肖特基势垒二极管3具有充分的耐压。

[0104]

图9a的半导体膜12是使原料气体(ga氯化物气体、含氧气体以及含掺杂物气体)以55cm/s的流速流入空间24而生长出的,图9b的半导体膜12是使原料气体以110cm/s的流速流入空间24而生长出的,图9c的半导体膜12是使原料气体以165cm/s的流速流入空间24而生长出的。图中的箭头的方向表示出原料气体的流动方向。

[0105]

图9a~图9c示出:原料气体的流速越大,晶片内的能得到耐压优异的肖特基势垒二极管3的区域就越增加。可以认为这是由于以下原因所致:越增大原料气体的流速,就越容易将在气相中生成的ga氧化物的颗粒冲走,因此,ga氧化物的颗粒向生长基底面11的附着量减少了,半导体膜12的致命缺陷减少了。

[0106]

并且,根据图9a~图9c可知,在晶片的直径为2英寸的情况下,通过使原料气体以110cm/s以上的流速流入空间24,能够显著地减少半导体膜12所含的致命缺陷的数量,通过使原料气体以165cm/s以上的流速流入空间24,能够进一步减少半导体膜12所含的致命缺陷的数量。

[0107]

不过,越增加原料气体的流速,对半导体膜12的生长没有贡献而流走的原料气体的量就越增多,因此,原料气体的使用效率会下降,其结果是,半导体膜12的制造成本会增加。所以,优选将恰好能在晶片内的整个区域内得到耐压优异的肖特基势垒二极管3这样的流速设为上限值。

[0108]

另外,在将切出肖特基势垒二极管3的晶片的尺寸增大的情况下,通过进一步增加原料气体的流速,能够将能得到耐压优异的肖特基势垒二极管3的区域确保得大。例如,在形成直径为4英寸的晶片的情况下,只要将原料气体的流速设为形成直径为2英寸的晶片的情况下的2倍即可,通过使原料气体以220cm/s以上的流速流入空间24,能够显著地减少半导体膜12所含的致命缺陷的数量,通过使原料气体以330cm/s以上的流速流入空间24,能够进一步减少半导体膜12所含的致命缺陷的数量。

[0109]

图10a、图10b分别是示出具备通过图3中说明的第2实施方式的方法形成的半导体膜12和2.3mm见方的正方形的阳极电极31的肖特基势垒二极管3的反向特性和正向特性的坐标图。图10a的虚线表示测定极限。另外,图10b的正向特性是施加脉冲宽度为1ms的脉冲电压而测定出的。

[0110]

根据图10a可知,即使在施加电压为-460v时漏电流的大小也不到1μa,得到了优异的反向泄漏特性。另外,根据图10b可知,在施加电压为2.1v以上时流过了10a以上的电流,得到了优异的大电流特性。

[0111]

以上,说明了本发明的实施方式和实施例,但本发明不限于上述实施方式和实施例,在不脱离发明的主旨的范围内能进行各种变形实施。另外,在不脱离发明的主旨的范围内能够将上述实施方式和实施例的构成要素任意组合。

[0112]

另外,上面所述的实施方式和实施例并不限制权利要求书所涉及的发明。另外,应当注意,实施方式和实施例中所说明的特征的所有组合对用于解决发明的问题的方案来说并非都是必须的。

[0113]

工业上的可利用性

[0114]

提供致命缺陷少的包括β-ga2o3系单晶的半导体膜及其制造方法。

[0115]

附图标记说明

[0116]1…

晶体层叠结构体,2

…

hvpe装置,3

…

肖特基势垒二极管,10

…

半导体基板,11

…

生长基底面,12

…

半导体膜,20

…

反应腔,21

…

第1气体导入端口,22

…

第2气体导入端口,23

…

第3气体导入端口,24

…

空间,31

…

阳极电极,32

…

阴极电极。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。