mos2层数变化与mos2/sio2异质结界面应力应变之间的定量关系研究方法

技术领域

1.本发明涉及mos2fets几何结构研究技术领域,具体为mos2层数变化与mos2/sio2异质结界面应力应变之间的定量关系研究方法。

背景技术:

2.传统的半导体器件都是基于硅的,众所周知,随着器件尺寸的持续减小,由于一系列小尺寸效应的存在,这一材料已经到达其尺寸的极限。因此过渡金属硫化物(tmd)作为替代硅的沟道材料被广泛研究。由于高的开关电流比和好的电子性能,二硫化钼(mos2)成为过渡金属硫化物中最常用的分层材料之一,它的电子结构与层数目、堆叠方向都有很大关系。而外加应力或应变来改变一个材料的物理特性,被认为是调控器件特性的一种清洁无害的手段。

3.在上述改变层数、堆叠方向和施加应力应变来调控mos2性能的领域,已经开展了大量的研究。例如应变诱导可使mos2由直接带隙变为间接带隙,还可实现将mos2从半导体属性转变到金属属性等物理效应。块体mos2是间接带隙半导体,减薄至单层后,由于激子间接跃迁能量的增大,mos2带隙转变为直接带隙。随着二硫化钼层数的减少,基于mos2的场效应晶体管中的发光量子效应、器件特性和优良的机械性能都会有显著变化。通过实验施加单轴拉伸应变(平面内),单层和双层mos2通常会发生光谱的红移。此外,三层mos2在施加面内压缩双轴应变时,光谱会发生蓝移。单层和多层mos2的直接和间接带间跃迁都可使用静水压力来进行有效地调控。理论工作预测,在mos2晶体结构的c轴上产生单轴压缩应变时,带隙会减小。

技术实现要素:

4.(一)解决的技术问题

5.针对现有技术的不足,本发明提供了mos2层数变化与mos2/sio2异质结界面应力应变之间的定量关系研究方法。

6.(二)技术方案

7.为实现上述目的,本发明提供如下技术方案:mos2层数变化与mos2/sio2异质结界面应力应变之间的定量关系研究方法,

8.步骤一:构建研究模型系统;

9.步骤二:对第一性原理的截断能进行了测试;

10.步骤三:mos

2 fets的隧穿特性研究;

11.步骤四:mos

2 fets的输出特性研究;

12.步骤五:mos

2 fets的阈值电压和亚阈值摆幅研究;

13.优选的,构建研究模型系统具体为:采用mos2作为沟道材料,mos2厚度的变化对应mos2fets沟道厚度的变化,采用氢钝化mos2/sio2结构(mos2/h

–

sio2)作为研究系统,氢钝化

mos2/sio2结构中的mo-s键长为晶格常数为上下硫原子的距离为

14.优选的,通过增减mos2层数,分别构造了由1层,2层,3层,4层和5层s

–

mo

–

s与sio2组成的mos2/h-sio2异质结,将这些结构依据mos2层数分别用1l,2l,3l,4l和5l来标记,异质结接触界面通过在2

×

2的sio2(111)表面上放置一个3

×

3的单层mos2来实现。

15.优选的,所述步骤二:对第一性原理的截断能具体为:在进行计算时,使用320ev的截断能;

16.第一性原理计算使用castep程序包赝势使用范德瓦尔超软赝势,结构优化使用的自洽场能量收敛准则为5

×

10-7

ev/atom,平面波的截断能e

cut

=320ev,k点网格大小为10

×

10

×

1,为了避免结构之间相互影响,在计算中,所有异质结界面结构全部使用的真空层厚度。

17.优选的,所述步骤三:mos

2 fets的隧穿特性研究具体为:使用平均势的方法计算价带谱mos2/sio2超晶格的静电势在x-y平面取平均;

18.a、z方向的平面微观势使用下式进行计算;

19.b、不同mos2层数的势垒高度;

20.c、计算mos2层数变化对mos

2 fets隧穿特性的影响;

21.d、考虑能带的非抛物线性的fn隧穿电流,fn隧穿电流随栅氧电压的变化;

22.e、考虑能带的非抛物线性的fn隧穿电流,fn隧穿电流随栅氧厚度的变化;

23.f、考虑镜像势引起的势垒降低效应和能带的非抛物线性的直接隧穿电流,直接隧穿电流随栅压的变化;

24.g、考虑镜像势引起的势垒降低效应和能带的非抛物线性的直接隧穿电流,镜像势对直接隧穿电流的影响。

25.优选的,所述步骤四:mos

2 fets的输出特性研究具体为:将mos2作为沟道材料,sio2作为栅介质材料,利用mos2/sio2界面替代si/sio2界面构造mosfet,运用mos器件输出特性方程,得到在不同的mos2层数条件下的输出特性曲线。

26.优选的,所述步骤五:mos

2 fets的阈值电压和亚阈值摆幅研究具体为:利用阈值电压公式计算mos2作为沟道材料,sio2作为栅介质材料的mos

2 fets的阈值电压,利用亚阈值摆幅的计算公式得到mos2基器件亚阈值摆幅与栅压的关系。

27.优选的,当mos2层厚相同时,施加栅压越小,亚阈值摆幅越大,在同样的栅压下,mos2层数越小,亚阈值摆幅的值也越小。

28.优选的,作为沟道的mos2的层数取值为1时,可实现低至70mv/dec的亚阈值摆幅,当栅压减小到0.3v时,亚阈值摆幅虽然会增大,但也仅有79mv/dec,而在第四章对硅基器件的亚阈值特性的研究中得到,当si层取值为1,栅压等于0.3v时,si/sio2界面mos器件的亚阈值摆幅高达109mv/dec

29.优选的,在整个亚阈值区,亚阈值摆幅的相对变化量,栅压越小,亚阈值摆幅的变化量越大,即在低功耗mos

2 fets的制备中,沟道厚度的细微变化,对器件开关特性都会造成很大的影响。

30.(三)有益效果

31.与现有技术相比,本发明提供了mos2层数变化与mos2/sio2异质结界面应力应变之

间的定量关系研究方法,具备以下有益效果:

32.1、该mos2层数变化与mos2/sio2异质结界面应力应变之间的定量关系研究方法,通过改变层厚和施加应力,能有效地调控mos2的光子、机械和电子性能,揭示了mos2层数变化与mos2/sio2异质结界面应力应变之间的定量关系,并系统地研究了mos2层数变化对器件光电性能的影响。

33.2、该mos2层数变化与mos2/sio2异质结界面应力应变之间的定量关系研究方法,通过利用mos

2 fets的输出特性研究结果,在进行实际器件设计时,可在满足器件小尺寸设计要求和保障栅极对器件进行有效调控的同时,使器件的饱和电流降低,这一发现,对目前新型二维器件追求小型化同时满足高效栅控性能的需求,有重要的理论意义。

附图说明

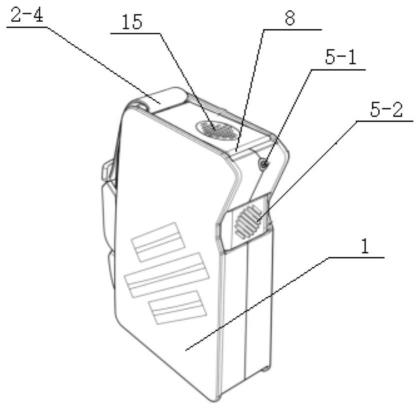

34.图1为本发明mos2fets的侧面几何结构示意图;

35.图2为本发明由4层mos2构成的mos2/h-sio2接触界面模型的侧面图

36.图3本发明截断能与基态能量的关系

37.图4本发明沿z方向的平面微观势

38.图5本发明不同mos2层数的势垒高度

39.图6本发明fn隧穿电流随栅氧电压的变化

40.图7本发明fn隧穿电流随栅氧厚度的变化

41.图8本发明直接隧穿电流随栅压的变化

42.图9本发明镜像势对直接隧穿电流的影响

43.图10发明直接隧穿电流随栅氧厚度的变化

44.图11发明镜像势对直接隧穿电流的影响

45.图12发明不同mos2层数的mos2fets的输出特性

46.图13发明不同mos2层厚度时夹断电压随栅压的变化;

47.图14发明阈值电压随mos2层数的变化情况

48.图15发明亚阈值摆幅与栅压的关系

49.图16发明在整个亚阈值区,亚阈值摆幅的相对变化量与栅压的关系

50.图17发明在整个亚阈值区,亚阈值摆幅的相对变化量与层数的关系

具体实施方式

51.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

52.请参阅图1-17,mos2层数变化与mos2/sio2异质结界面应力应变之间的定量关系研究方法,

53.在使用时,mos器件的几何结构如图1所示,其中mos2作为沟道材料,因此mos2厚度的变化对应mos2fets沟道厚度的变化,在进行mos2fets的研究时,选择已被广泛认可的氢钝化mos2/sio2结构(mos2/h

–

sio2)作为研究系统,如图2所示,mo-s键长为晶格常数为

上下硫原子的距离为

54.为揭示mos2层数变化和应力应变的关系,通过增减mos2层数,分别构造了由1层,2层,3层,4层和5层s

–

mo

–

s与sio2组成的mos2/h-sio2异质结,为了方便分析,将这些结构依据mos2层数分别用1l,2l,3l,4l和5l来标记,异质结接触界面通过在2

×

2的sio2(111)表面上放置一个3

×

3的单层mos2来实现,可有效降低晶格失配,图2给出了mos2层数为4时,mos2/h-sio2异质结界面理论模型,即4l的电子结构。

55.为使计算更加准确,首先对第一性原理的截断能进行了测试,由图3可见,当截断能高于310ev之后,能量基本收敛。

56.同时考虑计算成本和计算精确度,在进行计算时,使用320ev的截断能。

57.第一性原理计算使用castep程序包赝势使用范德瓦尔超软赝势,结构优化使用的自洽场能量收敛准则为5

×

10-7

ev/atom,平面波的截断能e

cut

=320ev,k点网格大小为10

×

10

×

1。为了避免结构之间相互影响,在计算中,所有异质结界面结构全部使用的真空层厚度。

58.mos

2 fets的隧穿特性研究

59.使用平均势的方法计算价带谱mos2/sio2超晶格的静电势在x-y平面取平均;接下来,z方向的平面微观势使用下式进行计算:

[0060][0061]

微观平均势的计算结果如图4示,由图4可见,在mos2/h-sio2界面处,能带从mos2一侧到sio2一侧是连续变化的,对微观平均势进行分析,计算得到的势垒高度如图5所示,图5中很明显看出,随着mos2层数的增大,mos2/h-sio2界面的势垒高度呈下降趋势,很显然,由于势垒高度的减小,隧穿电流将会随之增加,即隧穿电流会随mos2层数的增加而变大。

[0062]

利用给出fn隧穿电流和直接隧穿电流的公式,计算mos2层数变化对mos2fets隧穿特性的影响,图5计算得到的考虑能带的非抛物线性的fn隧穿电流随mos2层数变化情况。

[0063]

图6是计算得到的考虑能带的非抛物线性fn隧穿电流随栅氧电压的变化,由图可见,随着mos2层数的增大,fn隧穿电流增大,且栅氧电压越大,fn隧穿电流也越大,图7是fn隧穿电流随栅氧厚度的变化,从图中很明显看出,随着栅氧厚度的减小,fn隧穿电流直线增大,且mos2层数越小,栅氧厚度的变化对fn隧穿电流的影响越大,对应于图7中实线的斜率最大。

[0064]

为了分析在不同栅压下mos2层厚对隧穿电流的影响程度,接下来分别计算了v

ox

=0.5v和v

ox

=2v两种条件下隧穿电流的相对变化量,如图8,从图中看到,随着mos2层数的减小,隧穿电流的相对变化量增大,研究结果表明,随着mos2层数的减小,即随着器件尺寸的减小,沟道厚度的影响会越来越严重,在目前电子器件的制备进入纳米及以下尺寸的情况下,必须对mos2层厚的影响加以考虑和研究。

[0065]

图9是在不同的栅氧化层电压作用下,考虑镜像势引起的势垒降低效应和能带的非抛物线性的直接隧穿电流随mos2层数的变化情况,从图9中看出,随着mos2层数的增加,直接隧穿电流增大,但当mos2层数增加到3层及以上时,电流的增大趋势减弱,即此时mos2层厚变化对直接隧穿电流的影响变弱。

[0066]

为了进一步观察镜像势的存在对直接隧穿电流和栅氧电压关系的影响,图9给出

了考虑镜像势和不考虑镜像势得到的直接隧穿电流的比值,从图中看到,mos2层数越小,比值越大,这说明在薄沟道器件中,镜像势的影响越大,同时,还得到结论:镜像势对直接隧穿电流的影响随栅氧电压的增大而减小,且当接近fn隧穿区域时,该比值变得很小。

[0067]

图10是在不同的沟道厚度条件下,直接隧穿电流随栅氧厚度的变化情况,从图中看出,随着mos2层数的增加,直接隧穿电流增大,且mos2层数越小,栅氧厚度变化对直接隧穿电流的影响越大,即沟道厚度越小,直接隧穿电流受栅氧厚度变化的影响越大。

[0068]

为了进一步观察镜像势的存在对直接隧穿电流和栅氧厚度关系的影响,图11给出了考虑镜像势和不考虑镜像势得到的直接隧穿电流的比值,从图中看到,mos2层数越小,比值越大,并且镜像势对直接隧穿电流的影响随栅氧厚度的增大而增大,图10中j1为不考虑镜像势效应的直接隧穿电流。

[0069]

mos

2 fets的输出特性研究

[0070]

将mos2作为沟道材料,sio2作为栅介质材料,利用mos2/sio2界面替代si/sio2界面构造mosfet,运用mos器件输出特性方程,得到在不同的mos2层数条件下的输出特性曲线,如图12所示。

[0071]

由图12可见,随着mos2层数的增加,在同样的栅压和漏电压作用下,漏电流逐渐增大,这是因为随着mos2层数的增加,沟道厚度变大,半导体表面的反型层变厚,从源端到漏端的电子增多,引起漏电流的增大,这与以si/sio2接触界面构造的器件的漏流特性与沟道厚度的关系一致,当漏电压较小时,漏电流线性增加,而当漏电压较大时,器件开始进入饱和区,在所有层厚的mos

2 fets中均发现了这一现象,与mos2的层数无关,通过实验也观察到了同样的漏电流最大值随mos2层数的变化规律。

[0072]

从图12中还得到,mos2层数越小,达到饱和所需的漏电流越小,当mos2层数为1层时,漏端电压vd大约为1.7v时,器件就达到饱和,而当mos2层数为5时,vd约为2.2v时,器件才达到饱和,为了更清楚地观察饱和时夹断电压的情况,本章进一步计算了不同栅压条件下,不同mos2层数条件下夹断电压随栅压的变化情况,如图13所示。

[0073]

由图13可见,当栅极电压相同时,mos2层厚度越大,夹断电压越大,夹断电压与栅压成正比,因此,增加mos2层厚度与增加栅压一样,都会造成夹断电压的增大,从而引起饱和电流的增加,以mos2作为沟道材料时,漏电流随沟道厚度增加而增大的幅度要小于以si作为沟道的情况,计算结果表明,增减mos2层厚度可有效调节mos器件的饱和电流,即当减小mos2层厚度时,可在栅压不变的情况下,降低器件的饱和电流。

[0074]

利用这一研究结果,在进行实际器件设计时,可在满足器件小尺寸设计要求和保障栅极对器件进行有效调控的同时,使器件的饱和电流降低,这一发现,对目前新型二维器件追求小型化同时满足高效栅控性能的需求,有重要的理论意义。

[0075]

mos

2 fets的阈值电压和亚阈值摆幅研究

[0076]

利用阈值电压公式计算mos2作为沟道材料,sio2作为栅介质材料的mos2fets的阈值电压,计算结果如图14所示。

[0077]

从图14中看出,mos2层数越大,阈值电压越小,阈值电压的这一现象,与传统si/sio2器件阈值电压随si层数变化的趋势类似,即沟道厚度越小,阈值电压越高,减小氧化层的厚度也会造成阈值电压的减小,因此在小尺寸器件中,为得到不同的阈值电压,在无法增减氧化层厚度的情况下,可利用沟道mos2层数的变化对阈值电压的影响来实现对阈值电压

的间接调控,mos2基器件同样需要牺牲衬底的尺寸来获得较低的开启电压,mos2作为沟道材料,sio2作为栅介质材料,利用亚阈值摆幅的计算公式得到图15、图16和图17所示的mos2基器件亚阈值摆幅与栅压的关系。

[0078]

从图15中看到,当mos2层厚相同时,施加栅压越小,亚阈值摆幅越大,在同样的栅压下,mos2层数越小,亚阈值摆幅的值也越小,研究结果表明,通过减小mos2层数的方法可使亚阈值摆幅减小,从而提高器件的开关速度,栅压等于0.4v时,以单层mos2为沟道的mos

2 fets的亚阈值摆幅(~77mv/dec)小于2~5层mos2为沟道的mos

2 fets的亚阈值摆幅(分别为~81mv/dec,~84mv/dec,~86mv/dec和~86mv/dec),即mos

2 fets的沟道厚度越小,栅控特性越好,这是因为离栅最近的层可有效地屏蔽由于状态密度大而产生的栅极电势,而其他层不可以,因此当层数超过一层时,无法有效地控制栅极。

[0079]

进一步分析图15得到,作为沟道的mos2的层数取值为1时,可实现低至70mv/dec的亚阈值摆幅,当栅压减小到0.3v时,亚阈值摆幅虽然会增大,但也仅有79mv/dec,而在第四章对硅基器件的亚阈值特性的研究中得到,当si层取值为1,栅压等于0.3v时,si/sio2界面mos器件的亚阈值摆幅高达109mv/dec,这从理论上证明了基于二维材料的纳米器件,可解决传统硅基器件开关速度过慢的问题,具有很好的静电控制能力,因此,与传统硅基器件相比,在进行mos2基器件的制备时,可在满足小尺寸需求的同时,得到较高的开关速度。

[0080]

图16给出了mos2层数为1和5时,在整个亚阈值区,亚阈值摆幅的相对变化量,从图中得到,栅压越小,亚阈值摆幅的变化量越大,即在目前低功耗mos

2 fets的制备中,沟道厚度的细微变化,对器件开关特性都会造成很大的影响,造成器件性能的下降,为了更直观地观察mos2层厚度变化引起的亚阈值摆幅的变化情况,图17给出了取不同mos2层数时,在整个亚阈值区(栅压为0v-1v),亚阈值摆幅的相对变化量δs,从图中看出,mos2层厚越大,亚阈值摆幅的相对变化量越大,mos2为单层时,mos

2 fets的亚阈值摆幅相对变化量约为75mv/dec;而当mos2为5层时,亚阈值摆幅的相对变化量更高达133mv/dec,从图中还可看到,当mos2层数超过4层(此时沟道厚度约为3nm)之后,亚阈值摆幅几乎不再变化,即当沟道厚度增厚到3nm以上,依靠沟道层数变化而引入效应对异质结器件亚阈值摆幅进行调控的效果已经不明显,而在沟道厚度减小到3nm以下的小尺寸器件中,亚阈值摆幅对mos2层数的变化比较敏感,这给纳米及以下尺寸器件开关速度的提升提供了新的思路。

[0081]

尽管已经示出和描述了本发明的实施例,对于本领域的普通技术人员而言,可以理解在不脱离本发明的原理和精神的情况下可以对这些实施例进行多种变化、修改、替换和变型,本发明的范围由所附权利要求及其等同物限定。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。