芯片封装方法及封装结构

1.本专利申请是下列发明专利申请的分案申请:

2.申请号:201711227089.5

3.申请日:2017年11月29日

4.发明名称:

5.本公开涉及半导体技术领域,尤其涉及一种芯片封装方法及封装结构。

背景技术:

6.已有技术中,一种常见的芯片封装技术主要包含下述工艺过程:首先将芯片正面通过胶带粘接在衬底晶圆上,进行晶圆级塑封,将衬底晶圆剥离,然后在芯片正面进行再布线,形成再布线层,并进行封装。

技术实现要素:

7.本公开第一方面提供了一种芯片封装方法,包括:

8.在待封装芯片的正面形成保护层;

9.将正面形成有保护层的所述待封装芯片贴装于第一载板上,所述待封装芯片的背面朝上,正面朝向所述第一载板;

10.形成第一包封层,所述第一包封层形成在所述待封装芯片背面以及露出的所述第一载板上;

11.剥离所述第一载板,露出所述保护层。

12.可选地,在待封装芯片的正面形成保护层,包括:

13.在晶圆正面形成保护层;

14.将形成有保护层的所述晶圆切割成多个所述待封装芯片。

15.可选地,将形成有保护层的所述晶圆切割成多个所述待封装芯片之前,还包括:

16.在所述保护层上与多个所述待封装芯片的焊垫相对应的位置处形成保护层开口。

17.可选地,在所述保护层上与多个所述待封装芯片的焊垫相对应的位置处形成保护层开口之后,还包括:

18.在所述保护层开口中填充导电介质,使得导电介质与所述待封装芯片的焊垫电连接。

19.可选地,将正面形成有保护层的所述待封装芯片贴装于第一载板上,包括:

20.在所述第一载板上形成粘接层;

21.将所述待封装芯片通过所述粘接层粘贴于所述第一载板的预定位置处。

22.可选地,剥离所述第一载板,暴露出所述保护层之后,还包括:

23.在所述保护层上形成保护层开口,所述保护层开口位于所述待封装芯片的焊垫处;

24.在所述保护层上形成第一再布线层,所述第一再布线层通过所述保护层开口与所述待封装芯片上的焊垫电连接。

25.可选地,剥离所述第一载板,暴露出所述保护层之后,还包括:

26.在所述保护层上形成第一再布线层,所述第一再布线层通过所述保护层开口与所述待封装芯片上的焊垫电连接。

27.可选地,所述方法还包括:

28.在所述第一再布线层上形成第二包封层,并通过第一导电凸柱引出所述第一再布线层的焊垫或连接点。

29.可选地,所述方法还包括:

30.在第二包封层上形成第二再布线层,所述第二再布线层通过所述第一导电凸柱与所述第一再布线层的焊垫或连接点电连接;

31.在第二再布线层上形成第三包封层,并通过第二导电凸柱引出所述第二再布线层的焊垫或连接点。

32.可选地,在所述第一再布线层上形成第二包封层,并通过第一导电凸柱引出所述第一再布线层的焊垫或连接点,包括:

33.在所述第一再布线层的焊垫或连接点上形成第一导电凸柱;

34.在所述第一再布线层以及露出的钝化层上形成第二包封层,并露出所述第一导电凸柱;或,

35.在所述第一再布线层上形成第二包封层,并通过第一导电凸柱引出所述第一再布线层的焊垫或连接点,包括:

36.在所述第一再布线层以及露出的保护层上形成第二包封层;

37.在所述第二包封层上与所述第一再布线层的焊垫或连接点对应的位置处形成第一开口;

38.在所述第一开口内形成第一导电凸柱。

39.可选地,在第二再布线层上形成第三包封层,并通过第二导电凸柱引出所述第二再布线层的焊垫或连接点,包括:

40.在所述第二再布线层的焊垫或连接点上形成第二导电凸柱;

41.在所述第二再布线层以及露出的第二包封层上形成第三包封层,并露出所述第二导电凸柱;或,

42.形成第三包封层,包封所述第二再布线层以及露出的第二包封层,并通过第二导电凸柱引出所述第二再布线层的焊垫或连接点,包括:

43.在所述第二再布线层以及露出的第二包封层上形成第三包封层;

44.在所述第三包封层上与所述第二再布线层的焊垫或连接点对应的位置处形成第二开口;

45.在所述第二开口内形成第二导电凸柱。

46.可选地,将正面形成有保护层的所述待封装芯片贴装于第一载板上之后,还包括:

47.形成密封层,所述密封层包裹在所述至少一个待封装芯片的四周。

48.可选地,将所述包封层包封住的所述至少一个待封装芯片从所述第一载板剥离之前,还包括:

49.在包封层上粘贴第二载板。

50.可选地,所述方法还包括:

51.将至少一个被动元件贴装于所述第一载板上邻近所述待封装芯片的位置处,所述至少一个被动元件的背面朝上,正面朝向所述第一载板。

52.可选地,所述方法还包括:

53.在所述至少一个被动元件为导电凸柱或连接元件时,使得所述至少一个被动元件的厚度大于或等于所述至少一个待封装元件,且在形成第一包封层时将所述第一包封层减薄至所述至少一个被动元件的表面。

54.可选地,所述方法将至少一个被动元件贴装于所述第一载板上邻近所述待封装芯片的位置处,所述至少一个被动元件的正面朝向所述第一载板。

55.根据本公开第二方面,提供了一种芯片封装结构,包括:

56.第一包封层,该第一包封层上设置有多个内凹的第一腔体;

57.多个芯片,分别位于多个所述第一腔体内,所述多个芯片的背面超向所述第一包封层;

58.保护层,形成于所述多个芯片的正面,且所述保护层上形成有保护层开口,所述保护层开口位于所述多个芯片正面的焊垫对应位置处;

59.再布线结构,形成于所述多个芯片的正面,用于将所述多个芯片正面的焊垫引出。

60.根据本公开第三方面,还提供了一种芯片封装结构,包括:

61.第一包封层,该第一包封层上设置有内凹的第一腔体;

62.芯片,位于所述第一腔体内,所述芯片的背面超向所述第一包封层;

63.保护层,形成于所述芯片的正面,且所述保护层上形成有保护层开口,所述保护层开口位于所述芯片正面的焊垫对应位置处;

64.再布线结构,形成于所述芯片的正面,用于将所述芯片正面的焊垫引出。

65.可选地,所述芯片封装结构还包括:

66.密封层,形成于所述第一包封层上表面以及包裹在所述至少一个待封装芯片的四周,和/或所述密封层连续不间断的覆盖在所述第一包封层上表面以及至少包裹在所述芯片的四周。

67.可选地,所述再布线结构包括:

68.第一再布线层,形成于所述保护层和露出的第一包封层上,且通过所述保护层开口与所述芯片的焊垫电连接;

69.第二包封层,形成于所述第一再布线层以及露出的所述第一包封层上,且具有第一开口,所述第一开口内设置有与所述第一再布线层电连接的第一导电凸柱。

70.可选地,所述再布线结构包括:

71.第一再布线层,形成于所述保护层上,且通过所述保护层开口与所述芯片的焊垫电连接;

72.第二包封层,形成于所述第一再布线层以及露出的所述第一包封层上,且具有第一开口,所述第一开口内设置有与所述第一再布线层电连接的第一导电凸柱。

73.可选地,所述芯片封装结构还包括:

74.至少一个被动元件,位于所述第一包封层上设置的至少一个内凹的第二腔体内,

所述第二腔体邻近所述第一腔体设置,所述至少一个被动元件的背面朝向所述第一包封层,所述至少一个被动元件的正面与所述第一再布线层电连接。

附图说明

75.图1是根据本公开一示例性实施例提出的芯片封装方法的流程图。

76.图2(a)~(o)是根据本公开一示例性实施例提出的芯片封装方法的流程图。

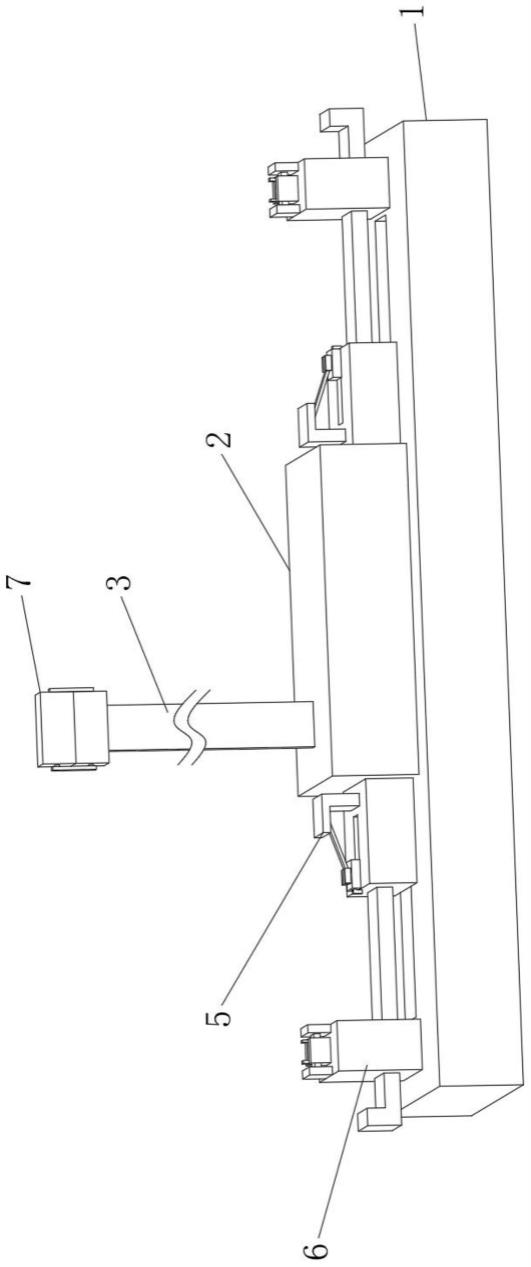

77.图3是根据本公开一示例性实施例提出的载板正面结构示意图。

78.图4(a)~(g)是根据本公开另一示例性实施例提出的芯片封装方法的流程图。

79.图5(a)~(j)是根据本公开一示例性实施例提供的利用上述芯片封装方法得到的芯片封装结构的结构示意图。

80.图6是根据本公开另一示例性实施例提供的利用上述芯片封装方法得到的芯片封装结构的结构示意图。

81.图7是根据本公开再一示例性实施例提供的利用上述芯片封装方法得到的芯片封装结构的结构示意图。

82.图8是根据本公开再一示例性实施例提供的利用上述芯片封装方法得到的芯片封装结构的结构示意图。

83.图9是根据本公开再一示例性实施例提供的利用上述芯片封装方法得到的芯片封装结构的结构示意图。

84.图10是根据本公开再一示例性实施例提供的利用上述芯片封装方法得到的芯片封装结构的结构示意图。

85.图11是根据本公开再一示例性实施例提供的利用上述芯片封装方法得到的芯片封装结构的结构示意图。

86.图12是根据本公开再一示例性实施例提供的利用上述芯片封装方法得到的芯片封装结构的结构示意图。

具体实施方式

87.为使本发明的目的、技术方案和优点更加清楚明白,以下结合具体实施例,并参照附图,对本发明进一步详细说明。

88.在封装过程中,待封装芯片的正面贴装于载板上后,在对待封装芯片的背面进行包封时,通常需要高压成型的方式形成包封层,而这个过程中包封材料容易渗入到待封装芯片与载板之间的缝隙当中,进而会破坏待封装芯片正面的焊垫和/或电路等,造成芯片不良率升高。

89.根据本公开的各个实施例,提供了一种芯片封装方法。在封装过程中,在待封装芯片的正面形成保护层,将正面形成有保护层的待封装芯片贴装于第一载板上,待封装芯片的正面朝向所述第一载板,而背面朝上,即相对载板朝外;之后形成第一包封层,覆盖住所述待封装芯片以及所述第一载板。在包封完成后,将第一载板剥离,即去除第一载板,暴露出保护层以及第一包封层。本公开的上述实施方式,通过将待封装芯片的正面形成保护层后贴装于载板上,之后再对待封装芯片上形成第一包封层时,可以防止包封材料渗透到待封装芯片及载板的缝隙中,进而破坏待封装芯片上的电路结构和/或焊垫等。

90.图1是根据本公开一实例性实施例提出的芯片封装方法的流程图。如图1所示,芯片封装方法包括下述步骤101-104。其中:

91.在步骤101中,在待封装芯片的正面形成保护层。

92.在一实施例中,待封装芯片是通过对一个半导体晶圆进行减薄、切割而成,每个半导体晶圆可以形成多个待封装芯片,待封装芯片之间具有切割道,每个半导体晶圆经过减薄、切割后形成多个芯片。待封装芯片的正面由芯片内部电路引出至芯片表面的导电电极构成,焊垫制备在这些导电电极上。

93.本实施例中,在将待封装芯片贴装于第一载板之前,在待封装芯片的正面形成保护层。所述保护层可以在将半导体晶圆切割成多个待封装芯片之前形成在半导体晶圆的正面,之后再对半导体晶圆进行切割,得到正面形成有保护层的待封装芯片。当然可以理解的是,在工艺允许的情况下,还可以将半导体晶圆切割成待封装芯片后,在每个待封装芯片正面形成保护层,具体根据实际的情况选择。

94.图2示出了本公开一示例性实施例中芯片封装方法的工艺流程图。

95.如图2(a)所示,在半导体晶圆100正面即对应待封装芯片201正面的表面形成一保护层202,之后再将形成有保护层202的所述半导体晶圆100沿着切割道进行切割,得到多个形成有保护层的待封装芯片201。

96.保护层202采用绝缘材料,如聚酰亚胺、环氧树脂、abf(ajinomoto buildup film)以及pbo(polybenzoxazole)等。可选地,保护层的材料选择绝缘,且能够适应化学清洗、研磨等的材料。保护层可以通过层压(lamination)、涂覆(coating)、印刷(printing)等方式形成在半导体晶圆上。由于半导体晶圆100再被切割之前通常会被磨薄,如磨薄到50微米,因此在操作半导体晶圆100时,通过在半导体晶圆100正面形成保护层202,既能够对半导体晶圆100正面的电路起到保护作用,还能对超薄的半导体晶圆100起到一定的支撑作用。

97.在步骤102中,将正面形成有保护层的所述待封装芯片贴装于第一载板上,所述待封装芯片的背面朝上,正面朝向所述第一载板。

98.如图2(b)所示,正面形成有保护层202的待封装芯片201(图中示出了多个待封装芯片)贴装于第一载板200。正面形成有保护层202的待封装芯片201与第一载板200之间通过粘接层203连接,保护层202与粘接层203直接接触。

99.在一实施例中,载板200的形状可包括:圆形、矩形或其他形状,本公开对载板200的形状不做限定。载板200可以是小尺寸的晶圆衬底,也可以是更大尺寸的载板,例如不锈钢板、聚合物基板等。利用本公开实施例的芯片封装方法,可采用的载板尺寸能够达到600*600mm。

100.在一实施例中,待封装芯片201可以通过粘接层203贴装于载板200,且粘接层203可采用易剥离的材料,以便将载板200和背面封装好的待封装芯片201剥离开来,例如可采用通过加热能够使其失去粘性的热分离材料。在其他实施例中,粘接层203可采用两层结构,热分离材料层和芯片附着层,热分离材料层粘贴在载板200上,在加热时会失去粘性,进而能够从载板200上剥离下来,而芯片附着层采用具有粘性的材料层,可以用于粘贴待封装芯片201。而待封装芯片201从载板200剥离开来后,可以通过化学清洗方式去除其上的芯片附着层。在一实施例中,可通过层压、印刷等方式,在载板200上形成粘接层203。

101.在一实施例中,如图3所示,载板200上预先设置有待封装芯片201的粘贴位置,在

形成粘接层203之后,将正面形成有保护层202的待封装芯片201粘贴在载板200的预定位置a处。在一实施例中,形成粘接层203之前,可采用激光、机械刻图、光刻等方式在载板200上预先标识出待封装芯片的粘贴位置,而同时待封装芯片201上也设置有对位标识,以在粘贴时与载板200上的粘贴位置瞄准对位。需要注意的是,保护层在某种光线下可以是透明的,以便能够看清设置在待封装芯片201上的对位标识,能够将待封装芯片201准确无误的粘贴在预定位置a处。此外,除了在载板上粘贴待封装芯片201之外,如果封装体需要被动元件的话,还可以在待封装芯片201的周围粘贴上被动元件。可以理解的是,一次封装过程中,待封装芯片201可以是多个,即在载板200上同时贴装多个待封装芯片201,进行封装,并在完成封装后,再切割成多个封装体;一个封装体可以包括一个或多个芯片,而多个芯片的位置可以根据实际产品的需要进行自由设置。

102.在另一实施例中,将形成有保护层的所述晶圆切割成多个所述待封装芯片之前,还包括:在所述保护层上与多个所述待封装芯片的焊垫相对应的位置处形成保护层开口。如图2(c)所示,在将形成有保护层202的半导体晶圆100切割成多个待封装芯片之前,在保护层202上与多个待封装芯片201的焊垫相对应的位置处形成多个保护层开口2021,使得待封装芯片201正面的焊垫或者从焊垫引出的线路从保护层开口2021暴露出来。如果保护层材料是激光反应性材料,可以采用激光图形化的方式一次形成一个保护层开口2021的方式开孔;如果保护层材料是光敏材料,则可以采用光刻图形化方式,一次形成多个保护层开口2021的开孔方式。保护层开口2021的形状可以是圆的,当然也可以是其他形状如椭圆形、方形、线形等。在一可选的实施例中,如图2(d)所示,在所述保护层202上形成有多个保护层开口2021,将芯片上的焊垫从所述保护层开口2021露出。在形成有所述保护层202的芯片粘贴在所述载板200的粘接层203上之后,多个保护层开口2021呈中空状态。

103.在另一实施例中,在所述保护层上与多个所述待封装芯片的焊垫相对应的位置处形成第一开口之后,还包括:在所述保护层开口中填充导电介质,使得导电介质与所述待封装芯片的焊垫电连接。导电介质在保护层开口中形成竖直的连接结构,使得将芯片表面的焊垫单一方面延伸至保护层表面,保护层可以围绕形成在连接结构的四周。如图2(e)所示,在保护层开口2021中填充导电介质2022,将待封装芯片203正面电路上的焊垫引出至保护层202的表面,以便后续工艺中进行再布线。在一可选的实现方式中,如图2(f)所示,在所述保护层202上形成多个保护层开口2021,且保护层开口2021中填充导电介质,导电介质在保护层开口中形成竖直的连接结构2022,将芯片上的焊垫沿竖直方向引出至保护层202的表面。所述保护层202和所述连接结构2022粘贴在所述载板200的粘接层203上。

104.本公开实施例,通过预先在保护层202上形成保护层开口2021和/或填入导电介质的方式,使得芯片正面的焊垫位置可以通过保护层开口2021精准定位,且保护层开口面积可以做的更小,开口之间的间距也能够更小,这样使得后续再布线时,布线可以更加紧密,不用担心芯片焊垫位置定位偏差的问题。

105.在步骤103中,形成第一包封层,所述第一包封层形成在所述待封装芯片以及露出的所述第一载板上。

106.第一包封层204形成在待封装芯片201的背面以及露出的所述第一载板200上,如果露出的第一载板200上形成有粘接层203时,第一包封层204形成在待封装芯片201的背面以及露出的粘接层203上,如图2(g)所示。第一包封层204用于将第一载板200和待封装芯片

201完全包封住,以重新构造一平板结构,以便在将载板200剥离后,能够继续在重新构造的该平板结构上进行再布线和封装。

107.可选地,在形成第一包封层204之前,可以执行一些前处理步骤,例如化学清洗、等离子清洗方式,将表面的杂质去除,以便第一包封层与待封装芯片和第一载板之间能够连接的更加密切,不会出现开裂的现象。

108.在一实施例中,第一包封层204可采用层压环氧树脂膜或abf(ajinomoto buildup film)的方式形成,也可以通过对环氧树脂化合物进行注塑成型(injection molding)、压模成型(compression molding)或转移成型(transfer molding)的方式形成。第一包封层204包括与第一载板200相对的第一表面2041,基本上呈平板状,且与所述第一载板200的表面平行。第一包封层204的厚度可以通过对第一表面2041进行研磨或抛光来减薄,在一实施例中,第一包封层204的厚度可减薄至待封装芯片201的背面。

109.在利用第一包封层204包封时,由于第一包封层在成型时需要高压成型,在此过程中包封材料容易渗透到第一载板200与待封装芯片201之间。通过本公开实施例,在待封装芯片201正面形成一层保护层202,保护层202与粘接层203的连接更加紧密,因此能够防止包封材料渗透到两者之间,而且即使包封材料有渗入,在与载板剥离之后,还可以通过化学方式或者研磨方式直接处理保护层202的表面,而不会直接接触到待封装芯片201的正面,进而无法破坏待封装芯片201正面的电路结构。

110.在步骤104中,剥离所述载板,露出所述保护层。

111.在一实施例中,如图2(h)所示,可直接机械的剥离第一载板200;如果第一载板200与保护层202之间的粘接层203具有热分离材料时,还可以通过加热的方式,使得粘接层203上的热分离材料在遇热后降低粘性,进而剥离第一载板200。第一载板200剥离后,暴露出了朝向第一载板200的第一包封层203的下表面和保护层202。剥离第一载板200后,得到了包括待封装芯片201、覆盖在待封装芯片201正面的保护层202以及包封待封装芯片201背面的第一包封层204的平板结构。在形成的上述平板结构上,可以根据实际情况进行再布线等。

112.本公开实施例中,在剥离了第一载板200之后,暴露出保护层202以及第一包封层204的表面,此时粘接层202中芯片附着层还存在于保护层202和第一包封层204的表面,而通过化学方式去除时,保护层202还能够保护芯片表面不受破坏;在完全去除粘接层后,如果之前渗入了包封材料时,还可以采用化学清洗或研磨的方式使得表面平整,有利于后面布线;而如果没有保护层,则无法通过化学方式或者研磨的方式处理芯片表面,以免破坏芯片正面的电路。

113.在一实施例中,剥离所述第一载板,暴露出所述保护层之后,还包括:在所述保护层上形成保护层开口,所述保护层开口位于所述待封装芯片的焊垫处;在所述保护层上形成第一再布线层,所述第一再布线层通过所述保护层开口与所述待封装芯片上的焊垫电连接。

114.如图2(i)所示,在剥离第一载板200之后,在保护层202上形成多个保护层开口2021,每个保护层开口2021至少对应位于待封装芯片201的焊垫或者从焊垫引出的线路上,使得待封装芯片201正面的焊垫或者从焊垫引出的线路从保护层开口2021暴露出来。如果保护层材料是激光反应性材料,可以采用激光图形化的方式一次形成一个保护层开口2021的方式开孔;如果保护层材料是光敏材料,则可以采用光刻图形化方式,一次形成多个保护

层开口2021的开孔方式。保护层开口2021的形状可以是圆的,当然也可以是其他形状如椭圆形、方形、线形等。

115.如图2(j)所示,形成保护层开口2021之后,在所述保护层202上进行再布线,即形成第一再布线层206。本实施例中,待封装芯片201正面具有芯片内部电路的焊垫,通过在待封装芯片201正面上进行再布线,可以将这些焊垫引出。

116.在一实施例中,如图2(j)所示,第一再布线层206形成在保护层202的表面上,采用导电材料制成,例如铜等金属。第一再布线层206包括填充在保护层开口2021的连接部2061以及形成在保护层202表面的图形化线路2062,连接部2061与待封装芯片201表面的焊垫形成电连接,且图形化线路2062与连接部2061形成电连接。

117.在另一实施例中,如果保护层202上已经形成了保护层开口2021,则剥离所述第一载板,暴露出所述保护层之后,还包括:在所述保护层上形成第一再布线层206,第一再布线层206的导电材料填充至保护层开口2021中,使所述第一再布线层通过所述保护层开口与所述待封装芯片上的焊垫电连接。

118.在将形成有保护层202的待封装芯片贴装于第一载板200之前,如果在保护层202上已经先形成了保护层开口2021,且在保护层开口2021中填充了导电介质的情况下,可以直接在保护层202上进行再布线,即形成第一再布线层205。

119.在传统工艺中,由于待封装芯片正面是裸露的,因此形成再布线层之前,需要在待封装芯片正面形成钝化层,并对钝化层进行开孔之后再形成再布线层,而本公开的上述方式,通过在待封装芯片201正面形成保护层202,不但能够保护待封装芯片201在后续工艺中不被破坏,还能够省却钝化层的制作步骤,大大节省了制作成本。

120.当然,在另一种实施方式中,形成再布线层时,如果需要表面是完整的同一材料的话,还是可以在保护层202上形成一层钝化层401,如图4(a)所示;之后在钝化层表面形成保护层开口2021,保护层开口2021贯穿钝化层401、保护层202,并对应于芯片正面的焊垫,如图4(b)所示;之后形成第一再布线层206,第一再布线层206的导电材料填充至保护层开口2021中,形成连接结构2061,如图4(c)所示。

121.在一实施例中,在保护层上形成第一再布线层之后,还包括:在所述第一再布线层上形成第二包封层,并通过第一导电凸柱引出所述第一再布线层的焊垫或连接点。在一实施例中,如图2(k)所示,形成第一再布线层206之后,利用第二包封层207对其进行封装。在封装完成后,第一再布线层206上的焊垫通过第一导电凸柱208(例如金属柱或外突焊垫等)从第二包封层207表面引出。第一导电凸柱208的形状可以是圆的,当然也可以是其他形状如椭圆形、方形、线形等。

122.在一实施例中,如果在保护层202上已经形成有保护层开口2021和/或连接结构2022的情况下,在形成第一布线层206时,可以直接看到保护层开口2021和/或连接结构2022,因此形成第一布线层206时能够更加准确的对位。

123.在一实施例中,形成有钝化层的实施方式中,形成第一导电凸柱208以及第二包封层207的结构如图4(d)和图4(e)所示。

124.在一实施例中,在所述第一再布线层上形成第二包封层,并通过第一导电凸柱引出所述第一再布线层的焊垫或连接点,包括:在所述第一再布线层的焊垫或连接点上形成第一导电凸柱;在所述第一再布线层以及露出的保护层上形成第二包封层,并露出所述第

一导电凸柱。例如,如图2(l)所示,在第一再布线层206的图形化线路上通过光刻和电镀方式形成第一导电凸柱208,之后再如图2(k)所示形成第二包封层207。

125.在另一实施例中,在所述第一再布线层上形成第二包封层,并通过第一导电凸柱引出所述第一再布线层的焊垫或连接点,包括:在所述第一再布线层上形成第二包封层;在所述第二包封层上与所述第一再布线层的焊垫或连接点对应的位置处形成第一开口;在所述第一开口内形成第一导电凸柱。例如,如图2(m)所示,可以在第一再布线层206上形成第二包封层207,之后在第二包封层207上通过开孔形成第一开口2071,并在第一开口2071中填充导电材料形成第一导电凸柱208。又一实施例中,第一开口2071可不被填充,使完成后的封装体的第一再布线层的焊垫或连接点从第一开口2071中露出。

126.第一导电凸柱208的形状优选为圆形,当然也可以是长方形、正方形等其他形状,且导电凸柱208与第一再布线层电连接。

127.在一实施例中,第二包封层207可通过层压(lamination)、成型(molding)或印刷(printing)的方式形成,优选采用环氧化合物。第二包封层207覆盖在第一再线层206上,第一再布线层206通过第一导电凸柱208从第二包封层207表面露出。通过先形成第一导电凸柱208,再形成第二包封层207的方式包封时,可以将第二包封层207覆盖住第一包封层204、保护层202和第一再布线层206上的所有露出表面,之后再减薄至第一导电凸柱208的表面。

128.在一实施例中,在多个待封装芯片201一起封装的情况,完成第一再布线层的封装后,通过激光或机械切割方式将整个封装结构切割成多个封装体,如图2(n)所示,形成的封装体的结构图如图7所示。而在保护层表面形成有钝化层情形下,完成第一再布线层的封装后,通过激光或机械切割方式将整个封装结构切割成多个封装体的结构如图4(f)所示。

129.在另一实施例中,在所述至少一个待封装芯片的正面通过重布线工艺完成封装还包括:

130.在第二包封层上形成第二再布线层,所述第二再布线层通过所述第一导电凸柱与所述第一再布线层的焊垫或连接点电连接;

131.在第二再布线层上形成第三包封层,并通过第二导电凸柱引出所述第二再布线层的焊垫或连接点。

132.本一实施例中,如图2(o)所示,在第二包封层207上形成第二再布线层209,第一再布线层206上的焊垫与第二再布线层209通过第一导电凸柱208电连接,而第二再布线层209上的焊垫通过第二导电凸柱211引出,并且第二再布线层209以及露出的第二包封层207由第三包封层210覆盖,第二导电凸柱211通过第三包封层210上的第二开口引出第二再布线层209上的焊垫或连接点。通过这种方式,可以实现多层封装结构。形成的多层封装体的结构图如图12所示。而在保护层202表面形成有钝化层的情形下,形成第二再布线层209后的结构如图4(g)所示。

133.在一实施例中,形成第三包封层,用于包封所述第二再布线层以及露出的第二包封层,并通过第二导电凸柱引出所述第二再布线层的焊垫或连接点,包括:在所述第二再布线层的焊垫或连接点上形成第二导电凸柱;在所述第二再布线层以及露出的第二包封层上形成第三包封层,并露出所述第二导电凸柱。在另一实施例中,形成第三包封层,包封所述第二再布线层以及露出的第二包封层,并通过第二导电凸柱引出所述第二再布线层的焊垫或连接点,包括:在所述第二再布线层以及露出的第二包封层上形成第三包封层;在所述第

三包封层上与所述第二再布线层的焊垫或连接点对应的位置处形成第二开口;在所述第二开口内形成第二导电凸柱。

134.第二再布线层的形成方式与第一再布线层的形成方式类似,可以在第二再布线层形成后,在第二再布线层上形成第二导电凸柱,之后再形成第三包封层,并通过相应工艺漏出所述第二导电凸柱,使得第二导电凸柱能够将所述第二再布线层上的焊垫或连接点引出;还可以先在第二再布线层上形成第三包封层,然后在第三包封层上形成第二开口,并在第二开口中形成第二导电凸柱,使得第二导电凸柱能够与第二再布线层上的焊垫或连接点电连接。具体细节可参见上述对第一再布线层的描述,在此不再赘述。

135.根据本公开一实施例,上述芯片封装方法中,在步骤102之后,还包括:形成密封层,所述密封层至少包裹在所述至少一个待封装芯片的四周。

136.如图5(a)所示,密封层205形成在待封装芯片背面和露出的粘接层203上,从而将待封装芯片201包裹起来。在一实施例中,密封层205可采用聚合物绝缘材料液体或糊状体,可通过喷涂(spraying)、印刷(printing)、涂覆(coating)等方式形成,且密封层205的厚度小于待封装芯片201的厚度。可选地,在一实施例中,可以将形成在待封装芯片201背面的密封层205去除。例如可采用板子、带子等物体将待封装芯片201背面的多余密封层材料粘除,减小后续形成的第一包封层的厚度,进而减小最终封装体的厚度。

137.在实际操作过程中,聚合物绝缘材料较佳为液体或者糊状,因此在喷涂完成后,会流向待封装芯片201的四周,覆盖任何空隙,达到厚度均匀,并在通过固化方式固化后,可以使得密封层205包裹住待封装芯片201,以锁止待封装芯片201的位置固定不变,如图5(a)所示。密封层205的形状主要取决于密封层材料的粘性、张力等特性。当然,在其他实施例中,密封层205还可以通过注射(dispensing)等方式,通过空气或机械产生的压力将密封层材料注入到待封装芯片之间的粘接层203上,使密封层材料不会覆盖待封装芯片201背面,如图5(b)所示。密封层材料须采用固化材料,并以高温或紫外线等方式进行固化。本公开上述实施例,通过密封层205包裹住待封装芯片201的四周,可避免待封装芯片201在后续工艺中发生位移后,导致由于无法预估发生移位后的待封装芯片201的位置而造成再布线层与待封装芯片201正面的焊垫无法电连接等的情形。

138.密封层205在形成时,覆盖整个载板200的表面,密封层205连续不间断的形成在所述第一包封层上表面以及至少包裹在所述待封装芯片的四周;载板200剥落之后,暴露出来的表面是保护层202和密封层205的表面。在一实现方式中,可以选择与保护层202相匹配的密封层材料,即保护层材料和密封层材料的膨胀系数、弹性模数等特性较为相近,使得形成第一布线层206形成在两种材料上之后,不会因为材料特性的不同,而影响布线。可选地,保护层材料和密封层材料可以采用同一种材料。另外,在上述实施例中,可以通过形成了密封层205和保护层202,更可以减少对钝化层的依赖。

139.在该实施例中,形成密封层205之后,对应于上述步骤103,形成第一包封层204;这种方式下,第一包封层204形成在密封层205的表面,或者密封层205及待封装芯片201背面(如果将芯片背面的密封层材料先去除了),如图5(c)所示。第一包封层204的形成方式以及材料等细节具体见对步骤103的描述,在此不再赘述。

140.该实施例中,形成第一包封层204之后,对应于上述步骤104,剥离载板200,露出所述保护层,如图5(d)所示。之后在保护层202上形成保护层开口2021,如图5(e)所示。之后再

形成第一布线层206,第一布线层206形成在保护层203的表面,布线层材料同时填充至保护层开口2021中,形成连接结构2061,如图5(f)所示;之后在第一布线层206上形成第一导电凸柱208以及第二包封层207,第一导电凸柱208用于将第一布线层206引至第二包封层207的表面,如图5(g)和5(h)所示。在仅需要单层布线的结构中,可以通过切割得到多个封装体,如图5(i)所示。切割之后,每个封装体的结构如图9所示。

141.如果需要进一步再布线的话,可以在第二包封层207上形成第二再布线层209,第二再布线层209通过第一导电凸柱208与第一再布线层206电连接,如图5(j)所示。上述步骤的具体细节可参见上述在步骤104之后对再布线的过程的详细描述,在此不再赘述。

142.在一实施例中,在第一载板200上形成粘接层203之后,在粘接层203上还可以贴装被动元件,被动元件贴装于第一载板200的预定位置处,使得被动元件位于邻近待封装元件的位置处。被动元件的背面朝向第一包封层,在形成第一再布线层206之后,被动元件的正面与第一再布线层电连接。

143.图6是根据本公开一示例性实施例提供的利用上述芯片封装方法得到的芯片封装结构的结构示意图。如图6所示,芯片封装结构包括:

144.第一包封层204,该第一包封层204上设置有至少一个内凹的第一腔体;

145.芯片201,位于所述第一腔体内,所述至少一个待封装芯片201的背面超向所述第一包封层204;

146.保护层202,形成于所述芯片201的正面,且所述保护层202上形成有保护层开口2021,所述保护层开口2021位于所述芯片201正面的焊垫对应位置处;

147.再布线结构300,形成于所述芯片201的正面,用于将所述芯片201正面的焊垫引出。

148.图7是根据本公开另一示例性实施例中芯片封装结构的结构示意图。如图7所示,芯片封装结构,包括:

149.第一包封层204,该第一包封层204上设置有至少一个内凹的第一腔体;

150.芯片201,位于所述第一腔体内,所述至少一个待封装芯片201的背面超向所述第一包封层204;

151.保护层202,形成于所述芯片201的正面,且所述保护层202上形成有保护层开口2021,所述保护层开口2021位于所述芯片201正面的焊垫对应位置处;

152.再布线结构300,包括:

153.第一再布线层206,形成于所述保护层202以及第一包封层204上,且通过所述保护层开口2021与所述芯片201的焊垫电连接;

154.第二包封层207,形成于所述第一再布线层206以及露出的第一包封层204上,且具有第一开口2071,所述第一开口2071内设置有与所述第一再布线层206电连接的第一导电凸柱208。

155.本实施例中,上述芯片封装结构可以通过上述芯片封装方法以及图2(a)~(o)所示的工艺流程得到,具体细节可参见上述对芯片封装方法以及工艺流程的详细介绍,在此不再赘述。

156.图8是根据本公开另一示例性实施例提供的利用上述芯片封装方法得到的芯片封装结构的结构示意图。如图8所示,芯片封装结构包括:

157.第一包封层204,该第一包封层204上设置有至少一个内凹的第一腔体;

158.芯片201,位于所述第一腔体内,所述至少一个待封装芯片201的背面朝向所述第一包封层204;

159.密封层205,形成于所述第一包封层204上表面以及至少包裹所述芯片201的四周;

160.保护层202,形成于所述芯片201的正面,且所述保护层202上形成有保护层开口2021,所述保护层开口2021位于所述芯片201正面的焊垫对应位置处;

161.再布线结构300,形成于所述芯片201的正面,用于将所述芯片201正面的焊垫引出。

162.图9是根据本公开另一示例性实施例中芯片封装结构的结构示意图。如图9所示,芯片封装结构,包括:

163.第一包封层204,该第一包封层204上设置有至少一个内凹的第一腔体;

164.芯片201,位于所述第一腔体内,所述至少一个待封装芯片201的背面超向所述第一包封层204;

165.密封层205,形成于所述第一包封层204上表面以及至少包裹所述芯片201的四周;

166.保护层202,形成于所述芯片201的正面,且所述保护层202上形成有保护层开口2021,所述保护层开口2021位于所述芯片201正面的焊垫对应位置处;

167.再布线结构300,包括:

168.第一再布线层206,形成于所述保护层202以及密封层205上,且通过所述保护层开口2021与所述芯片201的焊垫电连接;

169.第二包封层207,形成于所述第一再布线层206以及露出的密封层205上,且具有第一开口2071,所述第一开口2071内设置有与所述第一再布线层206电连接的第一导电凸柱208。

170.本实施例中,上述芯片封装结构可以通过上述芯片封装方法以及图2(a)~(o)所示的工艺流程得到,具体细节可参见上述对芯片封装方法以及工艺流程的详细介绍,在此不再赘述。

171.图10是根据本公开一示例性实施例提供的利用上述芯片封装方法得到的芯片封装结构的结构示意图。如图10所示,芯片封装结构包括:

172.第一包封层204,该第一包封层204上设置有至少一个内凹的第一腔体;

173.芯片201,位于所述第一腔体内,所述至少一个待封装芯片201的背面超向所述第一包封层204;

174.保护层202,形成于所述芯片201的正面,且所述保护层202上形成有保护层开口2021,所述保护层开口2021位于所述芯片201正面的焊垫对应位置处;

175.再布线结构300,包括:

176.钝化层401,形成在所述保护层202以及第一包封层204上;

177.第一再布线层206,形成于所述钝化层401上,且通过所述保护层开口2021与所述芯片201的焊垫电连接;

178.第二包封层207,形成于所述第一再布线层206以及露出的第一包封层204上,且具有第一开口2071,所述第一开口2071内设置有与所述第一再布线层206电连接的第一导电凸柱208。

179.本实施例中,上述芯片封装结构可以通过上述芯片封装方法以及图4(a)~(g)所示的工艺流程得到,具体细节可参见上述对芯片封装方法以及工艺流程的详细介绍,在此不再赘述。

180.图11是根据本公开一示例性实施例中芯片封装结构的结构示意图。如图11所示,芯片封装结构,包括:

181.第一包封层204,该第一包封层204上设置有至少一个内凹的第一腔体;

182.芯片201,位于所述第一腔体内,所述至少一个待封装芯片201的背面超向所述第一包封层204;

183.密封层205,形成于所述第一包封层204上表面以及至少包裹在所述芯片201的四周;

184.保护层202,形成于所述芯片201的正面,且所述保护层202上形成有保护层开口2021,所述保护层开口2021位于所述芯片201正面的焊垫对应位置处;

185.再布线结构300,包括:

186.钝化层401,形成在所述保护层202以及所述密封层205上;

187.第一再布线层206,形成于所述钝化层401上,且通过所述保护层开口2021与所述芯片201的焊垫电连接;

188.第二包封层207,形成于所述第一再布线层206以及露出的密封层205上,且具有第一开口2071,所述第一开口2071内设置有与所述第一再布线层206电连接的第一导电凸柱208。

189.本实施例中,上述芯片封装结构可以通过上述芯片封装方法以及图5(a)~(j)所示的工艺流程得到,具体细节可参见上述对芯片封装方法以及工艺流程的详细介绍,在此不再赘述。

190.图12是根据本公开另一示例性实施例中芯片封装结构的再布线结构300的结构示意图。如图12所示,芯片封装结构包括:

191.第一包封层204,该第一包封层204上设置有至少一个内凹的第一腔体;

192.芯片201,位于所述第一腔体内,所述至少一个待封装芯片201的背面超向所述第一包封层204;

193.保护层202,形成于所述芯片201的正面,且所述保护层202上形成有保护层开口2021,所述保护层开口2021位于所述芯片201正面的焊垫对应位置处;

194.再布线结构300,包括:

195.第一再布线层206,形成于所述保护层202以及第一包封层204上,且通过所述保护层开口2021与所述芯片201的焊垫电连接;

196.第二包封层207,形成于所述第一再布线层206以及露出的第一包封层204上,且具有第一开口2071,所述第一开口2071内设置有与所述第一再布线层206电连接的第一导电凸柱208;

197.第二再布线层209,形成于所述第二包封层207上,且通过所述第一导电凸柱208与所述第一再布线层206的焊垫电连接;

198.第三包封层210,用于包封所述第二再布线层209以及露出的第二包封层207,并通过第二导电凸柱211引出所述第二再布线层209的焊垫。

199.本实施例的细节可参见上述芯片封装方法以及图2(a)~(o)所示的工艺流程的描述,在此不再赘述。

200.与图12所示的实施例类似,在上述图7、9、11所示的芯片封装结构中的再布线结构300也可以再包括:

201.第二再布线层,形成于所述第二包封层207上,且通过所述第一导电凸柱208与所述第一再布线层206的焊垫电连接;

202.第三包封层,用于包封所述第二再布线层209以及露出的第二包封层207,并通过第二导电凸柱引出所述第二再布线层209的焊垫。

203.具体可参见上述图2(a)~(o)、图4(a)~(g)以及图5(a)~(j)所示的结构的描述,在此不再赘述。

204.在上述图7、9、11、12所示的芯片封装结构中,也可以包括:

205.至少一个被动元件,位于所述第一包封层204上设置的至少一个内凹的第二腔体内,所述第二腔体邻近所述第一腔体设置,所述至少一个被动元件的背面朝向所述第一包封层204,所述至少一个被动元件的正面与所述第一再布线层206电连接。

206.以上所述的具体实施例,对本发明的目的、技术方案和有益效果进行了进一步详细说明,所应理解的是,以上所述仅为本发明的具体实施例而已,并不用于限制本发明,凡在本发明的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。