1.本发明涉及一种高速高精度模数转换器片间同步性能检测系统及方法,属于模数转换器技术领域。

背景技术:

2.随着集成电路技术、通信技术的快速发展,大大促进了模数转换器技术的发展和应用。流水线结构是高速高精度模数转换器的主流设计结构,具有线性度高,低功率、低失调、瞬态响应速度快等特点,被广泛应用于对无杂散动态范围、总谐波等频域特性要求较高的通讯系统,对噪声、带宽等时域特性要求较高的成像系统,以及对时域和频域特性都要求较高的数据采集系统。

3.在图像检测、相控阵雷达、电子对抗等需要多通道同步数据采集的应用领域中,采用单片多通道高速高精度模数转换器搭建系统已是非常成熟的设计思路,但随着应用系统通道数的逐步增加、集成度的逐步提升,该设计思路已无法满足需求。采用多片高速高精度模数转换器同步采集的方案搭建大阵列、高集成化系统是目前应用最多的技术,但多片高速高精度模数转换器同步采集应用必然会对片间通道一致性设计提出挑战。

4.通过对高速高精度模数转换器片间同步性能的检测与筛选,可以在系统设计初期降低板级设计复杂性、不确定性。同时,掌握多芯片间的相位差数据可以在系统设计的软件编程阶段进一步准确地进行相位补偿。因此,高速高精度模数转换器的众多用户对转换器提出了更高要求的检测与筛选需求。

技术实现要素:

5.本发明的技术解决问题是:克服现有技术的不足,提供一种高速高精度模数转换器片间同步性能检测系统及方法,能够根据指定的工程实际需求条件完成同批次高速高精度模数转换器芯片同步性能检测、筛选分拣工作。

6.本发明的技术解决方案是:

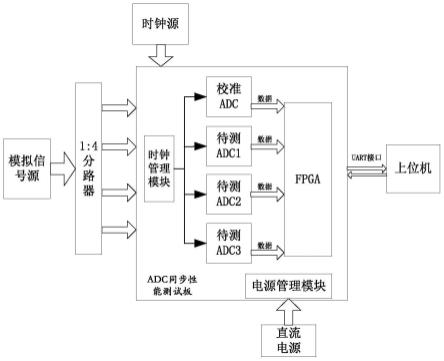

7.一种高速高精度模数转换器片间同步性能检测系统,包括fpga模块、校准adc芯片、待测adc芯片、时钟管理模块、电源管理模块、直流电源、模拟信号源、时钟源以及上位机;

8.直流电源用于给电源管理模块提供12v直流电压,电源管理模块再将12v电压转换成其他模块所需的工作电压;

9.模拟信号源用于为校准adc芯片及待测adc提供模拟输入信号;

10.时钟源用于为时钟管理模块提供输入时钟;

11.时钟管理模块用于接收输入时钟并产生4路同步时钟提供给校准adc芯片及待测adc芯片;

12.fpga模块用于接收上位机发送的采集控制信号,完成校准adc芯片和待测adc芯片的波形数据的同步采集,并通过uart接口上传至上位机;

13.上位机用于对波形数据进行fft及相位计算,记录信噪比参数值snr及其与校准adc芯片之间的相位差tδ,并使之与芯片编号一一对应,同时,上位机还用于待整批次芯片测试完毕后,对由snr与tδ组成的二维数据点集合进行聚类分析,完成筛选检测。

14.进一步的,还包括分路器,模拟信号源产生的输入信号通过分路器分为n路,分别输入到一个校准adc芯片以及n-1个待测adc芯片中,n为正整数。

15.进一步的,校准adc芯片及待测adc芯片为同批次的高速高精度流水线型adc芯片。

16.进一步的,所述校准adc芯片是从同批次芯片中随机选择,用于标定本批次内所有待测adc芯片与该校准adc芯片之间的相位差,用于形成相位差数据集合。

17.进一步的,所述上位机通过完成聚类分析确定二维数据点集合的最终聚类中心,再结合指定的工程实际需求条件,输出需分拣的芯片编号。

18.进一步的,所述进行聚类分析,具体包括:

19.(1)将在同一批次芯片中随机选取的校准adc芯片作为初始聚类中心k1’;

20.(2)通过计算所有数据对象与k1’的距离,将距离聚类中心最大的数据对象作为初始聚类中心k2’;

21.(3)再分别计算所有数据对象到k1’与k2’的距离,将数据对象划归至距离较近的聚类中心所在的簇内,最终形成两个大簇;

22.(4)对新形成的簇重新计算确定新的聚类中心;

23.(5)重复进行步骤(3)和步骤(4)过程,直至聚类中心不再更新,确定最终的聚类中心k1与k2。

24.进一步的,本发明还提出一种模数转换器片间同步性能检测方法,包括如下步骤:

25.步骤一:在同批次芯片中随机选择一颗芯片作为校准adc芯片,将校准adc芯片与待测adc芯片安装在测试板测试工位上,系统上电;

26.步骤二:上位机发送采集控制信号,fpga模块接收到控制信号后完成对校准adc芯片与待测adc芯片的波形数据的同步采集,并上传至上位机;

27.步骤三:上位机对接收到的波形数据进行fft及相位计算,记录各转换器信噪比参数值snr及其与校准adc之间的相位差tδ,并使之与芯片编号一一对应;

28.步骤四:更换所有待测adc芯片,重复进行步骤二、步骤三,直至本批次芯片全部测试完,形成全部芯片的snr与tδ组成的二维数据点集合;

29.步骤五:操作上位机对二维数据点集合进行聚类分析,具体包括:

30.(1)将在同一批次芯片中随机选取的校准adc芯片作为初始聚类中心k1’;

31.(2)通过计算所有数据对象与k1’的距离,将距离聚类中心最大的数据对象作为初始聚类中心k2’;

32.(3)再分别计算所有数据对象到k1’与k2’的距离,将数据对象划归至距离较近的聚类中心所在的簇内,最终形成两个大簇;

33.(4)对新形成的簇重新计算确定新的聚类中心;

34.(5)重复进行步骤(3)和步骤(4)过程,直至聚类中心不再更新,确定最终的聚类中心k1与k2。

35.步骤六:给上位机输入指定的工程实际需求的相位差距离值d和snr最小值,计算筛选出符合要求的二维数据点,在依据编号对应关系,输出需分拣的芯片编号。

36.本发明相对现有技术带来的有益效果为:

37.(1)转换器芯片在传统生产测试流程中主要专注于单芯片的全流程测试,很少会关注芯片间的同步性能指标,本发明填补了高速高精度模数转换器片间同步性能检测方向的空白。

38.(2)不同的工程应用存在不同的同步性能及动态性能需求,本发明只需将指定的工程指标输入上位机即可完成需分拣电路的编号的输出,具有很强地适用性和操作便捷性,适用于大批量adc芯片的特定条件筛选工作,大大提高了生产效率。

39.(3)由上位机输出芯片编号及片间相位差反馈至芯片用户端,芯片用户可以借助此数据在应用芯片时进一步准确地进行相位补偿,大大缩短用户工程的开发周期。

附图说明

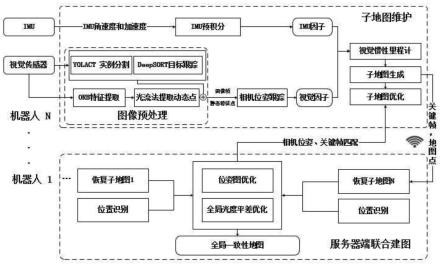

40.图1是本发明高速高精度模数转换器片间同步性能检测系统框图。

41.图2是所述系统的上位机操作面板示意图。

42.图3是所述系统的同步性能及动态性能测试工作流程图。

43.图4是所述系统上位机聚类分析过程示意图。

具体实施方式

44.下面结合实施例和附图对本发明做出进一步详细说明。

45.本发明提出一种高速高精度模数转换器片间同步性能检测系统。电源模块、时钟管理模块、直流电源、时钟源、模拟信号源用于提供系统正常工作的基础,核心在于fpga模块接收上位机发送的采集控制信号,开始控制四片adc同时采集同步输入的模拟正弦信号,采集完成后将波形数据通过uart口上传至上位机,上位机对波形数据进行fft及相位计算,记录各转换器信噪比参数值(snr)及其与校准adc之间的相位差(tδ)并使之与芯片编号一一对应,待整批次芯片测试完毕后,对由snr与tδ组成的二维数据点集合进行聚类分析;分析数据集合结束后可确定二维数据点集合的最终聚类中心k1与k2,再根据工程实际需求确定相位差距离值d(如20ps)和snr最小值,计算筛选出与最终聚类中心k1距离小于d且snr高于最小值要求的二维数据点,再通过二维数据点与芯片编号一一对应的关系从整个批次中进行分拣,最终获得两个子批次,每个子批次内的芯片同步性能及snr指标均能满足指定的工程实际需求,至此系统完成检测工作。

46.具体的,如图1所示,本发明提出的一种高速高精度模数转换器片间同步性能检测系统,该系统包括fpga模块、校准adc芯片、待测adc芯片、时钟管理模块、电源管理模块、直流电源、模拟信号源、时钟源、上位机。

47.直流电源用于给电源管理模块提供12v直流电压,电源管理模块再将12v电压转换成其他模块所需的工作电压;

48.模拟信号源用于为校准adc芯片及待测adc提供模拟输入信号;

49.时钟源用于为时钟管理模块提供输入时钟;

50.时钟管理模块用于接收输入时钟并产生4路同步时钟提供给校准adc芯片及待测adc芯片;

51.fpga模块用于接收上位机发送的采集控制信号,完成校准adc芯片和待测adc芯片

的波形数据的同步采集,并通过uart接口上传至上位机;

52.上位机用于对波形数据进行fft及相位计算,记录信噪比参数值snr及其与校准adc芯片之间的相位差tδ,并使之与芯片编号一一对应,同时,上位机还用于待整批次芯片测试完毕后,对由snr与tδ组成的二维数据点集合进行聚类分析,完成筛选检测。

53.优选的,本发明还包括分路器,模拟信号源产生的输入信号通过分路器分为n路,分别输入到一个校准adc芯片以及n-1个待测adc芯片中,n为正整数。

54.校准adc芯片及待测adc芯片为同批次的高速高精度流水线型adc芯片。所述校准adc芯片是从同批次芯片中随机选择,用于标定本批次内所有待测adc芯片与该校准adc芯片之间的相位差,用于形成相位差数据集合。

55.所述上位机通过完成聚类分析确定二维数据点集合的最终聚类中心,再结合指定的工程实际需求条件,输出需分拣的芯片编号。

56.本发明还提出一种模数转换器片间同步性能检测方法,包括如下步骤:

57.步骤一:在同批次芯片中随机选择一颗芯片作为校准adc芯片,将校准adc芯片与待测adc芯片安装在测试板测试工位上,系统上电;

58.步骤二:上位机发送采集控制信号,fpga模块接收到控制信号后完成对校准adc芯片与待测adc芯片的波形数据的同步采集,并上传至上位机;

59.步骤三:上位机对接收到的波形数据进行fft及相位计算,记录各转换器信噪比参数值snr及其与校准adc之间的相位差tδ,并使之与芯片编号一一对应;

60.步骤四:更换所有待测adc芯片,重复进行步骤二、步骤三,直至本批次芯片全部测试完,形成全部芯片的snr与tδ组成的二维数据点集合;

61.步骤五:操作上位机对二维数据点集合进行聚类分析,具体包括:

62.(1)将在同一批次芯片中随机选取的校准adc芯片作为初始聚类中心k1’;

63.(2)通过计算所有数据对象与k1’的距离,将距离聚类中心最大的数据对象作为初始聚类中心k2’;

64.(3)再分别计算所有数据对象到k1’与k2’的距离,将数据对象划归至距离较近的聚类中心所在的簇内,最终形成两个大簇;

65.(4)对新形成的簇重新计算确定新的聚类中心;

66.(5)重复进行步骤(3)和步骤(4)过程,直至聚类中心不再更新,确定最终的聚类中心k1与k2。

67.步骤六:给上位机输入指定的工程实际需求的相位差距离值d和snr最小值,计算筛选出符合要求的二维数据点,在依据编号对应关系,输出需分拣的芯片编号。

68.实施例:

69.如图1所示,本实施例提供的一种高速高精度模数转换器片间同步性能检测系统,包括fpga模块、校准adc及待测adc、时钟管理模块、电源管理模块、直流电源、模拟信号源、时钟源、上位机。

70.直流电源与电源模块负责提供系统工作电压,模拟信号源用于通过1:4分路器提供四路同步模拟输入信号,时钟源与时钟模块用于提供4路同步时钟;fpga模块完成adc的波形数据的同步采集、上传,上位机负责系统控制及计算分析。将校准adc及待测adc置于测试板上,系统上电后,fpga模块对时钟模块与adc的控制寄存器进行初始化配置,然后检测

adc数据时钟dco是否工作正常并反馈至上位机软件;上位机接收到正常工作反馈信号后向fpga模块发送采集控制信号,fpga接收控制信号后采集数据并上传;数据上传结束后,上位机对数据进行fft、相位差计算,记录测试结果完成单次测试工作;每次更换3只待测adc进行测试,将同批次芯片测试完毕后,形成测试数据集合,在通过上位机内置算法对数据合集进行聚类分析,再结合实际的工程需求输出筛选数据,检测人员在根据筛选数据对应的芯片编号完成两个子批次芯片分拣、筛选检测工作。

71.图2所示系统上位机软件的示意图。上位机端口指示灯点亮表明与测试板建立了正常通信,待接收到adc数据时钟dco反馈灯点亮表示可以开始采集;点击采集计算按钮,开始采集上传波形数据,计算结果显示于上位机面板上,便于实时观察系统工作状态;待全部芯片测试完毕后,点击聚类分析按钮对数据合集进行分析;输入工程实际指标要求,完成数据筛选并显示与面板,可通过结果导出按钮将最终结果记录导出至文档,方便完成分拣工作或提供跟芯片用户。

72.图3是同步性能及动态性能测试工作流程图,图4(a)-(f)是上位机聚类分析过程示意图,结合图3、图4可更直观的理解本发明提供的一种高速高精度模数转换器片间同步性能检测系统的整个工作流程,包括如下步骤:

73.系统上电后,进行初始化配置;

74.fpga检测adc数据时钟dco是否正常,若不正常则返回至初始化配置过程,若正常则将正常信号反馈至上位机并等待采集控制指令;

75.上位机在接收到数据时钟dco正常信号后,发送开始采集控制指令给fpga,fpga接收控制指令开始采集波形数据并上传;

76.上位机接收数据后计算得出波形数据的信噪比snr与相位差tδ指标数据,将数据记录完成单次测试;

77.待整个批次芯片完成测试后,上位机对数据集合进行聚类分析,图4(a)-(f)示意了数据集合的聚类分析过程;再结合输入的工程实际指标要求,完成两个子批次电路的筛选检测工作。

78.本发明说明书中未作详细描述的内容属本领域专业技术人员的公知技术。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。