一种100mhz-20ghz高性能低噪声放大器芯片

技术领域

1.本实用新型属于无线通信技术领域,尤其涉及一种100mhz-20ghz高性能低噪声放大器芯片。

背景技术:

2.随着当今社会信息化的快速发展,无线通信技术已经被社会广泛使用,而无线通信领域的高速发展主要体现在宽带化,高速化上。为了解决当今频带资源匮乏的问题,需要利用超宽带元器件。超宽带元器件因为抗干扰性能强、带宽极宽、频谱利用率高,成为实现无线个人局域网富有竞争力的产品之一,具有广阔的发展前景。

3.低噪声放大器lna(low noise amplifier)是现代微波/毫米波通信、雷达、电子对抗及遥测遥控接收系统等应用中的一个关键部件,常在接收系统的前端使用,但如何保证低噪声放大器的高性能稳定是一个难题。

技术实现要素:

4.本实用新型提供一种100mhz-20ghz高性能低噪声放大器芯片,旨在解决上述存在的问题。

5.本实用新型是这样实现的,一种100mhz-20ghz高性能低噪声放大器芯片,包括芯片,所述芯片上设置有漏端偏置电路、栅端偏置电路、七个并联放大单元组成的行波式放大结构、输入相移线、输出相移线和电流稳定单元;

6.所述行波式放大结构的第一级放大单元和第七级放大单元分别与所述漏端偏置电路和栅端偏置电路电性连接,每级放大单元之间通过输入相移线和输出相移线电性连接;所述放大单元包括两个采用共源共栅结构连接的晶体管,其中,每级所述放大单元的输出端连接漏极线并通过输出相移线至射频输出端口,所述电流稳定单元电性连接在漏极线上。

7.进一步的,所述漏端偏置电路包括电容1c、2c、电阻1r、2r、3r,其中,电容1c为低频滤波电容,电容2c为高频滤波电容,电阻1r连接在地与电容1c之间,电阻2r连接在地与电容2c之间,电阻3r串联在漏极线上。

8.进一步的,所述栅端偏置电路包括电容3c、4c、电阻4r、5r、6r,其中,电容3c为低频去耦电容,电容4c为高频滤波电容,电阻4r连接在地与电容3c之间,电阻5r连接在地与电容4c之间,电阻6r串联在栅极线上。

9.进一步的,每级所述放大单元包括两个栅宽为60um的晶体管q1-q14和一个接地电容5c-11c,其中,晶体管q1、q3、q5、q7、q9、q11、q13的漏极分别与q2、q4、q6、q8、q10、q12、q14的源极相连。

10.进一步的,所述晶体管q2、q4、q6、q8、q10、q12、q14的漏极连接漏极线并通过输出相移线至射频输出端口。

11.进一步的,所述晶体管q1、q3、q5、q7、q9、q11、q13的源极接地,所述晶体管q1、q3、

q5、q7、q9、q11、q13的栅极连接栅端偏置电路并通过输入相移线至射频输入端口。

12.进一步的,所述电流稳定单元包括晶体管q15,晶体管q2、q4、q6、q8、q10、q12、q14的栅极与晶体管q15的栅极和漏极连接,晶体管q15的栅极通过电阻接地,晶体管q2、q4、q6、q8、q10、q12、q14的栅极还与接地电容5c、6c、7c、8c、9c、10c、11c相连接。

13.所述芯片的射频输入输出上需要加隔直电容元件,并使用无拐角的不同线宽的微带线和工艺为250nm砷化镓基中的电容电阻来匹配各级中间电路。

14.与现有技术相比,本实用新型的有益效果是:本实用新型提供一种100mhz-20ghz高性能低噪声放大器芯片,采用特殊的偏置网络,漏极线上连接有晶体管q15组成的电流稳定结构以保证芯片在高低温时芯片性能有微弱变动,晶体管栅极与漏极连接并给放大单元中第二级晶体管q2、q4、q6、q8、q10、q12、q14提供栅压,晶体管q15的栅极通过电阻接地;通过共源共栅结构和行波式结构的配合使用达到增加带宽的作用。

附图说明

15.图1为本实用新型结构示意图;

16.图2为本实用新型的漏端偏置结构示意图;

17.图3为本实用新型的栅端偏置结构示意图;

18.图4为本实用新型的行波式放大结构示意图;

19.图5为本实用新型的电流稳定结构示意图;

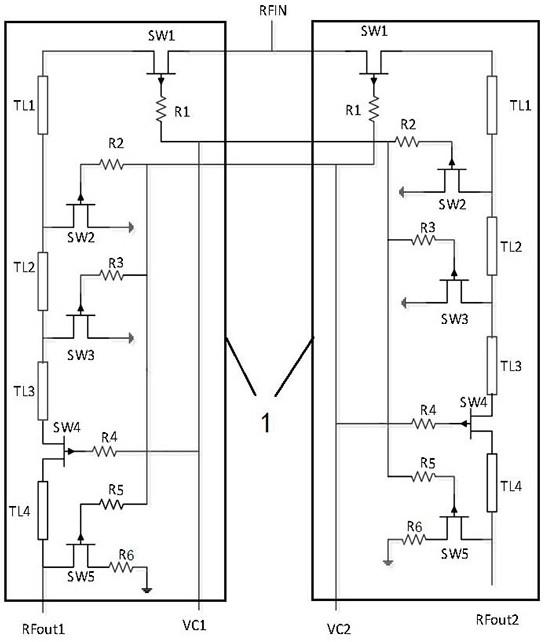

20.图6为本实用新型输入相移线结构图;

21.图7为本实用新型输出相移线结构图。

具体实施方式

22.为了使本实用新型的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本实用新型进行进一步详细说明。应当理解,此处所描述的具体实施例仅仅用以解释本实用新型,并不用于限定本实用新型。

23.在本实用新型的描述中,需要理解的是,术语“长度”、“宽度”、“上”、“下”、“前”、“后”、“左”、“右”、“竖直”、“水平”、“顶”、“底”“内”、“外”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本实用新型和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本实用新型的限制。此外,在本实用新型的描述中,“多个”的含义是两个或两个以上,除非另有明确具体的限定。

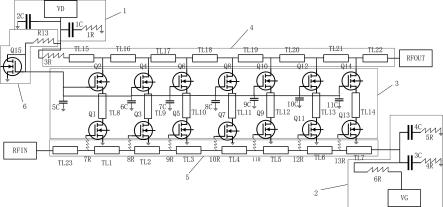

24.如图1所示,一种100mhz到20 ghz高性能低噪声放大器芯片,所述芯片为行波式共源共栅的结构,电路整体尺寸为2800

×

1600

×

100μm,芯片上设有漏端偏置电路1、栅端偏置电路2、七个并联放大单元组成的行波式放大结构3、输入相移线5、输出相移线4、电流稳定单元6;

25.其中,漏端偏置电路1包括电容1c、2c、电阻1r、2r、3r,其中,电容1c为低频滤波电容,电容2c为高频滤波电容,电阻1r连接在地与电容1c之间,电阻2r连接在地与电容2c之间,电阻3r串联在漏极线上;但是在图1和图2中,电阻2r未示出,电阻3r置于输出相移线4中。

26.如图2-图7所示,电容1c、2c,电阻1r构成漏端偏置电路1。

27.电容3c,4c,电阻4r、5r、6r构成栅端偏置电路2。

28.晶体管q1、q2,微带线tl8,接地电容5c构成第一放大单元。

29.晶体管q3、q4,微带线tl9,接地电容6c构成第二放大单元。

30.晶体管q5、q6,微带线tl10,接地电容7c构成第三放大单元。

31.晶体管q7、q8,微带线tl11,接地电容8c构成第四放大单元。

32.晶体管q9、q10,微带线tl12,接地电容9c构成第五放大单元。

33.晶体管q11、q12,微带线tl13,接地电容10c构成第六放大单元。

34.晶体管q13、q14,微带线tl14,接地电容11c构成第七放大单元。

35.输入相移线5由微带线tl23、tl1、tl2、tl3、tl4、tl5、tl6 、tl7构成。

36.输出相移线4由电阻3r,微带线tl15、微带线tl16、微带线tl17、微带线tl18、微带线tl19、微带线tl20、微带线tl21、微带线tl22构成。

37.晶体管q15和电阻13r构成电流稳定单元6。

38.如图2所示,vd为芯片内部的直流焊盘,尺寸为100um

×

100um;漏端直流馈电线上有接地电容1c,容值大小为26pf,用于滤除低频信号;电容2c容值为1pf,在电容2c与地之间有接有电阻1r(阻值为4欧姆),用于滤除高频信号;直流馈电线另一端连接输出相移线4单元中的电阻3r和电流稳定单元6中的电阻13r。

39.如图3所示,vg为栅端供电焊盘,尺寸为100um

×

100um;从供电焊盘上接串联电阻6r,阻值为48欧姆;串联电路6r另一端接有接地电容3c和4c,其中3c容值为30pf,4c容值为1pf;3c和4c与地之间分别接有电阻阻值均为4欧姆的4r和5r;其中电容3c滤除低频信号,4c电容滤除高频信号;电阻与接地电容3c和4c连接的那一端也与输入相移线5单元中的tl7微带线相连。

40.如图4所示,放大单元中的q1-q14管芯栅宽均为60um。

41.q1的漏极与q2的源级通过微带线tl8连接,构成共源共栅结构。q1的栅极通过电阻7r与输入相移微带线tl23和tl1之间连接,q2的栅极与晶体管q15的栅极和漏极连接,q2的栅极还与接地电容5c相连接,q2的漏极连接在tl15,tl16之间。

42.q3的漏极与q4的源级通过微带线tl9连接,构成共源共栅结构。q3的栅极通过电阻8r与输入相移微带线tl1和tl2之间连接,q4的栅极与晶体管q15的栅极和漏极连接,q4的栅极还与接地电容6c相连接,q4的漏极连接在tl16,tl17之间。

43.q5的漏极与q6的源级通过微带线tl10连接,构成共源共栅结构。q5的栅极通过电阻9r与输入相移微带线tl2和tl3之间连接,q6的栅极与晶体管q15的栅极和漏极连接,q6的栅极还与接地电容7c相连接。q6的漏极连接在tl17,tl18之间。

44.q7的漏极与q8的源级通过微带线tl11连接,构成共源共栅结构。q7的栅极通过电阻10r与输入相移微带线tl3和tl4之间连接,q8的栅极与晶体管q15的栅极和漏极连接,q8的栅极还与接地电容8c相连接。q8的漏极连接在tl18,tl19之间。

45.q9的漏极与q10的源级通过微带线tl12连接,构成共源共栅结构。q9的栅极通过电阻11r与输入相移微带线tl4和tl5之间连接,q9的栅极与晶体管q15的栅极和漏极连接,q9的栅极还与接地电容9c相连接。q10的漏极连接在tl19,tl20之间。

46.q11的漏极与q12的源级通过微带线tl13连接,构成共源共栅结构。q11的栅极通过

电阻12r与输入相移微带线tl5和tl6之间连接,q12的栅极与晶体管q15的栅极和漏极连接,q12的栅极还与接地电容10c相连接。q12的漏极连接在tl20,tl21之间。

47.q13的漏极与q14的源级通过微带线tl14连接,构成共源共栅结构。q13的栅极通过电阻13r与输入相移微带线tl6和tl7之间连接,q14的栅极与晶体管q15的栅极和漏极连接,q14的栅极还与接地电容10c相连接。q14的漏极连接在tl21,tl22之间。

48.电阻7r-13r的阻值均为2欧姆。电容5c-11c的容值均相同为3.3pf。微带线tl8-tl14的微带线长度均相同为240um,宽度为12um。

49.如图5所示为电流稳定单元6,其中晶体管q15的栅宽为30um,晶体管q15的栅极与漏极连接后与晶体管q2、q4、q6、q8、q10、q12、q14的栅极相连接。

50.如图6所示,输入相移线5由tl23、tl1、tl2、tl3、tl4、tl5、tl6、tl7依次串联,其中tl1、tl2、tl3、tl4、tl5、tl6均为线宽8um,线长500um。tl23线长400um,线宽30um。tl7长度为80um,宽度为8um。

51.tl23与tl1之间连接晶体管q1的栅极。

52.tl1与tl2之间连接晶体管q3的栅极。

53.tl2与tl3之间连接晶体管q5的栅极。

54.tl3与tl4之间连接晶体管q7的栅极。

55.tl4与tl5之间连接晶体管q9的栅极。

56.tl5与tl6之间连接晶体管q11的栅极。

57.tl6与tl7之间连接晶体管q13的栅极。

58.如图7所示,输出相移线4由电阻3r、微带线tl15、微带线tl16、微带线tl17、微带线tl18、微带线tl19、微带线tl20、微带线tl21、微带线tl22依次串联。

59.其中,电阻3r阻值为45欧姆,微带线tl15-tl22线宽均为12um,tl16-tl21长度均为660um。其中微带线tl15与tl16之间连接晶体管q2的漏极。微带线tl16与tl17之间连接晶体管q4的漏极。微带线tl17与tl18之间连接晶体管q6的漏极。微带线tl18与tl19之间连接晶体管q8的漏极。微带线tl19与tl20之间连接晶体管q10的漏极。微带线tl20与tl21之间连接晶体管q12的漏极。微带线tl21与tl22之间连接晶体管q14的漏极。

60.以上仅为本实用新型的较佳实施例而已,并不用以限制本实用新型,凡在本实用新型的精神和原则之内所作的任何修改、等同替换和改进等,均应包含在本实用新型的保护范围之内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。