1.本发明涉及自旋电子材料技术邻域,具体涉及一种高阻值半导体结构及其制备方法和自旋电子器件。

背景技术:

2.自旋电子器件是一种将电子自旋作为信息载体的器件,能够实现自旋的产生,输运和探测。在后摩尔时代,由于半导体电子器件的热量耗散问题和小型化问题日益突出,具有低功耗、非易失性、高速和高集成度等优点的自旋电子器件成为了当下的研究热点。

3.在自旋电子器件中,实现自旋-电流信号的转化是器件工作过程中关键的一步。传统的自旋电子器件主要利用磁性材料实现自旋-电流的转化。近些年,一些拓扑材料,例如灰锡(α-sn),被发现具有较高的自旋-电流转化效率,因此这类材料逐渐被用于自旋电子器件方面的研究,且在自旋电子器件方面有着良好的应用前景。

4.然而,目前高质量拓扑材料层的制备也面临着一些问题。目前,用于外延法生长拓扑材料层的衬底主要是insb衬底和cdte衬底。insb衬底作为一种成熟的商业化衬底,表面质量好,处理工艺成熟,能够用于生长高质量的拓扑材料层,但是由于insb衬底电阻率低,载流子迁移率高,因此会产生分流效应,对拓扑材料层输运性质的测试和器件应用产生不理影响。cdte衬底具有更高的电阻率,能够避免分流效应,但是cdte并不是成熟的商业化衬底,表面质量较差,处理工艺也不成熟,因此得到的拓扑材料层质量也较差。因此,要将拓扑材料层用于自旋电子器件,如何在保证薄膜质量的同时减少衬底带来的分流效应是一个亟待解决的问题。

技术实现要素:

5.本发明的目的在于提供一种高阻值半导体结构,能保证其拓扑材料层质量的同时,减小衬底分流效应的影响,使得拓扑材料层能够用于优良性能的自旋电子器件。

6.为实现上述发明目的,本发明提供了一种高阻值半导体结构,包括:衬底、高阻值缓冲层和拓扑材料层,高阻值缓冲层为iii-v族半导体层,厚度为5-50 nm。

7.优选地,高阻值缓冲层的材料为in

x

ga

1-x

sb、in

x

al

1-x

sb或inas

1-x

sb

x

合金(0≤x≤1)。

8.优选地,衬底的材料选用cdyzn

1-y

te(0≤y≤1)。

9.优选地,拓扑材料层为α-sn

1-z

gez(0≤z≤0.5)。

10.优选地,拓扑材料层的厚度为0.1-200 nm。

11.本发明提供了一种基于高阻值半导体结构的自旋电子器件结构,包括上述高阻值半导体结构、位于拓扑材料层上表面的自旋注入层和位于自旋注入层/拓扑材料层界面两侧的电极。

12.优选地,自旋注入层从上到下依次为铁磁材料层,保护层。

13.本发明还提供了一种高阻值半导体结构的制备方法,包括:提供cdyzn

1-y

te衬底,

其中0≤y≤1;用原子氢或者离子溅射进行表面处理;通过分子束外延的方法在衬底上生长高阻值缓冲层,厚度为5-50 nm;将衬底温度升高至300℃以上,退火10-30 min;通过分子束外延的方法在高阻值缓冲层上生长拓扑材料层。优选地,所述高阻值缓冲层的材料为in

x

ga

1-x

sb、in

x

al

1-x

sb或inas

1-x

sb

x

合金(0≤x≤1),所述拓扑材料层为α-sn

1-z

gez(0≤z≤0.5)。

14.优选地,原子氢或离子溅射的处理时间为30-120 min。

15.优选地,生长高阻值缓冲层时衬底温度保持在300℃以下。

16.通过上述技术方案可以看出,本发明通过在拓扑材料层和衬底之间增加高阻值缓冲层,在保证拓扑材料层质量的同时,能够避免衬底的分流效应,从而使得拓扑材料层能够用于性能优良的自旋电子器件。同时,本发明的制备方法通过低温外延生长、高温退火的方式在cdyzn

1-y

te衬底上可得到高阻值缓冲层,从而为后期高质量拓扑材料层的生长提供基础。

附图说明

17.图1为本发明中高阻值半导体结构的示意图。

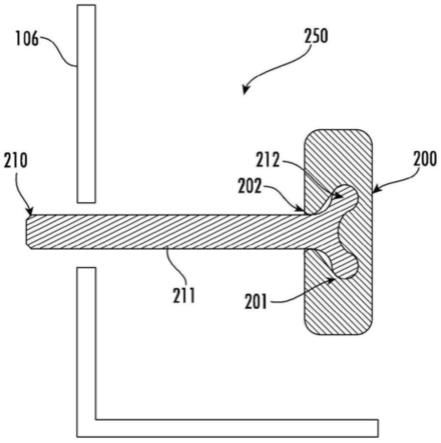

18.图2为本发明中自旋电子器件结构的示意图。

19.图3为本发明中自旋电子器件的自旋注入层的结构示意图。

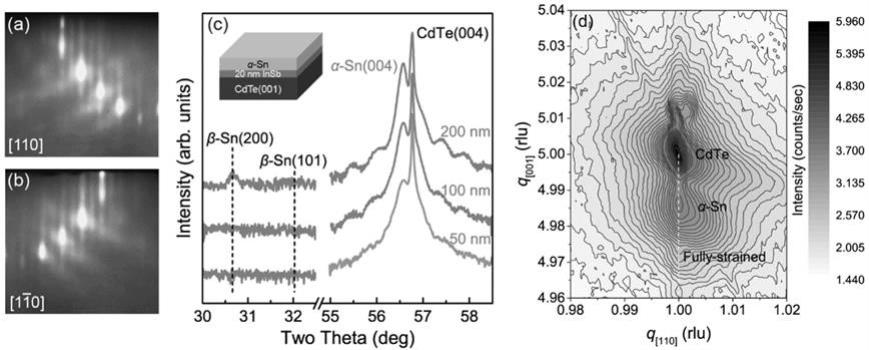

20.图4为实施例1中的结构表征结果。

21.图5为实施例1中的高阻值insb缓冲层的电学性质。

具体实施方式

22.下面结合附图和具体实施例对本发明做进一步详细说明。

23.本发明提供了一种高阻值半导体结构,如图1所示,包括:衬底1、高阻值缓冲层2、以及拓扑材料层3。其中,高阻值缓冲层为iii-v族半导体层,同时高阻值缓冲层的厚度为5-50nm。在本发明的结构中,由于高阻值缓冲层为iii-v族半导体材料,可以通过iii-v族半导体材料的合金化有效地调节晶格常数与所用拓扑材料匹配,形成更为稳定的结构;同时,超薄的高阻值缓冲层及其内部形成的纳米结构可以有效地降低载流子浓度和迁移率,实现电阻值数量级上的提升,减少分流效应的产生,形成更高质量的器件结构。优选地,高阻值缓冲层的厚度为10-30 nm。

24.在本发明中,高阻值缓冲层的材料可以是in

x

ga

1-x

sb、in

x

al

1-x

sb、inas

1-x

sb

x

(0≤x≤1)。此类材料可以通过合金化拓宽缓冲层材料的晶格常数,应用更为广泛,特别是与不同组分的α-sn

1-z

gez的晶体结构和晶格常数实现匹配,有利于提高拓扑材料的晶体质量以及相应的器件性能。除此之外,这三组材料的选择可以拓宽缓冲层材料的带隙范围,为器件结构的能带设计提供更多的选择。

25.在本发明中,衬底1为常用的高电阻率衬底,优选地,衬底的材料为cdyzn

1-y

te,其中0≤y≤1。

26.在本发明中,拓扑材料层3优选为α-sn

1-z

gez,其中,0≤z≤0.5。此类材料具有较高的自旋-电流转化效率。拓扑材料层3的厚度为0.1-200 nm。

27.本发明中高阻值半导体结构可通过将高阻值缓冲层2和拓扑材料层3采用分子束

外延方法依次在衬底1上得到。具体的,提供cdyzn

1-y

te衬底;用原子氢或离子溅射处理衬底表面;在衬底上生长高阻值缓冲层;将衬底温度升高至300℃,退火10-30 min;最后通过分子束外延的方法在高阻值缓冲层上生长拓扑材料层。在本发明中,高阻值缓冲层的材料为in

x

ga

1-x

sb、in

x

al

1-x

sb或inas

1-x

sb

x

合金(0≤x≤1),拓扑材料层为α-sn

1-z

gez(0≤z≤0.5)。在本制备方法中,低温生长后高温退火的方式可以更有效地降低载流子浓度和迁移率,进一步减少分流效应的产生。

28.在本发明中,原子氢炉或离子溅射的处理时间30-120 min,而生长高阻值缓冲层时,衬底温度保持在300℃以下。

29.本发明还提供一种基于上述高阻值半导体结构的自旋电子器件结构,如图2和图3所示,包括上述高阻值半导体结构,以及位于拓扑材料层3上方的自旋注入层4,还有位于自旋注入层4/拓扑材料层3界面两侧的电极5。其中自旋注入层4从上到下依次为铁磁材料层4-1、保护层4-2。自旋注入层用于给器件提供自旋流,其中铁磁材料层用于产生自旋流,保护层则用于保护拓扑材料层的表面,拓扑材料层则用于实现自旋-电流信号的转换。

30.在本发明中,电极材料、保护层材料和铁磁材料没有任何限制,采用本领域技术人员熟知的材料即可。在本发明中,铁磁材料可以是fe、co、ni或它们的合金,保护层材料可以是ag、al或alox。

31.实施例1(1)准备(001)晶面的cdte衬底;(2)在原子氢炉中对cdte衬底进行脱氧处理,原子氢炉的处理时间60 min;(3)采用分子束外延方法,在cdte衬底上生长insb缓冲层,生长过程中sb:in束流比为1:1,衬底温度为200℃,insb的厚度为20 nm;(4)提高衬底温度至300℃,退火10 min得到高阻值的insb缓冲层;(5)在iv族分子束外延设备中分别生长50 nm、100 nm、和200 nm的灰锡薄膜。

32.图4为上述三种不同厚度的灰锡薄膜结构表征结果。(a)和(b)展示了灰锡薄膜生长时非常清晰的(2

ꢀ×ꢀ

2)重构的线性rheed图案,(c)的xrd表征结果中明晰的灰锡(004)的衍射峰和厚度干涉条纹表明其具有良好的晶体质量和表面/界面质量。图(d)中的倒空间扫描(rsm)表明灰锡薄膜是完全应变的。总体而言,灰锡薄膜具有良好的晶体质量。

33.图5为得到的高阻值insb缓冲层的电学性质表征结果。在200k以下,随着温度降低,高阻值insb缓冲层的电阻率急剧增大(左边图),在低温下电阻率比通常的insb缓冲层要大一个量级;相应地高阻值insb缓冲层的载流子急剧减小(右边图),整体上表现出较为绝缘的性质。

34.据上述方法得到的灰锡薄膜,拓扑表面态的费米速度可达1.0

ꢀ×ꢀ

10

6 m/s量级,动量弛豫时间可达100 fs量级,理论转换效率(电流密度与自旋流密度之比)可达100 nm量级。

35.实施例2(1)准备(001)晶面的cd

0.9

zn

0.1

te衬底;(2)在原子氢炉中对cd

0.9

zn

0.1

te衬底进行脱氧处理,原子氢炉处理时间60 min;(3)采用分子束外延方法,在cd

0.9

zn

0.1

te衬底上生长in

0.9

ga

0.1

sb缓冲层。生长过程中sb:(in ga)束流比为1:1,衬底温度为200℃,in

0.9

ga

0.1

sb的厚度为30 nm;

(4)提高衬底温度至350℃,退火30 min得到高阻值的insb缓冲层;(5)在iv族分子束外延设备中生长50 nm的α-sn

0.9

ge

0.1

薄膜。

36.本实施例所得的α-sn

0.9

ge

0.1

薄膜同样具有较高的质量,且in

0.9

ga

0.1

sb缓冲层的载流子浓度减小一个量级。

37.以上所述仅是本发明优选的实施方式,应当指出,对于本技术领域的普通技术人员来说,在不脱离本发明原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也应视为本发明的保护范围。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。