一种iii-v族化合物半导体光芯片与硅基电芯片实现晶圆级别集成的方法

技术领域

1.本发明涉及半导体光电子技术领域,特别涉及一种iii-v族化合物半导体光芯片与硅基电芯片实现晶圆级别集成的方法。

背景技术:

2.硅光技术将原本分离的众多的光、电元件缩小集成到至一个独立微芯片中,实现高集成度、低成本、高速光传输。相比较传统的分立器件光模块,硅光子器件集成度更高(不再需要rosa和tosa封装)更加适应未来高速流量传输处理需要。与此同时,更紧密的集成方式降低了光模块的封装和制造成本。

3.由于si材料不能制作光源,因此硅光技术的核心难点是如何将光源集成到si芯片上。异质外延生长方法是现有硅光单片集成的常见方法,其首先在 si衬底上直接外延生长iii-v族材料的激光器有源区,然后进行芯片工艺,达到si衬底上集成激光器的效果,该方法的集成度最高,可实现光电一体融合,将电驱动芯片直接与激光器集成,但是直接在si衬底上进行iii-v族外延生长的难度巨大,近期很难有突破。以gaas外延结构为例,异质外延是实现si衬底上的gaas外延生长的一种方式,为了防止位错传播到有源区,需要使用一系列非常厚的晶格分级缓冲层,这使得芯片制作的成本很高,而且工艺很难控制。此外,这种iii-v族的异质外延生长技术大多无法用于300mm的大型晶圆。

4.另外,目前的硅基集成电路和电芯片已经发展到了12寸晶圆水平,而 iii-v族化合物基的光电芯片在晶圆尺寸方面远远落后于硅基,inp和gaas衬底商业化可用的最大尺寸分别只有4寸和6寸,这使得在晶圆级别实现光芯片和电芯片的集成几乎不可能,只能采用分立器件的组装,这也是目前在光通信和消费类光电子领域的光模块(光芯片 电芯片)成本居高不下、能耗高的主要原因之一。

技术实现要素:

5.本发明提供一种iii-v族化合物半导体光芯片与硅基电芯片实现晶圆级别集成的方法,其主要目的在于解决现有硅光单片集成方法所存在的制作成本高,工艺可控性差和适用范围小的问题。

6.本发明采用如下技术方案:

7.一种iii-v族化合物半导体光芯片与硅基电芯片实现晶圆级别集成的方法,包括如下步骤:

8.(1)在iii-v族衬底上生长牺牲层和外延层;

9.(2)将外延层刻蚀成单颗独立的iii-v族化合物半导体光芯片;

10.(3)在各iii-v族化合物半导体光芯片上方粘贴一片式的可延展胶带;

11.(4)使用hf溶液选择性刻蚀各iii-v族化合物半导体光芯片的牺牲层,从而将iii-v族衬底从单颗iii-v族化合物半导体光芯片的底部剥离;

12.(5)通过可延展胶带将各iii-v族化合物半导体光芯片转移至一片式的临时衬底上,并去除可延展胶带;

13.(6)通过临时衬底将各iii-v族化合物半导体光芯片转移至一片式的硅基衬底上,并去除临时衬底。

14.进一步,在步骤(5)中,首先采用扩膜装置对可延展胶带进行扩膜,从而使各iii-v族化合物半导体光芯片的位置符合预设的芯片位置,然后再将各iii-v族化合物半导体光芯片转移至一片式的临时衬底上。

15.更进一步,采用扩膜装置对可延展胶带进行整膜延展,从而调整各iii-v族化合物半导体光芯片之间的间距。

16.更进一步,采用扩膜装置对可对延展胶带进行局部延展,从而调整对应位置的相邻两iii-v族化合物半导体光芯片之间的间距。

17.进一步,在步骤(6)中,采用直接键合或粘合剂粘结的方式将各iii-v 族化合物半导体光芯片固定于一片式的硅基衬底上。

18.进一步,所述硅基衬底为si衬底。

19.进一步,所述iii-v族衬底为inp衬底,所述iii-v族化合物半导体光芯片为vcsel,所述牺牲层为alas/inalas/alas/inalas/alas超晶格结构,并且alas的厚度为1.52.1nm,inalas的厚度为1nm。

20.更进一步,在步骤(1)中,首先在inp衬底上成长inp第一缓冲层,然后再生长牺牲层和外延层;在步骤(5)中,使用hf溶液刻蚀牺牲层,从而将inp第一缓冲层和inp衬底同时剥离。

21.进一步,所述iii-v族衬底、临时衬底和硅基衬底的厚度均为300-700 μm。

22.进一步,所述iii-v族衬底为gaas衬底,所述iii-v族化合物半导体光芯片为vcsel,所述牺牲层为alas超晶格结构。

23.和现有技术相比,本发明产生的有益效果在于:

24.1、本发明首先基于同质外延生长方法在iii-v族衬底上完成iii-v族化合物半导体光芯片的外延生长以及部分或全部的工艺制程制作,然后通过衬底剥离工艺将iii-v族衬底从iii-v族化合物半导体光芯片底部剥离,最后利用扩膜工艺将iii-v族化合物半导体光芯片转移至硅基衬底上,由此实现了iii-v族化合物半导体光芯片与硅基电芯片在晶圆级别的集成,有效地克服了现有技术中基于异质外延生长的硅光单片集成所存在的缺陷,具有制作方法简单、可控性强、生产成本低和通用性高等优点,能广泛应用于各种类型的iii-v族化合物半导体光芯片生产和光芯片、电芯片集成方案。

25.2、本发明的衬底剥离工艺首先将芯片的外延层刻蚀成单颗独立的 iii-v族化合物半导体光芯片,然后采用晶格匹配的牺牲层来对单颗独立的 iii-v族化合物半导体光芯片进行衬底剥离,由此大大减小了剥离难度和制程时间,实现了iii-v族衬底的回收利用,极大地降低了企业的生产成本。

附图说明

26.图1为本发明中iii-v族化合物半导体光芯片的制备流程示意图一。

27.图2为本发明中iii-v族化合物半导体光芯片的制备流程示意图二。

28.图3为本发明实施例中两端带有组合反射镜的vcsel的结构示意图。

29.图4为本发明实施例中有源区的层状结构示意图。

30.图5为本发明实施例中光栅层的结构示意图。

31.图6为本发明实施例中衬底剥离前vcsel的外延结构示意图。

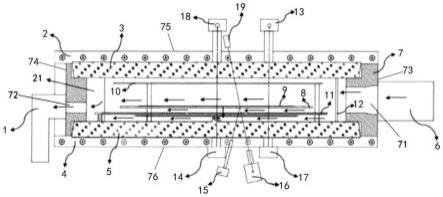

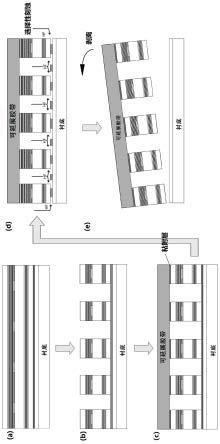

32.图7为本发明中可延展胶带的扩膜操作示意图。

33.图中:

34.10、inp衬底;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

11、inp第一缓冲层;

35.12、牺牲层;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

13、inp第二缓冲层;

36.14、第一n型掺杂dbr;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

15、有源区;

37.16、第二n型掺杂dbr;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

17、介质层dbr;

38.18、掩埋隧穿结;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

19、光栅层;

39.113、si衬底;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

151、限制层;

40.152、波导层;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

153、量子阱层;

41.154、对称波导层;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

155、对称限制层。

具体实施方式

42.下面参照附图说明本发明的具体实施方式。为了全面理解本发明,下面描述到许多细节,但对于本领域技术人员来说,无需这些细节也可实现本发明。

43.如图1和图2所示,本发明的主要构思在于提供一种iii-v族化合物半导体光芯片与硅基电芯片实现晶圆级别集成的方法,其包括如下步骤:

44.(1)在iii-v族衬底上生长牺牲层和外延层,如图1(a)所示;

45.(2)将外延层刻蚀成单颗独立的iii-v族化合物半导体光芯片,如图 1(b)所示;

46.(3)在各iii-v族化合物半导体光芯片上方粘贴一片式的可延展胶带,如图1(c)所示;

47.(4)使用hf溶液选择性刻蚀各iii-v族化合物半导体光芯片的牺牲层,从而将iii-v族衬底从单颗iii-v族化合物半导体光芯片的底部剥离,如图 1(d)和(e)所示;

48.(5)通过可延展胶带将各iii-v族化合物半导体光芯片转移至一片式的临时衬底上,并去除可延展胶带,如图2(a)和(b)所示;该步骤中,首先采用扩膜装置对可延展胶带进行扩膜,从而使各iii-v族化合物半导体光芯片的位置符合预设的芯片位置,如图7所示;然后再将各iii-v族化合物半导体光芯片转移至一片式的临时衬底上。在具体实施过程中,既可以采用整膜延展的方式对可延展胶带进行整体扩膜,从而调整各iii-v族化合物半导体光芯片之间的间距;也可以采用局部延展的方式对可对延展胶带进行局部扩膜,从而调整对应位置的相邻两iii-v族化合物半导体光芯片之间的间距;

49.(6)通过临时衬底将各iii-v族化合物半导体光芯片转移至一片式的硅基衬底上,并去除临时衬底,如图2(a)和(b)所示,该步骤中,采用直接键合或粘合剂粘结的方式将各iii-v族化合物半导体光芯片固定于一片式的硅基衬底上,硅基衬底可选用si衬底。

50.本实施例中iii-v族衬底优为inp衬底,iii-v族化合物半导体光芯片优选为两端带有组合反射镜的vcsel,硅基衬底优选为si衬底。

51.以下先对两端带有组合反射镜的vcsel进行介绍:

52.如图3所示,该vcsel包括si衬底113以及通过衬底剥离技术剥离inp 衬底后的外延层,外延层固定装设于si衬底113上方,且外延层由下至上依次包括第一反射镜、第二n型掺杂dbr16、掩埋隧穿结18、有源区15、第一n型掺杂dbr14、inp第二缓冲层13和第二反射镜。其中,第一反射镜和第二反射镜均可选用介质层dbr和光栅层两种中的任意一种。本实施例中第一反射镜优选为介质层dbr17,第二反射镜优选为光栅层19。本实施例采用组合反射镜的设计构思,利用介质层dbr/光栅层 第一n型掺杂dbr以及介质层dbr/光栅层 第二n型掺杂dbr的组合反射镜代替传统vcsel中膜层数目多、厚度大的inp/inalgaas的单一dbr反射镜,有效降低了vcsel的光、电损耗,提高vcsel的转换效率,并降低了器件的制作难度,符合激光雷达或数据通讯等领域对长波长vcsel的特性需求。

53.如图3和图5所示,本实施例中vcsel的外延结构参数如下:

54.si衬底113的厚度为300-700μm,其具有良好的导热性能,有利于芯片散热外,同时也起到了物理支撑作用,能够有效替代inp衬底。

55.介质层dbr17的材料为是由sio2/si3n4周期堆叠组成的反射镜,周期数为4-8,厚度为1800-3750nm。

56.第一n型掺杂dbr14和第二n型掺杂dbr16均是由inalgaas/inp或者 ingaasp/inp周期堆叠组成的反射镜。本实施例中第一n型掺杂dbr14和第二n型掺杂dbr16可提供足够的物理支撑,并提供部分反射率,从而确保外延片的反射镜组合方式可靠稳定。第一n型掺杂dbr14和第二n型掺杂dbr16 的周期数均为5-20,厚度为1000-5000nm。传统1550nm vcsel inp/inalgaasdbr反射镜反射率为99%时,半导体dbr厚度达8μm;采用第一n型半导体掺杂dbr(5-10周期数) 介质层dbr反射单元达到相同的反射率,半导体dbr 厚度只有1-2.5μm;采用第二n型半导体掺杂dbr(5-20周期数) hcg反射单元达到相同的反射率,半导体dbr厚度只有1-5μm。可见,采用介质层dbr17 第一n型掺杂dbr14以及光栅层19 第二n型掺杂dbr16的组合反射镜能够有效降低dbr反射镜的厚度,从而有效解决现有技术中vcsel的单一dbr反射镜所存在的膜层数目多、厚度大的问题。

57.inp第二缓冲层13的厚度为500-1000nm,掺杂原子为si,且掺杂浓度>10

18

cm-3

。由于本实施例所提供的vcsel需要采用衬底剥离工艺制作而成,因此设置inp第二缓冲层13可起到保证晶体质量的作用。

58.掩埋隧穿结18由下至上包括p型重掺层和n型重掺层。p型重掺层材料可以为但不限于ingaasp、ingaalas、alinas、inp,n型重掺层材料可以为但不限于gainas、inp、ingaasp、ingaalas、alinas;p型重掺层厚度范围为8-50nm,n型重掺层厚度范围为10-50nm;p型重掺层掺杂原子可以为但不限于c、mg、zn、be,n型重掺层掺杂原子可以为但不限于te、 se、si、s;p型重掺层与n型重掺层掺杂浓度为10

19-10

20

cm-3

数量级;掩埋隧穿结18孔径范围为4-50μm。

59.光栅层19优选为高折射率对比度亚波长光栅,其为被低折射率介质包围的高折射率材料的亚波长条纹形成的光栅类型,其中高折射率材料为sio2或si3n4,低折射率材料可以为空气或氧化物,光栅周期550nm<∧<800nm,填充系数350nm《η《500nm,光栅深度350nm《tg《500nm。

60.各vcsel的外延结构的相关设计参数参照表1。

61.表1 vcsel的外延结构参数表

[0062][0063]

如图4所示,本实施例中有源区15优选为有源区由下至上为限制层151、波导层152、量子阱层153、对称波导层154、对称限制层155。量子阱层 153的阱层/垒层为in

x

ga

1-x

asyp

1-y

/in

x

ga

1-x

asyp

1-y

或者不同ga/al比例的 alingaas。

[0064]

有源区的设计参数参照表2。

[0065]

表2有源区的参数表

[0066][0067]

以下详细介绍将两端带有组合反射镜的vcsel与si衬底的晶圆级别集成方法,其包括如下步骤:

[0068]

s1、在inp衬底10上生长外延片,外延片包括inp第一缓冲层11、牺牲层12和外延层,外延层包括inp第二缓冲层13、第一n型掺杂dbr14、有源区15、隧穿结层、第二n型掺杂dbr16和介质层dbr17。隧穿结层具有若干个相互间隔设置的掩埋隧穿结18,如图1(a)和图6所示。

[0069]

具体地,首先采用mocvd工艺在inp衬底10上依次沉积inp第一缓冲层11、牺牲层12、inp第二缓冲层13、第一n型掺杂dbr14、有源区15和隧穿结层;接着通过掩膜和刻蚀形成隧穿结层的台面来定义vcsel的孔径,然后通过二次外延来掩埋隧穿结,并生长第二n型掺

杂dbr16;最后采用 pecvd工艺在第二n型掺杂dbr16表面沉积介质层dbr17。

[0070]

需要说明的是,由于本实施例所提供的vcsel需要采用衬底剥离工艺制作而成,因此需要在有源区的两端设置保证晶体质量的inp第一缓冲层11 和inp第二缓冲层13,而衬底剥离过程中,牺牲层12被刻蚀掉,inp第一缓冲层11则需要同inp衬底10一起剥离,因此本实施例“外延片”特指包含有inp第一缓冲层11和牺牲层12的整个外延部分,而“外延层”特指牺牲层12以上的外延部分。

[0071]

s2、将外延层刻蚀成单颗独立的vcsel芯片。具体地,采用光刻与化学溶液刻蚀法将外延层刻蚀成单颗独立的vcsel芯片,如图1(b)所示。

[0072]

s3、在各vcsel芯片的介质层dbr17表面通过粘附层粘接一片式的可延展胶带,如图1(c)所示。

[0073]

s4、使用hf溶液选择性刻蚀各vcsel芯片的牺牲层12,从而将inp衬底10从各vcsel芯片底部剥离;具体地,hf溶液会对外延片进行选择性刻蚀,以使牺牲层从inp衬底10上分离,由此将整片外延层从inp衬底10 上剥离出来,如图1(e)所示。

[0074]

s5、通过可延展胶带将各vcsel芯片转移到一片式的临时衬底上,并去除可延展胶带,如图2(a)和(b)所示。

[0075]

s6、通过临时衬底将各vcsel芯片转移至si衬底113上,并去除临时衬底,如图2(c)和(d)所示。临时衬底为外延片与最终衬底的粘附提供了足够的物理支撑。在实际应用中,可采用直接键合或者粘合剂粘结的方式将临时衬底或最终衬底装设于外延片上,但是为了便于去除临时衬底,其与外延片的粘附力应相对较弱。

[0076]

s7、在各vcsel芯片的inp第二缓冲层13表面制作光栅层,其制作方法为:首先采用pecvd工艺在inp第二缓冲层13表面沉积若干相互间隔设置的sio2层或者si3n4层;然后通过光刻与化学溶液刻蚀或者局部氧化形成光栅层19。对步骤(7)得到的单颗独立的vcsel芯片进行切割分离,便可得到如图3所示的组合反射镜式vcsel。

[0077]

如图3所示,本实施例中牺牲层12优选为 alas/inalas/alas/inalas/alas超晶格结构,其中alas的厚度为1.5-2.1nm, inalas的厚度为1nm。牺牲层成分的选择与厚度在elo工艺中至关重要,较厚的膜层会导致蚀刻速度减慢,而太薄的层(通常小于5nm)则会导致蚀刻突然停止,有研究表明,牺牲层的合理厚度应控制在5-10nm范围内。现有技术中,基于inp衬底的el0工艺通常使用alas作牺牲层,但是,alas材料与inp材料的晶格失配高达3.6%。在已实现的以alas为牺牲层的inp衬底剥离实验中,使用厚度超过5nm的alas会导致牺牲层松弛,引起晶体缺陷,从而影响器件性能。为了克服alas层的厚度限制,本实施例使用 alas/inalas/alas/inalas/alas超晶格来代替alas做牺牲层,尽管alas 和inp之间存在高度的晶格失配,但是alas/inalas/alas/inalas/alas超晶格结构可以被视为一个单一的层,呈现出构成超晶格的有效平均成分,且可沉积更厚的牺牲层,并保持良好的材料晶体质量。可见,采用 alas/inalas/alas/inalas/alas超晶格结构可以在保证器件薄膜质量的同时,实现inp衬底的剥离与再利用,降低了企业的生产成本。在其他实施例中,还可采用基于gaas材料体系的vcsel芯片,当iii-v族衬底为gaas 衬底时,牺牲层为alas。

[0078]

上述仅为本发明的具体实施方式,但本发明的设计构思并不局限于此。凡是利用本发明的设计构思对本发明进行非实质性的改动,均应属于侵犯本发明保护范围的行为。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。