1.本发明涉及电路板、半导体装置及电路板的制造方法。

背景技术:

2.例如,在将半导体芯片等安装件安装于电路板时,电路板的最表层由被称作阻焊剂的绝缘材料的保护而避免焊料的附着以及污染等。这种情况下,为了形成与安装件连接所需的焊盘,而形成有开口部,该开口部用于使形成在阻焊剂的下层的布线层露出。

3.图12是表示以往的电路板100的一个示例及识别标记103的一个示例的示意平面图。图12所示的电路板100包括:用于搭载半导体芯片的芯片安装区域101、以及在芯片安装区域101内的多个焊盘102。此外,在芯片安装区域101的周围,形成有在将半导体芯片搭载于芯片安装区域101时用于定位的识别标记(对准标记)103。识别标记103是通过在形成于绝缘层105上的阻焊层104上形成平面形状为圆形的开口部104a,并从开口部104a露出布线图案来形成的。

4.识别标记103是由平面形状包含圆形部分103a和直线部分103b的布线图案形成的。并且,在芯片安装区域101周围,在电路板100的芯片安装区域101的对角线上,形成有两处识别标记103。

5.在用于将半导体芯片搭载于电路板100的芯片安装区域101上的搭载装置中,对芯片安装区域101周围的两处识别标记103进行识别,并以识别到的两处识别标记103的位置为基准来识别芯片安装区域101的位置。进一步地,搭载装置将半导体芯片搭载于识别到的芯片安装区域101上。其结果,能够在对识别标记103进行识别后将半导体芯片精确地配置于芯片安装区域101上。

6.专利文献1:日本特开平6-177492号公报

7.专利文献2:日本特开2007-258374号公报

8.专利文献3:日本特开2012-74443号公报

技术实现要素:

9.图13是表示以往的识别标记103的交界点y的识别动作的一个示例的说明图。搭载装置从电路板100上识别识别标记103,并对位于阻焊层104的开口部104a的识别标记103的圆形部分103a及直线部分103b(布线图案)与下层的绝缘层105之间的多个交界点y进行识别。并且,如图13所示,搭载装置基于识别到的多个交界点y,计算出虚拟圆,并计算出虚拟圆的中心来作为识别标记103的中心。搭载装置基于在芯片安装区域101周围计算出的两处识别标记103的中心,而识别出芯片安装区域101的位置。然而,识别标记103的中心是使用圆形部分103a及直线部分103b的布线图案来计算出的虚拟圆的中心,因此并不是算出正确的识别标记103的中心。

10.图14是表示以往的识别标记103的识别动作的问题的一个示例的说明图。在搭载装置中,若阻焊层104的开口部104a的位置偏离,则开口部104a内的识别标记103的圆形部

分103a及直线部分103b的布线图案的一部分将被隐藏于阻焊层104中。其结果,在搭载装置中,由于识别标记103的布线图案的一部分无法被识别,而导致识别标记103的识别准确度降低。而且,存在识别标记103的直线部分103b被隐藏于阻焊层104中而仅露出识别标记103的圆形部分103a的布线图案的情况。这种情况下,由于露出的识别标记103的圆形部分103a与焊盘102为尺寸相同的圆形,从而存在搭载装置将识别标记103误识别为焊盘102的风险。

11.此外,也可以考虑,将形成识别标记103的开口部104a不形成为圆形,而形成为四边形或三角形的情况。图15a是表示以往的开口部104b的一个示例的示意平面图,图15b是表示以往的开口部104c的一个示例的示意平面图。开口部104b及104c与圆形相比其开口尺寸需要加大,而在将开口尺寸缩小的情况下,则难以形成锐角的开口。其结果,开口部104b及104c的直线部分x1与边缘的圆弧部分x2的尺寸比不稳定,因此不适合作为开口部104a。

12.所公开的技术是鉴于上述问题而提出的,其目的在于提供一种能够提供识别性优越的识别标记的电路板、半导体装置及电路板的制造方法。

13.本发明公开的电路板在一形态下具有配线和覆盖所述配线的绝缘层。所述配线具有第一配线,所述第一配线形成为平面形状呈预设形状的识别标记。所述绝缘层具有平面形状呈异形的贯穿孔,所述贯穿孔以使所述第一配线的整个上表面露出的方式,沿该绝缘层的厚度方向贯穿该绝缘层。所述贯穿孔包括:平面形状呈预设形状的第一贯穿孔,其以使所述第一配线的整个上表面露出的方式沿所述厚度方向贯穿所述绝缘层;以及第二贯穿孔,其沿所述厚度方向贯穿作为所述第一贯穿孔内壁面的一部分的所述绝缘层。

14.根据本发明公开的电路板的一形态,通过使用以使识别标记的整个上表面露出的方式形成的异形的贯穿孔,能够提供一种识别性优越的识别标记。

附图说明

15.图1是表示本实施例的半导体装置及识别标记的一个示例的示意平面图。

16.图2是表示本实施例的电路板及识别标记的一个示例的示意平面图。

17.图3是图1所示的半导体装置的a-a线示意剖面图。

18.图4是表示识别标记的一个示例的平面图及b-b线示意剖面图。

19.图5是表示对识别标记的交界点的识别动作的一个示例的说明图。

20.图6是表示半导体装置的制造工序的步骤的一个示例的流程图。

21.图7a是表示第一布线层形成工序的一个示例的说明图。

22.图7b是表示绝缘层形成工序的一个示例的说明图。

23.图7c是表示第一开口形成工序的一个示例的说明图。

24.图7d是表示种晶层形成工序的一个示例的说明图。

25.图8a是表示第二布线层形成工序的一个示例的说明图。

26.图8b是表示图案去除工序的一个示例的说明图。

27.图8c是表示阻焊层形成工序的一个示例的说明图。

28.图9a是表示第二开口形成工序的一个示例的说明图。

29.图9b是表示部件搭载工序的一个示例的说明图。

30.图9c是表示半导体装置成品的一个示例的说明图。

31.图10是表示多个电路板的一个示例的示意平面图。

32.图11a是表示识别标记及贯穿孔的一个示例的示意平面图。

33.图11b是表示识别标记及贯穿孔的一个示例的示意平面图。

34.图11c是表示识别标记及贯穿孔的一个示例的示意平面图。

35.图11d是表示识别标记及贯穿孔的一个示例的示意平面图。

36.图12是表示以往的电路板及识别标记的一个示例的示意平面图。

37.图13是表示以往的识别标记的交界点的识别动作的一个示例的说明图。

38.图14是表示以往的识别标记的识别动作的问题的一个示例的说明图。

39.图15a是表示以往的开口部的一个示例的示意平面图。

40.图15b是表示以往的开口部的一个示例的示意平面图。

41.符号说明

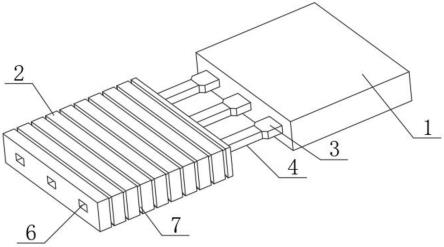

42.1 半导体装置

43.2 电路板

44.3 半导体芯片

45.20 布线图案(配线)

46.20a 布线图案

47.20a1 布线图案(第二配线)

48.20a2 布线图案(第一配线)

49.21a 焊盘

50.22 识别标记

51.30 阻焊层

52.30a 阻焊层

53.31a 开口部

54.32 贯穿孔

55.32a 第一贯穿孔

56.32b 第二贯穿孔

57.321 一侧贯穿孔

58.322 另一侧贯穿孔

59.32a1 一侧第一贯穿孔

60.32a2 另一侧第一贯穿孔

61.32b1 一侧第二贯穿孔

62.32b2 另一侧第二贯穿孔

63.ca 芯片安装区域

具体实施方式

64.下面,参照附图对本发明公开的电路板、半导体装置及电路板的制造方法的实施方式进行详细说明。此外,本发明并不限于该实施方式。

65.实施例

66.图1是表示本实施例的半导体装置1及识别标记22的一个示例的示意平面图,图2是表示本实施例的电路板2及识别标记22的一个示例的示意平面图,图3是图1所示的半导

体装置1的a-a线示意剖面图。

67.图1及图3所示的半导体装置1包括:电路板2、半导体芯片3以及底部填充树脂4。图3所示的电路板2包括:电路板主体10、作为最上层配线(配线)的布线图案20a(20)、作为最下层配线的布线图案20b(20)、最上层的阻焊层30a(30)以及最下层的阻焊层30b(30)。此外,安装于电路板2的半导体芯片3具备:在其电路形成面呈矩阵状配设的多个凸块3a。阻焊层30a为覆盖作为最上层配线的布线图案20a的绝缘层。在下文中,对如图3所示,阻焊层30a为最上层且阻焊层30b为最下层的情况进行了说明,但电路板2例如也可以上下翻转后使用,还可以以任意的姿势使用。

68.图3所示的电路板主体10包括:芯基材11、多个绝缘层12(12a、12b)、形成于多个绝缘层12的配线13(13a、13b)及导通孔(via)14(14a、14b)等。设于电路板主体10的配线13及导通孔14电气连接布线图案20a与20b。此外,作为配线13以及导通孔14的材料,例如可以使用铜(cu)。此外,作为绝缘层12的材料,例如可以使用环氧树脂或聚酰亚胺树脂这类绝缘树脂。

69.布线图案20a设于电路板主体10的芯片安装面侧(图3中的上表面侧),具有布线图案20a1和布线图案20a2。布线图案20a1为第二配线,其作为供半导体芯片3的凸块3a连接的焊盘21a。布线图案20a1的平面形状例如为圆形。

70.布线图案20a2为第一配线,其整个上表面从阻焊层30a露出而成为识别标记22。此外,如图1所示,布线图案20a2的平面形状例如为圆形。布线图案20a中的布线图案20a1及布线图案20a2形成为相同的厚度。作为布线图案20a的材料,即作为焊盘21a及识别标记22的材料,例如可以使用铜。此外,布线图案20a还可以通过在铜层的表面进行所需的电镀(例如,镀镍或镀金等)而形成。

71.如图3所示,布线图案20b设于电路板主体10的与芯片安装面相反的一侧(图3中的下表面侧)。布线图案20b为焊盘21b。此外,作为布线图案20b的材料,例如可以使用铜。

72.阻焊层30a以覆盖布线图案20a的方式设于电路板主体10的芯片安装面侧。作为阻焊层30a的材料,例如可以使用环氧树脂等绝缘性的非感光性树脂。在阻焊层30a中形成有用于使作为布线图案20a1的焊盘21a的一部分露出的多个开口部31a,并且形成有用于使作为布线图案20a2的识别标记22的整个上表面露出的贯穿孔32。

73.在此,对开口部31a进行说明。首先,由于半导体芯片3的凸块3a配设为矩阵状,根据其配设方式,焊盘21a也在电路板2的芯片安装区域ca中呈矩阵状地排列(参见图2)。因此,在阻焊层30a的芯片安装区域ca中,多个开口部31a形成为矩阵状。此外,各开口部31a的平面形状与布线图案20a1的焊盘21a一样地为圆形。进一步地来说,各开口部31a的平面形状形成为小于焊盘21a的平面形状,以使焊盘21a的一部分露出。并且,根据这种开口部31a,布线图案20a1的一部分作为焊盘21a从阻焊层30a露出。

74.接着,对贯穿孔32进行说明。图4是表示识别标记22的一个示例的平面图及b-b线示意剖面图。识别标记22及阻焊层30a形成在绝缘层12a(12)上。首先,识别标记22的平面形状例如为圆形。其次,贯穿孔32的平面形状的口径形成为大于布线图案20a2的平面形状的直径,以使布线图案20a2的整个上表面露出。具体而言,贯穿孔32的平面形状的开口面积大于识别标记22的平面面积,且贯穿孔32的平面形状为异形。此外,例如可以使用光刻法等而容易地使布线图案20a2形成为平面圆形。

75.此外,贯穿孔32的内壁面由与识别标记22的侧壁面隔开的阻焊层30a形成。换言之,识别标记22的周围呈与阻焊层30a隔开的状态。并且,贯穿孔32包括第一贯穿孔32a和第二贯穿孔32b。第一贯穿孔32a为平面形状呈圆形的贯穿孔,其以使识别标记22的整个上表面露出的方式沿阻焊层30a的厚度方向贯穿该阻焊层30a。第二贯穿孔32b为平面形状呈半圆形的贯穿孔,其沿阻焊层30a的厚度方向贯穿第一贯穿孔32a内壁面的一部分的阻焊层30a。这样,圆形的第一贯穿孔32a与半圆形的第二贯穿孔32b形成平面形状为异形的贯穿孔32。换言之,贯穿孔32的平面形状为在圆形的第一贯穿孔32a内壁面的一部分设有作为沉孔部的第二贯穿孔32b的形状,第一贯穿孔32a与第二贯穿孔32b以相连的方式形成。进一步地,在贯穿孔32中的第一贯穿孔32a内形成有圆形的识别标记22。

76.此外,如图3所示,焊盘21b通过使布线图案20b的一部分从形成于电路板主体10的下表面侧的阻焊层30b的开口部31b露出而形成。

77.半导体芯片3以倒装芯片方式接合于如上述方式构成的电路板2上的芯片安装区域ca。即,半导体芯片3通过配设于电路形成面的凸块3a,而与芯片安装区域ca内的焊盘21a电气连接。此外,在将半导体芯片3的凸块3a搭载于阻焊层30a的开口部31a内的焊盘21a上后,通过加热将焊料熔融一次来使阻焊层30a的开口部31a为被焊料填满的状态。

78.进一步地,底部填充树脂4以填充电路板2与半导体芯片3间的间隙的方式设置。该底部填充树脂4用于提高凸块3a与焊盘21a之间的连接部分的连接强度,并用于抑制布线图案20a1的腐蚀以及电迁移的发生,从而避免布线图案20a1的可靠性的降低。此外,作为底部填充树脂4的材料,例如可以使用环氧树脂。

79.图5是表示对识别标记22的交界点y的识别动作的一个示例的说明图。未图示的搭载装置例如将一定强度的光照射于电路板2上的识别标记22以及阻焊层30a等的表面,并根据该反射光的强度来识别异形的贯穿孔32。进一步地,搭载装置在识别出异形的贯穿孔32之后,对贯穿孔32内的识别标记22与绝缘层12a之间的多个交界点y进行识别。由此,能够容易地识别贯穿孔32内的识别标记22的轮廓(形状)。

80.接下来,对如上述方式构成的半导体装置1的制造方法进行说明。图6是表示半导体装置1的制造工序的步骤的一个示例的流程图。在图6中作为半导体装置1的制造工序,执行在芯基材11上形成配线13(13a、13b)的第一布线层形成工序(步骤s11)。作为制造工序,在执行了第一布线层形成工序之后,执行在芯基材11上形成绝缘层12(12a、12b)的绝缘层形成工序(步骤s12)。

81.进一步地,作为制造工序,在执行了绝缘层形成工序之后,执行在绝缘层12(12a、12b)上形成开口部12a1及12b1的第一开口形成工序(步骤s13)。作为制造工序,在执行了第一开口形成工序之后,执行在绝缘层12(12a、12b)上形成种晶层s1(s2)的种晶层形成工序(步骤s14)。

82.进一步地,作为制造工序,在执行了种晶层形成工序之后,在种晶层s1(s2)上形成用于形成布线图案20(20a,20b)的阻镀图案。进一步地,作为制造工序,在形成阻镀图案之后,执行形成用于构成布线图案20的电镀层的第二布线层形成工序(步骤s15)。作为制造工序,在执行了第二布线层形成工序之后,执行去除形成于种晶层s1(s2)上的阻镀图案的图案去除工序(步骤s16)。

83.进一步地,作为制造工序,在执行了图案去除工序之后,执行去除绝缘层12上不要

的种晶层s1(s2)的种晶层除去工序(步骤s17)。进一步地,作为制造工序,在执行了种晶层除去工序之后,执行在绝缘层12上以覆盖布线图案20表面的方式形成阻焊层30(30a,30b)的阻焊层形成工序(步骤s18)。进一步地,作为制造工序,在执行了阻焊层形成工序之后,执行在阻焊层30上形成开口部31a(31b)及贯穿孔32的第二开口形成工序(步骤s19)。

84.作为制造工序,在执行了第二开口形成工序之后,利用搭载装置对芯片安装区域ca周围的识别标记22进行识别,从而识别用于搭载半导体芯片3的芯片安装区域ca的位置,例如对识别标记之间的中央进行识别。然后,基于识别出的芯片安装区域ca的位置,执行将半导体芯片3搭载于芯片安装区域ca的部件搭载工序(步骤s20)。这样,半导体装置1得以制成。

85.在此,对半导体装置1的制造方法进行详细说明。图7a是表示第一布线层形成工序的一个示例的说明图。图7a所示的芯基材11例如通过在覆铜板(copper clad laminated:ccl)上形成通孔11a,并对通孔11a的侧面进行电镀从而导通两个表面。进一步地,芯基材11是通过减成法形成配线13a、13b来制造的。

86.图7b是表示绝缘层形成工序的一个示例的说明图。如图7b所示,在芯基材11的两个表面形成绝缘层12a、12b。接着,图7c是表示第一开口形成工序的一个示例的说明图。如图7c所示,以使配线13a、13b的端部露出的方式,在绝缘层12a、12b的预设位置例如通过激光分别形成开口部12a1、12b1。

87.图7d是表示种晶层形成工序的一个示例的说明图。在除胶渣处理之后,如图7d所示,形成种晶层s1以覆盖绝缘层12a及配线13a,并形成种晶层s2以覆盖绝缘层12b及配线13b。这些种晶层s1、s2例如是通过化学镀铜或溅射而形成的。

88.图8a是表示第二布线层形成工序的一个示例的说明图。如图8a所示,例如通过半加成法来形成布线图案20及导通孔14。即,通过光刻法在种晶层s1上形成阻镀干膜(dfr)40,其具有与布线图案20a的形状对应的开口图案40a。进一步地,通过将种晶层s1作为供电层的电镀铜来形成布线图案20a及导通孔14a。由此,形成所需形状(本实施例中为圆形)的布线图案20a1(焊盘21a)和所需形状(本实施例中为圆形)的布线图案20a2(识别标记22)。此时,如图8a所示,由于用于决定布线图案20a的形状的dfr40的开口图案40a是通过光刻法而形成的,因此能够精确地形成对应布线图案20a的圆形的开口图案40a。因此,如图8a所示,能够精确地形成圆形的布线图案20a。此外,布线图案20b及导通孔14b也通过与布线图案20a及导通孔14a同样的方式形成。

89.图8b是表示图案去除工序的一个示例的说明图。在如图8a所示形成布线图案20及导通孔14后,如图8b所示,从绝缘层12上将dfr40及不要的种晶层s1、s2去除。图8c是表示阻焊层形成工序的一个示例的说明图。接着,如图8c所示,形成阻焊层30a以覆盖形成于绝缘层12a的布线图案20a,并形成阻焊层30b以覆盖形成于绝缘层12b的布线图案20b。在采用液态阻焊剂的情况下,例如可以通过丝网印刷法、喷涂法或辊涂法等方法来形成这些阻焊层30a及30b。此外,还可以通过将膜状的阻焊层30层压于绝缘层12的上表面及下表面,来形成阻焊层30a、30b。

90.图9a是表示第二开口形成工序的一个示例的说明图。如图9a所示,通过激光加工在阻焊层30a的与焊盘21a(布线图案20a1)及识别标记22(布线图案20a2)对应的部位,形成沿阻焊层30a的厚度方向贯穿的开口部31a及贯穿孔32。进一步地,通过激光加工在阻焊层

30b的与焊盘21b对应的部位,形成沿阻焊层30b的厚度方向贯穿的开口部31b。此外,第二开口形成工序包括第一贯穿孔形成工序以及第二贯穿孔形成工序。在第一贯穿孔形成工序中,以使布线图案20a2的整个上表面露出的方式,在阻焊层30a形成沿阻焊层30a的厚度方向贯穿的、平面形状为圆形的第一贯穿孔32a。在第二贯穿孔形成工序中,在阻焊层30a形成第二贯穿孔32b,其沿厚度方向将作为第一贯穿孔32a内壁面的一部分的阻焊层30a贯穿。

91.图9b是表示部件搭载工序的一个示例的说明图。搭载装置对在电路板2上的芯片安装区域ca周围的两处贯穿孔32进行识别,并对识别出的贯穿孔32内的识别标记22与绝缘层12a之间的多个交界点y进行识别。进一步地,搭载装置基于多个交界点y,对识别标记22的轮廓进行识别,并由该识别结果计算出识别标记22的中心。然后,搭载装置基于计算出的两处识别标记22的中心,对芯片安装区域ca的位置进行识别。然后,搭载装置基于芯片安装区域ca的位置,如图9b所示,将半导体芯片3的凸块3a以倒装芯片方式接合于电路板2的芯片安装区域ca内的焊盘21a上。也即是说,在将半导体芯片3的凸块3a搭载于阻焊层30a的开口部31a内的焊盘21a上之后,通过加热将焊料熔融一次来使阻焊层30a的开口部31a由焊料填满。图9c是表示半导体装置1的成品的一个示例的说明图。在以倒装芯片方式接合的半导体芯片3与电路板2之间填充底部填充树脂4,并将该底部填充树脂4进行固化。其结果,能够如图9c所示制造出半导体装置1的成品。

92.图10是表示多个电路板2的一个示例的示意平面图。在基板上,沿纵横方向配置有多个用于搭载半导体芯片3的、平面形状为矩形的芯片安装区域ca。在每个芯片安装区域ca中,一侧贯穿孔321(32)与另一侧贯穿孔322(32)以相对的方式配置于在该芯片安装区域ca的大致对角线上的芯片安装区域ca的外侧位置。即,以芯片安装区域ca为中心,一侧贯穿孔321和另一侧贯穿孔322呈点对称的配置关系。一侧贯穿孔321包括:一侧第一贯穿孔32a1;以及形成于一侧第一贯穿孔32a1的内壁面的第一位置(附图中的右侧)的一侧第二贯穿孔32b1。即,一侧第二贯穿孔32b1形成于一侧第一贯穿孔32a1的图中右侧的内壁面(第一位置)。另一侧贯穿孔322包括:另一侧第一贯穿孔32a2;以及形成于另一侧第一贯穿孔32a2的内壁面的与第一位置不同的第二位置(附图中的左侧)的另一侧第二贯穿孔32b2。即,另一侧第二贯穿孔32b2形成于另一侧第一贯穿孔32a2的图中左侧的内壁面(第二位置)。

93.在搭载装置中,着眼于相对于第一贯穿孔32a的第二贯穿孔32b的形成位置,从而识别位于第一位置的一侧第二贯穿孔32b1及位于第二位置的另一侧第二贯穿孔32b2。然后,搭载装置能够通过识别出的一侧第二贯穿孔32b1及另一侧第二贯穿孔32b2,从而识别每个芯片安装区域ca的一对一侧贯穿孔321和另一侧贯穿孔322。然后,搭载装置基于一侧贯穿孔321内的圆形的识别标记22的中心和另一侧贯穿孔322内的圆形的识别标记22的中心,识别出芯片安装区域ca的位置。其结果,即使在多个贯穿孔32相邻的情况下,也能够避免对每个芯片安装区域ca的一对一侧贯穿孔321和另一侧贯穿孔322进行误识别。

94.本实施例的电路板2包括:作为最上层配线的布线图案20a;以及覆盖布线图案20a的阻焊层30a,布线图案20a具有形成为平面形状呈圆形的识别标记22的布线图案20a2。阻焊层30a具有平面形状为异形的贯穿孔32,其以使布线图案20a2的整个上表面露出的方式,沿该阻焊层30a的厚度方向贯穿阻焊层30a。其结果,由于贯穿孔32为异形,因而异形的贯穿孔32当然容易识别,贯穿孔32内的识别标记22也变得容易识别,从而能够提供识别性优越的识别标记22。而且,即使在贯穿孔32相对布线图案20a偏移的情况下,由于贯穿孔32的平

面形状为异形,因此也能够识别出贯穿孔32内的识别标记22。即使识别标记22与焊盘21a为同样的圆形,也能够对贯穿孔32进行识别从而避免将识别标记22误识别。

95.进一步地,贯穿孔32包括第一贯穿孔32a和第二贯穿孔32b。第一贯穿孔32a以使布线图案20a2的整个上表面露出的方式,沿厚度方向贯穿阻焊层30a,其为平面形状呈圆形的贯穿孔。第二贯穿孔32b为沿厚度方向贯穿作为第一贯穿孔32a内壁面的一部分的阻焊层30a的贯穿孔。其结果,能够简单地由第一贯穿孔32a及第二贯穿孔32b形成异形的贯穿孔32。

96.第一贯穿孔32a及布线图案20a2的平面形状为圆形,第一贯穿孔32a的口径大于布线图案20a2的直径。进一步地,以第一贯穿孔32a内的内壁面与布线图案20a2的侧壁不接触的方式,将布线图案20a2配置于第一贯穿孔32a内。其结果,即使识别标记22及焊盘21a的平面形状都为圆形,也能够以异形的贯穿孔32来识别圆形的识别标记22。

97.布线图案20a包括其至少一部分作为焊盘21a从阻焊层30a露出的布线图案20a1,布线图案20a1与布线图案20a2形成为相同的厚度。其结果,能够在同一工序中同时形成布线图案20a1及布线图案20a2(参见图8a),并且能够在同一工序形成焊盘21a及识别标记22(参见图9a)。

98.此外,上文对识别标记22的平面形状为圆形的情况进行了示例,但识别标记22的平面形状不限于圆形,也可以为大致圆形、有角的形状或异形,能够进行适当的变更。

99.上文示例了贯穿孔32由平面形状为圆形的第一贯穿孔32a及平面形状为半圆形的第二贯穿孔32b构成的情况。然而,本发明并不限于此,第二贯穿孔32b的平面形状也可以为如图11a~图11d所示的形状,能够进行适当的变更。图11a是表示识别标记22及贯穿孔32的一个示例的示意平面图。识别标记22的平面形状为圆形,第一贯穿孔32a的平面形状为圆形。但也可以将平面形状为半圆形的第二贯穿孔32b替换为如图11a所示的平面形状为长方形的第二贯穿孔32c。

100.图11b是表示识别标记22及贯穿孔32的一个示例的示意平面图。识别标记22的平面形状为圆形,第一贯穿孔32a的平面形状为圆形。但也可以将平面形状为半圆形的第二贯穿孔32b替换为如图11b所示的平面形状长半圆形的第二贯穿孔32d。

101.图11c是表示识别标记22及贯穿孔32的一个示例的示意平面图。识别标记22的平面形状为圆形,第一贯穿孔32a的平面形状为圆形。但也可以将平面形状为半圆形的第二贯穿孔32b替换为如图11c所示的平面形状为正方形的第二贯穿孔32e。

102.图11d是表示识别标记22及贯穿孔32的一个示例的示意平面图。识别标记22的平面形状为圆形,第一贯穿孔32a的平面形状为圆形。但平面形状为半圆形的第二贯穿孔32b可以不是一个而是多个。可以将一个第二贯穿孔32b替换为例如三个半圆形的第二贯穿孔32f。

103.例如,在根据由识别标记22等的表面反射出的反射光的强度来检测识别标记22的情况下,能够增大识别标记22与绝缘层12a的反射光的强度之差。其结果,识别标记22与绝缘层12a的交界部分,即识别标记22的轮廓得以突出强调,因此能够提高识别标记22的识别性。

104.通过将识别标记22以使贯穿孔32的内壁面与识别标记22的侧壁面隔开的方式配置于贯穿孔32内的绝缘层12a上,从而突出强调了识别标记22的轮廓,因此能够容易地识别

出识别标记22。

105.作为本实施例的电路板2,对具有呈矩阵状配设的焊盘21a的电路板2进行了说明,但也可以适用于具有呈外围状配设的焊盘的电路板。

106.上文中示例了在第二开口形成工序中,在形成贯穿孔32时,在第一贯穿孔形成工序中形成第一贯穿孔32a之后,在第二贯穿孔形成工序中在第一贯穿孔32a的内壁面形成第二贯穿孔32b的情况。然而,也可以在执行了第二贯穿孔形成工序之后,再执行第一贯穿孔形成工序。此外,还可以不分别单独执行第一贯穿孔形成工序及第二贯穿孔形成工序,而是一次性形成具有第一贯穿孔32a及第二贯穿孔32b的贯穿孔32,能够进行适当的变更。

107.上文中示例了阻焊层30例如使用环氧树脂等绝缘性的非感光性树脂的情况。这种情况下,作为在阻焊层30上形成贯穿孔32以及开口部31a(31b)的方法而示例了激光加工。然而,阻焊层30例如还可以使用丙烯酸树脂及聚酰亚胺树脂等绝缘性的感光性树脂。这种情况下,作为在阻焊层30上形成贯穿孔32以及开口部31a(31b)的方法,可以采用曝光

·

显影,能够进行适当的变更。此外,例如还可以使用喷砂处理、湿喷砂处理或树脂蚀刻处理来在阻焊层30上形成贯穿孔32以及开口部31a(31b),能够进行适当的变更。

108.本实施例中用于形成焊盘21a的开口部31a的形状为圆形,但并不限于此。此外,例如还可以不仅仅将布线图案21a1的表面的一部分而是整个表面作为焊盘21a露出的方式形成开口部31a。

109.在本实施例中,对识别了电路板2的识别标记22之后在芯片安装区域ca安装半导体芯片3的情况进行了说明,但被安装体并不限于半导体芯片3。被安装体可以适当的变更,例如,可以是使用识别标记22在电路板2的预设区域上层叠其他电路板的结构的倒装芯片封装(叠层封装,package on package),以代替半导体芯片3。

110.在本实施例中,并不特别对布线图案20a的下层的结构进行限定。此外,并不特别对芯基材11的结构及材质进行限定。此外,并不特别对形成于芯基材11上的下层配线(例如配线13a、13b)和将其覆盖的绝缘层(例如绝缘层12a、12b)的层数进行限定。即,也可以在芯基材11上形成预设数量的下层配线和将其覆盖的绝缘层。此外,并不特别对布线图案20a的图案形状进行限定。

111.并不限定于具有芯的芯基材11,还能够适用于无芯基板或外层的配线被埋入绝缘层而形成的ets(embedded trace substrate:嵌入式迹线基板)等常用的各种基板。

112.形成于本实施例的布线图案20a(20b)上的并不限定于阻焊层30,只要是绝缘层即可。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。