1.本发明的一个方式涉及一种显示装置。另外,本发明的一个方式涉及一种电子设备。

2.注意,本发明的一个方式不局限于上述技术领域。作为本发明的一个方式的技术领域的例子,可以举出半导体装置、显示装置、发光装置、显示系统、电子设备、照明装置、输入装置(例如,触摸传感器等)、输入输出装置(例如,触摸面板等)、这些装置的驱动方法或这些装置的制造方法。

3.注意,在本说明书等中,半导体装置是指能够通过利用半导体特性而工作的所有装置。有时可以将显示装置(液晶显示装置、发光显示装置等)、投影装置、照明装置、电光装置、蓄电装置、存储装置、半导体电路、摄像装置及电子设备等称为半导体装置。或者,有时可以说它们包括半导体装置。

背景技术:

4.此外,作为设置有用来增强现实(ar:augmented reality)或虚拟现实(vr:virtual reality)的显示装置的电子设备,可穿戴型电子设备及固定式电子设备逐渐普及。作为可穿戴型电子设备,例如,有头戴显示器(hmd:head mounted display)及眼镜型的电子设备等。作为固定式电子设备,例如,有平视显示器(hud:head-up display)等。

5.hmd等显示部离使用者近的电子设备有如下问题:使用者容易看到像素而可能感到很强的颗粒感,有时会减弱ar或vr的沉浸感及临场感。因此,hmd优选设置有像素密度高的显示装置,以使使用者看不到像素。该显示装置的像素密度优选为例如1000ppi以上、5000ppi以上或7000ppi以上。专利文献1公开了通过使用能够进行高速驱动的晶体管来实现像素密度高的hmd的方法。

6.[先行技术文献]

[0007]

[专利文献]

[0008]

[专利文献1]日本专利申请公开第2000-2856号公報

技术实现要素:

[0009]

发明所要解决的技术问题

[0010]

通过显示装置包含精细像素,可以提高像素密度。由此,可以在显示装置设置许多像素。另一方面,当在显示装置设置许多像素时,显示装置的功耗变大。由此,显示装置被电池供应电力时,有时能够连续使用设置有显示装置的电子设备的期间变短。此外,使能够连续使用设置有显示装置的电子设备的期间变长时,电池大型化及有时变重。设置有显示装置的电子设备中内置的电池大型化时,电子设备有时大型化。另外,电子设备中内置的电池变重时,电子设备有时变重。尤其是,可穿戴型电子设备中内置的电池变重时,电子设备的使用者的负担增加,有时使用者容易感到疲劳。

[0011]

本发明的一个方式的目的之一是提供一种低功耗的显示装置。此外,本发明的一

个方式的目的之一是提供一种能够显示高质量图像的显示装置。此外,本发明的一个方式的目的之一是提供一种高速驱动的显示装置。此外,本发明的一个方式的目的之一是提供一种可靠性高的显示装置。此外,本发明的一个方式的目的之一是提供一种新颖的显示装置。此外,本发明的一个方式的目的之一是提供一种上述显示装置的驱动方法。此外,本发明的一个方式的目的之一是提供一种设置有上述显示装置的电子设备。此外,本发明的一个方式的目的之一是提供一种新颖的半导体装置及其驱动方法等。

[0012]

注意,这些目的的记载不妨碍其他目的的存在。本发明的一个方式并不需要实现所有上述目的。可以从说明书、附图、权利要求书的记载中抽取上述目的以外的目的。

[0013]

解决技术问题的手段

[0014]

本发明的一个方式是一种显示装置,包括多个显示部、多个数据驱动电路及多个附加电路。在显示部中像素排列为矩阵状。此外,例如在上层设置显示部,在下层以具有与显示部重叠的区域的方式设置数据驱动电路及附加电路。数据驱动电路的输出端子与附加电路的输入端子电连接。附加电路的输出端子在每个列中通过数据线与像素电连接。就是说,数据驱动电路与像素之间设置有附加电路。数据驱动电路具有进行d/a转换的功能。

[0015]

在本发明的一个方式,首先,数据驱动电路将由第一数字值构成的第一数字数据转换为第一模拟数据,将由第二数字值构成的第二数字数据转换为第二模拟数据。然后,附加电路对第一模拟数据附加第二模拟数据。由此,附加电路可以生成第一数字值为高位且第二数字值为低位时的数字数据对应的模拟数据。由此,附加电路可以生成模拟数据而写入像素,该模拟数据对应于比数据驱动电路可以进行d/a转换的数字数据的位数更多的位数的数字数据。附加电路所生成的模拟数据通过数据线供应到像素。

[0016]

通过设置多个显示部,可以减少一个显示部中的像素的列数。由此,可以缩短数据线的长度,所以可以抑制对应于附加电路所生成的模拟数据的电位写入到像素之前衰减。

[0017]

此外,通过数据驱动电路与像素之间设置附加电路,将对应于比数据驱动电路可以进行d/a转换的数字数据的位数更多的位数的数字数据的模拟数据写入像素。因此,可以减少数据驱动电路可以进行d/a转换的数字数据的位数。由此,可以简化数据驱动电路的结构。由此,可以抑制数据驱动电路生成的对应于第一模拟数据的电位及对应于第二模拟数据的电位在数据驱动电路内部衰减。

[0018]

因此,在本发明的一个方式可以抑制数据驱动电路所生成的电位写入像素之前衰减。由此,在数据驱动电路与附加电路之间不设置缓冲放大器等,也不会大幅度降低本发明的一个方式的显示装置的驱动速度。因此,数据驱动电路的输出端子与附加电路的输入端子不通过缓冲放大器等可以直接连接。此外,即使在附加电路与像素之间不设置缓冲放大器等,也不会大幅度降低本发明的一个方式的显示装置的驱动速度。因此,附加电路的输出端子与像素可以直接连接而不通过缓冲放大器等。由此,本发明的一个方式的显示装置可以为低功耗的显示装置。

[0019]

本发明的一个方式是一种显示装置,包括:叠层的第一层和第二层,第一层包括电位供应电路、多个数据驱动电路及多个附加电路,数据驱动电路包括传输晶体管逻辑电路,第二层包括像素排列为矩阵状的多个显示部,多个显示部分别包括与数据驱动电路及附加电路重叠的区域,传输晶体管逻辑电路的输出端子与附加电路的输入端子直接连接,附加电路的输出端子与像素直接连接,电位供应电路具有对传输晶体管逻辑电路供应多种电位

的功能,传输晶体管逻辑电路具有根据对传输晶体管逻辑电路所输入的数字数据作为模拟数据输出多种电位中的任一个的功能,附加电路具有通过对通过第一数字数据输入到传输晶体管逻辑电路被输出的第一模拟数据附加通过第二数字数据输入到传输晶体管逻辑电路被输出的第二模拟数据生成第三模拟数据的功能。

[0020]

在上述方式中,附加电路可以包括第一开关、第二开关、第三开关及电容器,传输晶体管逻辑电路的输出端子与第一开关的一个端子可以直接连接,第一开关的一个端子与第二开关的一个端子可以电连接,第一开关的另一个端子与像素可以直接连接,电容器的一个端子与像素可以电连接,电容器的另一个端子与第二开关的另一个端子及第三开关的一个端子可以电连接。

[0021]

本发明的一个方式是一种显示装置,包括:叠层的第一层和第二层,第一层包括电位供应电路、多个数据驱动电路及多个附加电路,数据驱动电路包括传输晶体管逻辑电路,附加电路包括第一开关、第二开关、第三开关、第四开关、第五开关、第六开关、第一电容器、第二电容器、比较器电路、控制电路及保持电路,第二层包括像素排列为矩阵状的多个显示部,多个显示部分别包括与数据驱动电路及附加电路重叠的区域,传输晶体管逻辑电路的输出端子与第一开关的一个端子直接连接,第一开关的一个端子与第二开关的一个端子电连接,第二开关的另一个端子与第三开关的一个端子电连接,第一开关的另一个端子与像素直接连接,第一开关的另一个端子与第四开关的一个端子、第五开关的一个端子及第六开关的一个端子电连接,第五开关的另一个端子与第一电容器的一个端子电连接,第六开关的另一个端子与第二电容器的一个端子电连接,第一电容器的另一个端子及第二电容器的另一个端子与第三开关的一个端子电连接,第四开关的另一个端子与比较器电路的非反相输入端子或反相输入端子的一方电连接,电位供应电路具有对传输晶体管逻辑电路供应多种电位的功能,传输晶体管逻辑电路具有根据对传输晶体管逻辑电路所输入的数字数据作为模拟数据输出多种电位中的任一个的功能,附加电路具有通过对通过第一数字数据输入到传输晶体管逻辑电路被输出的第一模拟数据附加通过第二数字数据输入到传输晶体管逻辑电路被输出的第二模拟数据生成而保持第三模拟数据的功能,控制电路具有生成控制第五开关的开启/关闭及第六开关的开启/关闭的数字信号的功能,控制电路具有第三模拟数据保持在附加电路的情况下根据比较器电路输出的信号更新或确定数字信号的数字值的功能,保持电路具有保持被确定的数字信号的数字值的功能。

[0022]

在上述方式中,第三模拟数据可以相当于第一数字数据包含的数字值为高位且第二数字数据包含的数字值为低位时的数字数据转换为模拟数据的数据。

[0023]

此外,在上述方式中,电位供应电路可以包括多个放大电路,多个放大电路分别可以具有将彼此不同的电位输出到电位供应电路的功能。

[0024]

在上述方式中,可以对第三开关的另一个端子供应恒电位,通过第一及第三开关为开启状态且第二开关为关闭状态,可以写入第一模拟数据到附加电路,写入第一模拟数据到附加电路之后,通过第二开关为开启状态且第一及第三开关为关闭状态,可以写入第二模拟数据到附加电路以及生成第三模拟数据。

[0025]

在上述方式中,像素可以包括在沟道形成区域中包含金属氧化物的晶体管,金属氧化物可以包含in、元素m(m为al、ga、y或sn)及zn。

[0026]

包括本发明的一个方式的显示装置及电池的电子设备也是本发明的一个方式。

[0027]

发明效果

[0028]

根据本发明的一个方式,可以提供一种低功耗的显示装置。此外,根据本发明的一个方式,可以提供一种能够显示高质量图像的显示装置。此外,根据本发明的一个方式,可以提供一种高速驱动的显示装置。此外,根据本发明的一个方式,可以提供一种可靠性高的显示装置。此外,根据本发明的一个方式,可以提供一种新颖的显示装置。此外,根据本发明的一个方式,可以提供一种上述显示装置的驱动方法。此外,根据本发明的一个方式,可以提供一种设置有上述显示装置的电子设备。此外,根据本发明的一个方式,可以提供一种新颖的半导体装置及其驱动方法等。

[0029]

注意,这些效果的记载不妨碍其他效果的存在。本发明的一个方式并不需要具有所有上述效果。可以从说明书、附图、权利要求书的记载中抽取上述效果以外的效果。

附图说明

[0030]

图1是示出显示装置的结构例子的方框图。

[0031]

图2是示出显示装置的结构例子的方框图。

[0032]

图3是示出显示装置的结构例子的电路图。

[0033]

图4是示出显示装置的结构例子的电路图。

[0034]

图5a1及图5a2和图5b1及图5b2是示出像素的结构例子的电路图。

[0035]

图6是示出显示装置的结构例子的电路图。

[0036]

图7是示出显示装置的驱动方法的一个例子的时序图。

[0037]

图8是示出显示装置的结构例子的电路图。

[0038]

图9是示出显示装置的结构例子的电路图。

[0039]

图10是示出显示装置的结构例子的电路图。

[0040]

图11是示出显示装置的驱动方法的一个例子的时序图。

[0041]

图12是示出显示装置的驱动方法的一个例子的时序图。

[0042]

图13是示出显示装置的结构例子的方框图。

[0043]

图14是示出显示装置的结构例子的方框图。

[0044]

图15是示出显示装置的结构例子的方框图。

[0045]

图16是示出显示装置的结构例子的电路图。

[0046]

图17是示出显示装置的结构例子的方框图。

[0047]

图18是示出显示装置的结构例子的方框图。

[0048]

图19是示出显示装置的结构例子的方框图。

[0049]

图20是示出显示装置的结构例子的方框图。

[0050]

图21是示出显示装置的结构例子的方框图。

[0051]

图22是示出显示装置的结构例子的方框图。

[0052]

图23是示出显示装置的结构例子的截面图。

[0053]

图24是示出显示装置的结构例子的截面图。

[0054]

图25是示出显示装置的结构例子的截面图。

[0055]

图26是示出显示装置的结构例子的截面图。

[0056]

图27是示出显示装置的结构例子的截面图。

[0057]

图28是示出显示装置的结构例子的截面图。

[0058]

图29a是示出晶体管的结构例子的俯视图。图29b及图29c是示出晶体管的结构例子的截面图。

[0059]

图30a是示出晶体管的结构例子的俯视图。图30b及图30c是示出晶体管的结构例子的截面图。

[0060]

图31a是示出晶体管的结构例子的俯视图。图31b及图31c是示出晶体管的结构例子的截面图。

[0061]

图32a是示出晶体管的结构例子的俯视图。图32b及图32c是示出晶体管的结构例子的截面图。

[0062]

图33a是说明igzo的结晶结构的分类的图。图33b是说明caac-igzo膜的xrd谱的图。图33c是说明caac-igzo膜的纳米束电子衍射图案的图。

[0063]

图34a至图34d是示出电子设备的一个例子的图。

[0064]

图35a至图35f是示出电子设备的一个例子的图。

具体实施方式

[0065]

以下,参照附图对实施方式进行说明。但是,实施方式可以以多个不同方式来实施,所属技术领域的普通技术人员可以很容易地理解一个事实,就是其方式和详细内容可以被变换为各种各样的形式而不脱离本发明的宗旨及其范围。因此,本发明不应该被解释为仅限定在下面所示的实施方式所记载的内容中。

[0066]

在本说明书所说明的附图中,为便于清楚地说明,有时夸大表示各结构的大小、层的厚度或区域。因此,本发明并不局限于附图中的尺寸。此外,在附图中,示意性地示出理想的例子,因此本发明不局限于附图所示的形状或数值等。例如,在实际的制造工序中,有时由于蚀刻等处理而层或抗蚀剂掩模等被非意图性地被减薄,但是为了便于理解有时没有反映到附图。此外,在附图中,有时在不同的附图之间共同使用相同的附图标记来表示相同的部分或具有相同功能及材料等的部分,而省略其重复说明。此外,当表示具有相同功能及材料等的部分时有时使用相同的阴影线,而不特别附加附图标记。

[0067]

另外,本说明书所使用的“第一”、“第二”、“第三”等序数词是为了避免构成要素的混淆而附加的,而不是为了在数目方面上进行限定的。

[0068]

在本说明书等中,为方便起见,使用了“上”、“下”等表示配置的词句,以参照附图说明构成要素的位置关系。另外,构成要素的位置关系根据描述各构成要素的方向适当地改变。因此,不局限于说明书中所说明的词句,根据情况可以适当地换词句。

[0069]

此外,在本说明书等中,在晶体管的极性或电路工作中的电流方向变化等的情况等下,晶体管所包括的源极及漏极的功能有时相互调换。因此,源极和漏极可以相互调换。

[0070]

此外,在本说明书等中,“电极”、“布线”、“端子”等的词句不在功能上限定其构成要素。例如,有时将“电极”用作“布线”的一部分,反之亦然。再者,“电极”或“布线”还包括多个“电极”或“布线”被形成为一体的情况等。此外,例如,有时将“端子”用作“布线”或“电极”的一部分,反之亦然。再者,“端子”的词句包括多个“电极”、“布线”、“端子”等被形成为一体的情况等。因此,例如,“电极”可以为“布线”或“端子”的一部分,例如,“端子”可以为“布线”或“电极”的一部分。此外,“电极”、“布线”、“端子”等的词句有时置换为“区域”等的词句。

[0071]

此外,在本说明书等中,“电阻器”的电阻值有时取决于布线的长度。或者,电阻值有时通过连接到其电阻率与布线所使用的导电层不同的导电层而被决定。另外,电阻值有时通过对半导体层掺杂杂质而被决定。

[0072]

在本说明书等中,“电连接”包括直接连接的情况及通过“具有某种电作用的元件”连接的情况。这里,“具有某种电作用的元件”只要可以进行连接对象间的电信号的授受,就对其没有特别的限制。因此,即便记载为“电连接”,在实际电路中有时存在没有物理连接的部分而只是布线延伸的情况。此外,即便记载为“直接连接”,也包括通过触点以不同导电层体形成布线的情况。此外,作为布线,不同导电层有时包含一个以上的同一元素或者有时包含不同元素。

[0073]

在本说明书等中,“膜”和“层”可以相互调换。例如,可以将“导电层”变换为“导电膜”。此外,例如,可以将“绝缘膜”变换为“绝缘层”。

[0074]

另外,在本说明书等中,在没有特别的说明的情况下,关态电流是指晶体管处于关闭状态(也称为非导通状态、遮断状态)时的漏极电流。在没有特别的说明的情况下,在n沟道晶体管中,关闭状态是指栅极与源极间的电压v

gs

低于阈值电压v

th

(p沟道型晶体管中v

gs

高于v

th

)的状态。

[0075]

在本说明书等中,金属氧化物(metal oxide)是指广义上的金属的氧化物。金属氧化物被分类为氧化物绝缘体、氧化物导电体(包括透明氧化物导电体)和氧化物半导体(oxide semiconductor,也可以简称为os)等。例如,在将金属氧化物用于晶体管的活性层的情况下,有时将该金属氧化物称为氧化物半导体。换言之,可以将os晶体管称为包含氧化物或氧化物半导体的晶体管。

[0076]

(实施方式1)

[0077]

在本实施方式中,说明本发明的一个方式的显示装置。

[0078]

《显示装置的结构例子_1》

[0079]

图1是示出本发明的一个方式的显示装置的显示装置10的结构例子的方框图。显示装置10包括层20及层30,层30例如可以层叠设置在层20的上方。在层20与层30之间可以设置层间绝缘膜。

[0080]

在层20中设置电路21、电位生成电路22、电位供应电路23l、电位供应电路23r、数据驱动电路24l、数据驱动电路24r、电路25l、电路25r。在此,可以设置多个数据驱动电路24l、多个数据驱动电路24r、多个电路25l及多个电路25r。

[0081]

在层30中设置栅极驱动电路31l、栅极驱动电路31r、显示部32l、显示部32r。在显示部32l中像素33l排列为矩阵状,显示部32r中像素33r排列为矩阵状。在此,可以设置多个显示部32l及多个显示部32r。例如可以设置与数据驱动电路24l相同数量的显示部32l且设置与数据驱动电路24r相同数量的显示部32r。由此,显示装置10可以具有包括多个显示部的结构。就是说,显示装置10具有显示部分割的结构。

[0082]

在本说明书等中,将电位供应电路23l及电位供应电路23r统称为电位供应电路23。此外,将数据驱动电路24l及数据驱动电路24r统称为数据驱动电路24。此外,将电路25l及电路25r统称为电路25。此外,将栅极驱动电路31l及栅极驱动电路31r统称为栅极驱动电路31。此外,将显示部32l及显示部32r统称为显示部32。此外,将像素33l及像素33r统称为像素33。

[0083]

为了明确起见,在图1中未图示像素33l及像素33r与其他的电路的连接关系,但是实际上像素33l与栅极驱动电路31l及电路25l电连接,像素33r与栅极驱动电路31r及电路25r电连接。例如,同一行的像素33l可以通过同一的栅极线与栅极驱动电路31l电连接,同一行的像素33r可以通过同一的栅极线与栅极驱动电路31r电连接。此外,在同一的显示部32l设置的同一列的像素33l可以通过同一的数据线与电路25l电连接,在同一的显示部32r设置的同一列的像素33r可以通过同一的数据线与电路25r电连接。

[0084]

电路21具有从显示装置10的外部接收图像数据等数据的接口的功能。该数据可以为单端的数字数据。在使用lvds(low voltage differential signaling;低电压差分信号)等数据传输用信号接收数据的情况下,电路21也可以具有将该信号转换为能够被进行内部处理的信号规格的功能。

[0085]

此外,电路21也可以具有对上述单端的数字数据并行转换的功能。由此,即使将数据等从电路21传输到数据驱动电路24时的负载较大,也可以将数据从电路21高速传输到数据驱动电路24。

[0086]

电位生成电路22具有生成对电位供应电路23l及电位供应电路23r供应的电位的功能。

[0087]

电位供应电路23l具有从电位生成电路22生成的电位选择对数据驱动电路24l供应的电位的功能。电位供应电路23r具有从电位生成电路22生成的电位选择对数据驱动电路24r供应的电位的功能。

[0088]

数据驱动电路24l具有将从电路21供应的图像数据等数据对电路25l供应的功能。具体而言,数据驱动电路24l具有将从电路21供应的数字数据转换为模拟数据而将该模拟数据供应到电路25l的功能。具体而言,数据驱动电路24l具有根据从电路21供应的数字数据选择从电位供应电路23l供应的电位中的一个而将该电位作为模拟数据供应到电路25l的功能。

[0089]

数据驱动电路24r具有将从电路21供应的图像数据等数据供应到电路25r的功能。数据驱动电路24r的工作可以与数据驱动电路24l的工作相同,例如,根据从电路21供应的数字数据,选择从电位供应电路23r供应的电位中的一个而将该电位作为模拟数据供应到电路25r。

[0090]

由此,数据驱动电路24具有进行d/a(digital to analog)转换的功能。

[0091]

电路25l具有对模拟数据附加其他模拟数据的功能。具体而言,电路25l具有通过对数据驱动电路24l输出的第一模拟数据附加数据驱动电路24l输出的第二模拟数据,生成第三模拟数据的功能。例如,第一数字数据输入到数据驱动电路24l,第一数字数据由数据驱动电路24l转换为第一模拟数据。然后,第二数字数据输入到数据驱动电路24l,第二数字数据由数据驱动电路24l转换为第二模拟数据。在此情况下,通过对第一模拟数据附加第二模拟数据,电路25l生成的模拟数据相当于将第一数字数据包含的数字值为高位且第二数字数据包含的数字值为低位的数字数据转换为模拟数据的数据。

[0092]

与电路25l同样地,电路25r具有对模拟数据附加其他模拟数据的功能。具体而言,电路25r具有通过对数据驱动电路24r输出的第一模拟数据附加数据驱动电路24r输出的第二模拟数据,生成第三模拟数据的功能。

[0093]

栅极驱动电路31l具有选择写入电路25l输出的模拟数据的像素33l的功能。栅极

驱动电路31r具有选择写入电路25r输出的模拟数据的像素33r的功能。

[0094]

显示装置10包括在层20中设置的数据驱动电路24l及电路25l与在层30中设置的显示部32l重叠的区域。此外,还包括数据驱动电路24r及电路25r与显示部32r重叠的区域。

[0095]

在此,在数据驱动电路24l及电路25l不与显示部32l重叠的情况下,例如,数据驱动电路24l及电路25l设置在显示部32l的外围部。在此,从数据驱动电路24l及电路25l的设置位置等的角度来看,难以在显示装置中设置三个以上的显示部32l。同样地,难以在显示装置中设置三个以上的显示部32r。另一方面,在显示装置10中,通过在与显示部32设置的层不同的层中设置数据驱动电路24及电路25,可以以具有与显示部32重叠的区域的方式设置数据驱动电路24及电路25。因此,可以在显示装置10设置三个以上的显示部32l及三个以上的显示部32r。

[0096]

通过设置多个显示部32,并根据该多个显示部32设置数据驱动电路24及电路25,可以减少设置在一个显示部32中的像素33的列数。由此,例如可以缩短电路25与像素33电连接的数据线,所以可以缩小该数据线的布线电阻。因此,例如因为可以高速地进行从电路25到像素33的模拟数据的写入,所以可以高速驱动显示装置10。由此,即使增加显示装置10中的像素33也可以确保充分的帧期间,可以提高显示装置10的像素密度。例如,可以使显示装置10的像素密度为1000ppi以上、5000ppi以上或者7000ppi以上。此外,通过提高显示装置10的像素密度,可以提高显示装置10所显示的图像的分辨率。因此,显示装置10例如可以为ar或vr用显示装置,可以将其适当地用于hmd等显示部与使用者的距离近的电子设备。

[0097]

此外,通过显示装置10包括电路25,可以减少数据驱动电路24进行d/a转换的数字数据的位数。例如,5位的第一数字数据及5位的第二数字数据输入到数据驱动电路24。在此情况下,电路25生成的数据相当于10位的数字数据转换为模拟数据的数据。就是说,即使数据驱动电路24可以进行d/a转换的数字数据的位数的上限为5位,也可以对像素33写入对应于10位的数字数据的模拟数据。

[0098]

电路21、电位生成电路22、电位供应电路23、数据驱动电路24、电路25、栅极驱动电路31及像素33包括晶体管。就是说,在层20及层30中分别设置晶体管。在层20中设置的晶体管例如可以为在沟道形成区域中包含硅的晶体管(也称为si晶体管),例如可以为在沟道形成区域中包含单晶硅的晶体管。尤其是,当作为在层20中设置的晶体管使用在沟道形成区域中包含单晶硅的晶体管时,可以增大该晶体管的通态电流。由此,可以高速驱动电路21、电位生成电路22、电位供应电路23、数据驱动电路24及电路25,所以是优选的。另外,作为在层20中设置的晶体管,也可以使用在沟道形成区域中包含低温多晶硅、氢化非晶硅、微晶硅或多晶硅等的晶体管。此外,作为在层20中的晶体管,也可以使用os晶体管。

[0099]

另一方面,作为在层30中设置的晶体管,例如,可以使用os晶体管。尤其是,作为os晶体管优选使用在沟道形成区域中包括包含铟、元素m(元素m是铝、镓、钇或锡)和锌中的至少一个的氧化物的晶体管。这种os晶体管具有关态电流极低的特性。因此,尤其是,在作为像素33中设置的晶体管使用os晶体管时,可以由像素33长期间保持写入到像素33的模拟数据,所以是优选的。

[0100]

另外,作为在层30中设置的晶体管,也可以使用si晶体管。例如,也可以使用在沟道形成区域中包含低温多晶硅、氢化非晶硅、微晶硅或多晶硅等的晶体管。

[0101]

此外,可以不使在层20中设置的所有的晶体管为相同种类的晶体管,也可以不使

在层30中设置的所有的晶体管为相同种类的晶体管。例如,在层30中设置的晶体管中,也可以具有如下结构:在栅极驱动电路31设置的晶体管为si晶体管,在像素33中设置的晶体管为os晶体管。此外,例如,也可以具有如下结构:在像素33设置的晶体管中一部分的晶体管为si晶体管且其他的晶体管为os晶体管。

[0102]

图2是示出数据驱动电路24、电路25及显示部32的结构例子的方框图。注意,为了示出连接关系,在图2中还示出电路21、电位生成电路22、电位供应电路23及栅极驱动电路31。

[0103]

在显示部32,像素33配置为m行n列(m、n为1以上的整数)的矩阵状。此外,同一行的像素33通过同一的布线34与栅极驱动电路31电连接,同一列的像素33与同一的布线26电连接。在此,布线34为栅极线,布线26为数据线。

[0104]

在本说明书等中,在多个要素使用同一符号并且需要区别它们时,有时对符号附加“[m]”、“[m,n]”、“(0)”、“(1)”、“《0》”、“《1》”等用于识别的符号。例如,将第1行第1列的像素33表示为像素33[1,1],将第m行第n列的像素33表示为像素33[m,n]。此外,例如将与第1行的像素33电连接的布线34表示为布线34[1],将与第m行的像素33电连接的布线34表示为布线34[m]。另外,例如将与第1列的像素33电连接的布线26表示为布线26[1],将与第n列的像素33电连接的布线26表示为布线26[n]。有时也对其他要素进行相同记载。

[0105]

数据驱动电路24包括n个寄存电路42、n个锁存电路43、n个电平转换电路44、n个传输晶体管逻辑电路45。由寄存电路42[1]至寄存电路42[n],可以构成移位寄存电路41。另外,传输晶体管逻辑电路45的输出端子与布线27电连接。

[0106]

电路21输出的图像数据等数字数据供应到锁存电路43[1]至锁存电路43[n]。此外,电位供应电路23可以供应电位到传输晶体管逻辑电路45[1]至传输晶体管逻辑电路45[n]。

[0107]

寄存电路42具有生成控制锁存电路43的驱动的信号的功能。例如,当对寄存电路42[1]供应起始脉冲时,从寄存电路42[1]至寄存电路42[n]依次输出控制锁存电路43[1]至锁存电路43[n]的驱动的信号。

[0108]

锁存电路43具有保持或输出从电路21所输出的数字数据的功能。根据从寄存电路42供应到锁存电路43的信号,锁存电路43选择进行数字数据的保持还是输出。

[0109]

电平转换电路44具有改变表示从锁存电路43所输出的数字数据的信号的电位电平的功能。具体而言,电平转换电路44具有将表示从锁存电路43所输出的数字数据的信号的电位电平改变为传输晶体管逻辑电路45能够处理的电位电平的功能。

[0110]

传输晶体管逻辑电路45具有根据电平转换电路44所输出的数字数据的数字值输出从电位供应电路23供应到传输晶体管逻辑电路45的任一电位作为模拟数据的功能。例如,上述数字值越大,传输晶体管逻辑电路45所输出的电位越提高。

[0111]

由此,可以由电位供应电路23及传输晶体管逻辑电路45构成d/a转换电路。

[0112]

电路25包括n个附加电路50。附加电路50的输入端子与布线27电连接,附加电路50的输出端子与布线26电连接。如上所述,除了附加电路50的输入端子以外,布线27与数据驱动电路24包括的传输晶体管逻辑电路45的输出端子电连接。因此,数据驱动电路24从布线27输出数据。由此,布线27为数据线。

[0113]

在后面说明详细内容,在此传输晶体管逻辑电路45的输出端子与附加电路50的输

入端子可以通过布线27直接连接。此外,附加电路50的输出端子与像素33可以通过布线26直接连接。

[0114]

在本说明书等中,“x与y直接连接”是指以中间不夹有其他元件或电路的方式连接x与y。例如,x与y直接连接的情况下,x与y连接而不通过放大电路。此外,x与y通过电阻元件连接的情况下,可以说x与y直接连接。

[0115]

附加电路50具有通过对传输晶体管逻辑电路45所输出的第一模拟数据附加传输晶体管逻辑电路45所输出的第二模拟数据生成第三模拟数据的功能。此外,附加电路50具有保持所生成的第三模拟数据的功能。

[0116]

图3是示出电位生成电路22、电位供应电路23及传输晶体管逻辑电路45的具体的结构例子的电路图。注意,为了示出连接关系,图3还示出电平转换电路44及附加电路50。此外,作为一个例子,在图3中,5位的数字数据dd输入到数据驱动电路24。并且,作为一个例子,在图3中电位生成电路22生成256种电位,将这些电位中的32种电位供应到电位供应电路23。

[0117]

在本说明书等中,例如,将5位的数字数据dd包含的各位从低位依次记载为数字数据dd《0》至数字数据dd《4》。例如,数字数据dd的位数为5的情况下,数字数据dd《0》表示最低位,数字数据dd《4》表示最高位。

[0118]

电位生成电路22包括电阻器101(0)至电阻器101(254)及选择电路104。电阻器101(0)至电阻器101(254)串联连接来构成电阻串100。电阻器101(0)的一端与布线102电连接,对布线102可以供应电位vdd。另外,电阻器101(254)的一端与布线103电连接,对布线103可以供应电位vss。在此,电位vdd可以为比电位vss高电位。电阻器101(0)至电阻器101(254)的一端及另一端与选择电路104电连接。由此,可以将最高的电位设定为电位vdd,最低的电位设定为电位vss的256种电位供应到选择电路104。此外,例如通过将比图3所示的电阻器101的个数更多的电阻器101设置在电阻串100,也可以不供应电位vdd或电位vss的一方或双方到选择电路104。

[0119]

选择电路104具有在电阻串100输出的电位中选择供应到电位供应电路23的电位的功能。在图3中示出选择电路104具有在电阻串100所输出的256种电位中选择供应到电位供应电路23的32种电位的功能的例子。该32种电位分别设定为电位vdac0至电位vdac

31

。例如,为了对输入到电路21的图像数据可以进行伽马校正等的图像处理,选择电路104具有选择供应到电位供应电路23的电位的功能。

[0120]

电位供应电路23包括放大电路51。例如,电位供应电路23可以包括与电位生成电路22所输出的电位的种类个数相同数量的放大电路51。在图3中示出,电位供应电路23包括放大电路51(0)至放大电路51(31),即包括32个放大电路51的例子。

[0121]

选择电路104所输出的电位vdac0至电位vdac

31

各自输入到放大电路51(0)至放大电路51(31)的输入端子,例如输入到非反相输入端子。对放大电路51输入的电位被放大电路51放大而输入到传输晶体管逻辑电路45。放大电路51例如可以为单位增益缓冲器。此外,放大电路51的增益可以为大于1。

[0122]

如上所述,通过显示装置10包括电路25,可以减少数字数据dd的位数。例如,对像素33写入对应于10位的数字数据的模拟数据的情况下,数字数据dd也可以为9位以下的数字数据。因此,可以减少数据驱动电路24进行d/a转换的数字数据的位数。由此,可以减少电

位供应电路23对传输晶体管逻辑电路45输出的电位的种类个数。因此,可以不需将电位供应电路23设为电阻串型而抑制电位供应电路23的占有面积大幅度增加。当将电位供应电路23设为电阻串型时电流从该电阻串的一端流过另一端,所以显示装置10的功耗变大。由此,例如通过电位供应电路23为图3所示的结构,可以降低显示装置10的功耗。

[0123]

传输晶体管逻辑电路45包括晶体管52。图3所示的传输晶体管逻辑电路45由五级晶体管52构成。具体而言,每一级的电路分支为两个路径,传输晶体管逻辑电路45一共有32个路径。也就是说,晶体管52以淘汰赛图方式电连接。作为最后一级的第五级晶体管52的源极和漏极中的一个可以为传输晶体管逻辑电路45的输出端子而与布线27电连接。传输晶体管逻辑电路45可以从布线27输出模拟数据ad。

[0124]

具体而言,数字数据dd《0》可以供应到第一级晶体管52,数字数据dd《1》可以供应到第二级晶体管52,数字数据dd《2》可以供应到第三级晶体管52,数字数据dd《3》可以供应到第四级晶体管52,数字数据dd《4》可以供应到第五级晶体管52。由此,根据数字数据dd的数字值,可以将布线27的电位设为电位vdac0至电位vdac

31

中任一对应的电位。因此,可以将数字数据dd转换为模拟数据ad。

[0125]

此外,图3所示的传输晶体管逻辑电路45包括n沟道型晶体管52及p沟道型晶体管52的双方,但是也可以只设置n沟道型晶体管52。例如,除了数字数据dd《0》至数字数据dd《4》以外,还可以将其互补数据供应到晶体管52的栅极,以使设置在传输晶体管逻辑电路45中的晶体管52都由n沟道型晶体管构成。

[0126]

如上所述,传输晶体管逻辑电路45具有根据例如电平转换电路44输出的数字数据dd的数字值输出从电位供应电路23供应到传输晶体管逻辑电路45的电位vdac0至电位vdac

31

中任一对应的电位作为模拟数据ad的功能。因此,d/a转换电路可以由电位供应电路23及传输晶体管逻辑电路45构成。该d/a转换电路为d/a转换电路40。

[0127]

如上所述,通过显示装置10包括电路25,可以减少数字数据dd的位数。由此,可以减少d/a转换电路40可以进行d/a转换的数字数据的位数。在此,传输晶体管逻辑电路45包括的晶体管52的级数例如可以与数字数据dd的位数相同。通过减少d/a转换电路40可以进行d/a转换的数字数据的位数,可以减少晶体管52的级数。由此,可以抑制从电位供应电路23供应到传输晶体管逻辑电路45的电位在从布线27输出作为模拟数据ad之前因晶体管52的漏极-源极间的电阻等而被衰减。

[0128]

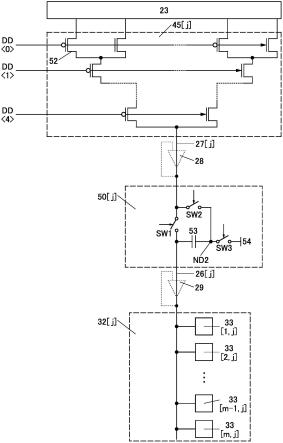

图4是示出布线26[j](j为1以上且n以下的整数)的寄生电容及布线电阻、像素33[1,j]至像素33[m,j]的结构例子、附加电路50[j]的结构例子的电路图。此外,在图4示出传输晶体管逻辑电路45[j],以示出与附加电路50[j]之间连接关系。

[0129]

如上所述,在图4所示的布线26[j]中表示布线26[j]包括的寄生电容及布线电阻。具体而言,布线26[j]对一个像素33包括电阻器rp作为布线电阻,包括电容器cp作为寄生电容。图4所示的显示部32的一列中设置m个像素33,布线26[j]包括串联连接的m个电阻器rp及并联连接的m个电阻器cp。另外,在图4示出一个像素33电连接于电容器cp的一个端子与电阻器rp的一个端子的电连接点。

[0130]

被用作寄生电容的电容器cp的另一个端子与布线lp电连接。布线lp可以为例如包括与布线26重叠的区域的布线34等。

[0131]

像素33包括开关swc及电路60。开关swc的一个端子与电路60电连接。此外,开关

swc的另一个端子与布线26电连接。在此,开关swc的一个端子与电路60电连接的节点为节点nd1。

[0132]

电路60包括显示元件。作为显示元件,例如可以使用有机发光元件、led(light emitting diode)元件等发光元件。或者,作为显示元件可以使用液晶元件、mems(micro electro mechanical systems)元件等。此外,在电路60设置电容器,借助该电容器可以将电荷储存在节点nd1。

[0133]

在本说明书等中,有时可以将“元件”换称为“器件”。例如,可以将显示元件、发光元件及液晶元件分别换称为显示器件、发光器件及液晶器件。

[0134]

附加电路50包括开关sw1、开关sw2、开关sw3及电容器53。开关sw1的一个端子及开关sw2的一个端子与布线27电连接。开关sw1的一个端子可以为附加电路50的输入端子。在后面说明详细内容,在此,传输晶体管逻辑电路45[j]的输出端子可以通过布线27与为附加电路50的输入端子的开关sw1的一个端子直接连接。

[0135]

开关sw1的另一个端子及电容器53的一个端子通过布线26与开关swc的另一个端子电连接。开关sw1的另一个端子可以为附加电路50的输出端子。在后面说明详细内容,在此,可以为附加电路50的输出端子的开关sw1的另一个端子可以通过布线26与开关swc的另一个端子直接连接。

[0136]

电容器53的另一个端子与开关sw2的另一个端子及开关sw3的一个端子电连接。开关sw3的另一个端子与布线54电连接。在此,开关sw2的另一个端子、开关sw3的一个端子以及电容器53的另一个端子彼此电连接的节点为节点nd2。

[0137]

对布线54可以供应恒电位。对布线54例如可以供应低电位,例如可以供应接地电位。

[0138]

通过使开关swc处于开启状态,可以将附加电路50输出的模拟数据写入到像素33。具体而言,节点nd1的电位可以为对应于附加电路50输出的模拟数据的电位。

[0139]

图5a1是示出像素33的结构例子的电路图。图5a1所示的像素33包括晶体管61及电路60,电路60包括发光元件70、晶体管71及电容器73。在此,晶体管61相当于图4所示的开关swc。

[0140]

晶体管61的源极和漏极中的一个、晶体管71的栅极及电容器73的一个端子与节点nd1电连接。晶体管71的源极和漏极中的一个与发光元件70的一个端子电连接。

[0141]

晶体管61的源极和漏极中的另一个与布线26电连接。晶体管61的栅极与布线34电连接。晶体管71的源极和漏极中的另一个及电容器73的另一个端子与布线74电连接。发光元件70的另一个端子与布线75电连接。

[0142]

对布线74及布线75可以供应恒电位。例如,如图5a1所示,发光元件70的阳极与晶体管71的源极和漏极中的一个电连接,发光元件70的阴极与布线75电连接的情况下,布线74的电位可以为高电位且布线75的电位可以为低电位。

[0143]

图5a1所示的像素33中,通过将对应于附加电路50所生成的模拟数据的电位保持在节点nd1,对应于晶体管71的栅极-源极间的电压的电流流过晶体管71的漏极-源极间。因为该电流流过发光元件70,发光元件70发射该电流对应的亮度的光。由此,图5a1所示的像素33可以发射对应于附加电路50所生成的模拟数据的亮度的光。由此,晶体管71被用作控制流过发光元件70的电流的驱动晶体管。

[0144]

除了栅极(也称为顶栅极)以外,晶体管61及晶体管71也可以包括背栅极。图5a2所示的像素33具有图5a1所示的像素33所包括的晶体管61及晶体管71中设置背栅极的结构。

[0145]

图5a2所示的像素33中,晶体管61的背栅极与晶体管61的栅极电连接。由此,可以增大晶体管61的通态电流。另外,晶体管71的背栅极与晶体管71的源极和漏极中的一个电连接,例如可以与晶体管71的源极电连接。由此,可以增大晶体管71的通态电流。由此,通过像素33具有图5a2所示的结构,可以高速驱动像素33,因此可以高速驱动显示装置10。

[0146]

图5b1所示的像素33是图5a1所示的像素33的变形例子,电路60的结构与图5a1所示的像素33不同。图5b1所示的电路60包括液晶元件80及电容器81。

[0147]

图5b1所示的像素33中,除了晶体管61的源极和漏极中的一个以外,液晶元件80的一个端子及电容器81的一个端子还与节点nd1电连接。此外,电容器81的另一个端子与布线82电连接,液晶元件80的另一个端子与布线83电连接。

[0148]

对布线82及布线83可以供应恒电位。对布线82及布线83例如可以供应低电位,例如可以供应接地电位。

[0149]

图5b1所示的像素33中,通过对应于附加电路50所生成的模拟数据的电位保持在节点nd1,液晶元件80所包含的液晶分子根据液晶元件80的两个端子之间的电位差取向。因为被取向的液晶分子对应于取向量的程度使来自显示装置10可以包括的背光单元的光透过,像素33可以发射对应于附加电路50所生成的模拟数据的亮度的光。

[0150]

如上所示,晶体管61也可以包括背栅极。图5b2所示的像素33具有图5b1所示的像素33包括的晶体管61中设置背栅极的结构。

[0151]

在图5b2所示的像素33中,晶体管61的背栅极与晶体管61的栅极电连接。如上所述,可以增大晶体管61的通态电流,所以可以高速驱动像素33,因此高速驱动显示装置10。

[0152]

《显示装置的驱动方法的一个例子_1》

[0153]

接着,说明显示装置10的驱动方法的一个例子。图6是示出说明驱动方法的一个例子的显示装置10的结构的电路图。如图6所示,对传输晶体管逻辑电路45输入数字数据dd《0》至数字数据dd《4》。此外,像素33包括的开关swc为晶体管61。并且,附加电路50包括的开关sw1为晶体管55,开关sw2为晶体管56,开关sw3为晶体管57。此外,在图6中,电容器cpt为在图4所示的布线26的寄生电容的电容器cp的总和,电连接于布线26的像素33为m个且所有的电容器cp的电容值都为相同的情况下,电容器cpt的电容值为“电容器cp的电容值

×

m”。此外,在图6中省略表示图4所示的布线26的布线电阻的电阻器rp。

[0154]

晶体管55的源极和漏极中的一个及晶体管56的源极和漏极中的一个与布线27电连接。晶体管55的源极和漏极中的一个可以为附加电路50的输入端子。在后面说明详细内容,在此,传输晶体管逻辑电路45的输出端子可以通过布线27与可以为附加电路50的输入端子的晶体管55的源极和漏极中的一个直接连接。

[0155]

晶体管55的源极和漏极中的另一个及电容器53的一个端子与布线26电连接。晶体管55的源极和漏极中的另一个可以为附加电路50的输出端子。在后面说明详细内容,在此可以为附加电路50的输出端子的晶体管55的源极和漏极中的另一个可以通过布线26与晶体管61的源极和漏极中的另一个直接连接。

[0156]

电容器53的另一个端子与晶体管56的源极和漏极中的另一个及晶体管57的源极和漏极中的一个电连接。晶体管57的源极和漏极中的另一个与布线54电连接。在此,晶体管

56的源极和漏极中的另一个、晶体管57的源极和漏极的一个以及电容器53的另一个端子彼此电连接的节点为节点nd2。

[0157]

晶体管55的栅极及晶体管57的栅极与布线58电连接。晶体管56的栅极与布线59电连接。布线58及布线59是进行晶体管55至晶体管57的开启状态和关闭状态的切换的布线。在此,晶体管55的栅极及晶体管57的栅极与布线58电连接,由此,通过对布线58供应高电位或低电位,可以同时进行晶体管55及晶体管57的开启状态和关闭状态的切换。此外,也可以分别独立地进行晶体管55的开启状态和关闭状态的切换及晶体管57的开启状态和关闭状态的切换。在此情况下,晶体管55的栅极及晶体管57的栅极与分别不同的布线电连接即可。

[0158]

图7是示出显示装置10的驱动方法的一个例子的时序图。图7所示的时序图表示在时间t01至时间t05及其附近的时间的布线34、布线58、布线59、布线26、布线27、节点nd1及节点nd2的电位的变化。另外,图7所示的时序图表示数字数据dd。此外,在图7所示的时序图中,“h”表示高电位,“l”表示低电位。其他时序图也同样记载。

[0159]

在时间t01至时间t05及其附近的时间,对布线54一直供应低电位。

[0160]

注意,在本说明书所示的驱动方法的一个例子中,在没有特别的说明的情况下,晶体管61及晶体管55至晶体管57在开启状态时最后在线性区域中工作。就是说,对晶体管61及晶体管55至晶体管57的栅极电压、源极电压及漏极电压进行适当的偏压,使得这些晶体管在线性区域中工作。此外,作为像素33使用图5a1或图5a2所示的像素33的情况下,优选使晶体管71在饱和区域中驱动。

[0161]

[时间t01之前]

[0162]

在时间t01之前,布线34被供应低电位。布线34的电位为低电位时对晶体管61的栅极供应低电位,因此,晶体管61成为关闭状态。就是说、布线26与节点nd1之间成为不电连接的状态。

[0163]

此外,布线58被供应低电位。布线58的电位为低电位时,对晶体管55的栅极及晶体管57的栅极供应低电位,晶体管55及晶体管57成为关闭状态。就是说,传输晶体管逻辑电路45与显示部32之间成为不电连接的状态,节点nd2与布线54之间也成为不电连接的状态。

[0164]

在时间t01之前,使布线59的电位从高电位变为低电位。布线59的电位为高电位时晶体管56的栅极被供应高电位,所以晶体管56成为开启状态。就是说,传输晶体管逻辑电路45与节点nd2之间成为电连接的状态。在此,从传输晶体管逻辑电路45的输出端子被输出的电位供应到节点nd2。此外,布线59的电位成为低电位时晶体管56为关闭状态,传输晶体管逻辑电路45与节点nd2之间为不电连接的状态。

[0165]

[时间t01]

[0166]

在时间t01,布线34被供应高电位。因此,在时间t01至时间t02对晶体管61的栅极供应高电位。由此,晶体管61成为开启状态。由此,布线26与节点nd1之间成为导通状态。

[0167]

此外,在时间t01,布线58被供应高电位。因此,在时间t01至时间t02,晶体管55的栅极及晶体管57的栅极被供应高电位。由此,晶体管55及晶体管57成为开启状态。由此,布线26与传输晶体管逻辑电路45之间成为导通状态。另外,节点nd2与布线54之间成为导通状态,节点nd2的电位成为低电位。

[0168]

在此,在时间t01之前,作为数字数据dd“x

h4

x

h3

x

h2

x

h1

x

h0”输入到传输晶体管逻辑电路45的输入端子。就是说,数字数据dd《0》为“x

h0”、数字数据dd《1》为“x

h1”、数字数据dd《2》

为“x

h2”、数字数据dd《3》为“x

h3”、数字数据dd《4》为“x

h4”的数字数据dd被输入。由d/a转换电路40“x

h4

x

h3

x

h2

x

h1

x

h0”被转换为第一模拟数据,布线27的电位成为电位v

data1

。因为晶体管55为开启状态,所以布线26的电位为电位v

data1

。此外,因为晶体管61为开启状态,所以像素33的节点nd1的电位为电位v

data1

。

[0169]

另一方面,晶体管57为开启状态,所以节点nd2的电位成为布线54的电位,即低电位。此外,晶体管56为关闭状态,所以布线27的电位v

data1

不供应到节点nd2。

[0170]

[时间t02]

[0171]

在时间t02,布线58被供应低电位。因此,在时间t02至时间t03,晶体管55的栅极及晶体管57的栅极被供应低电位。由此,晶体管55及晶体管57成为关闭状态。

[0172]

晶体管55为关闭状态时布线26与传输晶体管逻辑电路45之间成为非导通状态。由此,布线26及节点nd1成为电浮动状态。另外,晶体管57为关闭状态时节点nd2与布线54之间也成为非导通状态,所以节点nd2也成为电浮动状态。

[0173]

而且,在时间t02至时间t03,作为数字数据dd“x

l4

x

l3

x

l2

x

l1

x

l0”输入到传输晶体管逻辑电路45的输入端子。就是说,数字数据dd《0》为“x

l0”、数字数据dd《1》为“x

l1”、数字数据dd《2》为“x

l2”、数字数据dd《3》为“x

l3”、数字数据dd《4》为“x

l4”的数字数据dd被输入。由d/a转换电路40“x

l4

x

l3

x

l2

x

l1

x

l0”被转换为第二模拟数据,布线27的电位成为电位v

data2

。

[0174]

在本说明书中,例如数字数据“x

h4

x

h3

x

h2

x

h1

x

h0”有时称为第一数字数据或5位的第一数字数据。此外,例如数字数据“x

l4

x

l3

x

l2

x

l1

x

l0”有时称为第二数字数据或5位的第二数字数据。

[0175]

[时间t03]

[0176]

在时间t03,布线59被供应高电位。因此,在时间t03至时间t04对晶体管56的栅极供应高电位。由此,晶体管56成为开启状态。由此,布线27的电位v

data2

供应到节点nd2。此外,晶体管57为关闭状态,所以电流不从传输晶体管逻辑电路45流过布线54,节点nd2的电位成为电位v

data2

。

[0177]

另外,因为布线26与节点nd1为电浮动状态,通过节点nd2的电位变化,由于电容器53的电容耦合布线26的电位及节点nd1的电位也变化。在图7的时序图中,布线26的电位的变动量及节点nd1的电位的变动量为电位δvg。电容器53的静电电容值为电容值ca且合成作为布线26的寄生电容的电容器cpt与起因于电路60等的电容的静电电容值为电容值cb时,可以以下面算式(1)估计电位δvg。在此,起因于电路60等的电容的静电电容比布线26的寄生电容充分小时,电容值cb可以与电容器cpt的电容值相同。

[0178]

[算式1]

[0179][0180]

由此,节点nd1的电位为电位v

nd1

时下面的算式(2)表示电位v

nd1

。在时间t02至时间t03的节点nd2的电位为接地电位。

[0181]

[算式2]

[0182][0183]

如上所述,电位v

data1

是对应于第一模拟数据的电位,电位v

data2

是对应于第二模拟

数据的电位。因此,由于算式(2),可以对第一模拟数据附加第二模拟数据。由此,附加电路50可以生成而保持第三模拟数据。并且,像素33可以发射对应于第三模拟数据的电位v

nd1

对应的亮度的光。由此,可以在像素33设置的显示部32上显示图像。

[0184]

数字数据dd的位数为5位时,数字数据dd可以取得以2进制表示从“00000”至“11111”的值。在此,例如数字数据“x

h4

x

h3

x

h2

x

h1

x

h0”为“00000”时,从传输晶体管逻辑电路45的输出端子输出的电位v

data1

为0v。此外,例如数字数据“x

h4

x

h3

x

h2

x

h1

x

h0”为“11111”时,从传输晶体管逻辑电路45的输出端子输出的电位v

data1

为3.1v。在此情况下,电位v

data1

可取的电位为每隔0.1v从0v至3.1v的范围。

[0185]

由此,在图7所示的驱动方法的一个例子中,在时间t01至时间t02对布线26及节点nd1可以写入0v到3.1v的范围的电位v

data1

。

[0186]

在此,例如ca:cb=1:31。在此情况下,算式(1)为下面的算式(3)。

[0187]

[算式3]

[0188][0189]

同一个d/a转换电路40输出电位v

data1

和电位v

data2

时,与对应于电位v

data1

的数字数据同样,对应于电位v

data2

的数字数据可以取得以2进制表示从“00000”至“11111”的值。在此情况下,电位v

data2

可取的电位也为每隔0.1v从0v至3.1v的范围。因此,由于算式(3)电位δvg可取每隔0.003125v从0v至0.096875v的值。

[0190]

由此,图7所示的驱动方法的一个例子中,在时间t03至时间t04,由于算式(2)及算式(3),节点nd1的电位可取每隔0.003125v从0v至3.196875v的值。

[0191]

就是说,通过图7所示的方法驱动显示装置10,可以将比5位的d/a转换电路40可以输出的电位的步长更微细的步长的电位供应像素33的节点nd1。在上述的具体例子中,d/a转换电路40只能输出每隔0.1v的电位,可以写入每隔0.003125v的电位到节点nd1。因此,可以写入与比d/a转换电路40的分辨率的5位更多的位数对应的电位(模拟数据)到像素33。

[0192]

在上述的具体例子中,具有5位的分辨率的d/a转换电路40输出的电位v

data1

相当于表示在显示部32显示的图像的数字数据的高5位。此外,由于附加电路50的电容器53的电容耦合对节点nd1附加的电位δvg相当于该数字数据的低5位。如上所述,对像素33写入的模拟数据相当于数字值为“x

h4

x

h3

x

h2

x

h1

x

h0

x

l4

x

l3

x

l2

x

l1

x

l0”的10位的数字数据转换为模拟数据的数据。

[0193]

[时间t04]

[0194]

在时间t04,布线34被供应低电平电位。由此,在时间t04至时间t05,晶体管61的栅极被供应低电位。因此,晶体管61为关闭状态。

[0195]

晶体管61为关闭状态时,布线26与节点nd1之间成为不电连接的状态。由此,节点nd1的电位v

nd1

被保持。

[0196]

[时间t05]

[0197]

在时间t05,布线59被供应低电位。由此,时间t05之后晶体管56的栅极被供应低电位。由此,晶体管56成为关闭状态。

[0198]

晶体管56成为关闭状态,传输晶体管逻辑电路45与节点nd2之间成为不电连接的状态。此外,因为晶体管57为关闭状态,节点nd2成为电浮动状态。由此,节点nd2的电位由电

容器53保持。

[0199]

以上是显示装置10的驱动方法的一个例子。由此,通过开关sw1及开关sw3为开启状态且开关sw2为关闭状态,写入第一模拟数据到附加电路50。然后,通过开关sw2处于开启状态且开关sw1及开关sw3处于关闭状态,可能写入第二模拟数据到附加电路50及对第一模拟数据的第二模拟数据的附加。由此,附加电路50生成而保持第三模拟数据。

[0200]

图8是示出电位供应电路23、传输晶体管逻辑电路45[j]、附加电路50[j]、显示部32的连接关系的电路图。图8所示的传输晶体管逻辑电路45[j]的结构与图3所示的传输晶体管逻辑电路45的结构同样。此外,图8所示的附加电路50[j]的结构与图4所示的附加电路50[j]的结构同样。并且,图8还示出像素33[1,j]至像素33[m,j]作为设置在显示部32的像素33。

[0201]

如上所述,如图1所示设置多个显示部32而对应这些显示部设置数据驱动电路24及电路25时,可以减少设置在一个显示部32的像素33的列数。由此,可以缩短与像素33电连接并被用作数据线的布线26。因此,可以减小布线26的布线电阻。由此,可以抑制附加电路50输出的电位在写入到像素33之前衰减。

[0202]

此外,如上所述,通过显示装置10包括附加电路50,可以写入对应于比d/a转换电路40可以进行d/a转换的数字数据的位数更多的位数的数字数据的模拟数据到像素33。因此,可以减少d/a转换电路40可以进行d/a转换的数字数据的位数。由此,可以减少传输晶体管逻辑电路45包括的晶体管52的级数。因此,可以抑制从电位供应电路23供应到传输晶体管逻辑电路45的电位在从布线27被输出作为模拟数据之前因晶体管52的漏极-源极间的电阻等而衰减。

[0203]

由此,在本发明的一个方式,可以抑制电位供应电路23输出的电位在写入到像素33之前衰减。所以传输晶体管逻辑电路45的输出端子与附加电路50的输入端子之间不设置缓冲放大器等的情况也不会大幅度降低显示装置10的驱动速度。此外,附加电路50的输出端子与像素33之间不设置缓冲放大器等的情况也不会大幅度降低显示装置10的驱动速度。因此,可以将传输晶体管逻辑电路45的输出端子与附加电路50的输入端子由布线27直接连接。此外,可以将附加电路50的输出端子与像素33由布线26直接连接。在图8以由虚线表示放大电路28的方式示出传输晶体管逻辑电路45的输出端子与附加电路50的输入端子直接连接而不通过放大电路28。另外,图8以由虚线表示放大电路29的方式示出附加电路50的输出端子与像素33直接连接而不通过放大电路29。

[0204]

通过采用显示装置10不包括放大电路28及/或放大电路29的结构,可以减少显示装置10的功耗。因此,由电池进行对显示装置10的电力供应时,可以长时间连续地使用设置有显示装置10的电子设备。此外,通过降低显示装置10的功耗,可以实现设置有显示装置10的电子设备中内置的电池的小型化及轻量化。由此,可以实现电子设备的小型化及轻量化。尤其是,将例如显示装置10适用于hmd等可穿戴型电子设备时,由于电子设备的小型化及轻量化,减小电子设备的使用者的负担,使该使用者不容易感到疲劳,所以是优选的。

[0205]

另外,在显示装置10设置放大电路28及/或放大电路29的情况下,产生起因于每个放大电路28的电特性的不均匀及/或每个放大电路29的电特性的不均匀的显示不均匀。因此,通过采用显示装置10不包括放大电路28及/或放大电路29的结构,可以在显示部32显示显示不均匀少的高质量的图像。

[0206]

另外,也可以设置放大电路28或放大电路29中的一个。例如,也可以设置放大电路29。通过附加电路50的输出端子与像素33通过放大电路29电连接,可以在将附加电路50所生成的模拟数据放大之后将其写入到像素33。由此,可以高速驱动显示装置10。

[0207]

《显示装置的结构例子_2》

[0208]

图9是示出附加电路50的结构例子的电路图,也是图4所示的附加电路50的变形例子。图9所示的附加电路50与图4所示的附加电路50不同之处在于:除了开关sw1至开关sw3以外,还包括开关sw4、开关sw5《0》至开关sw5《k-1》(k为1以上的整数)、比较器电路91、控制电路93及保持电路94;包括k个电容器53(电容器53《0》至电容器53《k-1》)。注意,图9示出传输晶体管逻辑电路45及像素33以示出与附加电路50之间的连接关系。

[0209]

图9所示的附加电路50中,开关sw1的一个端子及开关sw2的一个端子与布线27电连接。如上所述,开关sw1的一个端子可以为附加电路50的输入端子,可以通过布线27与传输晶体管逻辑电路45的输出端子直接连接。

[0210]

另外,开关sw1的另一个端子、开关sw4的一个端子及开关sw5《0》至开关sw5《k-1》的一个端子与布线26电连接。如上所述,开关sw1的另一个端子可以为附加电路50的输出端子,可以通过布线26与设置在像素33的开关swc的另一个端子直接连接。

[0211]

开关sw5《0》至开关sw5《k-1》的另一个端子各自与电容器53《0》至电容器53《k-1》的一个端子电连接。开关sw2的另一个端子与开关sw3的一个端子电连接。开关sw3的一个端子与电容器53《0》至电容器53《k-1》的另一个端子电连接。如上所述,电容器53《0》至电容器53《k-1》通过开关sw5《0》至开关sw5《k-1》并联连接。

[0212]

在此,开关sw2的另一个端子、开关sw3的一个端子以及电容器53《0》至电容器53《k-1》的另一个端子彼此电连接的节点为节点nd2。

[0213]

开关sw3的另一个端子与布线54电连接。如上所述,布线54可以被供应恒电位。

[0214]

开关sw4的另一个端子与比较器电路91的非反相输入端子或反相输入端子的一方电连接。比较器电路91的非反相输入端子或反相输入端子的另一方与布线92电连接。布线92被供应基准电位vref。

[0215]

比较器电路91的输出端子与控制电路93的输入端子电连接。控制电路93的输出端子与保持电路94的输入端子电连接。

[0216]

比较器电路91具有输出表示输入到比较器电路91的非反相输入端子的电位和输入到比较器电路91的反相输入端子电位的大小关系的信号cmp的功能。具体而言,当输入到比较器电路91的非反相输入端子的电位比输入到比较器电路91的反相输入端子的电位大时,信号cmp成为高电位的信号。另一方面,当输入到比较器电路91的非反相输入端子的电位比输入到比较器电路91的反相输入端子的电位小时,信号cmp成为低电位的信号。因此,例如图9所示,比较器电路91的非反相输入端子被供应基准电位vref的情况下,比较器电路91的反相输入端子被供应的电位比基准电位vref高时,信号cmp的电位成为低电位。另一方面,比基准电位vref低时,信号cmp的电位成为高电位。在后面说明详细内容,基准电位vref可以为d/a转换电路40可以输出的电位的步长对应的值。

[0217]

控制电路93具有生成控制开关sw5《0》至开关sw5《k-1》的开启/关闭的信号cor的功能。信号cor可以为k位的数字信号。

[0218]

此外,控制电路93具有由于第二模拟数据附加到第一模拟数据生成的第三模拟数

据保持在附加电路50时根据信号cmp更新或确定信号cor的数字值的功能。具体而言,例如控制电路93具有信号cmp的电位为低电位时更新信号cor的数字值,信号cmp的电位为高电位时不更新信号cor的数字值而确定的功能。

[0219]

下面,信号cor为k位的数字信号,信号cor包含的各位记为信号cor《0》至信号cor《k-1》。

[0220]

例如,信号cor《0》表示“1”时,可以使开关sw5《0》为开启状态,信号cor《0》表示“0”时,可以使开关sw5《0》为关闭状态。另外,信号cor《0》表示“0”时,也可以使开关sw5《0》为开启状态,信号cor《0》表示“1”时,也可以使开关sw5《0》为关闭状态。信号cor《1》至信号cor《k-1》也是同样的。

[0221]

保持电路94具有保持信号cor表示的开关sw5《0》至开关sw5《k-1》的开启/关闭的信息的功能。例如,保持电路94具有保持被确定的信号cor的数字值的功能。保持电路94可以具有例如包括锁存电路的结构。或者,保持电路94也可以具有包括非易失性存储器的结构。

[0222]

在显示装置10,作为写入到像素33的模拟数据的电位以高精度表示像素33发射的光的亮度,优选精密地控制算式(1)及算式(2)表示的电容值ca与电容值cb的比率。但是,难以精密地测定电容值cb中包括的布线26的寄生电容的电容值。另外,例如可以设置在显示装置10的n个布线26的寄生电容的电容值有时根据各布线26产生不均匀。由此,通过设置多个电容器53各自通过开关sw5并联连接,可以精密地控制算式(1)及算式(2)中包括的“ca/(ca cb)”的值。具体而言,电容値ca可以为电容器53《0》至电容器53《k-1》中与开启状态的开关sw5电连接的电容器53的静电电容的总和。

[0223]

由此,通过附加电路50具有图9所示的结构,可以作为写入到像素33的模拟数据的电位以高精度显示从像素33发射的光的亮度。由此,显示装置10可以显示高质量的图像。

[0224]

《显示装置的驱动方法的一个例子_2》

[0225]

接着,说明包括图9所示的附加电路50的显示装置10的驱动方法的一个例子。图10是示出说明驱动方法的一个例子的显示装置10的结构的电路图。如图10所示,开关sw4为晶体管96。此外,k为8,开关sw5为晶体管98。并且,信号cor供应到晶体管98的栅极。其他的与图6所示的结构同样。

[0226]

图10所示的附加电路50中,晶体管96的源极和漏极中的一个与布线26电连接。晶体管96的栅极与布线97电连接。晶体管96的源极和漏极中的另一个与比较器电路91的反相输入端子电连接。晶体管98《0》至晶体管98《7》的源极和漏极中的一个与布线26电连接。晶体管98《0》至晶体管98《7》的源极和漏极中的另一个与电容器53《0》至电容器53《7》的一个端子各自电连接。

[0227]

首先,说明决定信号cor《0》至信号cor《7》的数字值的方法的一个例子。由此,可以决定晶体管98《0》至晶体管98《7》中的开启状态的晶体管。由此,可以决定电容值ca。

[0228]

图11是示出决定信号cor《0》至信号cor《7》的数字值的方法的一个例子的时序图。图11所示的时序图示出时间t11至时间t23及其附近时间中的布线97、布线58、布线59、布线26、布线27、信号cmp及节点nd2的电位的变化。此外,图11所示的时序图示出数字数据dd及信号cor。

[0229]

此外,在本说明书所示的驱动方法的一个例子中,在没有特别的说明的情况下,晶

体管96及晶体管98《0》至晶体管98《7》为开启状态时最后在线性区域中工作。也就是说,对晶体管96及晶体管98《0》至晶体管98《7》的栅极电压、源极电压及漏极电压进行适当的偏压,使得这些晶体管在线性区域中工作。

[0230]

此外,如上所述,数字数据dd的位数为5位时,数字数据dd可以取得以2进制表示从“00000”至“11111”的值。在此,数字数据dd的数字值为“00000”时的布线27的电位为低电位,即电位vss,数字数据dd的数字值为“11111”时的布线27的电位为高电位,即电位vdd。此外,布线54的电位为电位vss。并且,基准电位vref为电位vss以上且电位vdd以下。

[0231]

此外,在图11所示的方法中,控制电路93在第二模拟数据附加到第一模拟数据生成的第三模拟数据保持在附加电路50且信号cmp为低电位时更新信号cor的数字值。此外,第三模拟数据保持在附加电路50且信号cmp为高电位时不更新信号cor的数字值而确定。

[0232]

并且,起因于晶体管61的电容及起因于电路60的电容等起因于像素33的电容比布线26的寄生电容充分小。

[0233]

[时间t11之前]

[0234]

在时间t11之前,布线97被供应低电位。布线97的电位为低电位时对晶体管96的栅极供应低电位,因此,晶体管96成为关闭状态。就是说,布线26与比较器电路91的反相输入端子之间成为不电连接的状态。

[0235]

此外,布线58被供应低电位。布线58的电位为低电位时,对晶体管55的栅极及晶体管57的栅极供应低电位,晶体管55及晶体管57成为关闭状态。就是说,传输晶体管逻辑电路45与显示部32之间成为不电连接的状态,节点nd2与布线54之间也成为不电连接的状态。

[0236]

并且,布线26的电位、布线27的电位、节点nd1的电位及节点nd2的电位为低电位,信号cmp的电位为高电位。

[0237]

在时间t11之前,使布线59的电位从高电位变为低电位。布线59的电位为高电位时晶体管56的栅极被供应高电位,所以晶体管56成为开启状态。就是说,传输晶体管逻辑电路45与节点nd2之间成为电连接的状态。在此,从传输晶体管逻辑电路45的输出端子被输出的电位供应到节点nd2。此外,布线59的电位成为低电位时晶体管56为关闭状态,传输晶体管逻辑电路45与节点nd2之间为不电连接的状态。

[0238]

[时间t11]

[0239]

在时间t11,信号cor的数字值为“11111111”。由此,晶体管98《0》至晶体管98《7》的栅极被供应高电位,晶体管98《0》至晶体管98《7》成为开启状态。由此,电容器53《0》至电容器53《7》的一个端子与布线26之间成为导通状态。

[0240]

此外,在时间t11,布线97被供应高电位。因此,晶体管96的栅极被供应高电位,晶体管96成为开启状态。由此,布线26与比较器电路91的反相输入端子之间成为导通状态。注意,在时间t11至时间t23,布线97被供应高电位。因此,在时间t11至时间t23,晶体管96成为开启状态。

[0241]

此外,在时间t11,布线58被供应高电位。由此,晶体管55的栅极及晶体管57的栅极被供应高电位,晶体管55及晶体管57成为开启状态。通过晶体管57为开启状态,节点nd2与布线54之间成为导通状态。由此,节点nd2的电位成为布线54的电位,即低电位。

[0242]

在此,在时间t11,作为数字数据dd“00000”输入到传输晶体管逻辑电路45的输入端子。就是说,5位的数字数据可取的最小的数字值的数字数据dd被输入。接着,“00000”由

d/a转换电路40转换为第一模拟数据,布线27的电位成为低电位。在此,晶体管55为开启状态,所以布线26的电位为低电位。此外,晶体管96为开启状态,比较器电路91的反相输入端子的电位为低电位。由此,信号cmp的电位成为高电位。

[0243]

[时间t12]

[0244]

在时间t12,布线58被供应低电位。由此,晶体管55的栅极及晶体管57的栅极被供应低电位,晶体管55及晶体管57成为关闭状态。

[0245]

晶体管55为关闭状态时,布线26与传输晶体管逻辑电路45之间成为非导通状态。由此,布线26成为电浮动状态。此外,晶体管57为关闭状态时节点nd2与布线54之间成为非导通状态,所以节点nd2也成为电浮动状态。

[0246]

[时间t13]

[0247]

在时间t13,作为数字数据dd“11111”输入到传输晶体管逻辑电路45的输入端子。就是说,5位的数字数据可取的最大的数字值的数字数据dd被输入。接着,“11111”由d/a转换电路40转换为第二模拟数据,布线27的电位成为高电位。

[0248]

此外,在时间t13,布线59被供应高电位。由此,晶体管56的栅极被供应高电位,晶体管56成为开启状态。因此,布线27的电位,即高电位供应到节点nd2。此外,晶体管57为关闭状态,所以从传输晶体管逻辑电路45到布线54电流不流过,节点nd2的电位成为高电位。

[0249]

此外,因为布线26为电浮动状态,通过节点nd2的电位变动,由电容器53的电容耦合布线26的电位也变动。在时间t13,晶体管98《0》至晶体管98《7》为开启状态。因此,由于电容器53《0》至电容器53《7》的电容耦合,布线26的电位变动。由布线26的电位变动,第二模拟数据附加到第一模拟数据,第三模拟数据被生成。此外,第三模拟数据保持在附加电路50。在此,在时间t13至时间t14,布线26的电位比基准电位vref高。

[0250]

如上所述,在时间t13至时间t14,晶体管96为开启状态。因此,比较器电路91的反相输入端子被供应布线26的电位。如上所述,在时间t13至时间t14,布线26的电位比基准电位vref高。由此,信号cmp的电位成为低电位。

[0251]

[时间t14]

[0252]

在时间t14,布线59被供应低电位。由此,晶体管56的栅极被供应低电位,晶体管56成为关闭状态。

[0253]

此外,在时间t14,通过第二模拟数据附加到第一模拟数据被生成的第三模拟数据保持在附加电路50。此外,信号cmp的电位为低电位。由此,信号cor的数字值被更新。在时间t14,信号cor的数字值从“11111111”更新为“11111110”。通过信号cor的数字值为“11111110”,晶体管98《0》的栅极被供应低电位,晶体管98《0》成为关闭状态。由此,电容器53《0》与布线26之间成为非导通状态。另一方面,晶体管98《1》至晶体管98《7》的栅极被供应高电位,晶体管98《1》至晶体管98《7》成为开启状态。由此,电容器53《1》至电容器53《7》的一个端子与布线26之间成为导通状态。注意,图11所示的时序图中,不考虑在时间t14至时间t15中伴随信号cor的数字值被更新而发生的布线26等的电位变化。

[0254]

[时间t15]

[0255]

在时间t15,布线58被供应高电位。由此,与时间t11同样地,节点nd2的电位成为低电位。

[0256]

在此,在时间t15,与时间t11同样地,作为数字数据dd“00000”输入到传输晶体管

逻辑电路45的输入端子。由此,信号cmp的电位成为高电位。

[0257]

[时间t16]

[0258]

在时间t16,布线58被供应低电位。由此,与时间t12同样地,晶体管55及晶体管57成为关闭状态,布线26及节点nd2成为电浮动状态。

[0259]

[时间t17]

[0260]

在时间t17,与时间t13同样地,作为数字数据dd“11111”输入到传输晶体管逻辑电路45的输入端子。由此,布线27的电位成为高电位。

[0261]

此外,在时间t17,布线59被供应高电位。由此,与时间t13同样地,晶体管56成为开启状态,节点nd2的电位成为高电位。

[0262]

此外,与时间t13同样地布线26为电浮动状态,所以通过节点nd2的电位变动布线26的电位也变动。在时间t17,晶体管98《1》至晶体管98《7》为开启状态。因此,由于电容器53《1》至电容器53《7》的电容耦合,布线26的电位变动。由于布线26的电位变动,第二模拟数据附加到第一模拟数据,第三模拟数据被生成。此外,第三模拟数据保持在附加电路50。在此,在时间t17至时间t18,布线26的电位比基准电位vref高。

[0263]

在时间t17至时间t18中的布线26的电位为算式(2)表示的电位v

nd1

。如上所述,电容值ca可以为电容器53《0》至电容器53《7》中的与开启状态的晶体管98电连接的电容器53的静电电容的总和。在时间t17至时间t18,晶体管98《1》至晶体管98《7》为开启状态,晶体管98《0》为关闭状态。因此,电容值ca成为电容器53《1》至电容器53《7》的静电电容的总和对应的值。在此,在时间t13至时间t14,晶体管98《0》至晶体管98《7》为开启状态,所以电容值ca成为电容器53《0》至电容器53《7》的静电电容的总和对应的值。由此,在时间t17至时间t18中的电容值ca比在时间t13至时间t14中的电容值ca小。如算式(2)所示,电位v

data1

、电位v

data2

及电容值cb不变动时,电容值ca越小布线26的电位也越小。由此,在时间t17至时间t18中的布线26的电位比在时间t13至时间t14中的布线26的电位小。

[0264]

如上所述,在时间t17至时间t18,晶体管96为开启状态。因此,比较器电路91的反相输入端子被供应布线26的电位。如上所述,在时间t17至时间t18,布线26的电位成为比基准电位vref高。由此,信号cmp的电位成为低电位。

[0265]

[时间t18]

[0266]

在时间t18,布线59被供应低电位。由此,晶体管56的栅极被供应低电位,晶体管56成为关闭状态。

[0267]

此外,在时间t18,通过第二模拟数据附加到第一模拟数据被生成的第三模拟数据保持在附加电路50。此外,信号cmp的电位为低电位。由此,信号cor的数字值被更新。在时间t18,信号cor的数字值从“11111110”更新为“11111100”。通过信号cor的数字值为“11111100”,晶体管98《0》及晶体管98《1》的栅极被供应低电位,晶体管98《0》及晶体管98《1》成为关闭状态。由此,电容器53《0》及电容器53《1》与布线26之间成为非导通状态。另一方面,晶体管98《2》至晶体管98《7》的栅极被供应高电位,晶体管98《2》至晶体管98《7》成为开启状态。由此,电容器53《2》至电容器53《7》的一个端子与布线26之间成为导通状态。注意,图11所示的时序图中,不考虑在时间t18至时间t19中伴随信号cor的数字值被更新而发生的布线26等的电位变化。

[0268]

[时间t19]

[0269]

在时间t19,布线58被供应高电位。由此,与时间t11等同样地,节点nd2的电位成为低电位。

[0270]

在此,在时间t19,与时间t11等同样地,作为数字数据dd“00000”输入到传输晶体管逻辑电路45的输入端子。由此,信号cmp的电位成为高电位。

[0271]

[时间t20]

[0272]

在时间t20,布线58被供应低电位。由此,与时间t12等同样地晶体管55及晶体管57成为关闭状态,布线26及节点nd2成为电浮动状态。

[0273]

[时间t21]

[0274]

在时间t21,与时间t13等同样地,作为数字数据dd“11111”输入到传输晶体管逻辑电路45的输入端子。由此,布线27的电位成为高电位。

[0275]

此外,在时间t21,布线59被供应高电位。由此,与时间t13等同样地晶体管56成为开启状态,节点nd2的电位成为高电位。

[0276]

此外,与时间t13等同样地布线26为电浮动状态,所以通过节点nd2的电位变动布线26的电位也变动。在时间t21,晶体管98《2》至晶体管98《7》为开启状态。因此,由于电容器53《2》至电容器53《7》的电容耦合,布线26的电位变动。由布线26的电位变动,第二模拟数据附加到第一模拟数据,第三模拟数据被生成。此外,第三模拟数据保持在附加电路50。在此,在时间t21至时间t22,布线26的电位比基准电位vref低。

[0277]

在时间t21至时间t22中的布线26的电位为算式(2)表示的电位v

nd1

。如上所述,电容值ca可以为电容器53《0》至电容器53《7》中的与开启状态的晶体管98电连接的电容器53的静电电容的总和。在时间t21至时间t22,晶体管98《2》至晶体管98《7》为开启状态,晶体管98《0》及晶体管98《1》为关闭状态。因此,电容值ca成为电容器53《2》至电容器53《7》的静电电容的总和对应的值。在此,在时间t17至时间t18,晶体管98《1》至晶体管98《7》为开启状态,所以电容值ca成为电容器53《1》至电容器53《7》的静电电容的总和对应的值。由此,在时间t21至时间t22中的电容值ca比在时间t17至时间t18中的电容值ca小。如算式(2)所示,电位v

data1

、电位v

data2

及电容值cb不变动时,电容值ca越小布线26的电位也越小。由此,在时间t21至时间t22中的布线26的电位比在时间t17至时间t18中的布线26的电位小。

[0278]

如上所述,在时间t21至时间t22,晶体管96为开启状态。因此,比较器电路91的反相输入端子被供应布线26的电位。如上所述,在时间t21至时间t22,布线26的电位成为比基准电位vref低。由此,信号cmp的电位成为高电位。

[0279]

[时间t22]

[0280]

在时间t22,布线59被供应低电位。由此,晶体管56的栅极被供应低电位,晶体管56成为关闭状态。

[0281]

此外,在时间t22,通过第二模拟数据附加到第一模拟数据被生成的第三模拟数据保持在附加电路50。此外,信号cmp的电位为高电位。由此,信号cor的数字值不被更新而被确定。在时间t18,信号cor的数字值确定为“11111100”。确定的数字值保持在保持电路94。

[0282]

[时间t23]

[0283]

在时间t23,布线97被供应低电位。由此,晶体管96的栅极被供应低电位,晶体管96成为关闭状态。

[0284]

由此,可以决定信号cor《0》至信号cor《7》的数字值。

[0285]

如上所述,晶体管55及晶体管57为开启状态且晶体管56为关闭状态的情况下,将第一数字数据由d/a转换电路40转换为第一模拟数据,将该第一模拟数据写入到附加电路50。由此,布线26的电位成为第一模拟数据对应的电位。然后,晶体管56为开启状态且晶体管55及晶体管57为关闭状态的情况下,将第二数字数据由d/a转换电路40转换为第二模拟数据,将该第二模拟数据附加第一模拟数据。由此,布线26的电位变动,该变动量为对应于第二模拟数据的电位。变动后的布线26的电位相当于使第一数字数据包含的数字值为高位,第二数字数据包含的数字值为低位的数字数据被进行d/a转换后的模拟数据。

[0286]

由此,优选的是,第二数字数据的数字值为最大(例如,所有的位数为“1”)的情况的布线26的电位与第二数字数据的数字值为最小(例如,所有的位数为“0”)的情况的布线26的电位之差小于将第一数字数据的数字值增加1的情况的布线26的电位的变化量。就是说,优选的是,第二模拟数据供应到附加电路50的情况的布线26的电位的变化量的最大值小于d/a转换电路40可以输出的电位的步长。由此,例如第一数字数据包含的数字值为高位,第二数字数据包含的数字值为低位时的数字数据的数字值越大,写入到像素33的电位越可以提高。就是说,例如虽然第一数字数据包含的数字值为高位,第二数字数据包含的数字值为低位时的数字数据的数字值变大,但是可以抑制写入到像素33的电位变小。

[0287]

在图11所示的方法,首先,检测第二数字数据的数字值最大的情况的布线26的电位的变动幅度。接着,将信号cor的数字值減少1,同样地检测布线26的电位的变动幅度。重复该工序,布线26的电位变得小于基准电位vref时,确定信号cor《0》至信号cor《7》的数字值。如上所述,由信号cor《0》至信号cor《7》的数字值可以决定算式(1)及算式(2)所示的电容值ca。

[0288]

由此,d/a转换电路40可以输出的电位的步长为电位δv

dac

时,基准电位vref为电位“δv

dac

vss”以下,例如通过与电位“δv

dac

vss”相同的情况同时进行图11所示的方法,可以使第二模拟数据供应到附加电路50的情况的布线26的电位的变化量的最大值小于电位δv

dac

。由此,可以作为写入到像素33的模拟数据的电位以高精度显示像素33发射的光的亮度。此外,第一模拟数据供应到附加电路50的情况的布线26的电位不是电位vss而例如为电位v1的情况下,优选基准电位vref为电位“δv

dac

v

1”以下,例如等于电位“δv

dac

v

1”。因此,图11所示的方法决定信号cor的数字值的情况下,作为第一数字数据的数字值也可以不是数字数据dd可取的最小数字值(例如,所有的位数为“0”)。

[0289]

在此,优选的是,布线54的电位等于数字数据dd的数字值最小的情况的布线27的电位。由此,第二数字数据的数字值最大的情况的布线26的电位的变动幅度等于第二数字数据的数字值最大的情况的布线26的电位与第二数字数据的数字值最小的情况的布线26的电位之差。

[0290]

图12是示出从附加电路50到图10所示的情况的像素33的模拟数据的写入方法的一个例子的时序图。图12所示的时序图示出时间t31至时间t35及其附近的时间中的布线97、布线34、布线58、布线59、布线26、布线27、节点nd1及节点nd2的电位的变化。另外,图7所示的时序图示出数字数据dd及信号cor。

[0291]

在时间t31至时间t35,布线97被供应低电位。由此,在时间t31至时间t35,晶体管96的栅极被供应低电位。由此,晶体管96成为关闭状态。

[0292]

此外,在时间t31至时间t35,信号cor的数字值为由图11所示的方法等决定的数字

值。在图11中,信号cor的数字值决定为“11111100”,所以图12所示的时间t31至时间t35中信号cor的数字值为“11111100”。

[0293]

在时间t31至时间t35中的布线34、布线58、布线59、布线26、布线27、节点nd1及节点nd2的电位的变化及数字数据dd可以等同于图7所示的时间t01至时间t05中的布线34、布线58、布线59、布线26、布线27、节点nd1及节点nd2的电位的变化及数字数据dd。

[0294]

以上是图10所示的包括附加电路50的显示装置10的驱动方法的一个例子。

[0295]

《显示装置的结构例子_3》

[0296]

图1所示的显示装置10中,对应于一个显示部32设置一个数据驱动电路24及一个电路25,但是本发明的一个方式不局限于此。图13是示出一个显示部32、以具有与该显示部重叠的区域的方式设置的电路的方框图。在显示部32中m行n列的像素33排列为矩阵状。并且,以具有与显示部32重叠的区域的方式设置数据驱动电路24a、数据驱动电路24b、电路25a及电路25b。就是说,图13所示的结构例子与图1所示的结构例子不同之处在于:一个显示部32中设置多个数据驱动电路24(数据驱动电路24a及数据驱动电路24b)及多个电路25(电路25a及电路25b)。

[0297]

数据驱动电路24a的输出端子通过布线27与电路25a的输入端子电连接,电路25a的输出端子通过布线26与例如第奇数列的像素33电连接。数据驱动电路24b的输出端子通过布线27与电路25b的输入端子电连接,电路25b的输出端子通过布线26与例如第偶数列的像素33电连接。

[0298]

图14是示出数据驱动电路24a、数据驱动电路24b、电路25a及电路25b的结构例子的方框图。此外,为了示出连接关系,图14还示出电路21、电位生成电路22及电位供应电路23。

[0299]

与图2所示的数据驱动电路24同样地,数据驱动电路24a及数据驱动电路24b包括寄存电路42、锁存电路43、电平转换电路44及传输晶体管逻辑电路45。与图2所示的电路25同样地,电路25a及电路25b包括附加电路50。

[0300]

例如,寄存电路42[1]、锁存电路43[1]、电平转换电路44[1]及传输晶体管逻辑电路45[1]设置在数据驱动电路24a,附加电路50[1]设置在电路25a。此外,寄存电路42[2]、锁存电路43[2]、电平转换电路44[2]及传输晶体管逻辑电路45[2]设置在数据驱动电路24b,附加电路50[2]设置在电路25b。并且,这些电路设置在区域105(1)。

[0301]

此外,例如寄存电路42[n-1]、锁存电路43[n-1]、电平转换电路44[n-1]及传输晶体管逻辑电路45[n-1]设置在数据驱动电路24a,附加电路50[n-1]设置在电路25a。此外,寄存电路42[n]、锁存电路43[n]、电平转换电路44[n]及传输晶体管逻辑电路45[n]设置在数据驱动电路24b,附加电路50[n]设置在电路25b。并且,这些电路设置在区域105(n/2)。

[0302]

由此,h为1以上且n/2以下的整数时,寄存电路42[2h-1]、锁存电路43[2h-1]、电平转换电路44[2h-1]及传输晶体管逻辑电路45[2h-1]设置在数据驱动电路24a,附加电路50[2h-1]设置在电路25a。此外,寄存电路42[2h]、锁存电路43[2h]、电平转换电路44[2h]及传输晶体管逻辑电路45[2h]设置在数据驱动电路24b,附加电路50[2h]设置在电路25b。并且,这些电路设置在区域105(h)。

[0303]

区域105例如可以为矩形。由此,可以将附加电路50[2h-1]、传输晶体管逻辑电路45[2h-1]、电平转换电路44[2h-1]、锁存电路43[2h-1]、寄存电路42[2h-1]、寄存电路42

[2h]、锁存电路43[2h]、电平转换电路44[2h]、传输晶体管逻辑电路45[2h]及附加电路50[2h]例如从顶面来看一直线上进行布局。

[0304]

由此,通过显示装置10具有图13及图14所示的结构,可以将构成数据驱动电路24的电路及构成电路25的电路高效地布局在与显示部32重叠的区域的整个面。例如,可以抑制在与显示部32重叠的区域的一部分稠密地设置晶体管等且在其他区域几乎不设置晶体管等。

[0305]

图1所示的显示装置10中,电位供应电路23l设置在数据驱动电路24l及电路25l的左侧,电位供应电路23r设置在数据驱动电路24r及电路25r的右侧。此外,栅极驱动电路31l设置在显示部32l的左侧,栅极驱动电路31r设置在显示部32r的右侧。就是说,图1所示的显示装置10中,以夹着数据驱动电路24及电路25对置的方式设置两个电位供应电路23。此外,以夹着显示部32对置的方式设置两个栅极驱动电路31。但是,本发明的一个方式不局限于此。图15是示出显示装置10的结构例子方框图,是图1所示的显示装置10的变形例子。图15所示的显示装置10与图1所示的显示装置10不同之处在于:数据驱动电路24l及电路25l与数据驱动电路24r及电路25r之间设置电位供应电路23,显示部32l与显示部32r之间设置栅极驱动电路31。

[0306]

图15所示的显示装置10可以在抑制产生离电位供应电路23的输出端子有的布线距离长的数据驱动电路24的同时相比于图1所示的显示装置10进一步减少电位供应电路23的个数。此外,可以在抑制产生离栅极驱动电路31的输出端子有的布线距离长的像素33的同时相比于图1所示的显示装置10进一步减少栅极驱动电路31的个数。由此,可以将显示装置10小型化。此外,可以扩大显示部32的面积。

[0307]

图16是示出图15所示的显示装置10包括的电位供应电路23的结构例子的电路图。注意,为了示出连接关系,图16还示出电位生成电路22、数据驱动电路24l及数据驱动电路24r。

[0308]

与图3所示的电位供应电路23同样地,图16所示的电位供应电路23包括放大电路51。如图16所示,放大电路51的输出端子可以与数据驱动电路24l及数据驱动电路24r的双方电连接。

[0309]

在图1所示的显示装置10中,设置一个电位供应电路23l及一个电位供应电路23r,但是本发明的一个方式不局限于此。图17是示出显示装置10的结构例子的方框图,也是图1所示的显示装置10的变形例子。图17所示的显示装置10与图1所示的显示装置10不同之处在于:设置两个电位供应电路23l及两个电位供应电路23r。

[0310]

通过增加设置在显示装置10的电位供应电路23的个数,可以减少电连接于一个电位供应电路23的数据驱动电路24的个数。由此,可以缩小电位供应电路23的输出端子的负载。由此,可以降低显示装置10的功耗。

[0311]

图1所示的显示装置10中,设置一个栅极驱动电路31l及一个栅极驱动电路31r,但是也可以设置多个栅极驱动电路31l及多个栅极驱动电路31r。例如,也可以设置两个栅极驱动电路31l及两个栅极驱动电路31r,也可以设置各自三个以上。此外,例如也可以设置与显示部32l相同数量的栅极驱动电路31l,也可以设置与显示部32r相同数量的栅极驱动电路31r。图18是图1所示的显示装置10的变形例子,包括与显示部32l相同数量的栅极驱动电路31l,并且示出包括与显示部32r相同数量的栅极驱动电路31r的结构。

[0312]

在设置多个栅极驱动电路31l及栅极驱动电路31r的情况下,可以并行驱动该多个栅极驱动电路31。此外,对应于栅极驱动电路31l的驱动可以并行驱动多个数据驱动电路24l及电路25l,此外,对应于栅极驱动电路31r的驱动可以并行驱动多个数据驱动电路24r及电路25r。由此,例如可以缩短将一帧图像对应的模拟数据写入到像素33所需的时间。因此,可以缩短一帧期间,并可以提高帧频率。由此,可以高速驱动显示装置10。

[0313]

图19是示出显示装置10的结构例子的方框图,也是图1所示的显示装置10的变形例子。图19所示的显示装置10与图1所示的显示装置10不同之处在于:不设置电位供应电路23r、数据驱动电路24r、电路25r、栅极驱动电路31r及显示部32r。在图19中,将电位供应电路23l、数据驱动电路24l、电路25l、栅极驱动电路31l及显示部32l分别记为电位供应电路23、数据驱动电路24、电路25、栅极驱动电路31及显示部32。另外,也可以不设置电位供应电路23l、数据驱动电路24l、电路25l、栅极驱动电路31l及显示部32l的结构。

[0314]

在图19所示的显示装置10中,可以使电位供应电路23的个数及栅极驱动电路31的个数少于图1所示的显示装置10。由此,可以使显示装置10小型化。此外,可以使显示部32的面积变大。

[0315]

图20是示出显示装置10的结构例子方框图,图19所示的显示装置10的变形例子。图20示出的显示装置10与图19所示的显示装置10不同之处在于:作为栅极驱动电路31包括栅极驱动电路31a及栅极驱动电路31b。如图20所示,栅极驱动电路31a可以设置在显示部32的左侧,栅极驱动电路31b可以设置在显示部32的右侧。

[0316]

图21是示出图20所示的显示装置10包括的层30的结构例子的方框图。如图21所示,栅极驱动电路31a的输出端子通过布线34例如与第奇数行的像素33电连接。此外,栅极驱动电路31b的输出端子通过布线34例如与第偶数行的像素33电连接。

[0317]

通过显示装置10具有图20及图21所示的结构,可以减小构成栅极驱动电路31的晶体管等的元件的密度。由此,可以提高显示装置10的布局自由度。此外,图20示出以具有与栅极驱动电路31a重叠的区域的方式设置电位供应电路23的结构,但是本发明的一个方式不局限于此。例如,也可以以具有与栅极驱动电路31b重叠的区域的方式设置电位供应电路23。此外,例如,也可以设置两个电位供应电路23,设置一方的电位供应电路23为具有与栅极驱动电路31a重叠的区域,设置另一方的电位供应电路23为具有与栅极驱动电路31b重叠的区域。另外,也可以设置例如三个以上的电位供应电路23。

[0318]

图22是示出显示装置10的结构例子方框图,图19所示的显示装置10的变形例子。图22示出的显示装置10与图19所示的显示装置10不同之处在于:栅极驱动电路31设置在层20中。

[0319]

图22所示的结构的显示装置10可以使栅极驱动电路31所包括的晶体管为例如沟道形成区域包含单晶硅的晶体管。如上所述,在沟道形成区域包含单晶硅的晶体管的通态电流大。因此,图22所示的结构的显示装置10可以高速驱动栅极驱动电路31。

[0320]

本实施方式的至少一部分可以与本说明书所记载的其他实施方式适当地组合而实施。

[0321]

(实施方式2)

[0322]

在本实施方式中,说明本发明的一个方式的显示装置10的截面结构例子。

[0323]

《显示装置的截面结构例子_1》

[0324]

图23是示出显示装置10的结构例子的截面图。显示装置10包括衬底701及衬底705,该衬底701及该衬底705使用密封剂712贴合在一起。

[0325]

作为衬底701,可以使用单晶硅衬底等单晶半导体衬底。此外,也可以使用单晶半导体衬底以外的半导体衬底作为衬底701。

[0326]

衬底701上设置有晶体管441及晶体管601。晶体管441及晶体管601可以为实施方式1所示的层20中设置的晶体管。

[0327]

晶体管441由用作栅电极的导电层443、用作栅极绝缘层的绝缘层445及衬底701的一部分构成,并包括含有沟道形成区域的半导体区域447、用作源区和漏区中的一个的低电阻区域449a及用作源区和漏区中的另一个的低电阻区域449b。晶体管441可以为p沟道型或n沟道型。

[0328]

晶体管441及其他的晶体管由元件分离层403电分离。图23示出晶体管441及晶体管601由元件分离层403电分离的情况。元件分离层403可以利用locos(local oxidation of silicon:硅局部氧化)法或sti(shallow trench isolation:浅沟槽隔离)法等形成。

[0329]

在此,在图23所示的晶体管441中,半导体区域447具有凸形状。此外,半导体区域447的侧面及顶面以隔着绝缘层445被导电层443覆盖的方式设置。注意,图23未示出导电层443覆盖半导体区域447的侧面的情况。此外,导电层443可以使用调整功函数的材料。

[0330]

像晶体管441那样,半导体区域具有凸形状的晶体管因利用半导体衬底的凸部而可以被称为鳍型晶体管。此外,也可以以与凸部的顶面接触的方式具有被用作用来形成凸部的掩模的绝缘层。此外,虽然在图23中示出对衬底701的一部分进行加工来形成凸部的情况,但是也可以对soi衬底进行加工来形成具有凸部的半导体。

[0331]

此外,图23所示的晶体管441的结构只是一个例子而不局限于该结构,可以根据电路结构或电路工作方法等采用合适的结构。例如,晶体管441可以为平面型晶体管。

[0332]

晶体管601可以采用与晶体管441相同的结构。

[0333]

衬底701上除了设置有元件分离层403、晶体管441及晶体管601以外还设置有绝缘层405、绝缘层407、绝缘层409及绝缘层411。在绝缘层405、绝缘层407、绝缘层409及绝缘层411中嵌入导电层451。在此,可以使导电层451的顶面的高度与绝缘层411的顶面的高度大致相同。

[0334]

导电层451及绝缘层411上设置有绝缘层421及绝缘层214。在绝缘层421及绝缘层214中嵌入导电层453。在此,可以使导电层453的顶面的高度与绝缘层214的顶面的高度大致相同。

[0335]

导电层453及绝缘层214上设置有绝缘层216。在绝缘层216中嵌入导电层455。在此,可以使导电层455的顶面的高度与绝缘层216的顶面的高度大致相同。

[0336]

导电层455及绝缘层216上设置有绝缘层222、绝缘层224、绝缘层254、绝缘层280、绝缘层274及绝缘层281。在绝缘层222、绝缘层224、绝缘层254、绝缘层280、绝缘层274及绝缘层281中嵌入导电层305。在此,可以使导电层305的顶面的高度与绝缘层281的顶面的高度大致相同。

[0337]

导电层305及绝缘层281上设置有绝缘层361。在绝缘层361中嵌入导电层317及导电层337。在此,可以使导电层337的顶面的高度与绝缘层361的顶面的高度大致相同。

[0338]

导电层337及绝缘层361上设置有绝缘层363。在绝缘层363中嵌入导电层347、导电

层353、导电层355及导电层357。在此,可以使导电层353、导电层355及导电层357的顶面的高度与绝缘层363的顶面的高度大致相同。

[0339]

导电层353、导电层355、导电层357及绝缘层363上设置有连接电极760。此外,以与连接电极760电连接的方式设置有各向异性导电层780,并以与各向异性导电层780电连接的方式设置有fpc(flexible printed circuit:柔性电路板)716。通过使用fpc716,可以从显示装置10的外部向显示装置10供应各种信号等。

[0340]

如图23所示,晶体管441的用作源区和漏区中的另一个的低电阻区域449b通过导电层451、导电层453、导电层455、导电层305、导电层317、导电层337、导电层347、导电层353、导电层355、导电层357、连接电极760及各向异性导电层780电连接于fpc716。在图23中,作为具有电连接连接电极760和导电层347的功能的导电层示出导电层353、导电层355及导电层357的三个导电层,但本发明的一个方式不局限于此。具有电连接连接电极760和导电层347的功能的导电层的个数可以为一个、两个、四个以上。通过设置具有电连接连接电极760和导电层347的功能的多个导电层,可以降低接触电阻。

[0341]

绝缘层214上设置有晶体管750。晶体管750可以为设置在实施方式1所示的层30中的晶体管。例如,可以为设置在像素33中的晶体管。作为晶体管750,可以适当地使用os晶体管。os晶体管具有关态电流极低的特征。由此,可以长时间保持图像数据等,从而可以降低刷新频率。由此,可以降低显示装置10的功耗。

[0342]

在绝缘层254、绝缘层280、绝缘层274及绝缘层281中嵌入导电层301a及导电层301b。导电层301a与晶体管750的源极和漏极中的一个电连接,导电层301b与晶体管750的源极和漏极中的另一个电连接。在此,可以使导电层301a及导电层301b的顶面的高度与绝缘层281的顶面的高度大致相同。

[0343]

在绝缘层361中嵌入导电层311、导电层313、导电层331、电容器790、导电层333及导电层335。导电层311及导电层313与晶体管750电连接并用作布线。导电层333及导电层335与电容器790电连接。在此,可以使导电层331、导电层333及导电层335的顶面的高度与绝缘层361的顶面的高度大致相同。

[0344]

在绝缘层363中嵌入导电层341、导电层343及导电层351。在此,可以使导电层351的顶面的高度与绝缘层363的顶面的高度大致相同。

[0345]

绝缘层405、绝缘层407、绝缘层409、绝缘层411、绝缘层421、绝缘层214、绝缘层280、绝缘层274、绝缘层281、绝缘层361及绝缘层363用作层间膜,也可以用作分别覆盖其下方的凹凸形状的平坦化膜。例如,为了提高绝缘层363的顶面的平坦性,可以通过利用化学机械抛光(cmp:chemical mechanical polishing)法等的平坦化处理使其平面平坦化。

[0346]

如图23所示,电容器790包括下部电极321及上部电极325。此外,下部电极321与上部电极325之间设置有绝缘层323。也就是说,电容器790具有一对电极间夹有用作介电体的绝缘层323的叠层型结构。此外,虽然图23示出绝缘层281上设置有电容器790的例子,但是也可以在与绝缘层281不同的绝缘层上设置电容器790。

[0347]

图23示出导电层301a、导电层301b及导电层305形成在同一层中的例子。此外,还示出导电层311、导电层313、导电层317及下部电极321形成在同一层中的例子。此外,还示出导电层331、导电层333、导电层335及导电层337形成在同一层中的例子。此外,还示出导电层341、导电层343及导电层347形成在同一层中的例子。此外,还示出导电层351、导电层

353、导电层355及导电层357形成在同一层中的例子。通过在同一层中形成多个导电层,可以简化显示装置10的制造工序,由此可以减少显示装置10的制造成本。此外,它们也可以分别形成在不同的层中并含有不同种类的材料。

[0348]

图23所示的显示装置10包括发光元件70。发光元件70包括导电层772、el层786及导电层788。el层786可以具有有机化合物或量子点等的无机化合物。

[0349]

作为可用于有机化合物的材料,可以举出荧光性材料或磷光性材料等。此外,作为可用于量子点的材料,可以举出胶状量子点、合金型量子点、核壳(core shell)型量子点、核型量子点等。

[0350]

导电层772通过导电层351、导电层341、导电层331、导电层313及导电层301b电连接于晶体管750的源极和漏极中的另一个。导电层772形成在绝缘层363上,并被用作像素电极。

[0351]

导电层772可以使用对可见光具有透光性的材料或具有反射性材料。作为透光性材料,例如,可以使用含有铟、锌、锡等的氧化物材料。作为反射性材料,例如,可以使用含有铝、银等材料。

[0352]

虽然图23中没有进行图示,显示装置10可以设置偏振构件、相位差构件、抗反射构件等的光学构件(光学衬底)等。

[0353]

衬底705一侧设置有遮光层738及与它们接触的绝缘层734。遮光层738具有遮蔽从邻接区域发射的光的功能。或者,遮光层738具有防止外光到达晶体管750等的功能。

[0354]

图23所示的显示装置10在绝缘层363上设置有绝缘层730。在此,绝缘层730可以覆盖导电层772的一部分。此外,发光元件70包括透光性导电层788并为顶部发射型发光元件。此外,发光元件70也可以采用向导电层772一侧射出光的底部发射结构或者向导电层772及导电层788的两侧射出光的双面发射结构。

[0355]

此外,遮光层738具有与绝缘层730重叠的区域。此外,遮光层738被绝缘层734覆盖。此外,密封层732填充发光元件70与绝缘层734之间的空间。

[0356]

再者,绝缘层730与el层786之间设置有结构体778。此外,绝缘层730与绝缘层734之间设置有结构体778。

[0357]

图24示出图23所示的显示装置10的变形例子。图24示出的显示装置10与图23所示的显示装置10的不同之处在于设置有着色层736。注意,以具有与发光元件70重叠的区域的方式设置着色层736。通过设置着色层736,可以提高从发光元件70提取的光的颜色纯度。因此,显示装置10能够显示高质量图像。此外,因为显示装置10中的所有发光元件70例如可以为发射白色光的发光元件,所以不需要分别涂布形成el层786,可以实现高清晰的显示装置10。

[0358]

发光元件70可以具有光学微腔谐振器(微腔)结构。由此,即使不设置着色层也可以提取规定的颜色的光(例如rgb),由此显示装置10能够进行彩色显示。通过采用不设置着色层的结构,可以抑制由着色层吸收光。由此,显示装置10能够显示高亮度图像,并且可以降低显示装置10的功耗。此外,当通过在各像素中将el层786形成为岛状或者在各像素列中将el层786形成为条状,也就是说,通过分别涂布来形成el层786时,也可以采用不设置着色层的结构。

[0359]

图23及图24示出作为显示元件在显示装置10中设置发光元件的结构,但是也可以

作为显示元件设置例如液晶元件。图25是图24所示的显示装置10的变形例子,与图24所示的显示装置10不同之处在于设置液晶元件80代替发光元件70。

[0360]

液晶元件80在导电层772、导电层774及这些之间包括液晶层776。导电层774设置在衬底705一侧,被用作公共电极。此外,导电层772通过导电层351、导电层341、导电层331、导电层313及导电层301b电连接于晶体管750的源极和漏极中的另一个。与发光元件70同样地,导电层772形成在绝缘层363上,并被用作像素电极。

[0361]

与发光元件70同样地,导电层772可以使用对可见光具有透光性的材料或具有反射性材料。当作为导电层772使用反射性材料时,显示装置10为反射型液晶显示装置。当作为导电层772使用透光性材料且衬底701等使用透光性材料时,显示装置10为透射型液晶显示装置。当为反射型液晶显示装置的情况下,在观看侧设置偏振片。当显示装置10为透射型液晶显示装置的情况下,以夹着液晶元件80的方式设置一对偏振片。注意,图25中不示出偏振片。

[0362]

虽然图25中没有进行图示,也可以采用设置与液晶层776接触的取向膜。此外,可以适当地设置偏振构件、相位差构件、抗反射构件等的光学构件(光学衬底)及背光、侧光等光源。

[0363]

在绝缘层363与导电层774之间设置有结构体778。结构体778是柱状的间隔物,是为了控制衬底701与衬底705之间的距离(单元间隙)而设置。此外,作为结构体778可以使用球状的间隔物。

[0364]

液晶层776可以使用热致液晶、低分子液晶、高分子液晶、高分子分散型液晶(pdlc:polymer dispersed liquid crystal)、高分子网络型液晶(pnlc:polymer network liquid crystal)、铁电液晶、反铁电液晶等。此外,在采用水平电场方式的情况下,也可以使用不需要取向膜的呈现蓝相的液晶。

[0365]

作为液晶元件的模式,可以采用tn(twisted nematic:扭曲向列)模式、va(vertical alignment:垂直取向)模式、ips(in-plane-switching:平面内转换)模式、ffs(fringe field switching:边缘电场转换)模式、asm(axially symmetric aligned micro-cell:轴对称排列微单元)模式、ocb(optically compensated birefringence:光学补偿弯曲)模式、ecb(electrically controlled birefringence:电控双折射)模式、宾主模式等。

[0366]

液晶层776可以采用使用高分子分散型液晶或高分子网络型液晶等的散乱型液晶。此时,可以采用不设置着色层736进行黑白色显示的结构,也可以采用使用着色层736进行彩色显示的结构。

[0367]

作为液晶元件的驱动方法,可以应用利用继时加法混色法进行彩色显示的分时显示方式(也称为场序制列驱动方式)。在该情况下,可以采用不设置着色层736的结构。当采用分时显示方式的情况下,例如无需设置分别呈现r(红色)、g(绿色)、b(蓝色)的子像素,因此具有可以提高像素的开口率、清晰度等优点。

[0368]

虽然在图23至图25中示出设置有其沟道形成区域形成在衬底701内部的晶体管441及晶体管601,并在该晶体管441及该晶体管601上层叠有os晶体管的结构,但是本发明的一个方式不局限于此。图26示出图24的变形例子。图26所示的显示装置10与图24所示的显示装置10的主要不同之处在于包括作为os晶体管的晶体管602及晶体管603而代替晶体

管441及晶体管601。此外,作为晶体管750可以使用os晶体管。也就是说,图26所示的显示装置10层叠地设置有os晶体管。

[0369]

衬底701上设置有绝缘层613及绝缘层614,并且绝缘层614上设置有晶体管602及晶体管603。此外,也可以将晶体管等设置在衬底701与绝缘层613之间。例如,也可以在衬底701与绝缘层613之间设置与图24所示的晶体管441及晶体管601相同的晶体管。

[0370]

晶体管602及晶体管603可以为设置在实施方式1所示的层20中的晶体管。

[0371]

晶体管602及晶体管603可以为其结构与晶体管750相同的晶体管。此外,晶体管602及晶体管603也可以为其结构与晶体管750不同的os晶体管。

[0372]

绝缘层614上除了设置有晶体管602及晶体管603以外还设置有绝缘层616、绝缘层622、绝缘层624、绝缘层654、绝缘层680、绝缘层674及绝缘层681。在绝缘层654、绝缘层680、绝缘层674及绝缘层681中嵌入导电层461。在此,可以使导电层461的顶面的高度与绝缘层681的顶面的高度大致相同。

[0373]

导电层461及绝缘层681上设置有绝缘层501。在绝缘层501中嵌入导电层463。在此,可以使导电层463的顶面的高度与绝缘层501的顶面的高度大致相同。

[0374]

导电层463及绝缘层501上设置有绝缘层421及绝缘层214。在绝缘层421及绝缘层214中嵌入导电层453。在此,可以使导电层453的顶面的高度与绝缘层214的顶面的高度大致相同。

[0375]

如图26所示,晶体管602的源极和漏极中的一个通过导电层461、导电层463、导电层453、导电层455、导电层305、导电层317、导电层337、导电层347、导电层353、导电层355、导电层357、连接电极760及各向异性导电层780电连接于fpc716。

[0376]

绝缘层613、绝缘层614、绝缘层680、绝缘层674、绝缘层681及绝缘层501用作层间膜,也可以用作分别覆盖其下方的凹凸形状的平坦化膜。

[0377]

通过采用图26所示的显示装置10的结构,可以在实现显示装置10的窄边框化及小型化的同时作为显示装置10中的所有晶体管使用os晶体管。由此,例如可以使用同一装置制造实施方式1所示的层20中的晶体管和层30中的晶体管。由此,可以减少显示装置10的制造成本,并可以提供廉价的显示装置10。

[0378]

《显示装置的截面结构例子_2》

[0379]

图27是示出显示装置10的结构例子的截面图。与图24中的显示装置10的主要不同之处在于在具有晶体管750的层与具有晶体管602及晶体管603的层之间包括具有晶体管800的层。此外,在图27中示出晶体管601、晶体管750、晶体管800包括彼此重叠的区域的结构,但是不局限于此。例如,也可以为如下结构:晶体管601及晶体管750包括彼此重叠的区域且晶体管800与晶体管601及晶体管750不包括彼此重叠的区域。或者,也可以为如下结构:晶体管601及晶体管800包括彼此重叠的区域且晶体管750与晶体管601及晶体管800不包括彼此重叠的区域。

[0380]

实施方式1所示的层20可以具有第一电路层及第一电路层上的第二电路层的叠层结构。例如,晶体管601及晶体管603可以为设置在第一电路层中的晶体管。晶体管800可以为设置在第二电路层中的晶体管。晶体管750可以为设置在实施方式1所示的层30中的晶体管。

[0381]

导电层451及绝缘层411上设置有绝缘层821及绝缘层814。在绝缘层821及绝缘层

814中嵌入导电层853。在此,可以使导电层853的顶面的高度与绝缘层814的顶面的高度大致相同。

[0382]

导电层853及绝缘层814上设置有绝缘层816。在绝缘层816中嵌入导电层855。在此,可以使导电层855的顶面的高度与绝缘层816的顶面的高度大致相同。

[0383]

导电层855及绝缘层816上设置有绝缘层822、绝缘层824、绝缘层854、绝缘层880、绝缘层874及绝缘层881。在绝缘层822、绝缘层824、绝缘层854、绝缘层880、绝缘层874及绝缘层881中嵌入导电层805。在此,可以使导电层805的顶面的高度与绝缘层881的顶面的高度大致相同。

[0384]

导电层817及绝缘层881上设置有绝缘层421及绝缘层214。

[0385]

如图27所示,被用作晶体管441的源极区域和漏极区域中的另一个的低电阻区域449b通过导电层451、导电层853、导电层855、导电层805、导电层817、导电层453、导电层455、导电层305、导电层317、导电层337、导电层347、导电层353、导电层355、导电层357、连接电极760及各向异性导电层780电连接于fpc716。

[0386]

绝缘层814上设置有晶体管800。晶体管800可以为设置在实施方式1所示的层30中的晶体管。晶体管800优选为os晶体管。

[0387]

在绝缘层854、绝缘层880、绝缘层874及绝缘层881中嵌入导电层801a及导电层801b。导电层801a与晶体管800的源极和漏极中的一个电连接,导电层801b与晶体管800的源极和漏极中的另一个电连接。在此,可以使导电层801a及导电层801b的顶面的高度与绝缘层881的顶面的高度大致相同。

[0388]

晶体管750可以为设置在实施方式1所示的层30中的晶体管。例如,晶体管750可以为设置在像素33中的晶体管。晶体管750优选为os晶体管。

[0389]

此外,也可以在设置有晶体管441及晶体管601等的层与设置有晶体管800等的层之间设置os晶体管等。此外,也可以在设置有晶体管800等的层与设置有晶体管750等的层之间设置os晶体管等。再者,也可以在设置有晶体管750等的层上方设置os晶体管等。

[0390]

绝缘层405、绝缘层407、绝缘层409、绝缘层411、绝缘层821、绝缘层814、绝缘层880、绝缘层874、绝缘层881、绝缘层421、绝缘层214、绝缘层280、绝缘层274、绝缘层281、绝缘层361及绝缘层363用作层间膜,也可以用作分别覆盖其下方的凹凸形状的平坦化膜。

[0391]

在图27中,示出在同一层形成导电层801a、导电层801b及导电层805的例子。此外,示出在同一层形成导电层811、导电层813及导电层817的例子。

[0392]

虽然在图27中示出设置有其沟道形成区域形成在衬底701内部的晶体管441及晶体管601,并在该晶体管441及该晶体管601上层叠有os晶体管的结构,但是本发明的一个方式不局限于此。图28示出图27的变形例子。图28所示的显示装置10与图27所示的显示装置10不同之处在于包括作为os晶体管的晶体管602及晶体管603而代替晶体管441及晶体管601。也就是说,图28所示的显示装置10设置有三层的os晶体管的叠层。

[0393]

此外,也可以在设置有晶体管602及晶体管603等的层与设置有晶体管800等的层之间设置os晶体管等。此外,也可以在设置有晶体管800等的层与设置有晶体管750或晶体管750等的层之间设置os晶体管等。再者,也可以在设置有晶体管750等的层上方设置os晶体管等。

[0394]

例如,晶体管602及晶体管603可以为设置在第一电路层中的晶体管。晶体管800可

以为设置在第二电路层中的晶体管。晶体管750可以为设置在实施方式1所示的层30中的晶体管。

[0395]

导电层463及绝缘层501上设置有绝缘层821及绝缘层814。在绝缘层821及绝缘层814中嵌入导电层853。在此,可以使导电层853的顶面的高度与绝缘层814的顶面的高度大致相同。

[0396]

如图28所示,晶体管602的源极和漏极中的一个通过导电层461、导电层463、导电层853、导电层855、导电层805、导电层817、导电层453、导电层455、导电层305、导电层317、导电层337、导电层347、导电层353、导电层355、导电层357、连接电极760及各向异性导电层780电连接于fpc716。

[0397]

通过采用图28所示的显示装置10的结构,可以在实现显示装置10的窄边框化及小型化的同时作为显示装置10中的所有晶体管使用os晶体管。由此,不需要形成不同种类的晶体管,因此可以减少显示装置10的制造成本,并可以提供廉价的显示装置10。

[0398]

本实施方式的至少一部分可以与本说明书所记载的其他实施方式适当地组合而实施。

[0399]

(实施方式3)

[0400]

在本实施方式中,说明可以用于本发明的一个方式的显示装置的晶体管。

[0401]

《晶体管的结构例子_1》

[0402]

图29a、图29b及图29c是可以用于本发明的一个方式的显示装置的晶体管200a及晶体管200a周边的俯视图及截面图。可以将晶体管200a应用于本发明的一个方式的显示装置。

[0403]

图29a是晶体管200a的俯视图。此外,图29b及图29c是晶体管200a的截面图。在此,图29b是沿着图29a中的点划线a1-a2的截面图,该截面图相当于晶体管200a的沟道长度方向上的截面图。图29c是沿着图29a中的点划线a3-a4的截面图,该截面图相当于晶体管200a的沟道宽度方向上的截面图。注意,为了容易理解,在图29a的俯视图中省略部分构成要素。

[0404]

如图29所示,晶体管200a包括:配置在衬底(未图示)上的金属氧化物230a;配置在金属氧化物230a上的金属氧化物230b;配置在金属氧化物230b上的相互分离的导电层242a及导电层242b;配置在导电层242a及导电层242b上的以与导电层242a与导电层242b之间重叠的方式形成开口的绝缘层280;配置在开口中的导电层260;配置在金属氧化物230b、导电层242a、导电层242b以及绝缘层280与导电层260之间的绝缘层250;以及配置在金属氧化物230b、导电层242a、导电层242b以及绝缘层280与绝缘层250之间的金属氧化物230c。在此,如图29b和图29c所示,导电层260的顶面优选与绝缘层250、绝缘层254、金属氧化物230c以及绝缘层280的顶面大致一致。以下,金属氧化物230a、金属氧化物230b以及金属氧化物230c有时被统称为金属氧化物230。此外,导电层242a及导电层242b有时被统称为导电层242。

[0405]

在图29所示的晶体管200a中,导电层242a及导电层242b的位于导电层260一侧的侧面大致垂直于底面。此外,图29所示的晶体管200a不局限于此,也可以采用导电层242a及导电层242b的侧面和底面所形成的角度为10

°

以上且80

°

以下,优选为30

°

以上且60

°

以下的结构。此外,也可以采用导电层242a和导电层242b的相对的侧面具有多个面的结构。

[0406]

此外,如图29所示,优选在绝缘层224、金属氧化物230a、金属氧化物230b、导电层

242a、导电层242b及金属氧化物230c与绝缘层280之间配置有绝缘层254。在此,如图29b、图29c所示,绝缘层254优选与金属氧化物230c的侧面、导电层242a的顶面及侧面、导电层242b的顶面及侧面、金属氧化物230a及金属氧化物230b的侧面以及绝缘层224的顶面接触。

[0407]

注意,在晶体管200a中,在形成沟道的区域(以下也称为沟道形成区域)及其附近层叠有金属氧化物230a、金属氧化物230b及金属氧化物230c的三层,但是本发明的一个方式不局限于此。例如,可以是金属氧化物230b与金属氧化物230c的两层结构或者四层以上的叠层结构。此外,在晶体管200a中,导电层260具有两层结构,但是本发明的一个方式不局限于此。例如,导电层260也可以具有单层结构或三层以上的叠层结构。此外,金属氧化物230a、金属氧化物230b以及金属氧化物230c也可以各自具有两层以上的叠层结构。

[0408]

例如,在金属氧化物230c具有由第一金属氧化物和第一金属氧化物上的第二金属氧化物构成的叠层结构的情况下,优选的是,第一金属氧化物具有与金属氧化物230b同样的组成,而第二金属氧化物具有与金属氧化物230a同样的组成。

[0409]

在此,导电层260被用作晶体管的栅电极,导电层242a及导电层242b各被用作源电极或漏电极。如上所述,导电层260以嵌入绝缘层280的开口及被夹在导电层242a与导电层242b之间的区域中的方式形成。在此,导电层260、导电层242a及导电层242b的配置相对于绝缘层280的开口自对准地被选择。也就是说,在晶体管200a中,栅电极可以自对准地配置在源电极与漏电极之间。由此,可以以不设置用于对准的余地的方式形成导电层260,所以可以实现晶体管200a的占有面积的缩小。由此,可以实现显示装置的高清晰化。此外,可以实现窄边框的显示装置。

[0410]

如图29所示,导电层260优选包括配置在绝缘层250的内侧的导电层260a及以嵌入导电层260a的内侧的方式配置的导电层260b。

[0411]

晶体管200a优选包括配置在衬底(未图示)上的绝缘层214、配置在绝缘层214上的绝缘层216、以嵌入绝缘层216的方式配置的导电层205、配置在绝缘层216及导电层205上的绝缘层222以及配置在绝缘层222上的绝缘层224。优选在绝缘层224上配置有金属氧化物230a。

[0412]

优选在晶体管200a上配置有被用作层间膜的绝缘层274及绝缘层281。在此,绝缘层274优选与导电层260、绝缘层250、绝缘层254、金属氧化物230c以及绝缘层280的顶面接触。

[0413]

此外,绝缘层222、绝缘层254以及绝缘层274优选具有抑制氢(例如,氢原子、氢分子等)中的至少一个的扩散的功能。例如,绝缘层222、绝缘层254以及绝缘层274的氢透过性优选低于绝缘层224、绝缘层250以及绝缘层280。此外,绝缘层222及绝缘层254优选具有抑制氧(例如,氧原子、氧分子等)中的至少一个的扩散的功能。例如,绝缘层222及绝缘层254的氧透过性优选低于绝缘层224、绝缘层250以及绝缘层280。

[0414]

在此,绝缘层224、金属氧化物230以及绝缘层250与绝缘层280及绝缘层281由绝缘层254以及绝缘层274相隔。由此,可以抑制包含在绝缘层280及绝缘层281中的氢等杂质及过剩的氧混入绝缘层224、金属氧化物230a、金属氧化物230b以及绝缘层250中。

[0415]

半导体装置优选包括与晶体管200a电连接且被用作插头的导电层240(导电层240a及导电层240b)。此外,还包括与被用作插头的导电层240的侧面接触的绝缘层241(绝缘层241a及绝缘层241b)。也就是说,绝缘层241以与绝缘层254、绝缘层280、绝缘层274以及

绝缘层281的开口的内壁接触的方式形成。此外,可以以与绝缘层241的侧面接触的方式设置有导电层240的第一导电层且在其内侧设置第二导电层。在此,导电层240的顶面的高度与绝缘层281的顶面的高度可以大致相同。此外,示出在晶体管200a中,层叠有导电层240的第一导电体及导电层240的第二导电层的结构,但是本发明不局限于此。例如,导电层240也可以具有单层结构或者三层以上的叠层结构。在结构体具有叠层结构的情况下,有时按形成顺序赋予序数以进行区別。

[0416]

优选在晶体管200a中将被用作氧化物半导体的金属氧化物(以下也称为氧化物半导体)用于包含沟道形成区域的金属氧化物230(金属氧化物230a、金属氧化物230b及金属氧化物230c)。例如,作为将成为金属氧化物230的沟道形成区域的金属氧化物,优选使用其带隙为2ev以上,优选为2.5ev以上的金属氧化物。

[0417]

作为上述金属氧化物,优选至少包含铟(in)或锌(zn)。尤其是,优选包含铟(in)或锌(zn)。此外,除此之外,优选还包含元素m。元素m可以为铝(al)、镓(ga)、钇(y)、锡(sn)、硼(b)、钛(ti)、铁(fe)、镍(ni)、锗(ge)、锆(zr)、钼(mo)、镧(la)、铈(ce)、钕(nd)、铪(hf)、钽(ta)、钨(w)、镁(mg)和钴(co)等中的一种以上。尤其是,元素m优选为铝(al)、镓(ga)、钇(y)和锡(sn)中的一种以上。另外,元素m更优选包含ga和sn中的任一个或两个。

[0418][0419]

此外,如图29b所示,金属氧化物230b中的不与导电层242重叠的区域的厚度有时比其与导电层242重叠的区域的厚度薄。这是因为当形成导电层242a及导电层242b时去除金属氧化物230b的顶面的一部分的缘故。当在金属氧化物230b的顶面上形成用作导电层242的导电膜时,有时在与该导电膜的界面附近形成低电阻区域。如此,通过去除金属氧化物230b的顶面上的位于导电层242a与导电层242b之间的低电阻区域,可以抑制沟道形成在该区域中。

[0420]

通过本发明的一个方式,可以提供一种包括尺寸小的晶体管并其清晰度高的显示装置。此外,可以提供一种包括通态电流大的晶体管并其亮度高的显示装置。此外,可以提供一种包括工作速度快的晶体管并其工作速度快的显示装置。此外,可以提供一种包括电特性稳定的晶体管并其可靠性高的显示装置。此外,可以提供一种包括关态电流小的晶体管并其低功耗的显示装置。

[0421]

以下说明可以用于本发明的一个方式的显示装置的晶体管200a的详细结构。

[0422]

导电层205以包括与金属氧化物230及导电层260重叠的区域的方式配置。此外,导电层205优选以嵌入绝缘层216中的方式设置。

[0423]

导电层205包括导电层205a、导电层205b及导电层205c。导电层205a与设置在绝缘层216中的开口的底面及侧壁接触。导电层205b以埋入于形成在导电层205a的凹部的方式设置。在此,导电层205b的顶面低于导电层205a的顶面及绝缘层216的顶面。导电层205c与导电层205b的顶面及导电层205a的侧面接触。在此,导电层205c的顶面的高度与导电层205a的顶面的高度及绝缘层216的顶面的高度大致一致。换言之、导电层205b由导电层205a及导电层205c包围。

[0424]

作为导电层205a及导电层205c优选使用具有抑制氢原子、氢分子、水分子、氮原子、氮分子、氧化氮分子(n2o、no、no2等)、铜原子等杂质的扩散的功能的导电材料。此外,优选使用具有抑制氧(例如,氧原子、氧分子等中的至少一个)的扩散的功能的导电材料。

[0425]

通过作为导电层205a及导电层205c使用具有减低氢的扩散的功能的导电材料,可以抑制导电层205b中的氢等杂质通过绝缘层224等扩散到金属氧化物230。此外,通过作为导电层205a及导电层205c使用具有抑制氧的扩散的功能的导电材料,可以抑制使导电层205b氧化而导致导电率的下降。作为具有抑制氧的扩散的功能的导电材料,例如,优选使用钛、氮化钛、钽、氮化钽、钌、氧化钌等。因此,作为导电层205a可以使用上述导电材料的单层或叠层。例如,作为导电层205a使用氮化钽即可。

[0426]

另外,作为导电层205b优选使用以钨、铜或铝为主要成分的导电材料。例如,作为导电层205b使用钨即可。

[0427]

在此,导电层260有时被用作第一栅极(也称为顶栅极)电极。此外,导电层205有时被用作第二栅极(也称为底栅极)电极。在此情况下,通过独立地改变供应到导电层205的电位而不使其与供应到导电层260的电位联动,可以控制晶体管200a的v

th

。尤其是,通过对导电层205供应负电位,可以使晶体管200a的v

th

大于0v且可以减小关态电流。因此,与不对导电层205施加负电位时相比,在对导电层205施加负电位的情况下,可以减小对导电层260供应的电位为0v时的漏极电流。

[0428]

此外,导电层205优选比金属氧化物230中的沟道形成区域大。尤其是,如图29c所示,导电层205优选延伸到与沟道宽度方向上的金属氧化物230交叉的端部的外侧的区域。就是说,优选在金属氧化物230的沟道宽度方向的侧面的外侧,导电层205和导电层260隔着绝缘层重叠。

[0429]

就是说通过具有上述结构,可以由被用作第一栅电极的导电层260的电场和被用作第二栅电极的导电层205的电场电围绕金属氧化物230的沟道形成区域。

[0430]

此外,如图29c所示,将导电层205延伸来用作布线。但是,本发明不局限于此,也可以在导电层205下设置被用作布线的导电层。

[0431]

绝缘层214优选被用作抑制水或氢等杂质从衬底一侧进入晶体管200a的阻挡绝缘膜。因此,作为绝缘层214优选使用具有抑制氢原子、氢分子、水分子、氮原子、氮分子、氧化氮分子(n2o、no、no2等)、铜原子等杂质的扩散的功能(不容易使上述杂质透过)的绝缘材料。此外,优选使用具有抑制氧(例如,氧原子、氧分子等)中的至少一个的扩散的功能(不容易使上述氧透过)的绝缘材料。

[0432]

例如,优选的是,作为绝缘层214使用氧化铝或氮化硅等。由此,可以抑制水或氢等杂质从与绝缘层214相比更靠近衬底一侧扩散到晶体管200a一侧。此外,可以抑制包含在绝缘层224等中的氧扩散到与绝缘层214相比更靠近衬底一侧。

[0433]

被用作层间膜的绝缘层216、绝缘层280及绝缘层281的介电常数优选比绝缘层214低。通过将介电常数低的材料作为层间膜,可以减少产生在布线之间的寄生电容。例如,作为绝缘层216、绝缘层280及绝缘层281,适当地使用氧化硅、氧氮化硅、氮氧化硅、氮化硅、添加有氟的氧化硅、添加有碳的氧化硅、添加有碳及氮的氧化硅或具有空孔的氧化硅等。

[0434]

绝缘层222及绝缘层224被用作栅极绝缘层。

[0435]

在此,在与金属氧化物230接触的绝缘层224中,优选通过加热使氧脱离。在本说明书等中,有时将通过加热脱离的氧称为过剩氧。例如,作为绝缘层224适当地使用氧化硅或氧氮化硅等,即可。通过以与金属氧化物230接触的方式设置包含氧的绝缘层,可以减少金属氧化物230中的氧缺陷,从而可以提高晶体管200a的可靠性。

[0436]

具体而言,作为绝缘层224,优选使用通过加热使一部分的氧脱离的氧化物材料。通过加热使氧脱离的氧化物是指在tds(thermal desorption spectroscopy:热脱附谱)分析中换算为氧原子的氧的脱离量为1.0

×

10

18

atoms/cm3以上,优选为1.0

×

10

19

atoms/cm3以上,进一步优选为2.0

×

10

19

atoms/cm3以上,或者3.0

×

10

20

atoms/cm3以上的氧化物膜。此外,进行上述tds分析时的膜的表面温度优选在100℃以上且700℃以下,或者100℃以上且400℃以下的范围内。

[0437]

如图29c所示,有时在绝缘层224中不与绝缘层254重叠并不与金属氧化物230b重叠的区域的厚度比其他区域的厚度薄。在绝缘层224中,不与绝缘层254重叠并不与金属氧化物230b重叠的区域优选具有足够使上述氧扩散的厚度。

[0438]

与绝缘层214等同样,绝缘层222优选被用作抑制水或氢等杂质从衬底一侧混入晶体管200a的阻挡绝缘膜。例如,绝缘层222的氢透过性优选比绝缘层224低。通过由绝缘层222、绝缘层254以及绝缘层274围绕绝缘层224、金属氧化物230以及绝缘层250等,可以抑制水或氢等杂质从外部侵入晶体管200a。

[0439]

再者,绝缘层222优选具有抑制氧(例如,氧原子、氧分子等)中的至少一个的扩散的功能(不容易使上述氧透过)。例如,绝缘层222的氧透过性优选比绝缘层224低。通过使绝缘层222具有抑制氧及杂质的扩散的功能,可以减少金属氧化物230所具有的氧扩散到衬底一侧,所以是优选的。此外,可以抑制导电层205与绝缘层224及金属氧化物230所具有的氧起反应。

[0440]

绝缘层222优选为绝缘材料的包含铝和铪中的一方或双方的氧化物的绝缘层。作为包含铝和铪中的一方或双方的氧化物的绝缘层,优选使用氧化铝、氧化铪、包含铝及铪的氧化物(铝酸铪)等。当使用这种材料形成绝缘层222时,绝缘层222被用作抑制氧从金属氧化物230释放及氢等杂质从晶体管200a的周围部进入金属氧化物230的层。

[0441]

或者,例如也可以对上述绝缘层添加氧化铝、氧化铋、氧化锗、氧化铌、氧化硅、氧化钛、氧化钨、氧化钇、氧化锆。此外,也可以对上述绝缘层进行氮化处理。还可以在上述绝缘层上层叠氧化硅、氧氮化硅或氮化硅。

[0442]

作为绝缘层222,例如也可以以单层或叠层使用包含氧化铝、氧化铪、氧化钽、氧化锆、锆钛酸铅(pzt)、钛酸锶(srtio3)或(ba,sr)tio3(bst)等所谓的high-k材料的绝缘层。当进行晶体管的微型化及高集成化时,由于栅极绝缘层的薄膜化,有时发生泄漏电流等问题。通过作为被用作栅极绝缘层的绝缘层使用high-k材料,可以在保持物理厚度的同时降低晶体管工作时的栅极电位。

[0443]

此外,绝缘层222及绝缘层224也可以具有两层以上的叠层结构。此时,不局限于由相同材料构成的叠层结构,也可以是由不同材料构成的叠层结构。例如,也可以在绝缘层222下设置与绝缘层224同样的绝缘层。

[0444]

金属氧化物230包括金属氧化物230a、金属氧化物230a上的金属氧化物230b及金属氧化物230b上的金属氧化物230c。当在金属氧化物230b下设置金属氧化物230a时,可以抑制杂质从形成在金属氧化物230a下方的结构物扩散到金属氧化物230b。当在金属氧化物230b上设置金属氧化物230c时,可以抑制杂质从形成在金属氧化物230c的上方的结构物扩散到金属氧化物230b。

[0445]

此外,金属氧化物230优选具有各金属原子的原子个数比互不相同的氧化物的叠

层结构。例如,在金属氧化物230至少包含铟(in)及元素m的情况下,金属氧化物230a中的元素m与构成金属氧化物230a的全部元素的原子个数比优选大于金属氧化物230b中的元素m与构成金属氧化物230b的全部元素的原子个数比。此外,金属氧化物230a中的元素m与in的原子个数比优选大于金属氧化物230b中的元素m与in的原子个数比。在此,金属氧化物230c可以使用可用于金属氧化物230a或金属氧化物230b的金属氧化物。

[0446]

优选的是,使金属氧化物230a及金属氧化物230c的导带底的能量高于金属氧化物230b的导带底的能量。换言之,金属氧化物230a及金属氧化物230c的电子亲和势优选小于金属氧化物230b的电子亲和势。在此情况下,金属氧化物230c优选使用可以用于金属氧化物230a的金属氧化物。具体而言,金属氧化物230c中的元素m与构成金属氧化物230c的全部元素的原子个数比优选大于金属氧化物230b中的元素m与构成金属氧化物230b的全部元素的原子个数比。此外,金属氧化物230c中的元素m与in的原子个数比优选大于金属氧化物230b中的元素m与in的原子个数比。

[0447]

在此,在金属氧化物230a、金属氧化物230b及金属氧化物230c的接合部中,导带底的能级平缓地变化。换言之,也可以将上述情况表达为金属氧化物230a、金属氧化物230b及金属氧化物230c的接合部的导带底的能级连续地变化或者连续地接合。为此,优选降低形成在金属氧化物230a与金属氧化物230b的界面以及金属氧化物230b与金属氧化物230c的界面的混合层的缺陷态密度。

[0448]

具体而言,通过使金属氧化物230a与金属氧化物230b以及金属氧化物230b与金属氧化物230c除了氧之外还包含共同元素(为主要成分),可以形成缺陷态密度低的混合层。例如,在金属氧化物230b为in-ga-zn氧化物的情况下,作为金属氧化物230a及金属氧化物230c可以使用in-ga-zn氧化物、ga-zn氧化物及氧化镓等。此外,金属氧化物230c可以具有叠层结构。例如,可以使用in-ga-zn氧化物和该in-ga-zn氧化物上的ga-zn氧化物的叠层结构,或者,可以使用in-ga-zn氧化物和该in-ga-zn氧化物上的氧化镓的叠层结构。换言之,作为金属氧化物230c,也可以使用in-ga-zn氧化物和不包含in的氧化物的叠层结构。

[0449]

具体而言,作为金属氧化物230a使用in:ga:zn=1:3:4[原子个数比]或1:1:0.5[原子个数比]的金属氧化物,即可。此外,作为金属氧化物230b使用in:ga:zn=4:2:3[原子个数比]或3:1:2[原子个数比]的金属氧化物,即可。此外,作为金属氧化物230c使用in:ga:zn=1:3:4[原子个数比]、in:ga:zn=4:2:3[原子个数比]、ga:zn=2:1[原子个数比]或ga:zn=2:5[原子个数比]的金属氧化物,即可。此外,作为金属氧化物230c具有叠层结构的情况下的具体例子,可以举出in:ga:zn=4:2:3[原子个数比]和ga:zn=2:1[原子个数比]的叠层结构、in:ga:zn=4:2:3[原子个数比]和ga:zn=2:5[原子个数比]的叠层结构、in:ga:zn=4:2:3[原子个数比]和氧化镓的叠层结构等。

[0450]

此时,载流子的主要路径为金属氧化物230b。通过使金属氧化物230a及金属氧化物230c具有上述结构,可以降低金属氧化物230a与金属氧化物230b的界面及金属氧化物230b与金属氧化物230c的界面的缺陷态密度。因此,界面散射对载流子传导的影响减少,从而晶体管200a可以得到高通态电流及高频率特性。此外,在金属氧化物230c具有叠层结构时,被期待降低上述金属氧化物230b和金属氧化物230c之间的界面的缺陷态密度的效果及抑制金属氧化物230c所具有的构成元素扩散到绝缘层250一侧的效果。更具体而言,在金属氧化物230c具有叠层结构时,因为使不包含in的氧化物位于叠层结构的上方,所以可以抑

制会扩散到绝缘层250一侧的in。由于绝缘层250被用作栅极绝缘层,因此在in扩散在其中的情况下导致晶体管的特性不良。由此,通过使金属氧化物230c具有叠层结构,可以提供可靠性高的显示装置。

[0451]

在金属氧化物230b上设置被用作源电极及漏电极的导电层242(导电层242a及导电层242b)。作为导电层242,优选使用选自铝、铬、铜、银、金、铂、钽、镍、钛、钼、钨、铪、钒、铌、锰、镁、锆、铍、铟、钌、铱、锶和镧中的金属元素、以上述金属元素为成分的合金或者组合上述金属元素的合金等。例如,优选使用氮化钽、氮化钛、钨、包含钛和铝的氮化物、包含钽和铝的氮化物、氧化钌、氮化钌、包含锶和钌的氧化物、包含镧和镍的氧化物等。此外,氮化钽、氮化钛、包含钛和铝的氮化物、包含钽和铝的氮化物、氧化钌、氮化钌、包含锶和钌的氧化物、包含镧和镍的氧化物是不容易氧化的导电材料或者吸收氧也维持导电性的材料,所以是优选的。

[0452]

通过以与金属氧化物230接触的方式形成上述导电层242,金属氧化物230中的导电层242附近的氧浓度有时降低。此外,在金属氧化物230中的导电层242附近有时形成包括包含在导电层242中的金属及金属氧化物230的成分的金属化合物层。在此情况下,金属氧化物230的导电层242附近的区域中的载流子密度增加,该区域的电阻降低。

[0453]

在此,导电层242a与导电层242b之间的区域以与绝缘层280的开口重叠的方式形成。因此,可以在导电层242a与导电层242b之间自对准地配置导电层260。

[0454]

绝缘层250被用作栅极绝缘层。绝缘层250优选与金属氧化物230c的顶面接触地配置。绝缘层250可以使用氧化硅、氧氮化硅、氮氧化硅、氮化硅、添加有氟的氧化硅、添加有碳的氧化硅、添加有碳及氮的氧化硅、具有空孔的氧化硅。尤其是,氧化硅及氧氮化硅具有热稳定性,所以是优选的。

[0455]

与绝缘层224同样,优选降低绝缘层250中的水或氢等杂质的浓度。绝缘层250的厚度优选为1nm以上且20nm以下。

[0456]

也可以在绝缘层250与导电层260之间设置金属氧化物。该金属氧化物优选抑制从绝缘层250扩散到导电层260的氧。由此,可以抑制因绝缘层250中的氧所导致的导电层260的氧化。

[0457]

该金属氧化物有时被用作栅极绝缘层的一部分。因此,在将氧化硅及氧氮化硅等用于绝缘层250的情况下,作为该金属氧化物优选使用作为相对介电常数高的high-k材料的金属氧化物。通过使栅极绝缘层具有绝缘层250与该金属氧化物的叠层结构,可以形成具有热稳定性且相对介电常数高的叠层结构。因此,可以在保持栅极绝缘层的物理厚度的同时降低在晶体管工作时施加的栅极电位。此外,可以减少被用作栅极绝缘层的绝缘层的等效氧化物厚度(eot:equivalent oxide thickness)。

[0458]

具体而言,可以使用包含选自铪、铝、镓、钇、锆、钨、钛、钽、镍、锗和镁等中的一种或两种以上的金属氧化物。特别是,优选使用作为包含铝及铪中的一方或双方的氧化物的绝缘层的氧化铝、氧化铪、包含铝及铪的氧化物(铝酸铪)等。

[0459]

虽然在图29中,导电层260具有两层结构,但是也可以具有单层结构或三层以上的叠层结构。

[0460]

作为导电层260a优选使用上述具有抑制氢原子、氢分子、水分子、氮原子、氮分子、氧化氮分子(n2o、no、no2等)、铜原子等杂质的扩散的功能的导电材料。此外,优选使用具有

抑制氧(例如,氧原子、氧分子等)中的至少一个的扩散的功能的导电材料。

[0461]

当导电层260a具有抑制氧的扩散的功能时,可以抑制绝缘层250所包含的氧使导电层260b氧化而导致导电率的下降。作为具有抑制氧的扩散的功能的导电材料,例如,优选使用钽、氮化钽、钌或氧化钌等。

[0462]

作为导电层260b优选使用以钨、铜或铝为主要成分的导电材料。此外,由于导电层260还被用作布线,所以优选使用导电性高的材料。例如,可以使用以钨、铜或铝为主要成分的导电材料。此外,导电层260b可以具有叠层结构,例如可以具有钛、氮化钛与上述导电材料的叠层结构。

[0463]

如图29a和图29c所示,在金属氧化物230b的不与导电层242重叠的区域,即金属氧化物230的沟道形成区域中,金属氧化物230的侧面被导电层260覆盖。由此,可以容易将被用作第一栅电极的导电层260的电场影响到金属氧化物230的侧面。由此,可以提高晶体管200a的通态电流及频率特性。

[0464]

绝缘层254与绝缘层214等同样地优选被用作抑制水或氢等杂质从绝缘层280一侧混入晶体管200a的阻挡绝缘膜。例如,绝缘层254的氢透过性优选比绝缘层224低。再者,如图29b及图29c所示,绝缘层254优选与金属氧化物230c的侧面、导电层242a的顶面及侧面、导电层242b的顶面及侧面、金属氧化物230a及金属氧化物230b的侧面以及绝缘层224的顶面接触。通过采用这种结构,可以抑制绝缘层280所包含的氢从导电层242a、导电层242b、金属氧化物230a、金属氧化物230b及绝缘层224的顶面或侧面侵入金属氧化物230。

[0465]

再者,绝缘层254还具有抑制氧(例如,氧原子、氧分子等)中的至少一个的扩散的功能(不容易使上述氧透过)。例如,绝缘层254的氧透过性优选比绝缘层280或绝缘层224低。

[0466]

绝缘层254优选通过溅射法形成。通过在包含氧的气氛下使用溅射法形成绝缘层254,可以对绝缘层224与绝缘层254接触的区域附近添加氧。由此,可以将氧从该区域通过绝缘层224供应到金属氧化物230中。在此,通过使绝缘层254具有抑制扩散到上方的氧的功能,可以防止氧从金属氧化物230扩散到绝缘层280。此外,通过使绝缘层222具有抑制扩散到下方的氧的功能,可以防止氧从金属氧化物230扩散到衬底一侧。如此,对金属氧化物230中的沟道形成区域供应氧。由此,可以减少金属氧化物230的氧缺陷并抑制晶层管的常开启化。

[0467]

作为绝缘层254,例如可以形成包含铝及铪中的一个或多个的氧化物的绝缘层。注意,作为包含铝和铪中的一方或双方的氧化物的绝缘层,优选使用氧化铝、氧化铪、包含铝及铪的氧化物(铝酸铪)等。

[0468]

通过由对氢具有阻挡性的绝缘层254覆盖绝缘层224、绝缘层250以及金属氧化物230,绝缘层280由绝缘层254与绝缘层224、金属氧化物230以及绝缘层250分开。由此,可以抑制从晶体管200a的外部侵入氢等杂质,从而可以对晶体管200a赋予良好的电特性及可靠性。

[0469]

优选将绝缘层280隔着绝缘层254设置在绝缘层224、金属氧化物230及导电层242上。例如,作为绝缘层280,优选具有氧化硅、氧氮化硅、氮氧化硅、添加有氟的氧化硅、添加有碳的氧化硅、添加有碳及氮的氧化硅或具有空孔的氧化硅等。尤其是,氧化硅及氧氮化硅具有热稳定性,所以是优选的。特别是,因为氧化硅、氧氮化硅、具有空孔的氧化硅等的材料

容易形成包含通过加热脱离的氧的区域,所以是优选的。

[0470]

此外,优选绝缘层280中的水或氢等杂质的浓度得到降低。此外,绝缘层280的顶面也可以被平坦化。

[0471]

绝缘层274优选与绝缘层214等同样地被用作抑制水或氢等杂质从上方混入到绝缘层280的阻挡绝缘膜。作为绝缘层274,例如可以使用能够用于绝缘层214、绝缘层254等的绝缘层。

[0472]

优选在绝缘层274上设置被用作层间膜的绝缘层281。与绝缘层224等同样,优选绝缘层281中的水或氢等杂质的浓度得到降低。

[0473]

在形成于绝缘层281、绝缘层274、绝缘层280及绝缘层254中的开口中配置导电层240a及导电层240b。导电层240a及导电层240b以中间夹着导电层260的方式设置。此外,导电层240a及导电层240b的顶面的高度与绝缘层281的顶面可以位于同一平面上。

[0474]

此外,以与绝缘层281、绝缘层274、绝缘层280以及绝缘层254的开口的内壁接触的方式设置有绝缘层241a,以与其侧面接触的方式形成有导电层240a的第一导电层。导电层242a位于该开口的底部的至少一部分,导电层240a与导电层242a接触。同样,以与绝缘层281、绝缘层274、绝缘层280以及绝缘层254的开口的内壁接触的方式设置有绝缘层241b,以与其侧面接触的方式形成有导电层240b的第一导电层。导电层242b位于该开口的底部的至少一部分,导电层240b与导电层242b接触。

[0475]

导电层240a及导电层240b优选使用以钨、铜或铝为主要成分的导电材料。此外,导电层240a及导电层240b也可以具有叠层结构。

[0476]

当作为导电层240采用叠层结构时,作为与金属氧化物230a、金属氧化物230b、导电层242、绝缘层254、绝缘层280、绝缘层274及绝缘层281接触的导电层优选使用上述具有抑制水或氢等杂质的扩散的功能的材料。例如,优选使用钽、氮化钽、钛、氮化钛、钌或氧化钌等。可以以单层或叠层使用具有抑制水或氢等杂质的扩散的功能的导电材料。通过使用该导电材料,可以抑制添加到绝缘层280的氧被导电层240a及导电层240b吸收。此外,可以抑制水或氢等杂质从绝缘层281的上方的层通过导电层240a及导电层240b进入金属氧化物230。

[0477]

作为绝缘层241a及绝缘层241b,例如使用能够用于绝缘层254等的绝缘层,即可。因为绝缘层241a及绝缘层241b与绝缘层254及接触地设置,所以可以抑制从绝缘层280等水或氢等杂质经过导电层240a及导电层240b混入金属氧化物230。此外,可以抑制绝缘层280所包含的氧被导电层240a及导电层240b吸收。

[0478]

虽然未图示,但是可以以与导电层240a的顶面及导电层240b的顶面接触的方式配置被用作布线的导电层。被用作布线的导电层优选使用以钨、铜或铝为主要成分的导电材料。此外,该导电层可以具有叠层结构,例如,可以具有钛、氮化钛与上述导电材料的叠层结构。此外,该导电层也可以以嵌入绝缘层的开口中的方式形成。

[0479]

《晶体管的结构例子_2》

[0480]

图30a、图30b及图30c是可以用于本发明的一个方式的显示装置的晶体管200b及晶体管200b周边的俯视图及截面图。晶体管200b是晶体管200a的变形例子。

[0481]

图30a是晶体管200b的俯视图。此外,图30b及图30c是晶体管200b的截面图。在此,图30b是沿着图30a中的点划线a1-a2的截面图,该截面图相当于晶体管200b的沟道长度方

向上的截面图。图30c是沿着图30a中的点划线a3-a4的截面图,该截面图相当于晶体管200a的沟道宽度方向上的截面图。注意,为了容易理解,在图30a的俯视图中省略部分构成要素。

[0482]

晶体管200b与晶体管200a不同之处在于:包括绝缘层212及绝缘层283。

[0483]

在晶体管200b的衬底(未图示)上设置有绝缘层212。此外,在绝缘层212上及绝缘层271上设置有绝缘层283。

[0484]

晶体管200b具有绝缘层283覆盖绝缘层214、绝缘层216、绝缘层222、绝缘层224、绝缘层280及绝缘层274上的结构。绝缘层283接触于绝缘层274的顶面、绝缘层274的侧面、绝缘层280的侧面、绝缘层224的侧面、绝缘层222的侧面、绝缘层216的侧面、绝缘层214的侧面及绝缘层212的顶面。由此,金属氧化物230等被绝缘层283及绝缘层212与外部隔开。

[0485]

绝缘层283及绝缘层212的抑制氢(例如,氢原子、氢分子等中的至少一个)或水分子的扩散的功能优选高。例如,作为绝缘层281及绝缘层212优选使用氢阻挡性较高的材料的氮化硅或氮氧化硅。由此,由于可以抑制氢等扩散到金属氧化物230中,所以可以抑制晶体管200b的特性下降。因此,可以提高本发明的一个方式的半导体装置的可靠性。

[0486]

作为绝缘层283,例如,可以使用氮化硅。作为绝缘层283使用氮化硅的情况下,通过利用溅射法成膜,可以形成密度高且不容易形成空洞等的氮化硅膜。此外,也可以在通过溅射法作为绝缘层283形成的氮化硅上层叠利用ald法形成的氮化硅。通过采用上述结构,即使通过溅射法形成的氮化硅中产生缺陷例如空洞,也可以通过覆盖性良好的利用ald法形成的氮化硅填埋该空洞而提高密封性能。作为绝缘层212可以使用可以用于绝缘层214的材料。例如,作为绝缘层212可以使用氮化硅,作为绝缘层214可以使用氧化铝。

[0487]

《晶体管的结构例子_3》

[0488]

图31a、图31b及图31c是可以用于本发明的一个方式的显示装置的晶体管200c及晶体管200c周边的俯视图及截面图。晶体管200c是晶体管200a的变形例子。

[0489]

图31a是晶体管200c的俯视图。此外,图31b及图31c是晶体管200c的截面图。在此,图31b是沿着图31a中的点划线b1-b2的截面图,该截面图相当于晶体管200c的沟道长度方向上的截面图。图31c是沿着图31a中的点划线b3-b4的截面图,该截面图相当于晶体管200c的沟道宽度方向上的截面图。注意,为了容易理解,在图31a的俯视图中省略部分构成要素。

[0490]

在晶体管200c中,导电层242a及导电层242b具有与金属氧化物230c、绝缘层250及导电层260重叠的区域。由此,晶体管200c可以为通态电流高的晶体管。此外,晶体管200c可以为易于被控制的晶体管。

[0491]

用作栅电极的导电层260包括导电层260a及导电层260a上的导电层260b。导电层260a优选使用具有抑制氢原子、氢分子、水分子、铜原子等杂质扩散的功能的导电材料。此外,优选使用具有抑制氧(例如,氧原子、氧分子等中的至少一个)扩散的功能的导电材料。

[0492]

通过使导电层260a具有抑制氧扩散的功能,可以提高导电层260b的材料选择性。也就是说,通过包括导电层260a,可以抑制导电层260b的氧化,由此可以抑制导电率下降。

[0493]

优选以覆盖导电层260的顶面及侧面、绝缘层250的侧面及金属氧化物230c的侧面的方式设置绝缘层254。作为绝缘层254优选使用具有抑制水或氢等杂质及氧的扩散的功能的绝缘材料。

[0494]

通过设置绝缘层254,可以抑制导电层260的氧化。此外,通过包括绝缘层254,可以抑制绝缘层280所包含的水、氢等杂质扩散到晶体管200c。

[0495]

《晶体管的结构例子_4》

[0496]

图32a、图32b及图32c是可以用于本发明的一个方式的显示装置的晶体管200d及晶体管200d周边的俯视图及截面图。晶体管200d是晶体管200a的变形例子。

[0497]

图32a是晶体管200d的俯视图。此外,图32b及图32c是晶体管200d的截面图。在此,图32b是沿着图32a中的点划线c1-c2的截面图,该截面图相当于晶体管200d的沟道长度方向上的截面图。图32c是沿着图32a中的点划线c3-c4的截面图,该截面图相当于晶体管200d的沟道宽度方向上的截面图。注意,为了容易理解,在图32a的俯视图中省略部分构成要素。

[0498]

在晶体管200d中,在金属氧化物230c上包括绝缘层250,在绝缘层250上包括金属氧化物252。此外,在金属氧化物252上包括导电层260,在导电层260上包括绝缘层270。此外,在绝缘层270上包括绝缘层271。

[0499]

金属氧化物252优选具有抑制氧扩散的功能。通过在绝缘层250与导电层260之间设置抑制氧扩散的金属氧化物252,向导电层260的氧扩散得到抑制。换言之,可以抑制供应到金属氧化物230的氧量的减少。此外,可以抑制导电层260的氧化。

[0500]

此外,金属氧化物252可以被用作栅电极的一部分。例如,可以将可用作金属氧化物230的氧化物半导体用作金属氧化物252。在此情况下,通过利用溅射法形成导电层260,可以降低金属氧化物252的电阻值使其变为导电层。可以将其称为oc(oxide conductor)电极。

[0501]

金属氧化物252有时被用作栅极绝缘层的一部分。因此,在将氧化硅或氧氮化硅等用于绝缘层250的情况下,作为金属氧化物252优选使用作为相对介电常数高的high-k材料的金属氧化物。通过采用该叠层结构,可以形成具有热稳定性且相对介电常数高的叠层结构。因此,可以在保持物理厚度的同时降低在晶体管工作时施加的栅极电位。此外,可以减少被用作栅极绝缘层的绝缘层的等效氧化物厚度(eot)。

[0502]

虽然示出晶体管200d中的金属氧化物252是单层的结构,但是也可以采用两层以上的叠层结构。例如,可以将被用作栅电极的一部分的金属氧化物与被用作栅极绝缘层的一部分的金属氧化物层叠。

[0503]

当晶体管200d具有金属氧化物252,并将金属氧化物252用作栅电极时,可以在不减弱来自导电层260的电场的影响的情况下提高晶体管200d的通态电流。此外,当将金属氧化物252用作栅极绝缘层时,通过利用绝缘层250及金属氧化物252的物理厚度,可以保持导电层260与金属氧化物230之间的距离。由此,可以抑制导电层260与金属氧化物230之间的泄漏电流。由此,通过使晶体管200d具有绝缘层250及金属氧化物252的叠层结构,可以容易调节导电层260与金属氧化物230之间的物理距离及从导电层260施加到金属氧化物230的电场强度。

[0504]

具体而言,可以通过使可用于金属氧化物230的氧化物半导体低电阻化来将其用作金属氧化物252。或者,可以使用包含选自铪、铝、镓、钇、锆、钨、钛、钽、镍、锗和镁等中的一种或两种以上的金属氧化物。

[0505]

尤其是,优选使用作为包含铝和铪中的一方或双方的氧化物的绝缘层的氧化铝、氧化铪、包含铝及铪的氧化物(铝酸铪)等。尤其是,铝酸铪的耐热性比氧化铪高。因此,在后面的工序的热处理中不容易晶化,所以是优选的。注意,金属氧化物252不是必需的构成要素,可以根据所需的晶体管特性适当地设计。

[0506]

作为绝缘层270优选使用具有抑制水或氢等杂质及氧的透过的功能的绝缘材料。例如优选使用氧化铝或氧化铪等。由此,可以抑制导电层260因来自绝缘层270的上方的氧而氧化。此外,可以抑制来自绝缘层270的上方的水或氢等杂质通过导电层260及绝缘层250进入金属氧化物230中。

[0507]

绝缘层271被用作硬掩模。通过设置绝缘层271,可以以使导电层260的侧面与衬底表面大致垂直的方式对导电层260进行加工,具体而言,可以使导电层260的侧面与衬底表面所形成的角度为75度以上且100度以下,优选为80度以上且95度以下。

[0508]

此外,也可以通过作为绝缘层271使用抑制水或氢等杂质及氧的透过的功能的绝缘材料,来将绝缘层271兼用作阻挡层。在此情况下,也可以不设置绝缘层270。

[0509]

通过将绝缘层271用作硬掩模,选择性地去除绝缘层270、导电层260、金属氧化物252、绝缘层250及金属氧化物230c的一部分,可以使它们的侧面大致一致,且使金属氧化物230b的表面的一部分露出。

[0510]

晶体管200d在露出的金属氧化物230b的表面的一部分具有区域243a及区域243b。区域243a和区域243b中的一个被用作源区,另一个被用作漏区。

[0511]

例如通过利用离子注入法、离子掺杂法、等离子体浸没离子注入法或等离子体处理等,对露出的金属氧化物230b的表面引入磷或硼等杂质元素,来可以形成区域243a及区域243b。注意,在本实施方式等中,“杂质元素”是指主要成分元素之外的元素。

[0512]

也可以在使金属氧化物230b的表面的一部分露出之后形成金属膜,然后进行加热处理,来将包含在该金属膜中的元素扩散到金属氧化物230b中,由此形成区域243a及区域243b。

[0513]

被引入杂质元素的金属氧化物230b的一部分区域的电阻率下降。由此,有时将区域243a及区域243b称为“杂质区域”或“低电阻区域”。

[0514]

通过将绝缘层271和/或导电层260用作掩模,可以自对准地形成区域243a及区域243b。因此,区域243a和/或区域243b不与导电层260重叠,可以减小寄生电容。此外,偏置区域不形成在沟道形成区域与源漏区域(区域243a或区域243b)之间。通过自对准地形成区域243a及区域243b,可以实现通态电流的增加、阈值电压的降低、工作频率的提高等。

[0515]

晶体管200d在绝缘层271、绝缘层270、导电层260、金属氧化物252、绝缘层250及金属氧化物230c的侧面包括绝缘层272。绝缘层272优选为相对介电常数低的绝缘层。例如,优选使用氧化硅、氧氮化硅、氮氧化硅、氮化硅、添加有氟的氧化硅、添加有碳的氧化硅、添加有碳及氮的氧化硅、具有空孔的氧化硅或树脂等。尤其是,当将氧化硅、氧氮化硅、氮氧化硅或具有空孔的氧化硅用于绝缘层272时,在后面的工序中可在绝缘层272中容易形成过剩氧区域,所以是优选的。此外,氧化硅及氧氮化硅具有热稳定性,所以是优选的。此外,绝缘层272优选具有扩散氧的功能。

[0516]

此外,为了进一步降低关态电流,也可以在沟道形成区域与源漏区域之间设置偏置区域。偏置区域是电阻率高的区域,且是不被进行上述杂质元素的引入的区域。通过在形成绝缘层272后进行上述杂质元素的引入,可以形成偏置区域。在此情况下,与绝缘层271等同样,绝缘层272也被用作掩模。因此,金属氧化物230b的与绝缘层272重叠的区域不被引入杂质元素,由此可以将该区域的电阻率保持为高。

[0517]

晶体管200d在绝缘层272、金属氧化物230上包括绝缘层254。绝缘层254优选利用

溅射法形成。通过利用溅射法,可以形成水或氢等杂质少的绝缘层。

[0518]

有时利用溅射法形成的氧化膜从被形成的结构体抽出氢。因此,绝缘层254从金属氧化物230及绝缘层272吸收氢及水。由此,可以降低金属氧化物230及绝缘层272的氢浓度。

[0519]

《晶体管的构成材料》

[0520]

说明可用于晶体管的构成材料。

[0521]

[衬底]

[0522]

作为形成晶体管200a至晶体管200d的衬底例如可以使用绝缘体衬底、半导体衬底或导电体衬底。作为绝缘体衬底,例如可以举出玻璃衬底、石英衬底、蓝宝石衬底、稳定氧化锆衬底(氧化钇稳定氧化锆衬底等)、树脂衬底等。此外,作为半导体衬底,例如可以举出由硅或锗等构成的半导体衬底、或者由碳化硅、硅锗、砷化镓、磷化铟、氧化锌或氧化镓等构成的化合物半导体衬底等。再者,还可以举出在上述半导体衬底内部具有绝缘体区域的半导体衬底,例如有soi(silicon on insulator:绝缘体上硅)衬底等。作为导电体衬底,可以举出石墨衬底、金属衬底、合金衬底、导电树脂衬底等。或者,可以举出包含金属氮化物的衬底、包含金属氧化物的衬底等。再者,还可以举出设置有导电层或半导体层的绝缘体衬底、设置有导电层或绝缘层的半导体衬底、设置有半导体层或绝缘层的导电体衬底等。或者,也可以使用在这些衬底上设置有元件的衬底。作为设置在衬底上的元件,可以举出电容器、电阻器、开关元件、发光元件、存储元件等。

[0523]

[绝缘层]

[0524]

作为绝缘层,有具有绝缘性的氧化物、氮化物、氧氮化物、氮氧化物、金属氧化物、金属氧氮化物以及金属氮氧化物等。

[0525]

例如,当进行晶体管的微型化及高集成化时,由于栅极绝缘层的薄膜化,有时发生泄漏电流等的问题。通过作为被用作栅极绝缘层的绝缘层使用high-k材料,可以在保持物理厚度的同时实现晶体管工作时的低电压化。另一方面,通过将相对介电常数较低的材料用于被用作层间膜的绝缘层,可以减少产生在布线之间的寄生电容。因此,优选根据绝缘层的功能选择材料。

[0526]

作为相对介电常数较高的绝缘层,可以举出氧化镓、氧化铪、氧化锆、含有铝及铪的氧化物、含有铝及铪的氧氮化物、含有硅及铪的氧化物、含有硅及铪的氧氮化物或者含有硅及铪的氮化物等。

[0527]

作为相对介电常数较低的绝缘层,可以举出氧化硅、氧氮化硅、氮氧化硅、氮化硅、添加有氟的氧化硅、添加有碳的氧化硅、添加有碳及氮的氧化硅、具有空孔的氧化硅或树脂等。

[0528]

通过由具有抑制氢等杂质及氧的透过的功能的绝缘层(绝缘层214、绝缘层222、绝缘层254、及绝缘层274等)围绕使用氧化物半导体的晶体管,可以使晶体管的电特性稳定。作为具有抑制氢等杂质及氧的透过的功能的绝缘层,例如可以以单层或叠层使用包含硼、碳、氮、氧、氟、镁、铝、硅、磷、氯、氩、镓、锗、钇、锆、镧、钕、铪或钽的绝缘层。具体而言,作为具有抑制氢等杂质及氧的透过的功能的绝缘层,可以使用氧化铝、氧化镁、氧化镓、氧化锗、氧化钇、氧化锆、氧化镧、氧化钕、氧化铪或氧化钽等金属氧化物、氮化铝、氮化铝钛、氮化钛、氮氧化硅或氮化硅等金属氮化物。

[0529]

被用作栅极绝缘层的绝缘层优选为具有包含通过加热脱离的氧的区域的绝缘层。

例如,通过采用具有包含通过加热脱离的氧的区域的氧化硅或者氧氮化硅接触于金属氧化物230的结构,可以填补金属氧化物230所包含的氧缺陷。

[0530]

[导电层]

[0531]

作为导电层,优选使用选自铝、铬、铜、银、金、铂、钽、镍、钛、钼、钨、铪、钒、铌、锰、镁、锆、铍、铟、钌、铱、锶和镧等中的金属元素、以上述金属元素为成分的合金或者组合上述金属元素的合金等。例如,优选使用氮化钽、氮化钛、钨、包含钛和铝的氮化物、包含钽和铝的氮化物、氧化钌、氮化钌、包含锶和钌的氧化物、包含镧和镍的氧化物等。此外,氮化钽、氮化钛、包含钛和铝的氮化物、包含钽和铝的氮化物、氧化钌、氮化钌、包含锶和钌的氧化物、包含镧和镍的氧化物是不容易氧化的导电材料或者吸收氧也维持导电性的材料,所以是优选的。此外,也可以使用以包含磷等杂质元素的多晶硅为代表的导电率高的半导体以及镍硅化物等硅化物。

[0532]

也可以层叠多个由上述材料形成的导电层。例如,也可以采用组合包含上述金属元素的材料和包含氧的导电材料的叠层结构。此外,也可以采用组合包含上述金属元素的材料和包含氮的导电材料的叠层结构。此外,也可以采用组合包含上述金属元素的材料、包含氧的导电材料和包含氮的导电材料的叠层结构。

[0533]

此外,在将氧化物用于晶体管的沟道形成区域的情况下,作为被用作栅电极的导电层优选采用组合包含上述金属元素的材料和包含氧的导电材料的叠层结构。在此情况下,优选将包含氧的导电材料设置在沟道形成区域一侧。通过将包含氧的导电材料设置在沟道形成区域一侧,从该导电材料脱离的氧容易被供应到沟道形成区域。

[0534]

尤其是,作为被用作栅电极的导电层,优选使用含有包含在形成沟道的金属氧化物中的金属元素及氧的导电材料。此外,也可以使用含有上述金属元素及氮的导电材料。例如,也可以使用氮化钛、氮化钽等包含氮的导电材料。此外,可以使用铟锡氧化物、包含氧化钨的铟氧化物、包含氧化钨的铟锌氧化物、包含氧化钛的铟氧化物、包含氧化钛的铟锡氧化物、铟锌氧化物、添加有硅的铟锡氧化物。此外,也可以使用包含氮的铟镓锌氧化物。通过使用上述材料,有时可以俘获形成沟道的金属氧化物所包含的氢。或者,有时可以俘获从外方的绝缘层等进入的氢。

[0535]

本实施方式的至少一部分可以与本说明书所记载的其他实施方式适当地组合而实施。

[0536]

(实施方式4)

[0537]

在本实施方式中,说明可用于上述实施方式中说明的os晶体管的金属氧化物(以下称为氧化物半导体)。

[0538]

《结晶结构的分类》

[0539]

首先,对氧化物半导体中的结晶结构的分类参照图33a进行说明。图33a是说明氧化物半导体,典型为igzo(包含in、ga及zn的金属氧化物)的结晶结构的分类的图。

[0540]

如图33a所示那样,氧化物半导体大致分为“amorphous(无定形)”、“crystalline(结晶性)”、“crystal(结晶)”。此外,在“amorphous”中包含completely amorphous。此外,在“crystalline”中包含caac(c-axis-aligned crystalline)、nc(nanocrystalline)及cac(cloud-aligned composite)(excluding single crystal and poly crystal)。此外,在“crystalline”的分类中不包含single crystal(单晶)、poly crystal(多晶)及

completely amorphous。此外,“crystal”的分类中包含single crystal及poly crystal。

[0541]

此外,图33a所示的外框线被加粗的部分中的结构是介于“amorphous(无定形)”与“crystal(结晶)”之间的中间状态,是属于新的边界区域(new crystalline phase)的结构。就是说,该结构与“crystal(结晶)”或在能量性上不稳定的“amorphous(无定形)”可以说是完全不同的结构。

[0542]

此外,可以使用x射线衍射(xrd:x-ray diffraction)光谱对膜或衬底的结晶结构进行评价。在此,图33b示出被分类为“crystalline”的caac-igzo膜的通过gixd(grazing-incidence xrd)测量而得到的xrd谱。此外,将gixd法也称为薄膜法或seemann-bohlin法。下面,将图33b所示的通过gixd测量而得到的xrd谱简单地记为xrd谱。此外,图33b所示的caac-igzo膜的组成是in:ga:zn=4:2:3[原子个数比]附近。此外,图33b所示的caac-igzo膜的厚度为500nm。

[0543]

如图33b所示,在caac-igzo膜的xrd谱中检测出表示明确的结晶性的峰。具体而言,在caac-igzo膜的xrd谱中,2θ=31

°

附近检测出表示c轴取向的峰。此外,如图33b所示那样,2θ=31

°

附近的峰在以检测出峰强度(intensity)的角度为轴时左右非对称。

[0544]

此外,可以使用纳米束电子衍射法(nbed:nano beam electron diffraction)观察的衍射图案(也称为纳米束电子衍射图案)对膜或衬底的结晶结构进行评价。图33c示出caac-igzo膜的衍射图案。图33c是将电子束向平行于衬底的方向入射的nbed观察的衍射图案。此外,图33c所示的caac-igzo膜的组成是in:ga:zn=4:2:3[原子个数比]附近。此外,在纳米束电子衍射法中,进行束径为1nm的电子衍射法。

[0545]

如图33c所示那样,在caac-igzo膜的衍射图案中观察到表示c轴取向的多个斑点。

[0546]

[氧化物半导体的结构]

[0547]

此外,在注目于氧化物半导体的结晶结构的情况下,有时氧化物半导体的分类与图33a不同。例如,氧化物半导体可以分类为单晶氧化物半导体和除此之外的非单晶氧化物半导体。作为非单晶氧化物半导体,例如可以举出上述caac-os及nc-os。此外,在非单晶氧化物半导体中包含多晶氧化物半导体、a-like os(amorphous-like oxide semiconductor)及非晶氧化物半导体等。

[0548]

在此,对上述caac-os、nc-os及a-like os的详细内容进行说明。