脉冲边沿检测电路

1.相关申请的相互参照

2.本技术基于2020年3月31日申请的日本技术2020-063186号,本文引用其记载内容。

技术领域

3.本技术涉及检测根据电压信号的变化而生成的脉冲信号的边沿的电路。

背景技术:

4.例如在专利文献1、非专利文献1中公开有如下技术:测量伴随构成驱动负载的桥式电路的开关元件的开关动作而产生的负载信号,基于其测量结果,调整向开关元件输入的栅极信号的定时。

5.现有技术文献

6.专利文献

7.专利文献1:日本特开2019-057757号公报

8.非专利文献

9.非专利文献1:isscc 2019/session 15/power for 5g,wireless p ower,and gan c onverters/15.8,a 4.5v/ns active slew-rate-controlling gate driver with robust discrete-time feedback technique for 600v superjunction mosfets,shunsuke kawai,takeshi u e n o,k o h e i o n i z u k a,t o s h i b a,k a w a s a k i,j a p a n

技术实现要素:

10.然而,例如在逆变器等桥式电路以电机为驱动对象时,伴随开关元件的开关而产生的浪涌电压高速地变化。此外,对电机进行驱动控制的环境通常产生较多噪声,因此也无法避免受到噪声的影响。

11.在这种环境下中,例如若为了测量浪涌电压超过一定的基准电压的期间,设想检测通过比较电压信号与基准电压而生成的脉冲信号的两边沿,则由于其边沿间隔为ns级,因此边沿间隔的检测变得困难。而且,若通过模拟电路进行边沿的检测,则存在电路面积变大的隐患,若通过数字电路来进行,则使用高耐压工序形成时难以安装高速的时钟信号,仍旧难以检测各边沿。

12.本技术鉴于上述情况而完成,其目的在于提供能够不使用高速的时钟信号地、通过相对简单的构成捕捉伴随电压信号的变化而生成的高速的脉冲信号的边沿的脉冲边沿检测电路。

13.根据技术方案1记载的脉冲边沿检测电路,将比较器对电压信号与阈值电压进行比较并输出的脉冲信号的上升沿、下降沿的一方设为第一边沿,将另一方设为第二边沿时,第一、第二边沿检测部分别在第一、第二边沿产生的定时,输出第一、第二边沿检测信号。此

时,第二边沿检测部能够检测第二边沿的定时被第一边沿检测信号控制。

14.在脉冲信号中,继一方的边沿的产生,产生另一方的边沿。因此,通过第一边沿检测部在第一边沿的产生定时输出的第一边沿检测信号,来控制能够通过第二边沿检测部检测第二边沿的定时。由此,即使由于脉冲信号高速而两个边沿的产生间隔短,也能够不使用高速的时钟信号地,由第二边沿检测部检测第二边沿。

15.根据技术方案2记载的脉冲边沿检测电路,具备分别使第一、第二边沿检测信号与时钟信号同步地输出的第一、第二时钟同步电路。如上述这样构成,能够将同步用时钟信号的周期作为最小单位来表示由第一、第二边沿检测部检测出的第一、第二边沿的产生定时。

附图说明

16.本技术的上述目的以及其他目的、特征、优点通过参照附图以及下述的详细的记述而更加明确。其附图如下。

17.图1是表示第一实施方式中的脉冲边沿检测电路的图。

18.图2是表示脉冲边沿检测电路的动作的时序图。

19.图3是说明通过延迟电路赋予的延迟时间的作用的图。

20.图4是表示脉冲边沿检测电路的一应用例的图。

21.图5是表示电压vds的波形与脉冲信号vin的波形的图。

22.图6是表示第二实施方式中的脉冲边沿检测电路的图。

23.图7是表示脉冲边沿检测电路的动作的时序图。

24.图8是表示第三实施方式中的脉冲边沿检测电路的图。

25.图9是表示脉冲边沿检测电路的动作的时序图。

26.图10是表示第四实施方式中的脉冲边沿检测电路的图。

27.图11是表示电压vds的波形与脉冲信号vin的波形的图。

28.图12是表示脉冲边沿检测电路的动作的时序图。

29.图13是表示第五实施方式中的脉冲边沿检测电路的图。

30.图14是表示rsff 33(2)的延迟时间变得过长的情况下的动作的时序图。

31.图15是表示脉冲边沿检测电路的动作的时序图。

32.图16是表示第六实施方式中的脉冲边沿检测电路的图。

33.图17是表示第七实施方式中的脉冲边沿检测电路的图。

34.图18是说明在第八实施方式中,使用第四实施方式的脉冲边沿检测电路时,在被输入输出信号out1~out4的栅极驱动控制电路中,辨别由噪声引起的脉冲的边沿与测定对象的方法的图。

35.图19是说明在第九实施方式中,使用第四实施方式的脉冲边沿检测电路时,在被输入输出信号out1~out4的栅极驱动控制电路中,辨别由噪声引起的脉冲的边沿与测定对象的方法的图。

36.图20是说明在第十实施方式中,在栅极驱动控制电路中预先消除噪声的影响的方法的图。

37.图21是表示第十一实施方式中的脉冲边沿检测电路的图。

38.图22是表示脉冲边沿检测电路的动作的时序图。

39.图23是表示在第十二实施方式中,测量电路所使用的迟滞比较器的图。

40.图24是表示通过比较器去除噪声的例子的图(其1)。

41.图25是表示通过比较器去除噪声的例子的图(其2)。

42.图26是表示在第十三实施方式中,测量电路所使用的上侧、下侧迟滞比较器的图。

43.图27是表示通过比较器去除噪声的例子的图(其1)。

44.图28是表示通过比较器去除噪声放例子的图(其2)。

45.图29是表示在第十四实施方式中,测量电路所使用的施密特触发缓冲器的图。

46.图30是表示通过施密特触发缓冲器去除噪声的例子的图。

47.图31是表示第十五实施方式中的延迟电路的构成例的图。

具体实施方式

48.(第一实施方式)

49.以下,参照图1至图5对第一实施方式进行说明。如图4所示,n沟道mosfet 1p以及1n的串联电路构成三相的逆变器电路2的一相,并连接于直流电源3。逆变器电路2例如以未图示的三相电机为驱动对象。在fet1n的漏极、源极之间连接有由比较器构成的测量电路4。测量电路4将fet1n的漏极、源极之间电压vds与作为阈值电压的基准电压进行比较,并输出脉冲信号vin。

50.如图5所示,例如在直流电源3的电压为12v左右、fet1n被关断时,在漏极、源极之间例如产生超过18v的浪涌电压。通过将该浪涌电压vds与12v左右的基准电压进行比较,来生成脉冲信号vin。本实施方式的检测电路5检测与浪涌电压vds最初超过基准电压的定时对应的脉冲信号vin的上升沿、以及之后与浪涌电压vds最初低于基准电压的定时对应的脉冲信号vin的下降沿。在本实施方式中,上升沿相当于第一边沿,下降沿相当于第二边沿。

51.将检测电路5输出的上升沿检测信号设为out1、下降沿检测信号设为out2,这些检测信号经由数字控制电路8被输入到向fet1p以及1n的栅极输出驱动信号的栅极驱动控制电路6。栅极驱动控制电路6基于检测信号out1、out2,例如进行调整驱动信号的输出定时等控制。此外,数字控制电路8对检测电路5输出复位信号reset。测量电路4以及检测电路5构成了脉冲边沿检测电路7。

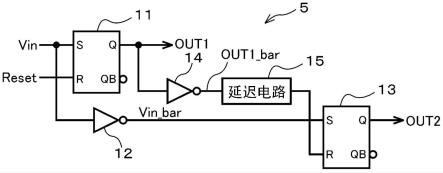

52.如图1所示,脉冲信号vin被输入到rs触发器11的置位(set)端子s、以及非门12的输入端子。对rs触发器11的复位端子r输入复位信号reset。非门12的输出端子连接于rs触发器13的置位端子s。以下,将“触发器”记载为“ff”。

53.rsff 11的输出端子q连接于非门14的输入端子。非门14的输出端子经由延迟电路15连接于rsff13的复位端子r。rsff 11、13的输出端子q分别输出信号out1、out2。rsff 11、13分别相当于第一、第二边沿检测部,并且分别相当于第一、第二锁存电路。

54.接下来,对本实施方式的作用进行说明。如图2所示,在初始状态下rsff 11被复位,若脉冲信号vin为低电平,则rsff 13为置位、复位同时有效。由此,虽然信号out2为“不定”,但在信号out1成为高电平有效(high active)之前则没有问题。数字控制电路8在使fet1n关断之前将信号reset设为高电平,从而将rsff 11重新复位。

55.之后,若由于fet1n关断从而电压vds超过基准电压,脉冲信号vin成为高电平,则rsff 11被置位从而信号out1成为高电平。于是,信号out1的反转信号out1_bar经由延迟电

路15被赋予复位端子r,从而rsff 13的复位被解除。

56.接下来,若电压vds降低并低于基准电压,则脉冲信号vin的反转信号vin_bar成为高电平,rsff 13被置位从而out2成为高电平。即,信号out1、2的上升沿间隔相当于脉冲信号vin的脉冲宽度,例如10ns。之后,即使电压vds由于振铃而再次超过基准电压,脉冲信号vin成为高电平,被rsff 11、13锁存的信号out1、2也不发生变化。

57.这里,对通过延迟电路15对信号out1_bar赋予的延迟时间进行说明。如图3所示,若在电压vds最初超过基准电压之前的阶段中,在信号vin_bar表现为高电平的期间rsff 13的复位被解除,则信号out2在早的定时变化为高电平。另一方面,若在电压vds最初超过基准电压之后立即rsff 13的复位被解除,则信号out2在迟的定时变化为高电平。因此,在脉冲信号vin的脉冲宽度例如设想为10ns左右时,延迟电路15中的延迟时间优选设定为小于10ns。

58.如以上那样根据本实施方式,在脉冲边沿检测电路7中,在测量电路4中,比较器将电压vds与基准电压进行比较并输出脉冲信号vin。rsff 11在由于脉冲信号vin变化为高电平从而检测出了上升沿的定时将信号out1设为高电平。由此,在rsff 13中,置位信号成为无效(inactive),并且复位信号成为有效(active),能够检测出脉冲信号vin的下降沿。而且,若脉冲信号vin从高电平变化为低电平而产生下降沿,则rsff 13的置位信号成为有效、信号out2成为高电平。

59.在高电平脉冲信号中,继上升沿的产生而产生下降沿。因此,根据rsff 11在上升沿的产生定时输出的信号out1来控制在rsff 13中能够检测出下降沿的定时。具体而言,通过信号out1的反转电平,解除rsff 13的复位。由此,即使由于脉冲信号vin高速从而两个边沿的产生间隔短,rsff 13也能够不使用高速的时钟信号地检测下降沿。

60.此外,由于具备使通过信号out1的反转电平来解除rsff 13的复位的定时延迟的延迟电路15,因此rsff 13的复位被解除后,rsff 13检测出之后产生的下降沿时,能够充分地确保建立时间(setup time)以及保持时间(hold time)。而且,由于将延迟电路15的延迟时间设定为小于对脉冲信号vin设想的脉冲宽度时间,因此rsff 13能够可靠地检测出下降沿。

61.(第二实施方式)

62.以下,对与第一实施方式相同的部分标注相同的附图标记并省略说明来对不同的部分进行说明。如图6所示,第二实施方式的脉冲边沿检测电路16将rsff 13替换为负逻辑输入的rsff 17,伴随于此删除了非门12以及14。此外,延迟电路15的输出端子连接于rsff 17的置位端子s,脉冲信号vin连接于其复位端子r。

63.如图7所示,在信号vin以及信号out1均表现为低电平的期间,rsff 17与第一实施方式同样成为不定。然后,若信号vin成为高电平且信号out1也成为高电平,则rsff 17的置位、复位均被解除。之后,若信号vin成为低电平,则rsff 17被复位,信号out2成为低电平。在该情况下,信号ou1的上升沿与信号ou2的下降沿的间隔表示信号vin的高电平脉冲宽度。根据以上那样构成的脉冲边沿检测电路16,与第一实施方式的脉冲边沿检测电路7相比,电路面积变小。

64.(第三实施方式)

65.图8所示的第三实施方式的脉冲边沿检测电路21例如在第一实施方式的检测电路

5的输出级配置dff 22(1)、22(2),并使信号out1、2与时钟信号clk同步地输出。dff 22(1)、22(2)分别相当于第一、第二时钟同步电路。时钟信号clk的频率例如为100mhz。

66.在图9中,为了进行比较,还示出了代替脉冲边沿检测电路21而仅通过一个dff以时钟同步地输出脉冲信号vin的情况下的信号out_ideal。在该情况下,由于脉冲信号vin的第二个脉冲也被时钟信号clk触发,因此信号out_ideal的脉冲宽度为20ns。

67.与此相对,在脉冲边沿检测电路21中,由于分别通过时钟同步输出单独检测出上升沿、下降沿的信号out1、out2,因此同步后的信号ffout1、ffout2的边沿间隔成为与脉冲信号vin的脉冲宽度相等的10ns。

68.如以上那样根据第三实施方式,脉冲边沿检测电路21具备使信号out1、out2与时钟信号clk同步地输出的dff 22(1)、22(2)。由此,能够将同步用时钟信号clk的周期作为最小单位来表示由rsff 11、13检测出的上升沿、下降沿的产生定时。

69.(第四实施方式)

70.图10所示的第四实施方式的脉冲边沿检测电路31具备相当于第一实施方式的检测电路5的构成,对它们的附图标记附加(1)来示出。而且,在脉冲边沿检测电路31中,对rsff 13(1)的输出端子q追加两组包括非门14、延迟电路15以及rsff 13的组,并将它们级联连接。对追加的两组分别附加符号(2)、(3)。

71.对rsff 13(2)的置位端子s赋予脉冲信号vin,对rsff 13(3)的置位端子s赋予经由非门12(2)后的脉冲信号vin。rsff 13(2)的输出端子q输出信号out3,rsff 13(3)的输出端子q输出信号out4。

72.接下来,对第四实施方式的作用进行说明。如图11所示,脉冲边沿检测电路31是如下的构成:设想成为测定对象的电压信号伴随fet1n的关断而开始上升,在超过测量电路4的基准电压之前噪声重叠,对该噪声采取对策。若噪声重叠,则如图12所示,在脉冲信号vin中的原本的测定对象脉冲之前,产出由噪声引起的脉冲。由此,信号out1、out2在由噪声引起的脉冲的上升沿、下降沿的产生定时变化为高电平。

73.而且,在rsff 13(2)中,若信号out2成为高电平,则复位被解除,因此在之后产生的测定对象脉冲的上升沿的产生定时,使信号out3变化为高电平。伴随于此,由于rsff 13(3)的复位被解除,因此rsff 13(3)在之后产生的测定对象脉冲的下降沿的产生定时使信号out4变化为高电平。

74.因此,根据第四实施方式的脉冲边沿检测电路31,即使在脉冲信号vin中的测定对象脉冲之前,产生了由噪声引起的脉冲的情况下,也能够通过信号out3、out4检测测定对象脉冲的上升沿、下降沿的产生定时。

75.(第五实施方式)

76.图13所示的第五实施方式的脉冲边沿检测电路32是对脉冲边沿检测电路31增加了延迟电路33(1)以及33(2)的构成。延迟电路33(1)使信号vin延迟并赋予到rsff 13(2)的置位端子s。延迟电路33(2)被插入非门12(2)与rsff 13(3)的置位端子s之间。

77.接下来,对第五实施方式的作用进行说明。对rsff 13(2)的复位端子r经由延迟电路15(1)以及15(2)赋予复位信号。因此,若延迟时间变得过长,则如图14所示,rsff 13(2)的复位解除变迟,存在在脉冲信号vin的上升沿产生之后复位被解除的隐患。另外,在图14中,作为一例,设想了没有第四实施方式那样的噪声的重叠的情况,因此通过信号out1、

out2检测测定对象脉冲的上升沿、下降沿。

78.因此,由于通过延迟电路33(1)生成延迟了信号vin的信号vin’,从而如图15所示,使信号vin’的上升沿、这里为由于振铃而产生的脉冲的上升沿延迟到rsff 13(2)的复位被解除之后,并反映于信号out3。由此,即使由于经由延迟电路15(1)以及15(2),复位信号延迟,rsff 13(2)也能够检测脉冲的对应的上升沿。

79.(第六实施方式)

80.图16所示的第六实施方式的脉冲边沿检测电路34具备将脉冲边沿检测电路31的输出信号数扩展至n的扩展检测电路31n。其中,n为“6”以上的偶数。而且,对扩展检测电路31n的各输出端子out1~out(n),与第三实施方式同样地配置有dff 22(1)~22(n)。由此,能够与第三实施方式同样地输出与时钟信号clk同步的信号ffout1~ffout(n)。

81.(第七实施方式)

82.图17所示的第七实施方式的脉冲边沿检测电路35为对脉冲边沿检测电路34追加了非门36a以及36b的串联电路的构成。该串联电路被插入dff 22(2)的时钟端子与dff 22(n-1)的时钟端子之间。对于脉冲边沿检测电路34,如第五实施方式所述那样,在延迟时间的累积成为问题时,通过非门36a以及36b使时钟信号clk延迟来调整定时即可。

83.(第八实施方式)

84.第八实施方式示出了例如在使用脉冲边沿检测电路31时,在被输入其输出信号out1~out4的数字控制电路8中,辨别由噪声引起的脉冲的边沿和测定对象脉冲的边沿的方法。控制电路8控制关断fet1n的定时,并且还控制对脉冲边沿检测电路31输出复位信号的定时。

85.因此,控制电路8还能够预先预测设想在解除脉冲边沿检测电路31的复位后产生测定对象脉冲的上升沿的时间。即,在图18中,使复位信号从高电平变化为低电平的时刻起至信号out3变化为高电平的时刻为止的时间相当于“设想的时间”。若无噪声重叠,则在“设想的时间”信号out1应当变化为高电平。

86.因此,在使复位信号变化为低电平的时刻起至信号out1变化为高电平的时刻为止的时间明显比“设想的时间”短的情况下,忽略信号out1、out2,将信号out3、out4设为测定对象脉冲的上升沿、下降沿的检测信号即可,

87.(第九实施方式)

88.第九实施方式也与第八实施方式同样,示出了在数字控制电路8中,辨别由噪声引起的脉冲的边沿和测定对象脉冲的边沿的方法。控制电路8应当能够预先预测测定对象脉冲的脉冲宽度为多长时间。因此,如图19所示,始终测量信号out1、out2的产生间隔t(1-2)、以及信号out3、out4的产生间隔t(3-4)。对于预测的脉冲宽度例如为10ns左右,设为t(1-2)=3ns

89.t(3-4)=10ns。

90.在该情况下,如下述那样构成逻辑即可:

91.t(1-2)判定为是由噪声产生的脉冲,

92.将t(3-4)判定为测定对象脉冲的脉冲宽度。

93.(第十实施方式)

94.第十实施方式示出了在数字控制电路8中,预先消除噪声的影响的方法。如图20所

示,控制电路8通过将解除复位信号的定时延长至测定对象脉冲的上升沿产生的定时的附近,从而能够消除由噪声的影响产生的脉冲的影响。如上述这样控制,即使在使用脉冲边沿电路5时,也能够消除噪声的影响。

95.(第十一实施方式)

96.图21是构成第五实施方式的脉冲边沿检测电路32的延迟电路15、33分别由非门15a及15b的串联电路、非门33a及33b的串联电路构成的图。而且,如图22所示,脉冲边沿检测电路32还能够用作根据测定对象脉冲、以及之后由于振铃而产生的脉冲的各边沿的产生来输出信号out1~out4的构成,而非用作噪声对策用的构成。

97.(第十二实施方式)

98.图23所示的第十二实施方式在代替测量电路4的测量电路41中使用迟滞比较器。由此,如图24所示,在电压vds将要超过基准电压时由于噪声重叠而产生基于噪声的脉冲时,通过在以所述基准电压为中心的上下两侧具备迟滞特性,如图25所示,能够阻止基于噪声的脉冲的产生。

99.(第十三实施方式)

100.在图26所示的第十三实施方式中,作为测量电路42仍然使用迟滞比较器,但通过比较器4、下侧迟滞缓冲器43l以及上侧迟滞缓冲器43h来构成测量电路42。如图27所示,若如测量电路41那样在以基准电压为中心的两侧具备迟滞特性,则由于高电平侧、低电平侧的阈值电压不同,因此在上升沿、下降沿的检测定时产生偏差。

101.而在测量电路42中,如图28所示,通过使缓冲器43l、43h的基准电压相同并分别使其具有下侧迟滞特性、上侧迟滞特性,从而使上升沿、下降沿的检测定时一致,能够高精度地测定脉冲宽度。

102.(第十四实施方式)

103.图29所示的第十四实施方式通过比较器4与施密特触发缓冲器45的串联电路来构成测量电路44。由此,如图30所示,即使在比较器4的输出信号上重叠了噪声,也能够通过施密特触发缓冲器45的迟滞特性抑制噪声。

104.(第十五实施方式)

105.第十五实施方式示出了延迟电路的其他构成例。在图31中,示出了延迟电路51~53,延迟电路51在非门15a的输入端子与接地之间连接有电容器c。在延迟电路52中,在非门14的输出端子与非门15a的输入端子之间插入有电阻元件r,在延迟电路53中,在非门15a的输入级,通过电阻元件r与电容器c的组合构成了cr滤波器。此外,也可以仅通过cr滤波器来构成延迟电路。

106.(其他实施方式)

107.第一、第二边沿与上升沿、下降沿的关系也可以相反。

108.也可以使用在置位信号与复位信号同时有效时,例如使复位侧优先的rs触发器。

109.延迟电路根据需要设置即可。

110.作为检测对象的电压不限于fet的漏极-源极间电压。

111.本技术基于实施例进行了记述,但应理解为本技术不限于该实施例、构造。本技术也包含各种变形例、等同范围内的变形。除此之外,各种组合、方式,进而包含仅其一要素、其以上、或者其以下的其他组合、方式也落入本技术的范畴、思想范围内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。