1.本实用新型属于电子控制技术领域,特别涉及一种纳秒脉宽信号简易发生电路。

背景技术:

2.随着光电子信息技术的迅速发展,纳秒级半导体脉冲激光器在光纤通讯、激光精密加工、激光测距,激光医疗等领域中拥有广泛应用。

3.为了获得高稳定性的短脉冲光信号,可以通过锁模技术获得, 利用cpa放大技术获得高能量脉冲, 但是涉及到振荡器、展宽器、放大器和压缩器等核心器件,最终的产品的不仅体积大而且成本高。

4.为了获得纳秒级脉宽的光信号,我们可以通过高性能的fpga芯片产生纳秒级高重频的信号来驱动开关管来得。但是高性能的fpga芯片价格也不便宜,而且fpga产生的信号幅值并不高,最高电压幅值约2.5v,部分可以达到 3.3v。fpga芯片驱动带载能力也比较弱,驱动电流最高十多毫安。

技术实现要素:

5.本实用新型的目的在于提供一种纳秒脉宽信号简易发生电路,以解决上述背景技术中提出的问题。

6.为实现上述目的,本实用新型提供如下技术方案:

7.一种纳秒脉宽信号简易发生电路,包括一级功率放大电路、信号延时电路、以及窄脉冲发生电路,其中,触发信号输入至一级功率放大电路的输入端,并由一级功率放大电路的输出端输出至信号延时电路的输入端,再由信号延时电路的输出端输出至窄脉冲发生电路的输入端,由窄脉冲发生电路的输出端输出纳秒脉宽信号。

8.与现有技术相比,本技术方案具有如下效果:

9.通过本技术的电路降低对外部输入trigger in 输入信号的上升沿,下降沿,幅值等性能要求,从而实现外部输入trigger in幅值可以在3~5v电压范围,上升沿和下降沿可以在纳秒范围。并且整个电路的制造成本比较低。

10.作为优选,所述一级功率放大电路包括芯片u70,所述芯片u70的第1引脚连接至电源2.5v,芯片u70的第3引脚与电容c95的第一端相连接且作为触发信号的输入端,电容c95的第二端连接至芯片u70的第2引脚且接地,芯片u70的第4引脚与电容c94的第一端相连且连接至电源5v,电容c9的第二端与芯片u70的第6引脚相连且接地。

11.作为优选,所述信号延时电路包括信号同相延时电路和信号反相延时电路,所述信号同相延时电路和信号反相延时电路彼此电连接。

12.作为优选,所述信号同相延时电路包括芯片u71,所述芯片u71的第4引脚连接至电源5v,芯片u71的第3引脚与电容c98的第一端、电阻r66的第二端相连接,电阻r66的第一端连接至芯片u70的第5引脚,电容c98的第二端。芯片u71的第2引脚、第6引脚均接地。

13.作为优选,所述信号反相延时电路包括芯片u72,所述芯片u72的第3引脚连接至芯

片u71的第1引脚,且芯片u72的第1引脚与电容c96的第一端、电阻r70的第二端相连,电容c96的第二段接地,且电阻r70的第一端连接至电阻r66的第一端,芯片u72的第4引脚连接至电源5v,且芯片u72的第2引脚、第6引脚均接地。

14.作为优选,所述窄脉冲发生电路包括芯片u76,芯片u76的第1引脚连接至芯片u71的第5引脚,芯片u76的第2引脚连接至芯片u72的第5引脚,且芯片u76的第6引脚与电容c106的第一端相连接且连接至电源5v,电容c106的第二端、芯片u76的第3引脚均接地,其中,所述芯片u76的第4引脚输出纳秒宽信号。

15.作为优选,所述芯片u70、芯片u71以及芯片u72均采用型号为lt1719cs6的比较器。

16.作为优选,所述芯片u76采用型号为nc7sz08l6x的芯片。

附图说明

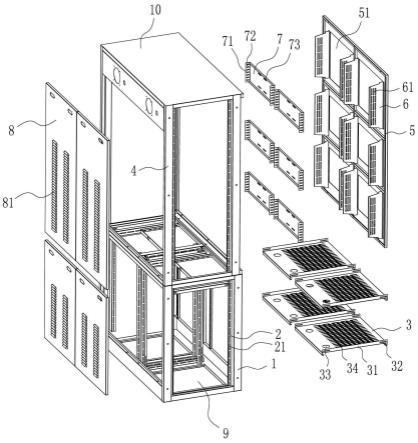

17.图1是本实用新型中整体架构示意图;

18.图2是本实用新型中一级功率放大电路原理示意图;

19.图3是本实用新型中信号同相延时电路原理示意图;

20.图4是本实用新型中信号反相延时电路原理示意图;

21.图5是本实用新型中窄脉冲发生电路原理示意图。

22.图中:10-一级功率放大电路;20-信号同相延时电路;30-信号反相延时电路;40-窄脉冲发生电路。

具体实施方式

23.下面将结合本实用新型实施例中的附图,对本实用新型实施例中的技术方案进行清楚,完整地描述,显然,所描述的实施例仅仅是本实用新型一部分实施例,而不是全部实施例。

24.实施例:

25.如图1所示的一种纳秒脉宽信号简易发生电路,包括一级功率放大电路10、信号延时电路、以及窄脉冲发生电路40;

26.在本实施例中,触发信号输入至一级功率放大电路10的输入端,并由一级功率放大电路10的输出端输出至信号延时电路的输入端,再由信号延时电路的输出端输出至窄脉冲发生电路40的输入端,由窄脉冲发生电路40的输出端输出纳秒脉宽信号;其中,所述信号延时电路包括信号同相延时电路20和信号反相延时电路30,所述信号同相延时电路20和信号反相延时电路30彼此电连接;其作用是,功率放大电路10输入到同相延时电路20的信号会先经过电阻给电容充电, 当电容电压超过比较器负极性电压的时候,比较器会输出 5v电压,否则输出电压0v。功率放大电路10输入到反相延时电路30的信号同样会先经过电阻给电容充电,当电容电压超过比较器正极性电压的时候, 比较器会输出0v电压, 否则输出电压 5v。经过信号延时电路输出的两个信号刚好反相,并且由于电阻值不同,会有一定的相位差。 最后窄脉冲发生电路40会在两个信号同为高电平的时候输出 5v电压,否则输出0v。

27.参考图2可知,所述一级功率放大电路10包括芯片u70,所述芯片u70的第1引脚连接至电源2.5v,芯片u70的第3引脚与电容c95的第一端相连接且作为触发信号的输入端,电

容c95的第二端连接至芯片u70的第2引脚且接地,芯片u70的第4引脚与电容c94的第一端相连且连接至电源5v,电容c9的第二端与芯片u70的第6引脚相连且接地;触发信号通过电容c95和电容c94进行整形滤波,其次,通过对芯片u70的第1引脚输入电压设置参考电压2.5v,若外部输入的触发信号输入幅值大于参考电压时,芯片u70的都5引脚输出5v高电平的脉冲信号。

28.在一实施例中,如图3所示,所述信号同相延时电路20包括芯片u71,所述芯片u71的第4引脚连接至电源5v,芯片u71的第3引脚与电容c98的第一端、电阻r66的第二端相连接,电阻r66的第一端连接至芯片u70的第5引脚,电容c98的第二端。芯片u71的第2引脚、第6引脚均接地;当输入u70第3引脚的电压大于u70第1引脚的电压2.5v的时候,u70第5引脚输出高电平,与输入信号同相。

29.另外,结合图4可知,所述信号反相延时电路30包括芯片u72,所述芯片u72的第3引脚连接至芯片u71的第1引脚,且芯片u72的第1引脚与电容c96的第一端、电阻r70的第二端相连,电容c96的第二段接地,且电阻r70的第一端连接至电阻r66的第一端,芯片u72的第4引脚连接至电源5v,且芯片u72的第2引脚、第6引脚均接地;当输入u71第3引脚的电压大于u70第1引脚的电压2.5v的时候,u70第5引脚输出低电平,与输入信号反相。

30.值得注意的是,所述芯片u70、芯片u71以及芯片u72均采用型号为lt1719cs6的比较器;三者型号一致,方便企业统一生产物料, 方便生产管控,三者可以选择性能相近的不同规格。

31.在一实施例中,所述窄脉冲发生电路40包括芯片u76,所述芯片u76采用型号为nc7sz08l6x的芯片,且该芯片u76的第1引脚连接至芯片u71的第5引脚,芯片u76的第2引脚连接至芯片u72的第5引脚,且芯片u76的第6引脚与电容c106的第一端相连接且连接至电源5v,电容c106的第二端、芯片u76的第3引脚均接地,其中,所述芯片u76的第4引脚输出纳秒宽信号;u71,u72采用高速、低寄生参数的比较器,实现电路高重频输出。 u76采用高速、大电流、高幅值逻辑与器件。

32.本实用的有益效果,通过采用上述的电路设置,可以将其集合封装,相对于传统的分立器件而言,有效降低了占地面积;通过少量元器件实现高重频、高幅值、稳定可靠的纳秒级脉宽信号,整个电路的制造成本比较低,可以采用国产芯片替代。

33.本实用新型的描述中,需要理解的是,术语“中心”、“横向”、“上”、“下”、“左”、“右”、“竖直”、“水平”、“顶”、“底”、“内”、“外”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本实用新型和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本实用新型的限制。此外,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者更多个该特征。在本实用新型的描述中,除非另有说明,“若干个”的含义是两个或两个以上。另外,术语“包括”及其任何变形,意图在于覆盖不排他的包含。

34.本实用新型按照实施例进行了说明,在不脱离本原理的前提下,本装置还可以作出若干变形和改进。应当指出,凡采用等同替换或等效变换等方式所获得的技术方案,均落在本实用新型的保护范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。