一种基于ddr3的读写控制动态调度方法及其存储介质

技术领域

1.本发明涉及雷达信号处理技术领域,具体涉及一种基于ddr3的读写控制动态调度方法。

背景技术:

2.随着雷达干扰模拟技术的不断发展,对数字储频板上存储信号的芯片要求也越来越高。现有数字储频板主要用qdr和ddr3这两种存储芯片来存储,相比较qdr而言,ddr3的成本低到可以忽略,且存储深度大,读写速度快,但是对数字信号的读写时序控制要求远比qdr复杂,原因在于ddr3不能同时进行读写操作,所以很难一边从接收天线采样脉冲信号,一边调制后经发送天线转发。

3.现有技术而言,为了解决这种收发同时遇到的情况,通常主要使用乒乓方式控制ddr读写,即一块ddr3读,另一块ddr3写,然后交替往复,或者用成本高昂的qdr来代替。前者会导致ddr3利用率减少,因为实际上两块ddr3存储的是一个采样期间的信号内容,而ddr3存储深度很大,其实一块ddr3完全满足采样需求,没必要使用第二块ddr3;后者则会造成使用成本上升,因为qdr相对ddr3成本会高不少。

技术实现要素:

4.发明目的:本发明目的在于针对现有技术的不足,提供一种基于ddr3的读写控制动态调度方法,实现在一片ddr3内控制读写实现收发天线同时工作的效果。

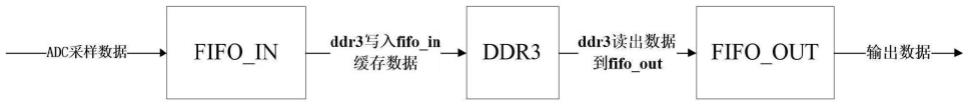

5.技术方案:本发明所述一种基于ddr3的读写控制动态调度方法,包括向ddr3存储模块写入数据步骤和由ddr3存储模块读出数据步骤,在向ddr3存储模块写入数据步骤中,adc采样数据通过先入先出的方式缓存到fifo存储器的fifo_in中,ddr3从所述fifo存储器的fifo_in中读入数据;由ddr3存储模块读出数据步骤中,将ddr3读出数据缓存到fifo存储器的fifo_out中,再从所述fifo存储器的fifo_out中读出数据。

6.本发明技术方案的进一步限定为,所述ddr3存储模块的写入数据和读出数据的切换控制方法为:s1、初始状态:当fifo_in为空的指示信号in_empty为低,写优先级置为1,读优先级置0,进入wr_start状态;s2、ddr3写入数据状态:当fifo_in内存储的数据量大于预设数据量in_prog_empty时,或者adc采样结束时,向ddr3存储模块写入数据,进入wr_start状态;s3、写切换状态wr_switch:当wr_startt状态结束时,开始读写选择wr_rd_switch,s3.1如果fifo存储器的fifo_out的可编程满标志为低,则写优先级置为0,读优先级置1,进入读状态rd_start;否则s3.2如果fifo_in为空的指示信号in_empty为低,则写优先级置为1,读优先级置

0,进入写状态wr_start;否则保持读写选择wr_rd_switch状态轮询判断s3.1和s3.2;s4、读切换状态rd_switch:当读状态rd_start结束时,开始读写选择wr_rd_switch,s4.1如果fifo_in为空的指示信号in_empty为低,则写优先级置为1,读优先级置0,进入写状态wr_start;否则s4.2如果fifo存储器的fifo_out的可编程满标志为高或者读完成状态为高,则写优先级置为0,读优先级置1,进入读状态rd_start;否则s4.3如果读完成状态为高,进入空状态,写优先级置为0,读优先级置0,完成读写;否则保持读写选择wr_rd_switch状态轮询判断s4.1、s4.2和s4.3。

7.进一步地,步骤s3中,判断wr_start状态结束的方法为:进入wr_start状态时,计数器开始计数,当计数器到达预先设定值wr_rd_count或者fifo_in为空的指示信号为高时,结束写状态wr_start。

8.进一步地,步骤s4中,判断rd_start状态结束的方法为:进入rd_start状态时,计数器开始计数,(1)当ddr3读的地址rd_addr等于写结束地址wr_addr时,不再给ddr3有效地址,记录此时的rd_addr_count,当rd_data_count等于rd_addr_count时,rd_start状态结束;否则(2)rd_addr_count等于设定值wr_rd_count时,不再给ddr3有效地址;数据计数rd_data_count等于预先设定值wr_rd_count时,rd_start状态结束。

9.进一步地,还包括读中断控制方法:当接收到读中断指令时,发送开始预读命令pre_rd,如果ddr3处于写入数据状态,结束写状态wr_start,ddr3读出数据至fifo存储器的fifo_out中,延时time_ddr3后,再发送开始读命令rd,进入读状态rd_start。

10.进一步地,读中断指令的触发方法为:设定计时器和预设时段,到达预设时段后,发送读中断指令,计时器归零。

11.本发明提供的另一技术方案为:一种计算机可读存储介质,所述计算机可读存储介质存储有计算机可执行指令,所述计算机可执行指令用于使计算机执行如权利要求1~6中任意一项所述的基于ddr3的读写控制动态调度方法。

12.有益效果:与现有技术相比,本发明的优点在于:(1)采用单ddr3实现类似乒乓读写操作,相比双ddr3乒乓和qdr方式节省成本。

13.(2)采用了读中断、预读和读方式准确控制数据的延时,使信号处理更加准确,出来信号质量更好。

14.(3)开发难度相对于双ddr3乒乓降低,节省开发成本。

[0015] (4) 充分利用ddr3的高时钟速率,快速切换读写操作,使ddr3控制类似双口ram,使得外部读写指令更加容易控制ddr3进行存取数据,减少时序控制难度。

附图说明

[0016]

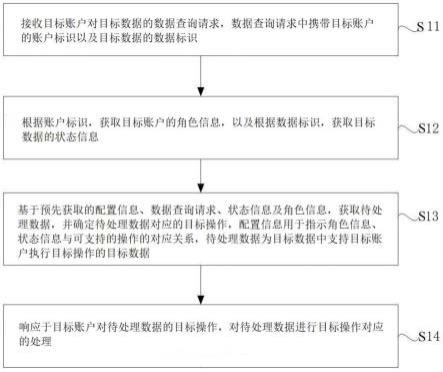

图1是本发明总方案流程图。

[0017]

图2实施例1ddr3的读写控制动态调度方法的状态切换流程图。

[0018]

图3是实施例1中ddr3的读状态时序图。

具体实施方式

[0019]

下面通过附图对本发明技术方案进行详细说明,但是本发明的保护范围不局限于所述实施例。

[0020]

实施例1 典型应用场景对于典型应用场景,adc通过模数转换采样一定时长信号数据,ddr3存储转发,需要将adc数据通过fifo_in不断送入ddr3,再从ddr3把数据通过fifo_out一直读出送给后续模块处理,这个过程中fifo_in保持不满,fifo_out保持不满,就可以保证数据正确传输,而合理的ddr3读写控制动态调度方法可满足需求。

[0021]

adc作用:模数转化,将外部的信号采样,生成数字量,供数字板上相关芯片处理;fifo_in:时钟域转化及数据缓冲,将adc采样数据用的adc时钟变化到ddr3存储数据所用的ddr3时钟,并通过先入先出缓冲一段数据;ddr3:存储数据,读取已存储数据,但不能同时进行存储和读取操作;fifo_out:时钟域转化及数据缓冲,将ddr3读出数据所用的ddr3时钟变回到ddr3时钟,并通过先入先出缓冲一段数据。

[0022]

应用于如上所述典型应用场景的一种基于ddr3的读写控制动态调度方法,总流程图如图1所示,包括向ddr3存储模块写入数据步骤和由ddr3存储模块读出数据步骤,在向ddr3存储模块写入数据步骤中,adc采样数据通过先入先出的方式缓存到fifo存储器的fifo_in中,ddr3从所述fifo存储器的fifo_in中读入数据;由ddr3存储模块读出数据步骤中,将ddr3读出数据缓存到fifo存储器的fifo_out中,再从所述fifo存储器的fifo_out中读出数据。

[0023]

本技术方案基于ddr3的读写控制动态调度方法的核心在于:利用ddr3的高读写速率和fifo的缓存特性,快速切换读写,因为读写操作是交替性进行,则需要确定读写操作的优先级,根据优先级实现当前ddr3的读写切换控制,可设优先级列表{0,1},读优先级为rd_pri,写优先级为wr_pri,当优先级为1时,指示当前操作优先级高,反之优先级低。

[0024]

根据以下情况考虑,来确定优先级的变化:(1)考虑到fifo_in保持不满,因为ddr3读写速率很快,不会满,只会空;(2)考虑到adc把数据写入fifo_in速度相较于ddr3从fifo_in里把数据读出速率慢上许多,所以如果每次等fifo_in有数据ddr3就从fifo_in读出数据,然后转发到fifo_out,会使ddr3读写切换频繁,而每次切换都会损耗几个时钟周期,累积下来损耗较大,所以设置ddr3每次读写一定数量wr_rd_count再进行切换;(3)考虑到adc数据停止采样需要判断fifo_in的空指示信号是否拉高,设fifo_in对应的此标志为in_empty,则ddr3每次将数据从fifo_in读出需要在非空的状态,另可利用fifo通用ip核设置的prog_empty(可编程空标志)设置fifo_in剩多少个数据,ddr3就不从fifo_in读数据,设fifo_in对应的此标志为in_prog_empty;(4)考虑到fifo_out保持不满,因为ddr3将已存储数据读出并送入fifo_out时,ddr3送数据给fifo_out速度比之fifo_out向外输出数据速度快上许多,所以需要fifo_out用可编程满标志指示什么时候不送数据,设fifo_out 的可编程满标志out_prog_full;

(5)考虑到初始状态ddr3没数据,所以初始状态默认写优先级高;(6)考虑到ddr3将fifo_in数据全部读入后,写操作无意义,因此此时写优先级低;(7)考虑到fifo_out 数据全部读出,设对应空指示标志out_empty,此时读写都无意义,因此都无优先级。

[0025]

设每次读开始地址计数信号为rd_addr_count,数据计数信号为rd_data_count,写开始地址和数据计数信号均为wr_count,adc采样结束标志为adcdata_finish,拉高代表采样结束,不往fifo_in里送数据,则基于上文本方法,ddr3存储模块的写入数据和读出数据的切换控制方法流程图如图2所示,具体步骤如下:s1、初始状态(idle):当fifo_in为空的指示信号in_empty为低,写优先级置为1,读优先级置0,进入wr_start状态。

[0026]

、ddr3写入数据状态(wr_start):当fifo_in内存储的数据量大于预设数据量in_prog_empty时,或者adc采样结束时,向ddr3存储模块写入数据,进入wr_start状态。即in_prog_empty拉低,ddr3开始从fifo_in中读入数据;若数据量太少,不够设置的in_prog_empty个数,则当采样结束标志adcdata_finish拉高时,ddr3也开始从fifo_in中读入数据。

[0027]

、写切换状态(wr_switch):当wr_startt状态结束时,开始读写选择wr_rd_switch。

[0028]

首先判断wr_start状态结束的方法为:进入wr_start状态时,计数器开始计数,当计数器到达预先设定值wr_rd_count或者fifo_in为空的指示信号为高时,结束写状态wr_start。即当ddr3从fifo_in中读入一个数,wr_count计数值加一;当wr_count计数到设定值wr_rd_count时或者in_empty拉高时,写状态结束,wr_complete拉高来记录,此时清零计数值wr_count;当in_empty拉高时,记录最终的写地址信息wr_addr;进入wr_rd_switch状态。

[0029]

然后,当wr_complete拉高,即写结束时,进入读写选择,s3.1如果fifo存储器的fifo_out的可编程满标志为低,则写优先级置为0,读优先级置1,进入读状态rd_start;否则s3.2如果fifo_in为空的指示信号in_empty为低,则写优先级置为1,读优先级置0,进入写状态wr_start;否则保持读写选择wr_rd_switch状态轮询判断s3.1和s3.2。

[0030]

具体执行时:

①

判断是否out_prog_full拉高:如果未拉高,则将读优先级置1,写优先级置0,wr_complete置0,进入rd_start状态;否则继续判断

②

;

②

判断是否in_empty拉低:如果拉低,则将读优先级置0,写优先级置1,wr_complete置0,进入wr_start状态;否则保持wr_rd_switch状态继续轮询判断

①

、

②

。

[0031]

、读切换状态(rd_switch) :当读状态rd_start结束时,开始读写选择wr_rd_switch。

[0032]

首先判断rd_start状态结束的方法为:进入rd_start状态时,计数器开始计数,当ddr3读的地址rd_addr等于写结束地址wr_addr时,不再给ddr3有效地址,记录此时的rd_addr_count,当rd_data_count等于rd_addr_count时,rd_start状态结束;否则rd_addr_count等于设定值wr_rd_count时,不再给ddr3有效地址;数据计数rd_data_count等于预先设定值wr_rd_count时,rd_start状态结束。

[0033]

然后,当rd_complete拉高,即读结束时,开始读写选择,s4.1如果fifo_in为空的指示信号in_empty为低,则写优先级置为1,读优先级置0,进入写状态wr_start;否则s4.2如果fifo存储器的fifo_out的可编程满标志为高或者读完成状态为高,则写优先级置为0,读优先级置1,进入读状态rd_start;否则s4.3如果读完成状态为高,进入空状态,写优先级置为0,读优先级置0,完成读写;否则保持读写选择wr_rd_switch状态轮询判断s4.1、s4.2和s4.3。

[0034]

具体执行时:

①

判断是否in_empty拉低:如果拉低,则将读优先级置0,写优先级置1,rd_complete置0,进入wr_start状态;否则继续判断

②

;

②ꢀ

判断是否out_prog_full拉高和是否rd_finish_all拉高:如果两个信号都未拉高,则将读优先级置1,写优先级置0,rd_complete置0,进入rd_start状态;如果rd_finish_all拉高,则进入idle状态,rd_complete置0,读优先级置0,写优先级置0;否则保持rd_switch状态继续轮询判断

①

、

②

。

[0035]

另外,为了配合上述的优先级确定步骤,ddr3写进行状态和ddr3读进行状态的设置如下:在ddr3写进行状态时,in_prog_empty拉低,ddr3开始从fifo_in中读入数据;若数据量太少,不够设置的in_prog_empty个数,则当采样结束标志adcdata_finish拉高时,ddr3也开始从fifo_in中读入数据;当ddr3从fifo_in中读入一个数,wr_count计数值加一;当wr_count计数到设定值wr_rd_count时或者in_empty拉高时,写状态结束,wr_complete拉高来记录,此时清零计数值wr_count;当in_empty拉高时,记录最终的写地址信息wr_addr;进入wr_rd_switch状态;ddr3读进行状态时,时序图如图3所示,每次给ddr3一个有效数据地址,地址计数信号rd_addr_count加一;ddr3根据所给地址读出一个数据进入fifo_out, 数据计数rd_data_count计数值加一;当ddr3读的地址rd_addr等于写结束地址wr_addr时,不再给ddr3有效地址,记录此时的rd_addr_count,当rd_data_count等于rd_addr_count时,整个读完成,rd_finish_all置高,rd_complete置高,计数rd_addr_count,rd_data_count置零;当ddr3读的地址rd_addr不等于写结束地址wr_addr时,rd_addr_count等于设定值wr_rd_count时,不再给ddr3有效地址;数据计数rd_data_count等于设定值wr_rd_count时,读结束,rd_complete置高,计数rd_addr_count,rd_data_count置零。

[0036]

对于典型场景,ddr3的实际作用是通过存储对数据进行延时处理控制,对于控制而言就是fifo_in进数据到fifo_out出数据时长要可控,所以延时的准确性必须得到保证,而根据ddr3官方手册的读时序图介绍可知,给其读数据命令后,其要等待app_rdy拉高时才有效,从而导致fifo_out出数据时间也存在波动。

[0037]

为了解决这个问题,本发明采用了开始读命令rd和开始预读命令pre_rd分别控制fifo_out的出数据使能和ddr3读出数据的使能,开始读命令rd拉高就出数据,所以在这之前必须通过开始预读命令pre_rd把ddr3中存储的数据读出到fifo_out里,考虑到ddr3每次需等待app_rdy拉高才可以开始送入地址,然后等数据被读出,设这段时间为time_ddr3,则可以每次在实际开始读命令time_ddr3之前开始给出预读命令pre_rd,这样来覆盖掉存在波动的时间,time_ddr3的设置可查找芯片手册或实际上电写测试程序测量。

[0038]

为了更好的控制延时,需要加入读中断控制,因为给出开始预读命令pre_rd时,ddr3需立即将当前状态结束,切换到读状态,对应实施例1的优先级就是,读优先级置高,写优先级置低。

[0039]

中断控制的具体方法为:当接收到读中断指令时,发送开始预读命令pre_rd,如果ddr3处于写入数据状态,结束写状态wr_start,ddr3读出数据至fifo存储器的fifo_out中,延时time_ddr3后,再发送开始读命令rd,进入读状态rd_start。读中断指令的触发方法为:设定计时器和预设时段,到达预设时段后,发送读中断指令,计时器归零。

[0040]

另外,本实施例还提供一种计算机可读存储介质,所述计算机可读存储介质存储有计算机可执行指令,所述计算机可执行指令用于使计算机执行如权利要求1~6中任意一项所述的基于ddr3的读写控制动态调度方法。

[0041]

如上所述,尽管参照特定的优选实施例已经表示和表述了本发明,但其不得解释为对本发明自身的限制。在不脱离所附权利要求定义的本发明的精神和范围前提下,可对其在形式上和细节上作出各种变化。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。