技术特征:

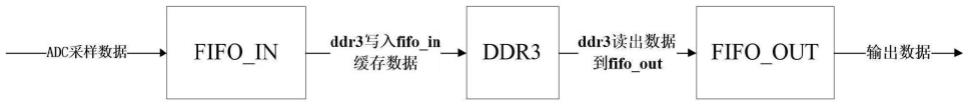

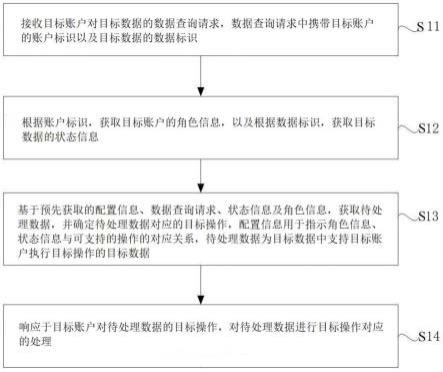

1.一种基于ddr3的读写控制动态调度方法,包括向ddr3存储模块写入数据步骤和由ddr3存储模块读出数据步骤,其特征在于:在向ddr3存储模块写入数据步骤中,adc采样数据通过先入先出的方式缓存到fifo存储器的fifo_in中,ddr3从所述fifo存储器的fifo_in中读入数据;由ddr3存储模块读出数据步骤中,将ddr3读出数据缓存到fifo存储器的fifo_out中,再从所述fifo存储器的fifo_out中读出数据。2.根据权利要求1所述的一种基于ddr3的读写控制动态调度方法,其特征在于,所述ddr3存储模块的写入数据和读出数据的切换控制方法为:s1、初始状态:当fifo_in为空的指示信号in_empty为低,写优先级置为1,读优先级置0,进入wr_start状态;s2、ddr3写入数据状态:当fifo_in内存储的数据量大于预设数据量in_prog_empty时,或者adc采样结束时,向ddr3存储模块写入数据,进入wr_start状态;s3、写切换状态wr_switch:当wr_startt状态结束时,开始读写选择wr_rd_switch,s3.1如果fifo存储器的fifo_out的可编程满标志为低,则写优先级置为0,读优先级置1,进入读状态rd_start;否则s3.2如果fifo_in为空的指示信号in_empty为低,则写优先级置为1,读优先级置0,进入写状态wr_start;否则保持读写选择wr_rd_switch状态轮询判断s3.1和s3.2;s4、读切换状态rd_switch:当读状态rd_start结束时,开始读写选择wr_rd_switch,s4.1如果fifo_in为空的指示信号in_empty为低,则写优先级置为1,读优先级置0,进入写状态wr_start;否则s4.2如果fifo存储器的fifo_out的可编程满标志为高或者读完成状态为高,则写优先级置为0,读优先级置1,进入读状态rd_start;否则s4.3如果读完成状态为高,进入空状态,写优先级置为0,读优先级置0,完成读写;否则保持读写选择wr_rd_switch状态轮询判断s4.1、s4.2和s4.3。3.根据权利要求2所述的一种基于ddr3的读写控制动态调度方法,其特征在于,步骤s3中,判断wr_start状态结束的方法为:进入wr_start状态时,计数器开始计数,当计数器到达预先设定值wr_rd_count或者fifo_in为空的指示信号为高时,结束写状态wr_start。4.根据权利要求2所述的一种基于ddr3的读写控制动态调度方法,其特征在于,步骤s4中,判断rd_start状态结束的方法为:进入rd_start状态时,计数器开始计数,(1)当ddr3读的地址rd_addr等于写结束地址wr_addr时,不再给ddr3有效地址,记录此时的rd_addr_count,当rd_data_count等于rd_addr_count时,rd_start状态结束;否则(2)rd_addr_count等于设定值wr_rd_count时,不再给ddr3有效地址;数据计数rd_data_count等于预先设定值wr_rd_count时,rd_start状态结束。5.根据权利要求2所述的一种基于ddr3的读写控制动态调度方法,其特征在于,还包括读中断控制方法:当接收到读中断指令时,发送开始预读命令pre_rd,如果ddr3处于写入数据状态,结束写状态wr_start,ddr3读出数据至fifo存储器的fifo_out中,延时time_ddr3后,再发送开始读命令rd,进入读状态rd_start。6.根据权利要求5所述的一种基于ddr3的读写控制动态调度方法,其特征在于,读中断

指令的触发方法为:设定计时器和预设时段,到达预设时段后,发送读中断指令,计时器归零。7.一种计算机可读存储介质,其特征在于,所述计算机可读存储介质存储有计算机可执行指令,所述计算机可执行指令用于使计算机执行如权利要求1~6中任意一项所述的基于ddr3的读写控制动态调度方法。

技术总结

本发明提供一种基于DDR3的读写控制动态调度方法,包括向DDR3存储模块写入数据步骤和由DDR3存储模块读出数据步骤,在向DDR3存储模块写入数据步骤中,ADC采样数据通过先入先出的方式缓存到FIFO存储器的FIFO_IN中,DDR3从所述FIFO存储器的FIFO_IN中读入数据;由DDR3存储模块读出数据步骤中,将DDR3读出数据缓存到FIFO存储器的FIFO_OUT中,再从所述FIFO存储器的FIFO_OUT中读出数据。本发明采用单ddr3实现类似乒乓读写操作,相比双DDR3乒乓和QDR方式节省成本,开发难度相对于双DDR3乒乓降低,节省开发成本。节省开发成本。节省开发成本。

技术研发人员:李继锋 李晃 朱文明 陈宏伟

受保护的技术使用者:扬州宇安电子科技有限公司

技术研发日:2022.08.19

技术公布日:2022/11/11

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。