具有工艺补偿的低压低功耗cmos基准电压源及调试方法

技术领域

1.本公开涉及电子及电路技术领域,尤其涉及一种具有工艺补偿的低压低功耗cmos基准电压源及调试方法。

背景技术:

2.随着智能家居、智能交通以及植入式医疗设备等应用的广泛使用,推动了低功耗物联网(internet of things,iot)技术的发展。另一方面,每年都在缩小的工艺尺寸导致电路的最小供电压也在减小。作为物联网应用中无处不在的基本模块,基准电压源为整个系统提供精确稳定的基准参考量,需要产生不受工艺、电源电压和温度(process,voltage,and temperature,pvt)变化影响的直流电压,以确保整个系统的稳健运行。

3.然而,目前的适用于低功耗设计的cmos基准电压源受工艺、电源电压和温度变化的影响较大,如何提供一种低供电压、低功耗,且几乎独立于pvt变化而稳定运行的基准电压源是一个亟待解决的技术课题。

技术实现要素:

4.基于上述问题,本公开提供了一种具有工艺补偿的低压低功耗cmos基准电压源及其调试方法,以缓解现有技术中的上述技术问题。

5.(一)技术方案

6.本公开提供一种具有工艺补偿的低压低功耗cmos基准电压源,包括等效nmos晶体管、以及以串联形式连接的第一等效晶体管、第二等效晶体管、第三等效晶体管,其中:所述等效nmos晶体管的漏极连接至电源,衬底接地;所述第一等效晶体管的源极连接至所述等效nmos晶体管的源极;所述第一等效晶体管的栅极、源极相连;所述第二等效晶体管和所述第三等效晶体管的栅极分别和自身的漏极相连;所述第一等效晶体管和所述第二等效晶体管产生具有第一偏斜的第一电压;所述第一等效晶体管和所述第三等效晶体管产生具有第二偏斜的第二电压,所述第二偏斜与所述第一偏斜能够互相补偿,从而使第一电压和第二电压求和后输出对pvt变化不敏感的基准电压。

7.根据本公开实施例,所述第一偏斜和所述第二偏斜分别包括工艺偏斜和温度偏斜。

8.根据本公开实施例,通过控制第一等效晶体管和第二等效晶体管的参数控制第一电压的工艺偏斜和温度偏斜。

9.根据本公开实施例,通过控制第一等效晶体管和第三等效晶体管的参数控制第二电压的工艺偏斜和温度偏斜。

10.根据本公开实施例,以上所述的参数包括单位沟道宽度、沟道长度、并联个数、阈值电压;工艺偏斜包括工艺偏斜量和工艺偏斜方向;温度偏斜包括温度偏斜量和温度偏斜方向。

11.根据本公开实施例,通过控制第一等效晶体管的单位沟道宽度和第二等效晶体管

的单位沟道宽度,以控制第一电压的工艺偏斜。

12.根据本公开实施例,通过控制第一等效晶体管的并联个数和第二等效晶体管的并联个数,以控制第一电压的温度偏斜。

13.根据本公开实施例,通过控制第一等效晶体管的单位沟道宽度和第三等效晶体管的单位沟道宽度,控制第二电压的工艺偏斜,以使第二电压的工艺偏斜和第一电压的工艺偏斜具有互补性,从而消除第一电压和第二电压的工艺偏斜。

14.根据本公开实施例,通过控制第一等效晶体管的并联个数和第三等效晶体管的并联个数,控制第二电压的温度偏斜,以使第二电压的温度偏斜和第一电压的温度偏斜具有互补性,从而消除第一电压和第二电压的温度偏斜。

15.本公开的另一方面,提供一种基准电压源的调试方法,用于调试以上任一项的基准电压源,调试方法包括:操作s1:确定第一等效晶体管的参数以设定偏置电流大小;操作s2:通过调整第二等效晶体管和第三等效晶体管的单位沟道宽度来控制第一电压和第二电压的工艺偏斜,以实现工艺补偿;操作s3:通过调整第二等效晶体管和第三等效晶体管的并联个数来控制第一电压和第二电压的温度偏斜,以实现温度补偿;以及操作s4:通过调整等效nmos晶体管的尺寸来提高基准电压源的电源抑制比和线性灵敏度。

16.(二)有益效果

17.从上述技术方案可以看出,本公开(具有工艺补偿的低压低功耗cmos基准电压源及其调试方法)至少具有以下有益效果其中之一或其中一部分:

18.(1)电路所需的最小供电压大幅度降低;

19.(2)功耗低;

20.(3)显著降低电路的工艺依赖性和温度依赖性,输出稳定性提高。

附图说明

21.图1为现有技术中混合型(bjt mosfet)基准电压源结构示意图;

22.图2为现有技术中混合型(bjt mosfet)基准电压源的原理示意图;

23.图3为现有技术中与电源无关的电压产生电路示意图;

24.图4为本公开实施例的基准电压源的原理示意图;

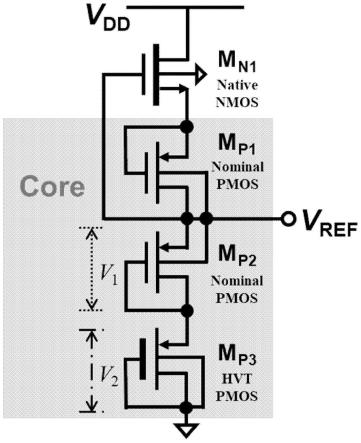

25.图5为本公开实施例的基准电压源的结构示意图;

26.图6为本公开实施例的基准电压源的调试方法流程图;

27.图7为本公开实施例的基准电压源在不同工艺角下随供电压的变化示意图;

28.图8为传统的无工艺补偿的cmos基准电压源示意图;

29.图9为本公开实施例的基准电压源在不同工艺角下有/无工艺补偿电路的温度特性对比示意图。

具体实施方式

30.本公开提供了一种具有工艺补偿的低压(供电压<1v)低功耗(皮瓦级)cmos基准电压源及其调试方法,采用尺寸诱导效应结合体偏置技术来实现工艺补偿和温度补偿。

31.目前应用广泛的基准电路可以根据其电路结构划分为两类:基于双极结型晶体管(bipolar junction transistor,bjt)的带隙基准源以及基于金属氧化物半导体场效应晶

体管(metal-oxide-semiconductor field-effect transistor,mosfet)的cmos基准源。其中,传统的带隙或混合结构基准电压源的输出基准电压通常基于bjt的基极-发射极电压(v

be

)产生,然而bjt的使用会限制基准电压源工作电压的降低(最小供电压通常大于1v)。传统的cmos基准电压源可以通过使用工作在亚阈值区域的mosfet实现超低功耗以及超低供电压,但由于其输出基准电压基于mosfet的阈值电压v

th

(threshold voltage)产生,而v

th

具有很高的工艺依赖性,导致传统的cmos基准电压源对工艺变化十分敏感。因此,对具有高工艺稳定性的低压低功耗基准电压源的技术课题研究具有十分重要的意义。

32.因此,为解决上述技术问题,本公开提供的技术方案如下:采用尺寸诱导效应结合体偏置技术来实现工艺补偿和温度补偿,通过工艺和温度偏斜控制技术来产生两个基于阈值电压v

th

的具有互补工艺和温度特性的电压,从而组合产生一个对pvt变化不敏感的基准电压。所提出的基准电压源核心电路仅由工作在亚阈值区域的mosfet组成,不仅实现了高工艺稳定性(与带隙基准源同等水平),因此还同时实现了超低功耗和超低供电压。

33.为使本公开的目的、技术方案和优点更加清楚明白,以下结合具体实施例,并参照附图,对本公开进一步详细说明。

34.如图1所示,现有技术提供了一种混合型(bjt mosfet)基准源[参考论文:y.ji et al.,“a 192pw hybrid bandgap-v

th

reference with process dependence compensated by a dimension-induced side-effect,”in proc.ieee int.solid-state circuitsconf.(isscc),san francisco,ca,usa,2019,pp.308-310.],其输出基准电压由带隙电压(v

bg

)和阈值电压(v

th

)组合而成。该结构分别基于bjt和mosfet生成两个具有互补工艺偏斜的电压,并根据mosfet尺寸变化与v

th

工艺偏斜量变化之间的函数关系,通过调节mosfet的尺寸来实现基准电压的工艺补偿。该结构输出基准电压的公式为:

[0035][0036]

其中,v

bg

为硅的带隙电压,m为亚阈值斜率因子,α为比例系数,v

th

为阈值电压,w为晶体管的单位沟道宽度,n为晶体管的并联个数,v

t

为热电压,t为温度。

[0037]

如图2所示,在该结构中,普通pmos晶体管m1和三极管q1组合产生一个与快速偏斜工艺成正比的电压v1,即具有ptfp偏斜特性;m1和普通pmos晶体管m2组合产生一个与快速偏斜工艺成反比的电压v2,即具有ctfp偏斜特性。当m1和m2的沟道长度为固定值时(l1=l2=常数),通过调整m1和m2的单位沟道宽度(w1和w2),可以使得ctfp电压v2的斜率与ptfp电压v1的斜率相等,从而实现电路的工艺补偿。ptfp电压v1和ctfp电压v2相加得到的电压为一个与工艺变化无关的基准电压(v

ref

)。此外,m1和q1组合产生的电压v1是一个与绝对温度成反比的电压,即具有ctat特性;m1和m2组合产生的电压v2是一个与绝对温度成正比的电压,即具有ptat特性。当m1和m2的单位沟道宽度为确定值时,通过调整m1和m2的并联个数(n1和n2),可以使得ptat电压v2的斜率与ctat电压v1的斜率相等,从而实现电路的温度补偿。通过将ptat电压v2和ctat电压v1相加得到一个与温度变化无关的基准电压(v

ref

)。本征nmos(native nmos)晶体管m

n1

层叠在核心电路的最上方,用于提高基准电压源的电源抑制比和线性灵敏度(line sensitivity,ls)。

[0038]

以上涉及术语解释:

[0039]

ptfp(proportional to faster-skewed process,与快速偏斜工艺成正比);

[0040]

ctfp(complementary to faster-skewed process,与快速偏斜工艺成反比);

[0041]

ptat(proportional to absolute temperature,与绝对温度成正比);

[0042]

ctat(complementary to absolute temperature,与绝对温度成反比);

[0043]

图1所示的混合型基准电压源通过使用bjt结合mosfet提供两个具有互补工艺偏斜的电压,相加得到输出基准电压,并通过调节mosfet的尺寸来补偿输出基准电压的工艺依赖性。但是,bjt的使用会限制基准电压源最小供电压的降低,难以满足低供电压系统的工作要求。

[0044]

图3为传统的与电源无关的电压产生电路的结构示意图,由两个工作在亚阈值区域的pmos晶体管串联而成,以实现超低功耗和超低供电压。电路的偏置电流由m1的零偏置漏电流提供,然后流经二极管形式连接的m2。当m1和m2的漏源电压(v

ds

)均高于100mv时,m1和m2的偏置电流可表示为:

[0045][0046][0047]

其中,v

t

代表热电压,v

t

=kt/q,k为玻尔兹曼常数(k=1.38

×

10-23

j/k),q为电子的电荷量(q=1.6

×

10-19

c),t是晶体管温度,m1、m2分别是晶体管m1和m2的亚阈值斜率因子,c

ox1

和c

ox2

分别是晶体管m1和m2的单位面积的栅氧化层电容,μ2、μ2分别代表晶体管m1和m2的载流子迁移率。w1、w2分别代表晶体管m1和m2的单位沟道宽度,n1、n2分别代表晶体管m1和m2的并联个数,l1、l2分别代表晶体管m1和m2的沟道长度,v

th1

、v

th2

分别代表晶体管m1和m2的阈值电压;依此类推,此结构下具有i个晶体管时,可以用wi、ni、li、v

thi

、mi、c

ox1

、μi分别表示晶体管mi的单位沟道宽度、并联个数、沟道长度、阈值电压、亚阈值斜率因子、单位面积的栅氧化层电容、载流子迁移率等参数。

[0048]

联立亚阈值电流方程,可得如图3所示的电压产生电路的输出电压v0的表达式为:

[0049][0050]

为了确定v0的工艺特性的决定性因素,本公开采用了蒙特卡洛仿真来量化这些晶体管参数的工艺依赖程度。v0的后一项(即的离散系数为σ/μ为1%,其中σ为标准差,μ为平均值,平均值为14mv。相比之下,v0的前一项(即)的σ/μ为12.43%,平均值为51mv,其中v

th1

的系数(即m2/m1)的μ和σ/μ分别为1和0.27%。因此,μ和m的工艺依赖对v0的总的影响几乎可以忽略不计,这意味着v0的工艺偏斜主要由m1和m2的v

th

之差(即v

th2-v

th1

)决定。

[0051]

尺寸诱导效应指出,v

th

在慢工艺角(slow corner)和快工艺角(fast corner)之间的差值(即v

th,ss-ff

)是晶体管尺寸的一个函数。当晶体管的沟道长度为固定值时,v

th,ss-ff

随着晶体管单位沟道宽度的增长而下降。此外,v

th

的工艺偏斜量仅由晶体管的单位沟道宽度决定,而不受并联个数的影响。这意味着我们可以固定晶体管的沟道长度,通过调整m1和m2的单位沟道宽度(w1和w2)来控制v

th1,ss-ff

及v

th2,ss-ff

,从而控制v

th2,ss-ff-v

th1

,

ss-ff

的差值,从

而控制v0的工艺偏斜量。

[0052]

此外,本公开通过仿真得出亚阈值斜率因子m随温度的变化约为0.01%/℃,证实了m几乎不随温度变化。因此,v0的温度特性主要取决于具有负温度系数(temperature coefficient,tc)的v

th

和具有正温度系数的v

t

。v0的温度特性可以表示为:

[0053][0054]

由(4)可知,我们可以在固定l1和l2以及给定w1和w2的情况下,通过调整n1和n2的比值来控制v0的温度偏斜量。

[0055]

在本公开实施例中,结合图4,图5所示,提供一种具有工艺补偿的低压低功耗cmos基准电压源,包括等效nmos晶体管m

n1

、第一等效晶体管m

p1

、第二等效晶体管m

p2

、第三等效晶体管m

p3

,其中:

[0056]

所述第一等效晶体管m

p1

的源极连接至所述等效nmos晶体管的源极;

[0057]

所述第一等效晶体管m

p1

的栅极、源极相连;所述第二等效晶体管m

p2

和所述第三等效晶体管m

p3

的栅极分别和自身的漏极相连;

[0058]

所述第一等效晶体管m

p1

和所述第二等效晶体管m

p2

产生具有第一偏斜的第一电压v1;所述第一等效晶体管m

p1

和所述第三等效晶体管m

p3

产生具有第二偏斜的第二电压v2,所述第二偏斜与所述第一偏斜能够互相补偿,从而使第一电压和第二电压求和后输出对pvt变化不敏感的基准电压。

[0059]

在本公开实施例中,如图4所示,上述所需的两个基于v

th

的具有相反工艺和温度特性的电压可分别由两组串联的工作在亚阈值区域的pmos晶体管产生。为了简化分析,假设m

p1

、m

p2

、m

p3

的沟道长度相同,即l1=l2=l3,两个基于v

th

的电压v1和v2可以表示为:

[0060][0061][0062]

其中,和是比例因子。

[0063]

由以上分析可知,v1和v2的工艺偏斜分别由v

th2-v

th1

和v

th3-v

th1

决定。本公开提出了一种采用尺寸诱导效应结合体偏置技术来控制v

th

大小及其工艺偏斜量的方法,从而设计实现两个基于v

th

的相互补偿的电压。在本公开的具体实施例中,m

p1

和m

p2

被选定为具有标准阈值电压的pmos晶体管(即nominal pmos)。通过选择合适的w1和w2并控制m

p1

的体偏压,可以实现v

th2

>v

th1

和v

th2,ss-ff

<v

th1,ss-ff

。由此产生的v1与快速偏斜工艺成正比(ptfp),即v

1,ss

<v

1,ff

。与v1的产生不同,v2的产生利用了高阈值pmos晶体管m

p3

来获得与v1相反的工艺偏斜。通过控制m

p3

的体偏压以及调整w1和w3,可获得比m

p1

更高的v

th

以及更大的工艺偏斜量,即v

th3

>v

th1

和v

th3,ss-ff

>v

th1,ss-ff

,从而得到一个与快速偏斜工艺成反比(ctfp)的v2,即v

2,ss

>v

2,ff

。通过平衡获得的ptfp和ctfp电压,理论上可以完全消除v

ref

的工艺依赖性。

[0064]v1

和v2的温度特性可以表示为:

确定后,可通过调整m

p2

和m

p3

的单位沟道宽度(w2和w3)来控制v1和v2的工艺偏斜量以实现工艺补偿。操作s3中,可通过调整m

p2

和m

p3

的并联个数(n2和n3)来控制v1和v2的温度偏斜量以实现温度补偿。最后,操作s4中,可通过调整层叠在核心电路上方的本征nmos晶体管m

n1

的尺寸(也可以包括其他参数,例如串联的nmos晶体管数量等)来提高基准电压源的电源抑制比和线性灵敏度。

[0079]

在具体实施过程中,本公开提出的具有工艺补偿的低压低功耗cmos基准电压源常温下(25℃)的功耗为500pw,且在三个工艺角下所需的最小供电压均低至0.5v,如图7所示。相较于现有技术提供的混合型(bjt mosfet)基准电压源(最小供电压为1v),电路所需的最小供电压大幅度降低。

[0080]

为了验证本公开中工艺补偿的效果,将提出的具有工艺补偿的低压低功耗cmos基准电压源与传统的无工艺补偿的cmos基准电压源(如图8所示)进行了对比,比较结果如图9所示。图9给出了基准电压的温度特性,无补偿cmos基准电压源在不同工艺角下的输出电压偏差很大,而具有工艺补偿cmos基准电压源在不同工艺角下输出电压的变化很小。以常温(25℃)下的输出基准电压值为例,无工艺补偿电路在三个工艺角下的输出基准电压差值高达109.1mv,而有工艺补偿电路在三个工艺角下的输出基准电压差值仅为1.7mv,可见本公开提供的技术方案能显著降低电路的工艺依赖性。

[0081]

至此,已经结合附图对本公开实施例进行了详细描述。需要说明的是,在附图或说明书正文中,未绘示或描述的实现方式,均为所属技术领域中普通技术人员所知的形式,并未进行详细说明。此外,上述对各元件和方法的定义并不仅限于实施例中提到的各种具体结构、形状或方式,本领域普通技术人员可对其进行简单地更改或替换。

[0082]

依据以上描述,本领域技术人员应当对本公开具有工艺补偿的低压低功耗cmos基准电压源及其调试方法有了清楚的认识。

[0083]

综上所述,本公开提供了一种具有工艺补偿的低压低功耗cmos基准电压源及其调试方法,关键点在于:采用尺寸诱导效应结合体偏置技术产生了两个基于v

th

的具有互补工艺和温度特性的电压。本公开提出的基准电压源核心电路仅由三个工作在亚阈值区域的mosfet串联而成,不限mosfet的类型,无需使用bjt,电路所需的最小供电压大幅度降低,能够输出一个对pvt变化不敏感的基准电压。

[0084]

还需要说明的是,以上为本公开提供的不同实施例。这些实施例是用于说明本公开的技术内容,而非用于限制本公开的权利保护范围。一实施例的一特征可通过合适的修饰、置换、组合、分离以应用于其他实施例。

[0085]

应注意的是,在本文中,除了特别指明的之外,具备“一”元件不限于具备单一的该元件,而可具备一或更多的该元件。

[0086]

此外,在本文中,除了特别指明的之外,“第一”、“第二”等序数,只是用于区别具有相同名称的多个元件,并不表示它们之间存在位阶、层级、执行顺序、或制程顺序。一“第一”元件与一“第二”元件可能一起出现在同一构件中,或分别出现在不同构件中。序数较大的一元件的存在不必然表示序数较小的另一元件的存在。

[0087]

在本文中,除了特别指明的之外,所谓的特征甲“或”(or)或“及/或”(and/or)特征乙,是指甲单独存在、乙单独存在、或甲与乙同时存在;所谓的特征甲“及”(and)或“与”(and)或“且”(and)特征乙,是指甲与乙同时存在;所谓的“包括”、“包含”、“具有”、“含有”,

是指包括但不限于此。

[0088]

此外,在本文中,所谓的“上”、“下”、“左”、“右”、“前”、“后”、或“之间”等用语,只是用于描述多个元件之间的相对位置,并在解释上可推广成包括平移、旋转、或镜像的情形。此外,在本文中,除了特别指明的之外,“一元件在另一元件上”或类似叙述不必然表示该元件接触该另一元件。

[0089]

此外,除非特别描述或必须依序发生的步骤,上述步骤的顺序并无限制于以上所列,且可根据所需设计而变化或重新安排。并且上述实施例可基于设计及可靠度的考虑,彼此混合搭配使用或与其他实施例混合搭配使用,即不同实施例中的技术特征可以自由组合形成更多的实施例。

[0090]

以上所述的具体实施例,对本公开的目的、技术方案和有益效果进行了进一步详细说明,所应理解的是,以上所述仅为本公开的具体实施例而已,并不用于限制本公开,凡在本公开的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本公开的保护范围之内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。