1.本发明属于微处理器的设计技术,具体涉及一种微处理器中的译码部件组合逻辑表达式的生成方法、系统及介质。

背景技术:

2.微处理器的译码部件会使用到大量组合逻辑表达式,其中组合逻辑表达式用于将取指部件提供的指令编码转译成多个译码信号。而这些组合逻辑表达式常用的生成方法是根据真值表提供的指令编码和译码信号的取值对应关系,利用转换工具将其转换成组合逻辑表达式。

3.译码部件会涉及到大量的指令编码与译码信号的取值对应关系,为了便于管理所有译码信号与指令编码的取值对应关系,常会用表格来人工维护,这个表格简称译码表。译码表维护的信息由指令编码和译码信号两部分组成,指令编码是输入信息,译码信号是输出信息,表格的每一行指出在某个特定指令编码下译码信号的取值,例如表1所示的译码表示例维护了2组译码信号(译码信号0和译码信号1)和指令编码的取值之间的对应关系。

4.表1:译码表示例。

5.序号指令编码译码信号0译码信号1numinst_opcode[31:0]dec_signal0[4:0]dec_signal1[0:0]032'b0000_0000_0000_0000_0000_0000_000x_xxxxinst_opcode[4:0]1'bx132'b0000_0000_0000_0000_000x_xxxx_0010_0000inst_opcode[12:8]1'b0232'b0000_0000_0000_0000_0000_0000_0100_00005'b0_00001'b1332'b0000_0000_0000_0000_0000_0000_0110_00005'b0_00011'b0532'bxxxx_x000_0000_0000_0000_0000_1xx0_0000inst_opcode[31:27]1'b1

[0006]

为便于描述,我们进行如下命名:将指令编码命名为inst_opcode,位宽为wi,因此指令编码可以完整表示为inst_opcode[wi-1:0],inst_opcode[wi-1:0]最多有2

wi

个可能值;将译码信号命名为dec_signali,位宽为wdi,i为译码信号序号,因此译码信号可以完整表示为dec_signali[wdi-1:0]。从表1的示例可知,wi=32,wd0=5,wd1=1,inst_opcode[31:0]有6个指令编码;译码信号的取值在不同指令编码下有2种来源,一种是来源于明确的二进制常值,另一种是来源于指令编码字段,比如dec_signal0[4:0]取值有2种来源,其源于的二进制常值有5'b0_0000和5'b0_0001,其源于的指令编码字段有inst_opcode[4:0]、inst_opcode[12:8]和inst_opcode[31:27];而dec_signal1[0:0]只有1种来源,其源于的二进制常值有1’b0、1’b1和1’bx。

[0007]

从译码表提取出真值表后,利用转换工具生成各个译码信号的组合逻辑表达式的难点在于:若译码信号的取值在某个指令编码下来源于指令编码字段,而非明确的二进制常值,那么需要将这个字段对应关系转换成转换工具可识别的二进制取值对应关系,比如表1的示例中dec_signal0[4:0]在32'b0000_0000_0000_0000_0000_0000_000x_xxxx这个指令编码取值下来源于inst_opcode[4:0]的字段,这个字段对应关系需要转换成二进制取值关系才能被转换工具识别。针对该难点,目前有两种解决办法:

[0008]

方法一:真值表全展开法。首先,从译码表中提取出指令编码和译码信号的取值对应关系;然后,对取值对应关系进行再处理,判断取值对应关系是否为字段取值关系,若是,则将所有字段对应关系按照字段的二进制可能值全部展开,生成转换工具可识别的二进制取值对应关系,若不是,则不再处理该二进制取值关系;然后,将所有二进制取值对应关系放入到译码信号的真值表中;最后,通过转换工具生成译码信号的组合逻辑表达式。假设用采用方法1生成dec_signal0[4:0]的组合逻辑表示式,则需要对表1中所示的译码表中序号分别为0、1和5的3个字段对应关系按照字段的5位二进制可能值全部展开,比如,以展开序号为0的单个字段对应关系为例,如图1所示,展开单个字段对应关系后会给真值表增加2

wd0

=25=32个二进制取值对应关系,因此,生成dec_signal0[4:0]的组合逻辑表示式最终需要给真值表增加3*32=96个二进制取值对应关系。然而,仅给真值表增加96个二进制取值对应关系建立在译码表简单,译码信号字段对应关系少的情况下,但实际的译码表译码信号众多、指令编码取值多达上百个,导致真值表庞大。由于真值表需要人工维护,维护庞大的真值表一方面增加了维护成本,另一方面也加大了引入错误的可能。

[0009]

方法二:译码信号来源选择法。首先,根据译码表确认译码信号来源选择信号这个独热码的位宽和每位代表译码信号的哪一个来源;之后,用组合逻辑表达式构造出的多路数据选择器(mux),并且在mux上预留译码信号来源选择信号的接口,其中,mux的输入为译码信号的所有来源,包括译码信号取值涉及的二进制常值和指令编码字段,mux的输出为译码信号,mux的选择信号为译码信号来源选择信号,mux的路数等于译码信号来源选择信号的位宽;然后,从译码表提取出指令编码与译码信号来源选择信号的二进制取值对应关系,并保存到译码信号来源选择信号的的真值表中;最后,用转换工具根据真值表生成译码信号来源选择信号的组合逻辑表达式后,接入到mux的预留接口上,从而组成译码信号完整的组合逻辑表达式。用方法二生成译码信号的组合逻辑表达式,重点在于生成译码信号来源选择信号的组合逻辑表达式,比如,用方法2生成dec_signal0[4:0]的来源选择信号的组合逻辑表达式,具体如图2所示。图2中dec_signal0[4:0]的来源选择信号为inst_field_sel,由于dec_signal0[4:0]有5个来源,分别是2个二进制常值来源5'b0_0000和5'b0_0001,3个指令编码来源inst_opcode[4:0]、inst_opcode[12:8]和inst_opcode[31:27],因此,inst_field_sel位宽定为5位,并且inst_field_sel[4:0]这个独热码从高位到低位依次代表dec_signal0[4:0]在某个指令编码下是否分别来源于inst_opcode[4:0]、inst_opcode[12:8]、inst_opcode[31:27]、inst_field_sel[2:0]、5'b0_0000和5'b0_000。确认inst_field_sel[4:0]的定义后,还需要从译码表提取指令编码和inst_field_sel[4:0]的二进制取值对应关系到真值表中,才能利用转换工具生成inst_field_sel[4:0]的组合逻辑表达式。由此可知,用方法二生成译码信号的组合逻辑表达式并不是从译码表直接提取出译码信号的取值,而是译码信号来源选择信号的独热码取值,通过转换工具生成译码信号来源选择信号后通过多路数据选择器最终生成译码信号,这导致译码逻辑结构复杂,且分阶段生成译码信号导致组合逻辑表达式无法被转换工具全局优化。

技术实现要素:

[0010]

本发明要解决的技术问题:针对现有技术的上述问题,提供一种译码部件组合逻辑表达式的生成方法、系统及介质,本发明能有效控制真值表的规模,生成优化后的组合逻

辑表达式,本发明生成的真值表不需要人工维护,组合逻辑表达式从译码表直接提取得到,可简化转换工具生成译码信号的逻辑结构。

[0011]

为了解决上述技术问题,本发明采用的技术方案为:

[0012]

一种译码部件组合逻辑表达式的生成方法,包括针对目标译码信号的w个位进行遍历并针对任意遍历得到的目标译码信号的第w位生成真值表,且其中针对任意遍历得到的目标译码信号的第w位生成真值表包括:

[0013]

s101,初始化可能值循环变量n;

[0014]

s102,从n个指令编码的可能值中遍历取出第n个可能值,n为指令编码的可能值数量;

[0015]

s103,根据译码表,判断目标译码信号的第w位来源于第n个可能值的任意第x位是否成立,若成立则将第n个可能值的第x位取值都由1'bx变为1'b1、其他位取值保留以得到第n个可能值的新值,并将第n个可能值的新值对应于目标译码信号的第w位的取值1'b1;否则,第n个可能值所对应的译码信号取值来源于固定的二进制常值1'b0或1'b1;

[0016]

s104,将第n个可能值和目标译码信号的第w位的取值形成的对应关系输入到译码信号第w位的真值表;

[0017]

s105,更新可能值循环变量n的值;

[0018]

s106,判断循环变量n的值等于指令编码的可能值数量n是否成立,若不成立,则跳转步骤s102;则判定目标译码信号的w个位遍历完成。

[0019]

可选地,所述指令编码的可能值数量n的值为2a,其中a为指令编码位宽。

[0020]

可选地,步骤s101中初始化可能值循环变量n时,可能值循环变量n的初始值为0;步骤s105中更新可能值循环变量n的值是指将可能值循环变量n在原值的基础上加1。

[0021]

可选地,所述针对目标译码信号的w个位进行遍历包括:

[0022]

s201,初始化位循环变量w;

[0023]

s202,从目标译码信号的w个位中遍历取出目标译码信号的第w位;

[0024]

s203,针对遍历得到的目标译码信号的第w位生成真值表;

[0025]

s204,更新位循环变量w的值;

[0026]

s205,判断位循环变量w的值等于目标译码信号的位宽w是否成立,若不成立,则跳转步骤s202;则判定目标译码信号的w个位遍历完成。

[0027]

可选地,步骤s201中初始化位循环变量w时,位循环变量w的初始值为0;步骤s204中更新位循环变量w的值是指将位循环变量w的值在原值的基础上加1。

[0028]

可选地,所述目标译码信号为译码部件需要处理的num个译码信号中的任意一个,所述针对目标译码信号的w个位进行遍历之前,还包括针对num个译码信号进行遍历的步骤:

[0029]

s301,初始化译码信号循环变量num;

[0030]

s302,从需要处理的num个译码信号中遍历取出第num个译码信号;

[0031]

s303,将遍历得到的位宽为w的第num个译码信号作为目标译码信号,执行针对目标译码信号的w个位进行遍历,且针对任意遍历得到的目标译码信号的第w位生成真值表;

[0032]

s304,更新译码信号循环变量num的值;

[0033]

s305,判断译码信号循环变量num的值等于num是否成立,若不成立,则跳转步骤

s302;则判定num个译码信号遍历完成。

[0034]

可选地,步骤s301中初始化译码信号循环变量num时,译码信号循环变量num的初始值为0;步骤s304中更新译码信号循环变量num的值是指将译码信号循环变量num的值在原值的基础上加1。

[0035]

可选地,所述针对任意遍历得到的目标译码信号的第w位生成真值表之后,还包括利用转换工具根据目标译码信号的第w位生成真值表生成目标译码信号的第w位的组合逻辑表达式。

[0036]

此外,本发明还提供一种译码部件组合逻辑表达式的生成系统,包括相互连接的微处理器和存储器,所述微处理器被编程或配置以执行所述译码部件组合逻辑表达式的生成方法的步骤。

[0037]

此外,本发明还提供一种计算机可读存储介质,所述计算机可读存储介质中存储有计算机程序,所述计算机程序用于被微处理器编程或配置以执行所述译码部件组合逻辑表达式的生成方法的步骤。

[0038]

本发明译码部件组合逻辑表达式的生成方法包括针对目标译码信号的w个位的任意第w位生成真值表,包括:针对n个指令编码的可能值遍历的第n个可能值,若第w位来源于第n个可能值的任意第x位则将第n个可能值的第x位取值都由1'bx变为1'b1、其他位取值保留以得到第n个可能值的新值,并将第n个可能值的新值对应于目标译码信号的第w位的取值1'b1;否则,第n个可能值对应于译码信号第w位的取值1'b1或1'b0;将第n个可能值和目标译码信号的第w位的取值形成的对应关系输入到译码信号第w位的真值表。和现有技术相比,本发明主要具有下述优点:

[0039]

1、本发明能有效控制译码表的规模。译码表中在译码信号取值在某个指令编码下来源于指令编码字段时,本发明会将该取值对应关系由1个展开成width个,width为字段位宽,同时,字段的位数越大,width与2

width

的差值越大,本发明方法展开的译码表规模相对于真值表全展开法就越小。因此,本发明方法能有效控制译码表的规模。

[0040]

2、本发明能生成优化的译码信号组合逻辑表达式。本发明方法只需要小规模展开译码表,即可通过转换工具直接生成译码信号的组合逻辑表达式,无需像译码信号来源选择法经过一个多路数据选择器才能间接生成译码信号的组合逻辑表达式。因此,相对译码信号来源选择法,本发明方法生成的组合逻辑表达式能被转换工具全局优化,从而生成优化的译码信号组合逻辑表达式。

[0041]

3、本发明方法生成的真值表不需要人工维护,采用本发明方法生成的组合逻辑表达式为从译码表直接提取得到,因此可简化转换工具生成译码信号的逻辑结构。

附图说明

[0042]

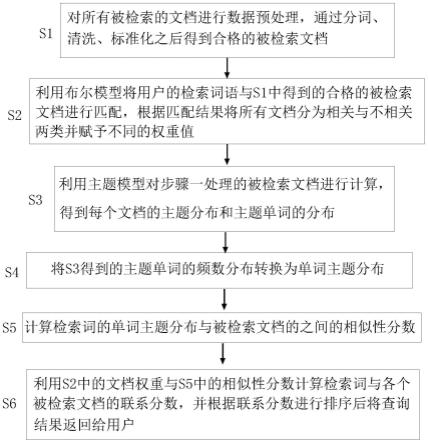

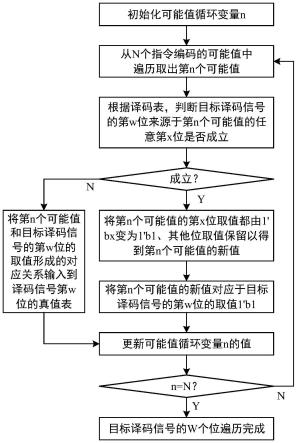

图1是现有技术中真值表全展开法展开译码信号与指令编码字段的取值对应关系示意图。

[0043]

图2是现有技术中译码信号来源选择法示意图。

[0044]

图3为本发明实施例核心方法的流程示意图。

[0045]

图4为本发明实施例方法的流程示意图。

[0046]

图5是本发明实施例方法展开译码信号与指令编码字段的取值对应关系示意图。

具体实施方式

[0047]

本实施例译码部件组合逻辑表达式的生成方法包括针对目标译码信号的w个位进行遍历并针对任意遍历得到的目标译码信号的第w位生成真值表,如图3所示,其中针对任意遍历得到的目标译码信号的第w位生成真值表包括:

[0048]

s101,初始化可能值循环变量n;

[0049]

s102,从n个指令编码的可能值中遍历取出第n个可能值,n为指令编码的可能值数量;

[0050]

s103,根据译码表,判断目标译码信号的第w位来源于第n个可能值的任意第x位是否成立,若成立则将第n个可能值的第x位取值都由1'bx变为1'b1、其他位取值保留以得到第n个可能值的新值,并将第n个可能值的新值对应于目标译码信号的第w位的取值1'b1;否则,,第n个可能值所对应的译码信号取值来源于固定的二进制常值1'b0或1'b1(二进制的常数0或1),而非来源于第n个可能值的某位;

[0051]

s104,将第n个可能值和目标译码信号的第w位的取值形成的对应关系输入到译码信号第w位的真值表;

[0052]

s105,更新可能值循环变量n的值;

[0053]

s106,判断循环变量n的值等于指令编码的可能值数量n是否成立,若不成立,则跳转步骤s102;则判定目标译码信号的w个位遍历完成。

[0054]

根据指令编码位宽即可确定指令编码的可能值数量na,本实施例中指令编码的可能值数量n的值为2a,其中a为指令编码位宽。

[0055]

本实施例步骤s101中初始化可能值循环变量n时,可能值循环变量n的初始值为0;步骤s105中更新可能值循环变量n的值是指将可能值循环变量n在原值的基础上加1。

[0056]

参见图4,本实施例针对目标译码信号的w个位进行遍历包括:

[0057]

s201,初始化位循环变量w;

[0058]

s202,从目标译码信号的w个位中遍历取出目标译码信号的第w位;

[0059]

s203,针对遍历得到的目标译码信号的第w位生成真值表;

[0060]

s204,更新位循环变量w的值;

[0061]

s205,判断位循环变量w的值等于目标译码信号的位宽w是否成立,若不成立,则跳转步骤s202;则判定目标译码信号的w个位遍历完成。

[0062]

参见图4,本实施例步骤s201中初始化位循环变量w时,位循环变量w的初始值为0;步骤s204中更新位循环变量w的值是指将位循环变量w的值在原值的基础上加1。

[0063]

参见图4,本实施例目标译码信号为译码部件需要处理的num个译码信号中的任意一个,所述针对目标译码信号的w个位进行遍历之前,还包括针对num个译码信号进行遍历的步骤:

[0064]

s301,初始化译码信号循环变量num;

[0065]

s302,从需要处理的num个译码信号中遍历取出第num个译码信号;

[0066]

s303,将遍历得到的位宽为w的第num个译码信号作为目标译码信号,执行针对目标译码信号的w个位进行遍历,且针对任意遍历得到的目标译码信号的第w位生成真值表;

[0067]

s304,更新译码信号循环变量num的值;

[0068]

s305,判断译码信号循环变量num的值等于num是否成立,若不成立,则跳转步骤

s302;则判定num个译码信号遍历完成。

[0069]

参见图4,本实施例步骤s301中初始化译码信号循环变量num时,译码信号循环变量num的初始值为0;步骤s304中更新译码信号循环变量num的值是指将译码信号循环变量num的值在原值的基础上加1。

[0070]

本实施例中,针对任意遍历得到的目标译码信号的第w位生成真值表之后,还包括利用转换工具根据目标译码信号的第w位生成真值表生成目标译码信号的第w位的组合逻辑表达式。由于利用转换工具根据目标译码信号的第w位生成真值表生成目标译码信号的第w位的组合逻辑表达式为现有方法,故其实现细节在此不再详述。

[0071]

如图4所示,本实施例方法的完整步骤包括:1)开始生成num个译码信号的所有组合逻辑表达式;2)从第一个译码信号开始生成其所有位的组合逻辑表达式,num=0;3)从第num个译码信号第0位开始生成组合逻辑表达式,w=0,第num个译码信号位宽为w;4)生成第num个译码信号第w位的真值表,5)继续生成第num个译码信号下一位的真值表,w=w 1;6)w是否等于w,w若等于w,代表第num个译码信号的所有位都已经生成其组合逻辑表达式,则跳到步骤7);w若不等于w,代表第num个译码信号存在部分位还尚未生成组合逻辑表达式,则跳到步骤4);7)继续生成下一个译码信号所有位的组合逻辑表达式,num=num 1;8)num是否等于num,num若等于num,代表所有译码信号的所有位都已经生成其组合逻辑表达式,则跳到步骤9);num若不等于num,代表存在部分译码信号的所有位尚未生成组合逻辑表达式,则跳到步骤3);9)结束。

[0072]

其中,步骤4)的详细步骤为:4-1)从指令编码的第一个可能值开始生成与译码信号第w位取值的对应关系,n=0,指令编码的可能值总数为n,n等于2^(指令编码位宽);4-2)根据译码表判断译码信号第w位是否来源于指令编码第n个可能值的某一位,即第x位,若是,则跳到步骤4-4);若不是,则跳到步骤4-3);4-3)指令编码第n个可能值对应于译码信号第w位的取值1'b1或1'b0,跳到步骤4-6);4-4)将指令编码第n个可能值的第x位取值都由1'bx变为1'b1,指令编码第n个可能值的其他位取值保留,得到指令编码第n个可能值的新值;4-5)指令编码第n个可能值的新值对应于译码信号第w位的取值1'b1;4-6)将指令编码第n个可能值和译码信号第w位取值形成的对应关系输入到译码信号第w位的真值表;4-7)继续生成指令编码下一个可能值与译码信号第w位取值的对应关系,n=n 1;4-8)n是否等于n,n若等于n,代表指令编码所有可能值与译码信号第w位的取值对应关系都已经保存到译码信号第w位的真值表中,则跳到步骤4-9);n若不等于n,代表指令编码存在部分可能值还尚未与译码信号第w位取值确定对应关系,则跳到步骤4-2);4-9)转换工具根据译码信号第w位的真值表生成译码信号第w位的组合逻辑表达式。

[0073]

综上所述,本实施例译码部件组合逻辑表达式的生成方法包括方法将根据译码表独立生成译码信号每位的真值表,在译码信号某一位在某个指令编码下来源于指令编码字段某一位的情况时,将译码信号该位来源于某个指令编码的那位由1'bx变为1'b1,形成该指令编码新值;与1'b1形成新的译码信号与指令编码的取值对应关系输入到真值表;但在译码信号该位在其他指令编码下为常值1'b0或1'b1的情况时,无需特殊处理,将现有的取值对应关系输入到真值表即可;最终通过转换工具将真值表转换成译码信号该位的组合逻辑表达式;按照译码信号位数重复上述步骤若干次即可得到译码信号完整的组合逻辑表达式。本实施例译码部件组合逻辑表达式的生成方法具有下述优点:1、本实施例方法能有效

控制译码表的规模。译码表中在译码信号取值在某个指令编码下来源于指令编码字段时,本实施例方法会将该取值对应关系由1个展开成width个,width为字段位宽,比如用本实施例方法展开dec_signal0[4:0]取值来源于的某个指令编码的取值对应关系,如图5所示,对比图1和图5,可以发现本发明方法仅需要对上述取值关系由1个展开成width=5个译码信号与指令编码的取值对应关系,即可得到译码信号的组合逻辑表达式,而真值表全展开法需要展开成2

width

=25个译码信号与指令编码的取值对应关系才能得到。同时,字段的位数越大,width与2

width

的差值越大,本实施例方法展开的译码表规模相对于真值表全展开法就越小。因此,本实施例方法能有效控制译码表的规模。2、本实施例方法能生成优化的译码信号组合逻辑表达式。本实施例方法只需要小规模展开译码表,即可通过转换工具直接生成译码信号的组合逻辑表达式,无需像译码信号来源选择法经过一个多路数据选择器才能间接生成译码信号的组合逻辑表达式。因此,相对译码信号来源选择法,本实施例方法成的组合逻辑表达式能被转换工具全局优化,从而生成优化的译码信号组合逻辑表达式。

[0074]

此外,本实施例还提供一种译码部件组合逻辑表达式的生成系统,包括相互连接的微处理器和存储器,所述微处理器被编程或配置以执行前述译码部件组合逻辑表达式的生成方法的步骤。此外,本实施例还提供一种计算机可读存储介质,所述计算机可读存储介质中存储有计算机程序,所述计算机程序用于被微处理器编程或配置以执行前述译码部件组合逻辑表达式的生成方法的步骤。

[0075]

本领域内的技术人员应明白,本技术的实施例可提供为方法、系统、或计算机程序产品。因此,本技术可采用完全硬件实施例、完全软件实施例、或结合软件和硬件方面的实施例的形式。而且,本技术可采用在一个或多个其中包含有计算机可用程序代码的计算机可读存储介质(包括但不限于磁盘存储器、cd-rom、光学存储器等)上实施的计算机程序产品的形式。本技术是参照根据本技术实施例的方法、设备(系统)、和计算机程序产品的流程图和/或方框图来描述的。应理解可由计算机程序指令实现流程图和/或方框图中的每一流程和/或方框、以及流程图和/或方框图中的流程和/或方框的结合。可提供这些计算机程序指令到通用计算机、专用计算机、嵌入式处理机或其他可编程数据处理设备的处理器以产生一个机器,使得通过计算机或其他可编程数据处理设备的处理器执行的指令产生用于实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能的装置。这些计算机程序指令也可存储在能引导计算机或其他可编程数据处理设备以特定方式工作的计算机可读存储器中,使得存储在该计算机可读存储器中的指令产生包括指令装置的制造品,该指令装置实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能。这些计算机程序指令也可装载到计算机或其他可编程数据处理设备上,使得在计算机或其他可编程设备上执行一系列操作步骤以产生计算机实现的处理,从而在计算机或其他可编程设备上执行的指令提供用于实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能的步骤。

[0076]

以上所述仅是本发明的优选实施方式,本发明的保护范围并不仅局限于上述实施例,凡属于本发明思路下的技术方案均属于本发明的保护范围。应当指出,对于本技术领域的普通技术人员来说,在不脱离本发明原理前提下的若干改进和润饰,这些改进和润饰也应视为本发明的保护范围。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。