一种多沟道gan hemt器件及制作方法

技术领域

1.本发明涉及gan hemt器件技术领域,特别涉及一种多沟道gan hemt器件及制作方法。

背景技术:

2.gan hemt器件具有低导通电阻、高开关频率的优势,成为高效小型化电源系统研制的优选器件。gan hemt采用algan/gan异质结结构,可以通过调整algan势垒层的组分和厚度来调制沟道载流子的浓度。然而对于p-gan帽层结构,由于p-gan无法获得高浓度的掺杂,为保证获得常关型器件,algan/gan异质结中不能有非常高的载流子浓度,从而制约了器件导通电阻的降低。

3.增加沟道层数可以成倍增加沟道载流子浓度,从而显著降低沟道导通电阻。然而,由于电场屏蔽效应的存在,单个栅很难实现对下层多个沟道的有效控制,因此大部分gan hemt产品均采用单沟道结构。为了开发多沟道结构,有研究人员开发了fin结构,采用在沟道的侧面增加栅结构来提升栅对多层沟道的控制作用。而为满足fin结构的工作要求,栅包裹区域多沟道材料的宽度被限制在1um以内,导致器件的有效导通面积受到严重制约。

技术实现要素:

4.本发明所要解决的技术问题是如何解决单栅控制在多沟道结构中遇到的电场屏蔽问题,以及如何提升栅对多沟道结构的控制能力。

5.本发明解决上述技术问题的技术方案如下:一种多沟道gan hemt器件,包括从下至上依次生长的衬底、高阻缓冲层、多层沟道结构、介质掩膜层和隔离介质层;多层沟道结构为交替的势垒层与沟道层,且多层沟道结构的底层和顶层均为势垒层;还包括底栅控制层、顶栅控制层、栅电极、源电极和漏电极;高阻缓冲层的上表面位于多层沟道结构的底层势垒层中生长有底栅控制层,多层沟道结构的顶层势垒层的上表面位于介质掩膜层中生长有顶栅控制层,栅电极用于连通底栅控制层和顶栅控制层,栅电极外包裹有用于隔离多层沟道结构的隔离介质层,源电极和漏电极位于多层沟道结构的两侧,且贯穿多层沟道结构的顶层势垒层、中间沟道层和中间势垒层延伸至底层势垒层的上表面;隔离介质层和介质掩膜层开设有裸露栅电极、源电极和漏电极的窗口。

6.本发明的有益效果是:多沟道gan hemt器件进一步降低了器件导通电阻,同时引入底栅控制结构,解决了顶栅结构对多沟道结构控制能力差的问题,相对于fin结构提升栅对多沟道控制能力的结构,器件传输截面显著提升,更加有利于高压大电流器件的制备。

7.在上述技术方案的基础上,本发明还可以做如下改进。

8.进一步,衬底为硅、gan、sic或蓝宝石;高阻缓冲层为algan或gan,电阻率大于1e6ω.m。

9.进一步,栅控制层包括底栅控制层和顶栅控制层,栅控制层为掺杂gan材料,掺镁、

硅或锗元素形成n型或者p型材料,掺杂后离化载流子浓度大于1e17cm-3

。

10.进一步,介质掩膜层为sio2或si3n4等氟基等离子体或含氟湿法溶液可以刻蚀的介质材料。

11.进一步,势垒层为algan材料;沟道层为非故意掺杂gan材料,沟道层厚度小于100nm。

12.进一步,源电极和漏电极均为欧姆接触金属,欧姆接触金属为ti、al、ni、au、si及tin组成的多层金属,其中ti金属层或tin金属层与底层势垒层的上表面接触。

13.进一步,隔离介质层为沉积的alo、hfo或aln介质。

14.进一步,栅电极为栅接触金属,栅接触金属为可与gan材料形成良好肖特基接触的金属。

15.本发明另一技术方案如下:一种沟道gan hemt器件的制作方法,制作方法包括如下步骤:步骤1,在衬底上依次沉积高阻缓冲层、底栅控制层以及介质掩膜层;步骤2,采用标准光刻工艺定义底栅控制层的光刻胶掩膜,刻蚀光刻胶掩膜以外的步骤1中生成的介质掩膜层,去除光刻胶掩膜,然后采用剩余介质掩膜层作为刻蚀掩膜,刻蚀掉刻蚀掩膜以外的底栅控制层;步骤3,去除步骤2剩余的介质掩膜层后,在样品上依次沉积多层沟道结构和顶栅控制层的多层结构,然后沉积一层介质掩膜层;步骤4,采用标准光刻工艺定义顶栅控制层的光刻胶掩膜,刻蚀光刻胶掩膜以外的步骤3中生成的介质掩膜层,去除光刻胶掩膜,然后采用剩余介质掩膜层作为刻蚀掩膜,刻蚀掉刻蚀掩膜以外的顶栅控制层;步骤5,去除步骤4剩余的介质掩膜层后,在样品上重新沉积一层介质掩膜层,采用标准光刻工艺定义欧姆接触金属区域,刻蚀掉欧姆接触金属区域的介质掩膜层,利用剩余的介质掩膜层做刻蚀掩膜,刻蚀掉剩余的介质掩膜层以外的顶层势垒层、中间沟道层、中间势垒层直到底层势垒层;步骤6,在欧姆接触金属区域,制备欧姆接触金属,然后将欧姆接触金属进行退火,生成源电极和漏电极;步骤7,再在样品上沉积一层介质掩膜层,利用标准光刻工艺定义底栅接触孔区域,刻蚀掉底栅接触孔区域的介质掩膜层,利用剩余的介质掩膜层作为刻蚀掩膜,刻蚀掉剩余的介质掩膜层以外的顶层势垒层、中间沟道层、中间势垒层和底层势垒层直到底栅控制层,然后再生长一层隔离介质层;步骤8,采用标准光刻工艺定义顶栅接触孔区域,刻蚀掉顶栅接触孔区域的隔离介质层和介质掩膜层;在底栅接触孔区域刻蚀掉隔离介质层;步骤9,采用标准光刻工艺定义栅接触孔区域,刻蚀掉栅接触孔区域部分隔离介质层,以使栅接触孔区域连通底栅接触孔区域和顶栅接触孔区域形成栅金属区域,在栅金属区域制备栅接触金属,生成栅电极;然后再生长一层隔离介质层;步骤10,采用标准光刻工艺定义台面隔离区域,采用光刻胶做掩膜刻蚀器件位于源电极和漏电极连线方向两侧的隔离介质层、介质掩膜层、多层沟道结构和部分高阻缓冲层;采用标准光刻工艺定义金属接触孔区域,利用光刻胶做掩膜刻蚀金属接触孔区域对应

的隔离介质层和介质掩膜层裸露栅电极、源电极和漏电极。

16.进一步,高阻缓冲层、势垒层和沟通层均采用氯基等离子进行刻蚀;栅控制层采用氯基干法刻蚀方法进行刻蚀;隔离介质层采用氟基或氯基等离子进行刻蚀;采用有机清洗的方法去除光刻胶掩膜;采用正胶剥离的方法制备欧姆接触金属和栅接触金属;欧姆接触金属的退火温度在400度到900度,气氛为惰性气体。

附图说明

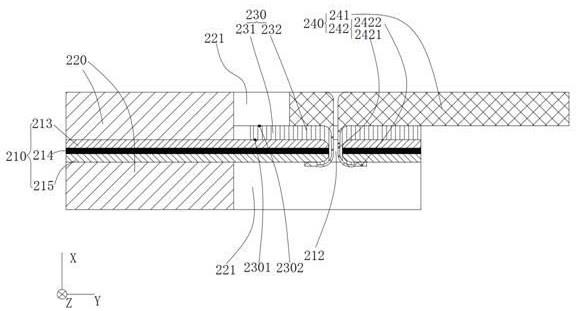

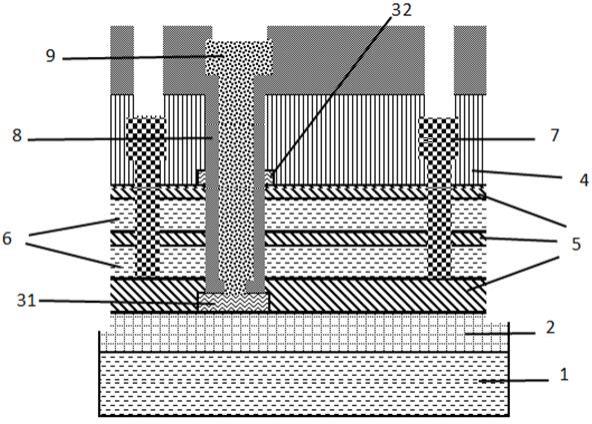

17.图1为本发明一种多沟道gan hemt器件的制作方法第一示意图;图2为本发明一种多沟道gan hemt器件的制作方法第二示意图;图3为本发明一种多沟道gan hemt器件的制作方法第三示意图;图4为本发明一种多沟道gan hemt器件的制作方法第四示意图;图5为本发明一种多沟道gan hemt器件的制作方法第五示意图;图6为本发明一种多沟道gan hemt器件的制作方法第六示意图;图7为本发明一种多沟道gan hemt器件的制作方法第七示意图;图8为本发明一种多沟道gan hemt器件的制作方法第八示意图;图9为本发明一种多沟道gan hemt器件的制作方法第九示意图;图10为本发明一种多沟道gan hemt器件的制作方法第十示意图;图11为本发明一种多沟道gan hemt器件的制作方法第十一示意图;图12为本发明一种多沟道gan hemt器件的制作方法第十二示意图;图13为本发明一种多沟道gan hemt器件的制作方法第十三示意图;图14为本发明一种多沟道gan hemt器件的制作方法第十四示意图;图15为本发明一种多沟道gan hemt器件的第一结构示意图;图16为本发明一种多沟道gan hemt器件的第二结构示意图。

18.附图中,各标号所代表的部件列表如下:1、衬底,2、高阻缓冲层,3、栅控制层,31、底栅控制层,32、顶栅控制层,4、介质掩膜层,5、势垒层,6、沟道层,7、欧姆接触金属,8、隔离介质层,9、栅接触金属。

具体实施方式

19.以下结合附图对本发明的原理和特征进行描述,所举实例只用于解释本发明,并非用于限定本发明的范围。

20.如图1~16所示,本发明实施例1一种多沟道gan hemt器件,包括从下至上依次生长的衬底1、高阻缓冲层2、多层沟道结构、介质掩膜层4和隔离介质层8;多层沟道结构为交替的势垒层5与沟道层6,且多层沟道结构的底层和顶层均为势垒层5;还包括底栅控制层31、顶栅控制层32、栅电极、源电极和漏电极;高阻缓冲层2的上表面位于多层沟道结构的底层势垒层5中生长有底栅控制层31,多层沟道结构的顶层势垒层5的上表面位于介质掩膜层4中生长有顶栅控制层32,栅电极用于连通底栅控制层31和顶栅控制层32,栅电极外包裹有用于隔离多层沟道结构的隔离介质层8,源电极和漏电极位于多层沟道结构的两侧,且贯穿多层沟道结构的顶层势垒层5、中间沟道层6和中间势垒层5延伸至底层势垒层5的上表面;隔离介质层8和介质掩膜层4开设有裸露栅电极、源电极和漏电极的窗口。

21.多沟道gan hemt器件进一步降低了器件导通电阻,同时引入底栅控制结构,解决了顶栅结构对多沟道结构控制能力差的问题,相对于fin结构提升栅对多沟道控制能力的结构,器件传输截面显著提升,更加有利于高压大电流器件的制备。

22.本发明实施例2一种多沟道gan hemt器件,在实施例1的基础上,衬底1为硅、gan、sic或蓝宝石;高阻缓冲层2为algan或gan,电阻率大于1e6ω.m。

23.本发明实施例3一种多沟道gan hemt器件,在实施例1的基础上,栅控制层3包括底栅控制层31和顶栅控制层32,栅控制层3为掺杂gan材料,掺镁、硅或锗元素形成n型或者p型材料,掺杂后离化载流子浓度大于1e17cm-3

。

24.本发明实施例4一种多沟道gan hemt器件,在实施例1的基础上,介质掩膜层4为sio2或si3n4等氟基等离子体或含氟湿法溶液可以刻蚀的介质材料。

25.本发明实施例5一种多沟道gan hemt器件,在实施例1的基础上,势垒层5为algan材料;沟道层6为非故意掺杂gan材料,沟道层6厚度小于100nm。

26.本发明实施例6一种多沟道gan hemt器件,在实施例1的基础上,源电极和漏电极均为欧姆接触金属7,欧姆接触金属7为ti、al、ni、au、si及tin组成的多层金属,其中ti金属层或tin金属层与底层势垒层5的上表面接触。

27.本发明实施例7一种多沟道gan hemt器件,在实施例1的基础上,隔离介质层8为沉积的alo、hfo或aln介质。沉积采用ald方法。

28.本发明实施例8一种多沟道gan hemt器件,在实施例1的基础上,栅电极为栅接触金属9,栅接触金属9为可与gan材料形成良好肖特基接触的金属。如n型gan所用ni/au、pt/au等,p型gan所用 ti/au、tin/al/ti等。

29.本发明实施例9,在实施例1至8任一实施例的基础上,用于制作实施例 1至8任一实施例的多沟道gan hemt器件,制作方法包括如下步骤:步骤1,如图1所示,在衬底1上依次沉积高阻缓冲层2、底栅控制层31以及介质掩膜层4;步骤2,如图2所示,采用标准光刻工艺定义底栅控制层31的光刻胶掩膜,刻蚀光刻胶掩膜以外的步骤1中生成的介质掩膜层4,去除光刻胶掩膜,然后采用剩余介质掩膜层4作为刻蚀掩膜,刻蚀掉刻蚀掩膜以外的底栅控制层31;步骤3,如图3所示,去除步骤2剩余的介质掩膜层4后,在样品上依次沉积多层沟道结构和顶栅控制层32的多层结构,然后沉积一层介质掩膜层4;步骤4,如图4所示,采用标准光刻工艺定义顶栅控制层32的光刻胶掩膜,刻蚀光刻胶掩膜以外的步骤3中生成的介质掩膜层4,去除光刻胶掩膜,然后采用剩余介质掩膜层4作为刻蚀掩膜,刻蚀掉刻蚀掩膜以外的顶栅控制层32;步骤5,如图5所示,去除步骤4剩余的介质掩膜层4后,在样品上重新沉积一层介质掩膜层4,采用标准光刻工艺定义欧姆接触金属区域,刻蚀掉欧姆接触金属区域的介质掩膜层4,利用剩余的介质掩膜层4做刻蚀掩膜,刻蚀掉剩余的介质掩膜层4以外的顶层势垒层5、中间沟道层6、中间势垒层5直到底层势垒层5;步骤6,如图6所示,在欧姆接触金属区域,制备欧姆接触金属7,然后将欧姆接触金属7进行退火,生成源电极和漏电极;步骤7,再在样品上沉积一层介质掩膜层4,利用标准光刻工艺定义底栅接触孔区

域,刻蚀掉底栅接触孔区域的介质掩膜层4,利用剩余的介质掩膜层4作为刻蚀掩膜,刻蚀掉剩余的介质掩膜层4以外的顶层势垒层5、中间沟道层6、中间势垒层5和底层势垒层5直到底栅控制层31,然后再生长一层隔离介质层8,底栅接触区域以外如图7,底栅接触孔区域如图8;步骤8,采用标准光刻工艺定义顶栅接触孔区域,刻蚀掉顶栅接触孔区域的隔离介质层8和介质掩膜层4;在底栅接触孔区域刻蚀掉隔离介质层8,底栅接触区域以外如图9,底栅接触孔区域如图10;步骤9,采用标准光刻工艺定义栅接触孔区域,刻蚀掉栅接触孔区域部分隔离介质层8,以使栅接触孔区域连通底栅接触孔区域和顶栅接触孔区域形成栅金属区域,在栅金属区域制备栅接触金属9,生成栅电极;然后再生长一层隔离介质层8,顶栅接触孔区域以外如图11,顶栅接触孔区域以内如图12;步骤10,采用标准光刻工艺定义台面隔离区域,采用光刻胶做掩膜刻蚀器件位于源电极和漏电极连线方向两侧的隔离介质层8、介质掩膜层4、多层沟道结构和部分高阻缓冲层2;采用标准光刻工艺定义金属接触孔区域,利用光刻胶做掩膜刻蚀金属接触孔区域对应的隔离介质层8和介质掩膜层4裸露栅电极、源电极和漏电极,顶栅接触孔区域如图13,底栅接触孔区域如图14。

30.本发明实施例10一种多沟道gan hemt器件的制作方法,在实施例9的基础上,高阻缓冲层2、势垒层5和沟通层6均采用氯基等离子进行刻蚀;栅控制层3采用氯基干法刻蚀方法进行刻蚀;隔离介质层8采用氟基或氯基等离子进行刻蚀;采用有机清洗的方法去除光刻胶掩膜;采用正胶剥离的方法制备欧姆接触金属7和栅接触金属9;欧姆接触金属7的退火温度在400度到900度,气氛为惰性气体。

31.具体实施例11、在洁净的si衬底1上采用mocvd依次沉积碳掺杂algan高阻缓冲层2和200nm的mg掺杂p型gan底栅控制层31,掺杂后p型gan空穴载流子浓度达到1e17cm-3

,采用pecvd沉积sin介质掩膜层4。

32.2、采用标准光刻工艺定义底栅控制层31的光刻胶掩膜,采用氟基等离子体刻蚀光刻胶掩膜以外的sin介质掩膜层4,采用丙酮和乙醇有机清洗的方式去除光刻胶掩膜,然后用剩余sin介质掩膜层4作为刻蚀掩膜,刻蚀掉介质掩膜层4以外的p-gan底栅控制层31。

33.3、采用boe溶液湿法刻蚀sin介质掩膜层4后,在样品上利用mocvd依次沉积20nm al

0.2

ga

0.8

n势垒层5、50nm gan沟道层6、20 nm al

0.2

ga

0.8

n势垒层5、50 nmgan沟道层6、20 nm al

0.2

ga

0.8

n势垒层5和100nm p-gan顶栅控制层32,其中p-gan顶栅控制层32采用mg掺杂,掺杂后空穴载流子浓度达到1e17cm-3

,最后采用pecvd生长一层sin介质掩膜层4。

34.4、采用标准光刻工艺定义顶栅控制层32的光刻胶掩膜,采用氟基等离子体刻蚀光刻胶掩膜以外的步骤3中生成的sin介质掩膜层4,采用丙酮和乙醇有机清洗的方式去除光刻胶掩膜,然后用sin介质掩膜层4作为刻蚀掩膜,刻蚀掉刻蚀掩膜以外的p-gan顶栅控制层32。

35.5、采用boe溶液湿法刻蚀工艺去除sin介质掩膜层4后,在样品上重新沉积一层sin介质掩膜层4,采用标准光刻工艺定义欧姆接触金属区域,利用氟基等离子体刻蚀掉欧姆接触区域sin介质掩膜4,然后利用有丙酮和乙醇机清洗工艺去除光刻胶,在此基础上利用剩

余的sin介质掩膜层4刻蚀掉sin介质掩膜层4以外的algan势垒层5、gan沟道层6、algan势垒层5和gan沟道层6的多层结构。

36.6、利用标准光刻工艺定义欧姆接触金属区域,采用正胶剥离的方法制备ti/al/ti欧姆接触金属7,然后在氮气气氛下600度进行金属退火。

37.7、再在样品上沉积一层sin介质掩膜,利用标准光刻工艺定义底栅接触孔区域,刻蚀掉底栅接触孔区域以外的sin介质掩膜层4,采用丙酮和乙醇有机清洗的方式去除光刻胶掩膜,再以sin介质掩膜层4作为刻蚀掩膜,刻蚀掉剩余的sin介质掩膜层4以外的algan势垒层5、gan沟道层6、algan势垒层5、gan沟道层6的多层结构,并刻蚀多层结构下方的部分algan势磊层5,直到p-gan栅控制层31,然后再用ald生长一层alo隔离介质层8。

38.8、采用标准光刻工艺定义顶栅接触孔区域,采用氟基等离子体刻蚀掉sin介质掩膜层4,采用氯基等离子体刻蚀掉alo隔离介质层8;在底栅控制孔区域采用氯基等离子体刻蚀掉alo隔离介质层8。

39.9、采用标准光刻工艺定义栅接触孔区域,采用氯基等离子体刻蚀掉栅接触孔其区域部分alo隔离介质层8,以使栅接触孔区域连通底栅控制孔区域和顶栅接触孔区域形成栅金属区域,采用正胶剥离的方法,在栅金属区域制备ti/au栅接触金属9,生成栅电极,然后再用ald生长一层alo隔离介质层8。

40.10、采用标准光刻工艺定义台面隔离区域,采用光刻胶做掩膜刻蚀基于氯基等离子体刻蚀alo隔离介质层8,采用氟基等离子体刻蚀sin介质掩膜层4,再利用氯基等离子体刻蚀algan势垒层5、gan沟道层6、algan势垒层5、gan沟道层6和algan势垒层5的多层结构,然后刻蚀部分algan高阻缓冲层2材料,采用丙酮和乙醇有机清洗去除光刻胶,从而形成台面隔离。

41.利用标准光刻工艺定义金属接触孔区域,利用光刻胶掩膜基于氯基等离子体刻蚀alo隔离介质层8,利用氟基等离子体刻蚀sin介质掩膜层4,露出栅电极、源电极和漏电极。

42.以上所述仅为本发明的较佳实施例,并不用以限制本发明,凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。