1.本发明属于微组装技术领域,尤其涉及一种硅基芯片的多层基板堆叠的封装体及堆叠封装方法。

背景技术:

2.随着军事电子产品小型化、高密度化、高集成度化的发展趋势,内部组件要求在越来越小的体积内承受越来越多的性能指标,例如电流承载能力、功率输出能力、散热能力等,在组件小型化进程中,叠层封装在电子组件中越来越受到重视,尤其是针对大功率、高承载电流一类的硅基芯片,芯片背面为硅基,无散热通道,目前只能采用直接粘接的方式进行芯片的组装,因此可以通过叠层封装的方式来解决封装过程中遇到的可靠性、散热等一系列问题。

3.现有技术中,对于大功率硅基芯片的封装,具有以下不足:

4.一方面,芯片散热技术主要采用合金共晶或粘接的方式实现,其中采用合金共晶的方式要求芯片底层镀金,采用粘接的方式散热效果较差。

5.另一方面,芯片表面采用金丝楔形键合的方式进行电气连接,但是在输出电流大时,容易造成金丝熔断,且芯片表面需要键合数根金丝与外部电路相连,会增加整个芯片的使用面积。

6.再一方面,在芯片与基板之间的连接一般采用焊接的方式,在进行堆叠的操作过程中,需要考虑到散热、输出功率、电路匹配等问题,芯片封装完成后,还需要考虑整个封装体在组件及模块中的组装方式,尤其在大功率芯片在进行封装时均不容易实现。

技术实现要素:

7.鉴于上述的分析,本发明旨在提供一种硅基芯片的多层基板堆叠的封装体及堆叠封装方法,解决了现有技术中的芯片散热效果差、连接可靠性差、使用面积大等问题。

8.本发明的目的主要是通过以下技术方案实现的:

9.本发明提供了一种硅基芯片的多层基板堆叠的封装体,包括依次层叠连接的顶层基板、中间基板和底层基板;中间基板上开设通孔,硅基芯片置于通孔中;硅基芯片正面的芯片栅极、芯片漏极和芯片源极上设有金凸点,硅基芯片正面通过金凸点与底层基板键合形成电气连接,硅基芯片背面与顶层基板之间在封装过程中形成金硅共晶层。

10.进一步地,硅基芯片包括硅层以及设于硅层同一表面的芯片栅极、芯片漏极和芯片源极,金凸点设于芯片栅极、芯片漏极和芯片源极上。

11.进一步地,顶层基板包括顶层板体以及设于顶层板体正面的正面镀金层,正面镀金层与硅基芯片的背面之间在封装过程中形成金硅共晶层。

12.进一步地,底层基板包括底层板体、底层焊接层、底层栅极键合区、底层漏极键合区、底层源极键合区、底层栅极、底层漏极和底层源极;底层栅极键合区、底层漏极键合区、底层源极键合区设于底层板体的正面,底层栅极、底层漏极和底层源极设于底层板体的背

面;底层栅极键合区与底层栅极连通,底层漏极键合区与底层漏极连接,底层源极键合区与底层源极连接;底层栅极键合区与芯片栅极上的金凸点键合,底层漏极键合区与芯片漏极上的金凸点键合,底层源极键合区与底层源极上的金凸点键合。

13.进一步地,中间基板包括中间板体、设于中间板体正面的正面焊接层以及设于中间板体背面的背面焊接层,正面焊接层与顶层基板的顶层焊接层位置相对应且电气连接,背面焊接层与底层基板的底层焊接层位置相对应且电气连接。

14.进一步地,金凸点和硅基芯片的总厚度大于中间基板的厚度。

15.进一步地,金凸点包括基体凸点以及设于基体凸点顶部的植球。

16.本发明还提供了一种硅基芯片的堆叠封装方法,用于制备上述多层基板堆叠的封装体,堆叠封装方法包括如下步骤:

17.步骤1:提供一硅基芯片和顶层基板,将硅基芯片背面与顶层基板进行金硅共晶,在硅基芯片的背面与顶层基板之间形成金硅共晶层,得到第一叠层封装体;

18.步骤2:在硅基芯片正面制作金凸点;

19.步骤3:提供一中间基板,在中间基板上开设通孔,将硅基芯片置于通孔中,中间基板的正面与顶层基板连接形成电气通路,得到第二叠层封装体;

20.步骤4:提供一底层基板,将第二叠层封装体倒装至底层基板上,底层基板与具有金凸点的硅基芯片部分键合形成电气连接,中间基板背面与底层基板连接,得到第三叠层封装体;

21.步骤5:对第三叠层封装体进行灌封,得到多层基板堆叠的封装体。

22.进一步地,步骤3包括如下步骤:

23.步骤31:对硅基芯片和顶层基板整体进行预热;

24.步骤32:提供一中间基板,在中间基板上开设通孔,在中间基板的正面焊接层上放置与正面焊接层外部尺寸一致的焊片;

25.步骤34:将硅基芯片插入通孔中,将中间基板的正面焊接层与顶层基板重合并焊接,使得中间基板正面与顶层基板形成可靠性焊接和电气通路,得到第二叠层封装体。

26.进一步地,步骤4包括如下步骤:

27.步骤41:对第二叠层封装体进行预热;

28.步骤42:在中间基板的背面焊接层放置与背面焊接层外部尺寸一致的焊片;

29.步骤43:将第二叠层封装体倒装至底层基板上,底层基板与具有金凸点的硅基芯片部分键合形成电气连接,中间基板的背面焊接层与底层基板重合并焊接,得到第三叠层封装体。

30.与现有技术相比,本发明至少可实现如下有益效果之一:

31.a)本发明提供的硅基芯片的多层叠层封装体采用三层复合式封装结构,能够实现低成本封装、重复性焊接、标准化器件等功能。

32.b)本发明提供的硅基芯片的多层叠层封装体,一方面,硅基芯片的背面与顶层基板之间在封装过程中形成金硅共晶层,能够促进硅基芯片的背面快速散热,同时,能够提高硅基芯片的背面与顶层基板之间的焊接可靠性;另一方面,在硅基芯片的正面上的芯片栅极、芯片漏极和芯片源极的pad区域分别制作倒装键合的金凸点,金凸点与底层基板直接倒装键合,能够有效提高硅基芯片的功率输出能力和电流承载能力,具有良好的电性能和焊

接性能,还可以有效代替楔形键合带来的金丝长度所占用的体积,有利于实现封装的小型化应用;再一方面,在中间基板开设与硅基芯片尺寸一致的通孔,将硅基芯片封装于中间基板的通孔中,能够对硅基芯片进行位置保护,增加了整个多层基板堆叠的封装体的可靠性。

33.c)本发明提供的硅基芯片的堆叠封装方法中,全过程无钎焊、助焊剂等污染流程,能够更加绿色环保地将硅基芯片组装于电路中。

34.本发明的其他特征和优点将在随后的说明书中阐述,并且,部分的从说明书中变得显而易见,或者通过实施本发明而了解。本发明的目的和其他优点可通过在所写的说明书以及附图中所特别指出的结构来实现和获得。

附图说明

35.附图仅用于示出具体实施例的目的,而并不认为是对本发明的限制,在整个附图中,相同的参考符号表示相同的部件。

36.图1a为本发明实施例一提供的多层基板堆叠的封装体中硅基芯片的正面示意图;

37.图1b为本发明实施例一提供的多层基板堆叠的封装体中硅基芯片的背面示意图;

38.图1c为本发明实施例一提供的多层基板堆叠的封装体中硅基芯片的金凸点示意图;

39.图2a为本发明实施例一提供的多层基板堆叠的封装体中顶层基板的正面示意图;

40.图2b为本发明实施例一提供的多层基板堆叠的封装体中顶层基板的背面示意图;

41.图3a为本发明实施例一提供的多层基板堆叠的封装体中底层基板的正面示意图;

42.图3b为本发明实施例一提供的多层基板堆叠的封装体中底层基板的背面示意图;

43.图4a为本发明实施例一提供的多层基板堆叠的封装体中中间基板的正面示意图;

44.图4b为本发明实施例一提供的多层基板堆叠的封装体中中间基板的背面示意图;

45.图5为本发明实施例一提供的多层基板堆叠的封装体的结构示意图。

46.附图标记:

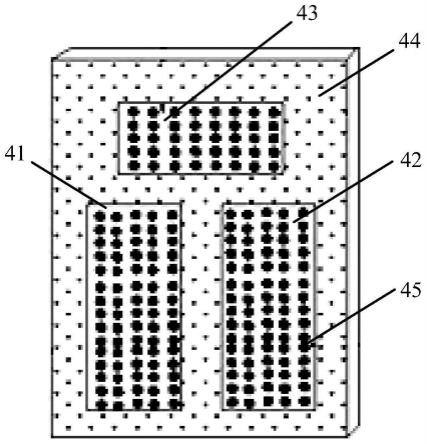

47.1-顶层基板;11-顶层板体;12-顶层焊接层;2-中间基板;21-中间板体;22-正面焊接层;23-背面焊接层;3-底层基板;31-底层板体;32-底层焊接层;33-底层栅极键合区;34-底层漏极键合区;35-底层源极键合区;36-底层栅极;37-底层漏极;38-底层源极;4-硅基芯片;41-芯片栅极;42-芯片漏极;43-芯片源极;44-硅层;45-金凸点;451-基体凸点;452-植球。

具体实施方式

48.下面结合附图来具体描述本发明的优选实施例,其中,附图构成本发明的一部分,并与本发明的实施例一起用于阐释本发明的原理。

49.实施例一

50.本实施例提供了一种硅基芯片的多层基板堆叠的封装体,参见图1a至图5,包括依次层叠的顶层基板1(例如,陶瓷基板)、中间基板2和底层基板3,中间基板2正面与顶层基板1连接形成电气通路,中间基板2上开设贯穿中间基板2正面与背面的通孔,形成通路,通孔尺寸与硅基芯片4的外部尺寸一致,硅基芯片4(例如,大功率硅基三极管裸芯片)置于通孔中,硅基芯片4正面的芯片栅极41、芯片漏极42和芯片源极43上设有金凸点45,硅基芯片4正

面通过金凸点45与底层基板3键合形成电气连接,硅基芯片4背面与顶层基板1之间在封装过程中形成金硅共晶层。

51.与现有技术相比,本发明提供的硅基芯片4的多层叠层封装体采用三层复合式封装结构,能够实现低成本封装、重复性焊接、标准化器件等功能。

52.具体来说,一方面,硅基芯片4的背面与顶层基板1之间在封装过程中形成金硅共晶层,能够促进硅基芯片4的背面快速散热,同时,能够提高硅基芯片4的背面与顶层基板1之间的焊接可靠性;另一方面,在硅基芯片4的正面上的芯片栅极41、芯片漏极42和芯片源极43的pad区域分别制作倒装键合的金凸点45,金凸点45与底层基板3直接倒装键合,能够有效提高硅基芯片4的功率输出能力和电流承载能力,具有良好的电性能和焊接性能,还可以有效代替楔形键合带来的金丝长度所占用的体积,有利于实现封装的小型化应用;再一方面,在中间基板2开设与硅基芯片4尺寸一致的通孔,将硅基芯片4封装于中间基板2的通孔中,能够对硅基芯片4进行位置保护,增加了整个多层基板堆叠的封装体的可靠性。

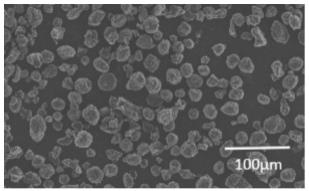

53.对于硅基芯片4,示例性地,参见图1a至图1b,硅基芯片4包括硅层44以及设于硅层44同一表面的芯片栅极41、芯片漏极42和芯片源极43,金凸点45设于芯片栅极41、芯片漏极42和芯片源极43上,需要说明的是,定义硅层44设有芯片栅极41、芯片漏极42和芯片源极43的表面为正面,与正面相对的表面为背面,可以理解的是,硅基芯片4的背面为硅层44。

54.为了实现顶层基板1与硅基芯片4和中间基板2之间的电气连接,对于顶层基板1的结构,参见图2a至图2b,具体来说,其包括顶层板体11、设于顶层板体11正面的正面镀金层、设于顶层共晶面四周的顶层焊接层12以及设于顶层板体11背面的背面散热层,正面镀金层与硅基芯片4的背面之间在封装过程中形成金硅共晶层,其中,正面镀金层和背面散热层均采用全镀金。

55.为了实现底层基板3与中间基板2之间的电气能接,对于底层基板3的结构,参见图3a至图3b,具体来说,包括底层板体31、底层焊接层32、底层栅极36键合区33、底层漏极37键合区34、底层源极38键合区35、底层栅极36、底层漏极37和底层源极38,其中,底层栅极键合区33、底层漏极键合区34、底层源极键合区35设于底层板体31的正面,底层栅极36、底层漏极37和底层源极38设于底层板体31的背面,底层栅极键合区33与底层栅极36连通,底层漏极键合区34与底层漏极37连接,底层源极键合区35与底层源极38连接,对应于芯片栅极41、芯片漏极42和芯片源极43,底层栅极键合区33与芯片栅极41上的金凸点45键合,底层漏极键合区34与芯片漏极42上的金凸点45键合,底层源极键合区35与底层源极38上的金凸点45键合,需要说明的是,底层焊接层32与底层板体31的背面不连通,只作为与中间基板2的焊接层的连接。

56.需要说明的是,中间基板2需要与多个部件进行电气连接,因此,对对于中间基板2的结构,参见图4a至4b,中间基板2的外部尺寸与顶层基板1一致,其包括中间板体21、设于中间板体21正面的正面焊接层22以及设于中间板体21背面的背面焊接层23,正面焊接层22与顶层基板1的顶层焊接层12位置相对应且电气连接,背面焊接层23与底层基板3的底层焊接层32位置相对应且电气连接。

57.值得注意的是,将硅基芯片4置于中间基板2的通孔后,要求硅基芯片4上的金凸点45凸出中间基板2,以实现金凸点45与底层基板3正面的底层焊接层32、底层栅极36、底层漏极37和底层源极38的键合,因此,金凸点45和硅基芯片4的总厚度大于中间基板2的厚度。

58.示例性地,中间基板2的厚度(即中间板体21、正面焊接层22和背面焊接层23的总厚度)为540~560μm(例如,550μm),硅基芯片4与金凸点45的总厚度为570~590μm(例如,580μm),其中,硅基芯片4的厚度为490~510μm(例如,500μm),金凸点45的高度为70~90μm(例如,80μm)。

59.对于金凸点45的结构,具体来说,其为双层结构的金凸点45,参见图1c,包括基体凸点451以及设于基体凸点451顶部的植球452,其中,基体凸点451的高度为45~55μm,植球452的高度为25~35μm,两者叠加形成高度为70~90μm的金凸点45整体。

60.实施例二

61.本实施例提供了一种硅基芯片的堆叠封装方法,包括如下步骤:

62.步骤1:提供一硅基芯片和顶层基板,将硅基芯片背面与顶层基板进行金硅共晶,在硅基芯片的背面与顶层基板之间形成金硅共晶层,得到第一叠层封装体;

63.步骤2:在硅基芯片正面制作金凸点;

64.步骤3:提供一中间基板,在中间基板上开设通孔,将硅基芯片置于通孔中,中间基板的正面与顶层基板连接形成电气通路,得到第二叠层封装体;

65.步骤4:提供一底层基板,将第二叠层封装体倒装至底层基板上,底层基板与具有金凸点的硅基芯片部分键合形成电气连接,中间基板背面与底层基板连接,得到第三叠层封装体;

66.步骤5:对第三叠层封装体进行灌封,得到多层基板堆叠的封装体。

67.与现有技术相比,本实施例提供的硅基芯片的堆叠封装方法与实施例一提供的多层基板堆叠的封装体的有益效果基本相同,在此不一一赘述。

68.此外,在上述硅基芯片的堆叠封装方法中,全过程无钎焊、助焊剂等污染流程,能够更加绿色环保地将硅基芯片组装于电路中。

69.具体来说,对于上述步骤1,其包括如下步骤:

70.步骤11:提供一硅基芯片和顶层基板,将顶层基板放置于365~375℃(例如,370℃)热台上,对顶层基板进行预热;

71.步骤12:将硅基芯片放置于顶层基板上,硅基芯片背面与顶层基板接触;

72.步骤13:采用贴片共晶设备将硅基芯片背面的硅层直接与顶层基板表面的镀金层进行共晶磨合,共晶磨合时间为8~12s(例如,10s),实现金硅共晶工艺,形成金硅共晶层,得到第一叠层封装体。

73.为了能够保证形成的金硅共晶层的质量,上述步骤13之后还包括如下步骤:

74.步骤14:采用x-ray射线仪对第一叠层封装体进行检测空洞率,空洞率要求小于10%。

75.对于上述步骤2,其包括如下步骤:

76.步骤21:将第一叠层封装体放置于球键合机的键合台上,采用球键合机、直径为23~27μm(例如,25μm)的金丝分别在硅基芯片正面的芯片栅极、芯片漏极和芯片源极植上凸点基体;

77.步骤22:在凸点基体上进行植球,得到双层结构的金凸点。

78.对于上述步骤3,其包括如下步骤:

79.步骤31:将硅基芯片正面放置于220~230℃(例如,223℃)热台上,对硅基芯片和

顶层基板整体进行预热;

80.步骤32:提供一中间基板,在中间基板上开设通孔,在中间基板的正面焊接层上放置与正面焊接层外部尺寸一致的焊片(例如,snagcu合金焊片,熔点温度为217℃);

81.步骤34:将硅基芯片插入通孔中,将中间基板的正面焊接层与顶层基板重合并焊接,使得中间基板正面与顶层基板形成可靠性焊接和电气通路,得到第二叠层封装体。

82.对于上述步骤4,其包括如下步骤:

83.步骤41:将第二叠层封装体放置于180~200℃(例如,190℃)热台上,对第二叠层封装体进行预热;

84.步骤42:在中间基板的背面焊接层放置与背面焊接层外部尺寸一致的焊片(例如,sn63pb37合金焊片);

85.步骤43:将第二叠层封装体倒装至底层基板上,底层基板与具有金凸点的硅基芯片部分键合形成电气连接,中间基板的背面焊接层与底层基板重合并焊接,得到第三叠层封装体。

86.需要说明的是,上述步骤3与步骤4中,中间基板的正面焊接层和顶层基板所采用的焊片与中间基板的背面焊接层和底层基板所采用的焊片种类不同,使得中间基板的正面焊接层和顶层基板与中间基板的背面焊接层和底层基板的焊接温度不同。这样,采用温度梯度实现中间基板与顶层基板和底层基板之间的焊接,更有利于多层基板堆叠的封装体的返修。

87.对于上述步骤5,其包括如下步骤:

88.采用聚氨酯液芯片灌封胶对第三叠层封装体进行灌封,灌封位置仅限于顶层基板与底层基板之间,底层基板背面和顶层基板背面不做灌封,得到多层基板堆叠的封装体。

89.对采用上述堆叠封装方法所获的封装体进行各项性能的测试如下:

90.散热性能:对芯片的多层基板堆叠封装体进行建模,加载边界条件进行散热仿真分析,最终得出该大功率硅基三极管芯片在经过多层基板堆叠封装后,工作时顶层基板最高温度为63.4℃,中间层为82.7℃,底层最高温度为68.5℃,相对于芯片单面散热封装,多层基板叠层封装体充分利用芯片正面和背面的散热通道,将芯片产生的热量通过多层基板结构传递到接地面,然后,耗散到印制板或金属墙体或空气环境中,可以降低35%的结壳热阻。

91.电流电压承载能力:本发明中,采用大功率硅基芯片为一种大电流、高电压、大功率的三极管硅基芯片,通过该叠层封装结构可以实现单片最大工作电压60~100v,最大工作电压5~10a,最大输出功率为90~110w。

92.焊接性能:本发明中,对于大功率硅基芯片的多层基板堆叠封装体焊接性能取决于于封装结构和封装工艺。该结构中具有明显的焊接温度梯度,整个封装体分为三层结构,充分保证了每一层的可靠性焊接,封装体可以作为整个器件采用183℃锡铅焊料进行焊接。

93.使用寿命:本发明中,多层基板堆叠封装体设计寿命通常为10年,对该多层堆叠封装体采用有限元分析方法,建立多层堆叠封装体的功率可靠性分析模型,并和实验结果进行校核,基于基板的芯片叠层封装方法的疲劳老化模型,建立叠层基板封装体寿命模型,并分析每一层的不同封装材料、封装结构对封装体寿命的影响规律。为了暴露多层基板堆叠封装体的失效模式,采用了温度冲击、高低温循环、震动等加速老化实验方法,测试表征多

层基板堆叠封装体的寿命。

94.以上所述,仅为本发明较佳的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,可轻易想到的变化或替换,都应涵盖在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。