1.本发明涉及数字集成电路,特别是一种可重复触发数字控制的单稳态触发器。

背景技术:

2.单稳态触发器输出低电平的触发信号,使得单稳态触发器的由稳态转换到暂态。在普通的单稳态触发器电路中,利用电阻-电容电路(resistor-capacitance circuit,rc)充放电,电容和电阻两端的电压逐渐变化,单稳态触发器电路输出端口的与非门,受电压影响超过阀值时,单稳态触发器电路的状态由暂态回到稳态。暂态时间由rc充放电路的时间常数决定,时间常数为电阻值与电容值的乘积。rc充放电路中的电阻、电容一旦选定了,暂态时间便确定了。虽然电路中可采用可调电阻和可调电容,通过旋转电阻电容元件上的调节口改变电阻值电容值,改变时间常数,进而改变暂态时间,但通过旋转调节口的方式调整暂态时间比较粗放,不利于精确控制。

技术实现要素:

3.发明目的:本发明的目的是提供一种可重复触发数字控制的单稳态触发器,从而解决现有技术中单稳态触发器电路中通过旋转调节口的方式调整暂态时间比较粗放,不利于精确控制的技术问题,通过重复触发,可适当延长暂态时间。

4.技术方案:本发明所述的一种可重复触发数字控制的单稳态触发器,包括触发信号输入端、作为输出端的rs触发器的q端;

5.所述可重复触发数字控制电路包括多谐振荡器、计数器、可重复触发控制电路;多谐振荡器电性连接计数器的时钟信号输入端,计数器的进位输出电性连接rs触发器的r输入端;

6.触发信号的输入电性串连接与非门6,rs触发器的s输入端;

7.可重复触发控制电路包括与非门1,jk触发器jk1、jk2和与非门2、与非门3;与非门1电性连接jk触发器jk1的时钟信号输入端,jk触发器jk1的端电性连接jk触发器jk2的时钟信号输入端。

8.所述计数器的进位数值包括二进制、五进制、十进制、十六进制。

9.所述计数器的实现方法包括反馈清零法和反馈置数法。

10.所述单稳态触发器的运行步骤如下:

11.(1)电路启动时,rs触发器置0端相连接的电容电压为0v,rs触发器输出低电平,同时连接计数器的使能端,计数器暂停计数输出低电平;电源通过电阻对电容相进行充电,变为高电平,置0端失效,rs触发器正常工作;

12.(2)计数器的进位端连接rs触发器的r输入端,r=0;触发信号输入端正常高电平,连接与非门6输入端,与非门6输出低电平,连接rs触发器的s输入端,s=0;rs触发器的输入状态为:r=0,s=0,输出保持原状态,维持低电平;

13.(3)触发信号输入信号出现低电平脉冲,与非门6输出高电平脉冲,rs触发器的s输

入端高电平脉冲;r=0,s=1时,rs触发器输出高电平;r=0,s=0时,rs触发器输出保持原状态,维持高电平;

14.(4)rs触发器输出高电平,计数器开始计数;此时单稳态触发器所处状态为暂态;

15.(5)触发信号再次输入信号出现低电平脉冲,与非门6输出高电平脉冲,rs触发器的s输入端高电平脉冲;r=0,s=1时,rs触发器输出高电平;r=0,s=0时,rs触发器输出保持原状态,维持高电平;

16.(6)触发器jk1输出高电平,触发器jk2输出低电平,与非门2输出高电平,与非门3输出低电平脉冲,计数器重新开始计数;此时单稳态触发器所处状态为暂态;

17.(7)触发信号输入信号多次出现低电平脉冲后,与非门3输出低电平脉冲,计数器重新开始计数;触发器jk1和触发器jk2,均输出高电平,与非门2输出低电平,锁定与非门1,限制新的触发;

18.(8)计数器完成预定的计数,进位端输出高电平脉冲,计数器的进位端连接rs触发器的r输入端,r=1,s=0时,rs触发器输出低电平;计数器暂停计数输出低电平,进位端输出低电平,r=0,s=0时,rs触发器输出保持原状态,维持低电平;此时单稳态触发器所处状态为稳态。

19.有益效果:与现有技术相比,本发明具有如下优点:

20.本发明利用可精确控制时间并能够输出高低电平的可重复触发数字控制电路来替代传统rc电路,可重复触发数字控制电路包括计数器、多谐振荡器、rs触发器,可重复触发控制电路。计数器的使能端与单稳态触发器的输出端连接,时钟信号输入端与多谐振荡器连接,进位端rs触发器的r输入端。利用多谐振荡器产生的矩形波作为计数器的时钟输入,利用计数器预设定的进位数值可对时钟信号分频,输出不同时间长度的脉冲信号,rs触发器响应于脉冲信号发生翻转,输入信号出现低电平脉冲时,单稳态触发器输出端的输出高电平,计数器开始工作,如果发生了再次触发,可重复触发控制电路,输出低电平脉冲,计数器清零并重新计数,触发信号输入信号多次出现低电平脉冲后,计数器清零并重新计数,与非门2输出低电平,锁定与非门1,限制新的触发。

21.完成预定的计数输出高电平脉冲,单稳态触发器输出端的输出低电平,便可使得单稳态触发器在暂态与稳态之间发生转换。基于本发明单稳态触发器及其控制方法,通过设置计数器的进位数值可精确控制矩形波的脉冲时间,从而能够精确控制单稳态触发器的暂态时间,通过重复触发,可适当延长暂态时间。

附图说明

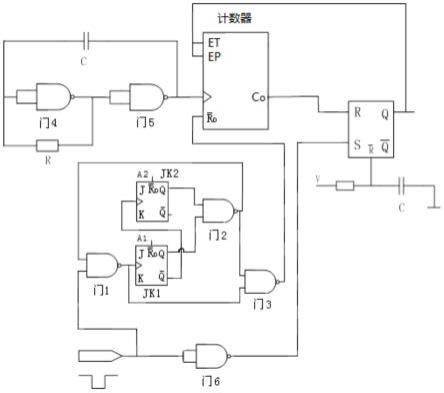

22.图1为本发明单稳态触发器实施例的电路图;

23.图2为一种传统单稳态触发器的电路图。

具体实施方式

24.下面结合附图对本发明的技术方案作进一步说明。

25.目前,单稳态触发器按照电路形式可以分为门电路组成的单稳态触发器,msi集成单稳态触发器和用555定时器组成的单稳态触发器,用cmos门电路组成的单稳态触发器分正脉冲触发和负脉冲触发。常见的一种简单的单稳态触发器电路,如图2所示,是本发明实

施例中提及的一种传统单稳态触发器的电路图,由与非门1、电容、电阻和与非门2组成,其基本工作过程如下:当没有触发信号时,该电路处于稳态,输出低电平。当有低电平触发信号输入到与非门1时,与非门1输出高电平,电容两端电压不能跃变;此时,与非门2的输入端电压变成高电平,输出低电平,同时输出电压反馈到与非门1输入端,维持与非门1输出高电平;随着电容的充电,电容两端电压按指数规律上升,与非门2的输入端电压同时下降,当电压低于与非门2的阀值,与非门2的输出回到高电平的稳态,同时反馈到与非门1输入端,与非门1输出低电平。该电路中,利用rc充放电路以确定暂态时间,这个方式存在暂态时间短和暂态时间调节困难的技术缺陷。

26.如图1所示,针对上述技术问题和缺陷,本发明提出了一种可重复触发数字控制的单稳态触发器,包括触发信号输入端、作为输出端的rs触发器的q端;所述可重复触发数字控制电路包括多谐振荡器、计数器、可重复触发控制电路;多谐振荡器电性连接计数器的时钟信号输入端,计数器的进位输出电性连接rs触发器的r输入端;触发信号的输入电性串连接与非门6,rs触发器的s输入端;可重复触发控制电路包括与非门1,jk触发器jk1、jk2和与非门2、与非门3;与非门1电性连接jk触发器jk1的时钟信号输入端,jk触发器jk1的端电性连接jk触发器jk2的时钟信号输入端。

27.本发明所述的一种可重复触发数字控制的单稳态触发器的运行步骤如下:

28.(1)电路启动时,rs触发器置0端相连接的电容电压为0v,rs触发器输出低电平,同时连接计数器的使能端,计数器暂停计数输出低电平;电源通过电阻对电容相进行充电,变为高电平,置0端失效,rs触发器正常工作;

29.(2)计数器的进位端连接rs触发器的r输入端,r=0;触发信号输入端正常高电平,连接与非门6输入端,与非门6输出低电平,连接rs触发器的s输入端,s=0;rs触发器的输入状态为:r=0,s=0,输出保持原状态,维持低电平;

30.(3)触发信号输入信号出现低电平脉冲,与非门6输出高电平脉冲,rs触发器的s输入端高电平脉冲;r=0,s=1时,rs触发器输出高电平;r=0,s=0时,rs触发器输出保持原状态,维持高电平;

31.(4)rs触发器输出高电平,计数器开始计数;此时单稳态触发器所处状态为暂态;

32.(5)触发信号再次输入信号出现低电平脉冲,与非门6输出高电平脉冲,rs触发器的s输入端高电平脉冲;r=0,s=1时,rs触发器输出高电平;r=0,s=0时,rs触发器输出保持原状态,维持高电平;

33.(6)触发器jk1输出高电平,触发器jk2输出低电平,与非门2输出高电平,与非门3输出低电平脉冲,计数器重新开始计数;此时单稳态触发器所处状态为暂态;

34.(7)触发信号输入信号多次出现低电平脉冲后,与非门3输出低电平脉冲,计数器重新开始计数;触发器jk1和触发器jk2,均输出高电平,与非门2输出低电平,锁定与非门1,限制新的触发;

35.(8)计数器完成预定的计数,进位端输出高电平脉冲,计数器的进位端连接rs触发器的r输入端,r=1,s=0时,rs触发器输出低电平;计数器暂停计数输出低电平,进位端输出低电平,r=0,s=0时,rs触发器输出保持原状态,维持低电平;此时单稳态触发器所处状态为稳态。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。