1.本技术涉及半导体技术领域,尤其涉及一种曲率芯片、封装及终端设备。

技术背景

2.随着半导体技术的发展,芯片体积一路向着"轻、薄、小"的方向发展,将更多功能、更强功效集成于狭小空间,但是,在追求小的前提下,对芯片功效与功耗的不断要求,进而提升制程设备精度及工艺,导致即将面临“量子隧穿效应”成为本领域科学家研究的主题。如我国的华为就在2019800998428和2019801009413提出的"芯片堆叠"封装,其中之一目的在于同一制程设备制作高效芯片(扩充库容),其创造性缺陷在于:1)丧失芯片纵向的"薄",2)即使横向交错堆叠,均未逃离芯片"追求投影面面积小"的思维束缚。

3.尤其,当今芯片发展存在:1)soc集成芯片、3d堆叠集成芯片技术应用面临晶体管电路库容有限;2)sip、sop集合芯片内置无源器件空间不足;3)system board系统更是难以集成于芯片狭小空间;4)“3d堆叠集成芯片”也是由于库容体积过小,导致多层叠加过程更多运用tsv通孔,造成技术难度和成本的上升,因此,问题均集中于芯片库容的如何逾越。

4.本技术基于屏幕或电池的投影面积,对芯片库容、散热和量子隧穿效应问题的同时克服,颠覆性的提出芯片"轻、薄、大"的发展方向,实现换道超车及倍数级的逾越,推动芯片发展。

5.所述"大"可行性分析,基于以通用尺寸150mmx80mm=12000mm

²

手机屏为例,芯片投影面积13.5mmx8.5mm=115mm

²

,12000mm

²÷

115

²

=105,同手机屏幕大小的芯片,其搭建一层晶体管电路,即等同于105层(公开数据传统芯片60层)传统芯片晶体管库容,因此,每增加一层,即库容增加1.5倍。

6.综上所述,芯片的超级放大、极剧减薄,在不丧失功效的前提下还得以倍数级的提升,还为低性能设备造出高性能芯片实现可能,更是为未来设备的超薄奠定了坚实的基础。

技术实现要素:

7.本技术提供一种曲率芯片、封装及终端设备,能够在保证供电需求的同时还保证具合理安装空间,解决库容扩容和增加芯片散热面积,更是解决同一制程设备(x纳米)制作芯片颠覆式的提升功效和降低功耗,尤其功效超越更高制程设备一代或两代甚至三代制作的芯片功效,阶段性的克服量子隧穿效应的延后面临。

8.第一方面,本技术提供一种曲率芯片包括:一种曲率芯片,包括衬低经光刻设备及工艺、刻蚀设备及工艺、覆膜沉积设备及工艺制程制作的:数字电路芯片、模拟电路芯片、存储电路芯片以及硅光集成芯片任一裸片及封装,其特征在于,(一)数字电路芯片、模拟电路芯片、存储电路芯片以及硅光集成芯片任一裸片的扩容;(二)数字电路芯片、模拟电路芯片、存储电路芯片以及硅光集成芯片任一裸片散热面的增加;(三)所述数字电路芯片、模拟电路芯片、存储电路芯片或硅光集成芯片任一裸片的包裹或涂装介电材料,(四)介电封装后的芯片投影面曲率呈0

°

或大于0

°

的曲率芯片;其引出引入电路端设置于裸片的投影面、

投影面相背面、投影相邻的端面至少之一;所述曲率芯片还包括与其投影面相邻的两个相对端面呈v形折叠、s 形折叠、波浪线折叠、阿基米德螺线任一形态,其引脚设置于投影面、投影面相背面、投影相邻的端面至少之一。

9.所述库容和散热面的增加基于数字电路芯片、模拟电路芯片、存储电路芯片、硅光集成芯片任一的投影面面积最小大于18mmx13.5mm,最大小于应用设备的屏幕面积之间取值,厚度基于毫米级、微米级或纳米级尺寸。

10.所述投影面面积18mmx13.5mm尺寸是基于1)公开,2)芯片尺寸面积以及未有本技术领域人员提出,芯片面积基于屏幕投影面积设计方案,而不涉及通用芯片尺寸确定的下限设计面积。

11.所述毫米级、微米级或纳米级厚度基于通用芯片毫米级,以及ibm公开的14纳米柔性晶圆及公开的2纳米制程工艺及介电喷涂下限制定的最薄厚度纳米级,再由毫米级与纳米级之间取微米级厚度值。

12.所述曲率芯片大于0

°

的状态包括:封装后的静态状态、封装后曲率呈0

°

受外力作用下的状态。

13.所述芯片制程至少包括:晶圆涂膜、晶圆光刻显影、蚀刻、掺加杂质、晶圆测试、裸片测试、标注、粘膜、切割、键合封装基板的放大电路、键合引脚、封装介电材料、包装芯片。

14.所述数字电路芯片包括:逻辑电路、通用处理器、存储器、单片系统、微控制器、定制电路、可编程逻辑器件。

15.所述厚度值的取值依据设计库容需要体积除以曲率芯片投影面积取值裸片厚度、介电包裹层厚度确定高度。

16.所述模拟电路芯片包括:处理声音、光线、温度、感知而集成的数字处理信号芯片和电源控制芯片,以及射频芯片和内存接口芯片。

17.所述存储电路芯片包括:闪存和内存;所述闪存至少包括nand flash和nor flash;所述内存至少包括dram。

18.所述放大电路至少包括扩大裸片引出引入电路端的面积或体积,提升微球焊键合或引脚键合的可操控性。

19.所述衬低或者还包括与衬低位置相对的顶层增设衬低。

20.所述引脚至少包括凸点、金属柱、焊球、导爪或导线。

21.所述衬低材料包括硅基、碳基、锗基、镓基或铟基任一半导体独片或卷材晶圆。

22.所述光子芯片至少包括:硅光集成芯片和cmos存储芯片,或者,硅光集成芯片、cmos存储芯片和模拟电路芯片。

23.所述硅光集成芯片至少包括:激光器、电光调制器、光电探测器、光衰减器、光复用/解复用器以及光放大器。

24.所述厚度基于毫米级、微米级或纳米级的尺寸取值依据包括:依据设计库容所需体积

÷

投影面积+介电封装厚度=曲率0

°

芯片厚度值。

25.所述曲率芯片至少包括soc集成芯片、sip集合芯片、sop集合芯片任一架构;所述曲率0

°

芯片投影面积还包括:所述曲率芯片的投影面积大于应用设备的屏幕面积时,应用卷曲、折叠至少之一方案安装。

26.所述卷曲、折叠方案应用还包括曲率芯片的收纳包装之一方案。

27.所述衬低材质包括还包括碳化硅、砷化镓、氮化嫁、磷化铟半导体。

28.所述曲率芯片还包括除设引脚的面,剩余至少一个面粘接散热片。

29.第二方面,本技术提供一种曲率芯片的封装,包括应用soc集成芯片、3d堆叠集成芯片、sip集合芯片、sop集合芯片任一方案架构的数字电路芯片裸片、模拟电路芯片裸片、存储电路芯片裸片、硅光集成芯片裸片至少一个面填充介电材料实现封装,其特征在于,(一)数字电路芯片、模拟电路芯片、存储电路芯片以及硅光集成芯片任一裸片的扩容。

30.(二)数字电路芯片、模拟电路芯片、存储电路芯片以及硅光集成芯片任一裸片散热面的增加。

31.(三)所述数字电路芯片、模拟电路芯片、存储电路芯片或硅光集成芯片任一裸片的涂装介电材料。

[0032] (四)介电封装后的曲率芯片投影面的曲率呈0

°

或大于0

°

的曲率芯片;其引出引入电路端设置于裸片的投影面、投影面相背面、投影相邻的端面至少之一。

[0033]

所述曲率芯片还包括与其投影面相邻的两个相对端面呈v形折叠、s 形折叠、波浪线折叠、阿基米德螺线任一形态,其连接引出引入电路端子的引脚设置于芯片裸片的投影面、投影面相背面、投影相邻的端面至少之一。

[0034]

所述库容和散热面的增加基于数字电路芯片、模拟电路芯片、存储电路芯片、硅光集成芯片任一的投影面面积最小大于18mmx13.5mm,最大小于应用设备的屏幕面积,厚度基于毫米级、微米级或纳米级尺寸。

[0035]

所述光子芯片至少包括:硅光集成芯片和cmos存储芯片,或者,硅光集成芯片、cmos存储芯片和模拟电路芯片。

[0036]

所述填充介电材料工艺至少包括:dip双列直插式、qfp塑料方型扁平式、pfp塑料扁平组件式pga插针网格阵列、bga球栅阵列、csp芯片尺寸。

[0037]

所述涂装介电材料工艺至少包括:喷涂、滴涂、刷涂、滚涂、覆膜。

[0038]

所述曲率芯片的架构或者还包括与衬低位置相对的顶层增设衬低。

[0039]

所述填充介电材料至少包括:塑料、树脂、玻璃、陶瓷。

[0040]

所述引脚设置位置包括曲率芯片的投影面与其相背的底面或相邻的端面至少之一;所述引脚至少包括凸点、微球、金属柱、焊球、导爪或导线;所述曲率芯片的裸片介电封装方案还包括在常压、常温至少之一环境中喷涂、滚涂、刷涂、覆膜、粘膜一种或多种的工序组合;或者,在常压、常温至少之一环境中喷涂、滚涂、刷涂、覆膜、粘膜一种或多种的工序组合,再进入压力空间、加温空间至少之一进行介电材料填充优化;或者,在高压、高温至少之一环境中喷涂、滚涂、刷涂、覆膜、粘膜一种或多种的工序组合。

[0041]

所述填充介电材料至少包括:塑料、树脂、玻璃、陶瓷。

[0042]

所述曲率芯片的架构或者还包括与衬低位置相对的顶层增设衬低。

[0043]

所述曲率芯片所涉:soc集成芯片、3d堆叠集成芯片、sip集合芯片、sop集合芯片任一封装方案架构还包括:植入承载无源器件的基板和无源器件,或者,嵌入无源器件的基板;所述封装基板材料包括玻璃、陶瓷、塑料、亚克力、树脂、半导体一种或多种的合成物片材或卷材;所述无源器件至少包括电阻,电容,电感,转换器,渐变器,匹配网络,谐振器,滤波器,混频器和开关。

[0044]

所述厚度基于毫米级、微米级或纳米级的尺寸取值依据包括:依据设计库容所需体积

÷

投影面积+介电封装厚度=曲率0

°

芯片厚度值。

[0045]

所述曲率芯片的封装还包括soc集成芯片、sip集合芯片、sop集合芯片任一的裸片植入system board系统。

[0046]

所述曲率芯片的封装还包括soc集成芯片、sip集合芯片、sop集合芯片任一的裸片与system board系统裸片堆叠封装。

[0047]

所述曲率芯片的封装还包括sip集合芯片裸片、sop集合芯片裸片至少两片堆叠封装。

[0048]

所述堆叠至少包括数字电路芯片、模拟电路芯片、存储电路芯片以及硅光集成芯片任意组合至少两个叠加。

[0049]

所述堆叠至少包括逻辑电路、通用处理器、存储器、单片系统、微控制器、定制电路、可编程逻辑器件、声音感知处理器、光线感知处理器、温度感知处理器、电源控制芯片、射频芯片、nand flash芯片、nor flash、dram任意组合至少两个叠加。

[0050]

所述堆叠包括纵向和横向至少之一有序或无序阵列;所述纵向堆叠形态至少包括:柱形、金字塔形、悬臂形、至少一排并肩形、至少一排上下勾连形。

[0051]

所述堆叠封装还包括tsv穿孔植入导体或走线结构,电路经tsv穿孔使相邻或相近的至少两个裸片电路导通,或者,顶层芯片与底部的rdl的连接。

[0052]

所述连接至少包括混合键合、表面活化键合或原子扩散键合。

[0053]

所述堆叠封装包括至少两个芯片、至少一个芯片和至少一个裸片、至少两个裸片任意有序或无序阵列,对其周围填充介电材料,顶层芯片与底部的扇出型布线层连接,保证顶层芯片供电;如底层芯片遮挡顶层芯片局部区域,通过铜柱和底部的rdl连接难以满足顶层芯片引出引入电路设置,对其下层芯片应用硅通孔方案,实现顶层芯片与底部的rdl的有效连接。

[0054]

所述tsv穿孔工艺至少包括:激光钻孔、刻蚀工艺制作的盲孔或通孔。

[0055]

所述tsv填充工艺包括:微凸点、铜柱、金丝、焊球、可控坍塌芯片连接结构中的一种或多种的组合。

[0056]

所述通孔填充包括:晶圆制程晶体管电路之前或晶体管电路制程之后填充。

[0057]

所述曲率芯片的封装还包括倒装焊。

[0058]

所述倒装焊工艺至少包括:倒装芯片焊接的工艺方法主要有热压焊法、再流焊法、环氧树脂光固化法和各向异性导电胶黏接法。

[0059]

所述曲率芯片还包括除设引脚的面,剩余至少一个面粘接散热片。

[0060]

第三方面,本技术提供曲率芯片的制备及封装包括下列所述任一工艺流程的其中一段:soc曲率芯片工艺流程(一)衬低制备~晶体管电路搭建~打磨衬低~焊接封装基板~键合放大电路~键合引脚~检测电路~封装介电材料~刻蚀或印刷标注~分切芯片~独立封装。

[0061]

soc曲率芯片工艺流程(二)衬低制备~晶体管电路搭建~打磨衬低~键合放大电路~键合引脚~检测电路~封装介电材料~刻蚀或印刷标注~分切芯片~独立封装。

[0062]

soc曲率芯片工艺流程(三)衬低制备~晶体管电路搭建~刻蚀放大电路~键合引脚~检测电路~封装介电材料~刻蚀或印刷标注~分切芯片~独立封装。

[0063]

soc曲率芯片工艺流程(四)衬低制备~晶体管电路搭建~刻蚀放大电路~打磨衬低~键合引脚~检测电路~封装介电材料~刻蚀或印刷标注~分切芯片~独立封装。

[0064]

soc曲率芯片工艺流程(五)衬低制备~晶体管电路搭建~焊接封装基板~键合放大电路~键合引脚~检测电路~封装介电材料~刻蚀或印刷标注~分切芯片~独立封装。

[0065]

sip封装曲率芯片工艺流程(一)衬低制备~晶体管电路搭建~焊接内置无源器件的封装基板~键合放大电路~键合引脚~检测电路~封装介电材料~刻蚀或印刷标注~分切芯片~独立封装。

[0066]

sop曲率芯片工艺流程(一)衬低制备~晶体管电路搭建~焊接外设无源器件的封装基板~键合放大电路~键合引脚~检测电路~封装介电材料~刻蚀或印刷标注~分切芯片~独立封装。

[0067]

3d堆叠曲率芯片工艺流程(一)衬低制备~tsv开盲孔~植入线路~晶体管电路搭建~打磨衬低~键合放大电路~键合引脚~封装介电材料~检测电路~刻蚀或印刷标注~分切芯片―独立包装。

[0068]

3d堆叠曲率芯片工艺流程(二)衬低制备~tsv开通孔~植入线路~晶体管电路搭建~键合放大电路~键合引脚~封装介电材料~检测电路~刻蚀或印刷标注~分切芯片―独立包装。

[0069]

3d堆叠曲率芯片工艺流程(三)衬低制备~tsv开盲孔~晶体管电路搭建~打磨衬低~植入线路~键合放大电路~键合引脚~封装介电材料~检测电路~刻蚀或印刷标注~分切芯片―独立包装。

[0070]

3d堆叠曲率芯片工艺流程(四)衬低制备~tsv开通孔~晶体管电路搭建~植入线路~键合放大电路~键合引脚~封装介电材料~检测电路~刻蚀或印刷标注~分切芯片―独立包装。

[0071]

所述晶体管电路搭建包括光刻设备及刻蚀设备;或者,原子或离子打印机打印。

[0072]

所述晶体管电路搭建制备还包括原子或离子打印晶体管电路:工艺流程(一)基于衬低打印晶体管电路~填充介电材料~打磨显露引入引出电路端~再基于引入引出电路端打印晶体管电路~再打磨~键合放大电路~键合引脚~封装介电材料~检测电路~刻蚀或印刷标注~分切芯片―独立包装;打印晶体管电路工艺流程。

[0073]

工艺流程(二)包括基于衬低打印晶体管电路~填充介电材料~打磨显露引入引出电路端~再基于引入引出电路端打印晶体管电路~再打磨~打印引出引入端放大电路~键合引脚~封装介电材料~检测电路~刻蚀或印刷标注~分切芯片―独立包装。

[0074]

所述终端设备,包括对讲机、夜视仪、手机、平板电脑、电脑、武器载电脑、机载电脑、设备应用、笔记本、车载电脑、智能手表、智能手环的应用,其特征在于,终端设备的应用,包括曲率芯片引出引入电路端与屏幕引出引入电路端键合;或者,曲率芯片引出引入电路端与主板引出引入电路端键合;或者,曲率芯片引出引入电路端与电池引出引入电路端键合或触接;或者,屏幕引出引入电路端与曲率芯片引出引入电路端一端键合、曲率芯片引出引入电路端另一端与主板引出引入电路端键合、主板引出引入电路端与电池引出引入电路端键合或触接;或者,屏幕引出引入电路端与曲率芯片引出引入电路端一端键合、曲率芯片引出引入电路端另一端与电池引出引入电路端键合或触接;或者,屏幕引出引入电路端与主板引出引入电路端键合、主板引出引入电路端与电池引出引入电路端键合或触接。

[0075]

所述终端设备至少包括民用和军用电子设备。

附图说明

[0076]

为了更清楚地说明本技术实施例或

背景技术:

中的技术方案,下面将对本技术实施例或背景技术中所需要使用的附图进行说明。

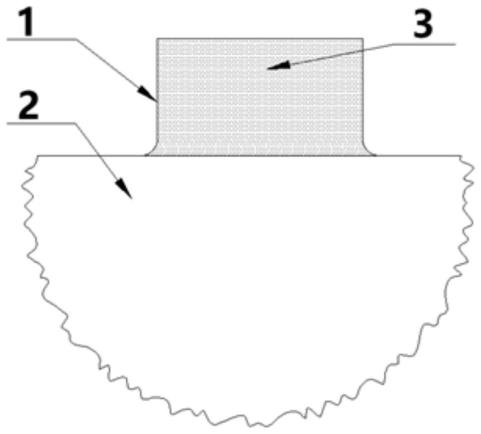

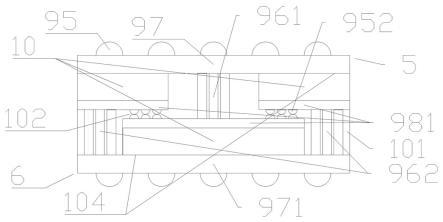

[0077]

图1为本技术soc曲率芯片其中之一方案3d堆叠集成曲率0

°

的其中之一结构展示示意图;图2为本技术soc曲率芯片其中之一方案3d堆叠集成曲率0

°

的塔式叠加其中之一结构展示示意图;图3为本技术soc曲率芯片其中之一方案3d堆叠集成曲率0

°

增加基板的其中之一结构展示示意图;图4为本技术sip集合曲率芯片双面设引脚及tsv穿孔其中之一方案曲率0

°

结构示意图;图5为本技术sop集合曲率芯片双面设引脚及tsv穿孔其中之一方案曲率0

°

结构示意图;图6为本技术sop集合曲率芯片同向双设引脚其中之一方案曲率0

°

结构示意图;图7为3d堆叠集成曲率芯片、sop集合曲率芯片、sip集合曲率芯片任一基于阿基米德螺线收纳的曲率芯片其中之一结构展示示意图;图8为3d堆叠集成曲率芯片、sop集合曲率芯片、sip集合曲率芯片任一基于大于0

°

曲率的其中之一结构展示示意图。

[0078]

其中:1、数字电路芯片,2、模拟电路芯片,3、存储电路芯片,4、硅光集成芯片,5、soc集成芯片,6、3d堆叠集成芯片,7、sip集合芯片,8、sop集合芯片,9、投影面,901、投影面相背面,902、投影相邻的端面,903、投影相邻的端面,91、高度,92、无源器件,93、衬低,94、晶体管电路,95、引脚,951、引线,952、焊球,96、tsv穿孔,961、互连架构,962、互连架构,97、走线架构层rdl,971、走线架构层rdl,98、有源面,981、有源面,982、交叠区,983、非交叠区,10、晶体管电路集成模块,101、介电材料,102、键合层,103、基板,104、粘接层。

具体实施方式

[0079]

除非另作定义,本技术使用的技术术语或者科学术语应当为本领域技术人员所理解的通常意义。在本技术实施例的描述中,除非另有说明,“多个”的含义是两个或两个以上,至少之一或至少一个含义是包括其中任意一个、任意两个或两个以上;厚度等同于高度;所述投影面方位术语是相对于侧视附图中芯片放置其顶面的定义,所述级表示一定的取值范围,尤其投影面方向性术语是相对的概念,它用于相对于的描述和澄清,其可以根据芯片放置的方位的变化而相应地发生变化。

[0080]

下面结合本技术实施例中的附图对本技术实施例进行描述。以下描述中,参考形成本技术一部分并以说明之方式示出本技术实施例的具体方面或可使用本技术实施例的具体方面的附图。应理解,本技术实施例可在其它方面中使用,并可包括附图中未描绘的结构或逻辑变化。因此,以下详细描述不应以限制性的意义来理解,且本技术的范围由所附权利要求书界定。另外,还应理解的是,除非另外明确提出,本文中所描述的各示例性实施例

和/或方面的特征可以相互组合。

[0081]

本技术一些实施例提供一种终端设备。该终端设备可以为对讲机、夜视仪、手机、平板电脑、电脑、武器载电脑、机载电脑、设备应用、笔记本、车载电脑、智能手表、智能手环等电子产品。本技术实施例对上述终端设备的具体形式不做特殊限制。

[0082]

上述终端设备中包括芯片堆叠封装,该芯片堆叠封装通过连接件与终端设备中其他相关电子器件连接。例如,芯片堆叠封装可以通过连接件与终端设备中的电路板连接。

[0083]

所述实施例均基于芯片制程搭建的晶体管、电路首先一层、再两层、然后三层渐进依据库容需要叠加。

[0084]

本技术曲率芯片的封装方案一:裸片未封装前,对裸片电路引入端及引出端由互连架构与封装基板键合、再对封装基板引出和引入端焊接引脚、将完成的芯片基础模块在除引脚均通过包裹或涂装工艺封装介电材料,然后通过物理、化学至少之一工艺,清除引脚介电材料。

[0085]

本技术曲率芯片的封装方案二:裸片未封装前,对裸片电路引入端及引出端由互连架构与引脚键合、将完成的芯片基础模块在除引脚均通过包裹或涂装工艺封装介电材料,然后通过物理、化学至少之一工艺,清除引脚介电材料。

[0086]

本技术曲率芯片的封装方案三:对其方案一和方案二封装介电材料之前对引脚涂装介电材料脱离剂,再封装(填充)介电材料,然后经物理、化学至少之一工艺,清除引脚脱离剂,或者依托其脱离剂导电性对其保留。

[0087]

本技术曲率芯片3d堆叠方案的封装方案四:衬低搭建晶体管电路之前,或衬低打磨之前或之后设置tsv通孔,衬低经光刻机、刻蚀设备及工艺、覆膜设备、制程搭建晶体管及晶体管控制、连接电路,其中引出和引入端与tsv通孔植入导体对应且形成互连架构焊接引脚或键合焊球。

[0088]

本技术曲率芯片3d堆叠方案的封装方案五:衬低搭建晶体管电路之前,或衬低打磨之前或之后设置tsv盲孔,衬低经光刻机、刻蚀设备及工艺、覆膜设备、制程搭建晶体管及晶体管控制连接电路、打磨衬低漏出tsv通孔、tsv通孔植入导体、构焊接引脚或键合焊球形成互连架构。

[0089]

本技术曲率芯片的封装方案六:所述方案一、二、三、四任一所涉衬低搭建晶体管及电路集成,包括soc集成芯片电路搭建方案、soc集成芯片集成system board系统;或者,sip集合芯片、sop集合芯片植入system board系统;或者,soc集成芯片、sip集合芯片、sop集合芯片集成无源器件,尤其集成电容;所述集成电容为片状或集成于芯片的功能区块;所述无源器件至少包括电阻、电容、电感、转换器、渐变器、匹配网络、谐振器、滤波器、混频器和开关。

[0090]

本技术曲率芯片的封装方案七:所述方案一、二、三、四、五任一所涉衬低还包括衬低打磨工序,减小其厚度。

[0091]

本技术曲率芯片的封装方案八:所述方案一、二、三、四、五任一还包括增设封装基板。

[0092]

本技术曲率芯片的封装方案九:所述方案一、二、三、四、五任一对介电填充尤其包括涂装方案。

[0093]

本技术曲率芯片的封装方案十:所述方案九涂装环境至少包括常温常压、高压高

温、常温高压、高温常压至少之一密闭、无尘制作。

[0094]

本技术曲率芯片的封装方案十一:上述本技术曲率芯片的封装方案所涉衬低搭建集成电路模块至少搭建,逻辑模块、计算模块、存储模块、通信模块、感知模块和电源供给模块至少之一,再封装介电材料。

[0095]

本技术曲率芯片的封装方案十二:本技术曲率芯片包括逻辑曲率芯片、计算曲率芯片、存储曲率芯片、通信曲率芯片、感知曲率芯片和电源曲率芯片。

[0096]

本技术曲率芯片的封装方案十三:本技术曲率芯片引脚设置位置包括投影面;或者,投影面和投影面相背的面;或者,投影面和投影面相邻端面;或者,投影面相邻端面;所涉引脚个数、引脚的连接、引脚形状、引脚的设置位置均依据设计需要和实际情况,应用本技术公开方案,或者,本技术领域技术人员公知方案实施。

[0097]

本技术曲率芯片的封装方案十四:本技术所涉硅基、碳基、锗基、镓基或铟基芯片,光子芯片涉及的电路搭建方案与制备,本技术领域技术人员公知方案。

[0098]

本技术曲率芯片的封装方案十五:所述曲率芯片还包括除设引脚的面,其余至少之一面键合或粘接散热片。

[0099]

本技术曲率芯片的封装方案十六:所述引脚设双路时还包括:曲率芯片一路引脚与屏幕键合,另一路与主板或电池键合。

[0100]

在上述实施例表述可互相参照、可重组、绝不是对发明范围的限定,尤其对工序或功能的增加或删减均属本技术涉及范畴。

[0101]

而本实施例与附图用于阐述本技术所述结构的可行性和例举功能,不对发明的范围进行限制。

[0102]

基于"现行芯片投影面积的增大"、"芯片曲率大于0

°

"至少之一创新,对其所涉电路构建、制程设备及工艺、封装、工艺方法或顺序实现芯片或裸片库容的提升,以及功效、功耗至少之一的改善,亦在本发明保护范围之内。

[0103]

由于各实施例的表述各有侧重,某个实施例中没有细述的部分,其它实施例的侧重可引入阐述。

[0104]

本技术在上述部分实施例中所讨论的工艺步骤,仅仅是一些优选实现方法,以上所述,仅为本技术的具体实施方式,但本技术的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本技术揭露的技术范围内,可轻易想到变化或替换,都应涵盖在本技术的保护范围之内。

[0105]

因此,本技术的保护范围应以所述权利要求的保护范围为准。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。