技术特征:

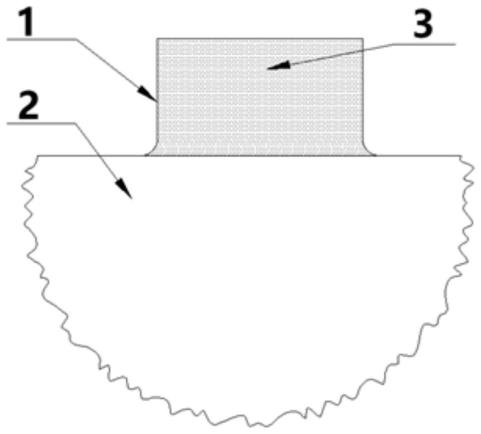

1.一种曲率芯片,包括衬低经光刻设备及工艺、刻蚀设备及工艺、覆膜沉积设备及工艺制程制作的:数字电路芯片、模拟电路芯片、存储电路芯片以及硅光集成芯片任一裸片及封装,其特征在于,数字电路芯片、模拟电路芯片、存储电路芯片以及硅光集成芯片任一裸片的扩容、增加散热面、包裹或涂装介电材料、封装后的芯片投影面的曲率呈0

°

或大于0

°

的曲率芯片;其引出引入电路端设置于裸片的投影面、投影面相背面、投影相邻的端面至少之一;所述曲率芯片还包括与其投影面相邻的两个相对端面呈v形折叠、s 形折叠、波浪线折叠、阿基米德螺线任一形态,其连接引出引入电路端的引脚设置于曲率芯片投影面、投影面相背的面、投影面相邻的端面至少之一面;所述库容和散热面的增加基于数字电路芯片、模拟电路芯片、存储电路芯片、硅光集成芯片任一的投影面面积最小大于18mmx13.5mm,最大小于应用设备的屏幕面积之间取值,厚度基于毫米级、微米级或纳米级尺寸;所述曲率芯片大于0

°

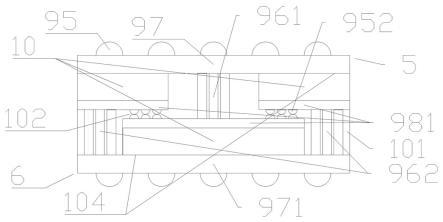

的状态包括:封装后的静态状态、封装后曲率呈0

°

受外力作用下的状态,所述芯片制程至少包括:晶圆涂膜、晶圆光刻显影、蚀刻、掺加杂质、晶圆测试、裸片测试、标注、粘膜、切割、键合封装基板的放大电路、键合引脚、封装介电材料、包装芯片;所述数字电路芯片包括:逻辑电路、通用处理器、存储器、单片系统、微控制器、定制电路、可编程逻辑器件;所述模拟电路芯片包括:处理声音、光线、温度、感知而集成的数字处理信号芯片和电源控制芯片,以及射频芯片和内存接口芯片;所述存储电路芯片包括:闪存和内存;所述闪存至少包括nand flash和nor flash;所述内存至少包括dram;所述放大电路至少包括扩大裸片引出引入电路端的面积或体积,提升微球焊键合或引脚键合的可操控性;所述衬低或者还包括与衬低位置相对的顶层增设衬低。2.如权利要求1所述曲率芯片,其特征在于;所述引脚设置位置包括曲率0

°

芯片的投影面与其相背的底面或相邻的侧面至少之一;所述引脚至少包括凸点、金属柱、焊球、导爪或导线;所述衬低材料包括硅基、碳基、锗基、镓基或铟基任一半导体独片或卷材晶圆;所述光子芯片至少包括:硅光集成芯片和cmos存储芯片,或者,硅光集成芯片、cmos存储芯片和模拟电路芯片;所述硅光集成芯片至少包括:激光器、电光调制器、光电探测器、光衰减器、光复用/解复用器以及光放大器;所述厚度基于毫米级、微米级或纳米级的尺寸取值依据包括:依据设计库容所需体积

÷

投影面积+介电封装厚度=曲率0

°

芯片厚度值。3.如权利要求1、2任一所述曲率芯片,其特征在于;所述曲率芯片至少包括soc集成芯片、sip集合芯片、sop集合芯片任一架构;所述曲率芯片投影面还包括:曲率芯片的投影面积大于应用设备的屏幕面积,应用卷曲、折叠至少之一方案安装;所述卷曲、折叠方案应用还包括曲率芯片的收纳包装;所述衬低材质包括还包括碳化硅、砷化镓、氮化嫁、磷化铟半导体;所述曲率芯片还包括除设引脚的面,剩余至少一个面粘接散热片。4.一种曲率芯片的封装,包括应用soc集成芯片、3d堆叠集成芯片、sip集合芯片、sop集合芯片任一方案架构的数字电路芯片裸片、模拟电路芯片裸片、存储电路芯片裸片、硅光集成芯片裸片至少一个面填充介电材料实现封装,其特征在于,数字电路芯片、模拟电路芯片、存储电路芯片以及硅光集成芯片任一裸片的扩容、增加散热面、涂装介电材料、封装后的芯片投影面的曲率呈0

°

或大于0

°

的曲率芯片;其引出引入电路端设置于裸片的投影面、投影面相背面、投影相邻的端面至少之一;所述曲率芯片还包括与其投影面相邻的两个相对端面呈v形折叠、s 形折叠、波浪线折叠、阿基米德螺线任一形态,其连接引出引入电路端的引脚设置于曲率芯片投影面、投影面相背的面、投影面相邻的端面至少之一面;所述库容

和散热面的增加基于数字电路芯片、模拟电路芯片、存储电路芯片、硅光集成芯片任一的投影面面积最小大于18mmx13.5mm,最大小于应用设备的屏幕面积,厚度基于毫米级、微米级或纳米级尺寸;所述光子芯片至少包括:硅光集成芯片和cmos存储芯片,或者,硅光集成芯片、cmos存储芯片和模拟电路芯片;所述填充介电材料工艺至少包括:dip双列直插式、qfp塑料方型扁平式、pfp塑料扁平组件式pga插针网格阵列、bga球栅阵列、csp芯片尺寸;所述涂装介电材料工艺至少包括:喷涂、滴涂、刷涂、滚涂、覆膜;所述曲率芯片的架构或者还包括与衬低位置相对的顶层增设衬低。5.如权利要求4所述曲率芯片的封装,其特征在于,所述引脚设置位置包括曲率芯片的投影面与其相背的底面或相邻的侧面至少之一;所述引脚至少包括凸点、微球、金属柱、焊球、导爪或导线;所述曲率芯片的裸片介电封装方案还包括在常压、常温至少之一环境中喷涂、滚涂、刷涂、覆膜、粘膜一种或多种的工序组合;或者,在常压、常温至少之一环境中喷涂、滚涂、刷涂、覆膜、粘膜一种或多种的工序组合,再进入压力空间、加温空间至少之一进行介电材料填充优化;或者,在高压、高温至少之一环境中喷涂、滚涂、刷涂、覆膜、粘膜一种或多种的工序组合;所述填充介电材料至少包括:塑料、树脂、玻璃、陶瓷。6.如权利要求4、5任一所述曲率芯片的封装,其特征在于,所述曲率芯片所涉:soc集成芯片、3d堆叠集成芯片、sip集合芯片、sop集合芯片任一封装方案架构还包括:植入承载无源器件的基板和无源器件,或者,嵌入无源器件的基板;所述封装基板材料包括玻璃、陶瓷、塑料、亚克力、树脂、半导体一种或多种的合成物片材或卷材;所述无源器件至少包括电阻,电容,电感,转换器,渐变器,匹配网络,谐振器,滤波器,混频器和开关;所述厚度基于毫米级、微米级或纳米级的尺寸取值依据包括:依据设计库容所需体积

÷

投影面积+介电封装厚度=曲率0

°

芯片厚度值。7.如权利要求4、5、6任一所述曲率芯片的封装,其特征在于,所述曲率芯片的封装还包括soc集成芯片、sip集合芯片、sop集合芯片任一的裸片植入system board系统;所述曲率芯片的封装还包括soc集成芯片、sip集合芯片、sop集合芯片任一的裸片与system board系统裸片堆叠封装;所述曲率芯片的封装还包括sip集合芯片裸片、sop集合芯片裸片至少两片堆叠封装;所述堆叠至少包括数字电路芯片、模拟电路芯片、存储电路芯片以及硅光集成芯片任意组合至少两个叠加;或者,所述堆叠至少包括逻辑电路、通用处理器、存储器、单片系统、微控制器、定制电路、可编程逻辑器件、声音感知处理器、光线感知处理器、温度感知处理器、电源控制芯片、射频芯片、nand flash芯片、nor flash、dram任意组合至少两个叠加;所述堆叠包括纵向和横向至少之一有序或无序阵列;所述纵向堆叠形态至少包括:柱形、金字塔形、悬臂形、至少一排并肩形、至少一排上下勾连形;所述堆叠封装还包括tsv穿孔植入导体或走线结构,电路经tsv穿孔使相邻或相近的至少两个裸片电路导通,或者,顶层芯片与底部的rdl的连接;所述连接至少包括混合键合、表面活化键合或原子扩散键合;所述堆叠封装包括至少两个芯片、至少一个芯片和至少一个裸片、至少两个裸片任意有序或无序阵列;所述tsv穿孔工艺至少包括:激光钻孔、刻蚀工艺制作的盲孔或通孔;所述tsv填充工艺包括:微凸点、铜柱、金丝、焊球、可控坍塌芯片连接结构中的一种或多种的组合;所述通孔填充包括:晶圆制程晶体管电路之前或晶体管电路制程之后填充;所述曲率芯片的封装还包括倒装焊;所述曲率芯片还包括除设引脚的面,剩余至少一个面粘接散热片。8.如权利要求4、5、6、7任一所述曲率芯片的封装,其特征在于,所述曲率芯片的制备及

封装包括下列所述任一工艺流程的其中一段:soc曲率芯片工艺流程(一)衬低制备~晶体管电路搭建~打磨衬低~焊接封装基板~键合放大电路~键合引脚~检测电路~封装介电材料~刻蚀或印刷标注~分切芯片~独立封装;或者,soc曲率芯片工艺流程(二)衬低制备~晶体管电路搭建~打磨衬低~键合放大电路~键合引脚~检测电路~封装介电材料~刻蚀或印刷标注~分切芯片~独立封装;或者,soc曲率芯片工艺流程(三)衬低制备~晶体管电路搭建~刻蚀放大电路~键合引脚~检测电路~封装介电材料~刻蚀或印刷标注~分切芯片~独立封装;或者,soc曲率芯片工艺流程(四)衬低制备~晶体管电路搭建~刻蚀放大电路~打磨衬低~键合引脚~检测电路~封装介电材料~刻蚀或印刷标注~分切芯片~独立封装;或者,soc曲率芯片工艺流程(五)衬低制备~晶体管电路搭建~焊接封装基板~键合放大电路~键合引脚~检测电路~封装介电材料~刻蚀或印刷标注~分切芯片~独立封装;或者,sip封装曲率芯片工艺流程(一)衬低制备~晶体管电路搭建~焊接内置无源器件的封装基板~键合放大电路~键合引脚~检测电路~封装介电材料~刻蚀或印刷标注~分切芯片~独立封装;或者,sop曲率芯片工艺流程(一)衬低制备~晶体管电路搭建~焊接外设无源器件的封装基板~键合放大电路~键合引脚~检测电路~封装介电材料~刻蚀或印刷标注~分切芯片~独立封装;或者,3d堆叠曲率芯片工艺流程(一)衬低制备~tsv开盲孔~植入线路~晶体管电路搭建~打磨衬低~键合放大电路~键合引脚~封装介电材料~检测电路~刻蚀或印刷标注~分切芯片―独立包装;或者,3d堆叠曲率芯片工艺流程(二)衬低制备~tsv开通孔~植入线路~晶体管电路搭建~键合放大电路~键合引脚~封装介电材料~检测电路~刻蚀或印刷标注~分切芯片―独立包装;或者,3d堆叠曲率芯片工艺流程(三)衬低制备~tsv开盲孔~晶体管电路搭建~打磨衬低~植入线路~键合放大电路~键合引脚~封装介电材料~检测电路~刻蚀或印刷标注~分切芯片―独立包装;或者,3d堆叠曲率芯片工艺流程(四)衬低制备~tsv开通孔~晶体管电路搭建~植入线路~键合放大电路~键合引脚~封装介电材料~检测电路~刻蚀或印刷标注~分切芯片―独立包装制作的曲率芯片,其特征在于,晶体管电路搭建包括光刻设备及刻蚀设备;或者,原子或离子打印机打印晶体管电路。9.如权利要求8所述曲率芯片的封装,其特征在于,所述晶体管电路搭建制备还包括原子或离子打印晶体管电路;其工艺流程(一)包括基于衬低打印晶体管电路~填充介电材料~打磨显露引入引出电路端~再基于引入引出电路端打印晶体管电路~再打磨~键合放大电路~键合引脚~封装介电材料~检测电路~刻蚀或印刷标注~分切芯片―独立包装;打印晶体管电路工艺流程;工艺流程(二)包括基于衬低打印晶体管电路~填充介电材料~打磨显露引入引出电路端~再基于引入引出电路端打印晶体管电路~再打磨~打印引出引入端放大电路~键合引脚~封装介电材料~检测电路~刻蚀或印刷标注~分切芯片―独立包装。10.一种终端设备,包括对讲机、夜视仪、手机、平板电脑、电脑、武器载电脑、机载电脑、设备应用、笔记本、车载电脑、智能手表、智能手环,其特征在于,终端设备的应用,包括曲率芯片引出引入电路端与屏幕引出引入电路端键合;或者,曲率芯片引出引入电路端与主板引出引入电路端键合;或者,曲率芯片引出引入电路端与电池引出引入电路端键合或触接;或者,屏幕引出引入电路端与曲率芯片引出引入电路端一端键合、曲率芯片引出引入电路端另一端与主板引出引入电路端键合、主板引出引入电路端与电池引出引入电路端键合或触接;或者,屏幕引出引入电路端与曲率芯片引出引入电路端一端键合、曲率芯片引出引入电路端另一端与电池引出引入电路端键合或触接;或者,屏幕引出引入电路端与主板引出

引入电路端键合、主板引出引入电路端与电池引出引入电路端键合或触接。

技术总结

一种曲率芯片、封装及终端设备,基于芯片投影面积的超级放大、通用芯片厚度的极剧减薄,在不丧失功效的前提下还得以倍数级的提升,实现低性能设备制程高性能芯片,更是为克服隧穿效应以及设备的超薄奠定了坚实的基础,包括数字电路芯片、模拟电路芯片、存储电路芯片、硅光集成芯片任一类别曲率芯片,特征在于投影面面积最小大于18mmX13.5mm,最大小于应用设备的屏幕面积之间取值,厚度基于毫米级至纳米级取值,且封装后投影面曲率0

技术研发人员:王永明

受保护的技术使用者:王永明

技术研发日:2022.09.02

技术公布日:2022/10/27

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。