1.本技术实施例涉及电子技术领域,尤其涉及一种测试装置和测试设备。

背景技术:

2.随着高速信号技术的发展,出现了许多类型的高速信号,例如,高速串行计算机扩展总线(peripheral component interconnect express,pcie)信号、串行连接小型计算机系统接口(serial attached small computer system interface,sas)信号、串行高级技术附件(serial advanced technology attachment,sata)信号等高速信号。随着高速信号的不断发展,高速信号的链路设计的挑战越来越大,高速信号的测试也越来越重要。

3.例如,在服务器的主板上设置有互相耦合的处理器和高速串行计算机扩展总线插槽,处理器与高速串行计算机扩展总线插槽之间的链路用于传输高速信号,需要对该高速信号进行眼图和误码率的测试。但是,目前的测试方式操作复杂且测试效率低。

技术实现要素:

4.本技术实施例提供一种测试装置和测试设备,能够简化测试操作并且能够提高测试效率。

5.为达到上述目的,本技术实施例采用如下技术方案:

6.本技术实施例第一方面,提供一种测试装置,该测试装置包括:接口电路、测试电路和测试接口,接口电路、测试电路和测试接口耦合。其中,测试接口用于连接待测试装置。其中,测试接口用于接收来自待测试装置的测试信号,测试电路用于根据测试信号确定待测试装置的测试结果,接口电路用于发送测试结果。

7.本技术实施例提供的测试装置包括测试电路和测试接口,测试接口用于与待测试装置对接,通过测试接口接收来自待测试装置的测试信号,测试电路用于根据测试信号产生测试结果,该测试装置的结构简单,测试方式简单,相比于采用价格昂贵的示波器或误码仪进行测试以产生测试结果,降低了测试成本。同时,与采用示波器或误码仪进行测试相比,本实施例的测试装置与待测试装置直接连接,不需要通过同轴电缆连接器与示波器或误码仪连接,也不需要多次改变同轴电缆连接器的连接位置,因此能够简化测试操作,能够提高测试效率。

8.结合第一方面,在一种可能的实现方式中,上述测试信号为第一测试码型,上述测试结果包括眼图数据和/或眼图测试结论,眼图测试结论用于指示眼图数据是否满足预设眼图测试指标。

9.本技术实施例提供的测试装置,通过测试接口接收来自待测试装置的测试信号,通过测试电路产生眼图数据和/或眼图测试结论,与采用示波器进行测试相比,本实施例的测试装置与待测试装置直接连接,不需要通过同轴电缆连接器与示波器连接,也不需要多次改变同轴电缆连接器的连接位置,因此能够简化测试操作,能够提高测试效率,而且能够降低测试成本。

10.结合第一方面,在一种可能的实现方式中,当测试结果为眼图数据时,测试电路具体用于根据第一测试码型获取同步时钟信号,根据第一测试码型和同步时钟信号确定多个时钟周期的波形数据,根据多个时钟周期的波形数据确定眼图数据。或者,当测试结果为眼图测试结论时,测试电路还用于根据眼图数据和预设眼图测试指标确定眼图测试结论。

11.本技术实施例提供的测试装置,通过测试接口接收来自待测试装置的第一测试码型,通过测试电路产生眼图数据和/或眼图测试结论,与采用示波器进行测试相比,本实施例的测试装置与待测试装置直接连接,不需要通过同轴电缆连接器与示波器连接,也不需要多次改变同轴电缆连接器的连接位置,能够简化测试操作,能够提高测试效率,而且能够降低测试成本。

12.结合第一方面,在一种可能的实现方式中,上述测试信号为第二测试码型,上述测试结果为误码信息。接口电路还用于接收控制信号,测试电路还用于根据控制信号产生第三测试码型,测试接口还用于向待测试装置发送第三测试码型,第二测试码型为待测试装置根据第三测试码型转换得到。

13.本技术实施例提供的测试装置,通过测试接口接收来自待测试装置的第二测试码型,通过测试电路根据第二测试码型和第三测试码型产生误码信息,与采用误码仪进行测试相比,本实施例的测试装置与待测试装置直接连接,不需要通过同轴电缆连接器与误码仪连接,也不需要多次改变同轴电缆连接器的连接位置,能够简化测试操作,能够提高测试效率,而且能够降低测试成本。

14.结合第一方面,在一种可能的实现方式中,上述测试电路具体用于将第二测试码型和第三测试码型逐位比较,确定第二测试码型的误码的位数,根据误码的位数和第三测试码型的总位数的比值确定误码信息。

15.本技术实施例提供的测试装置,通过测试接口接收来自待测试装置的第二测试码型,通过测试电路根据第二测试码型和第三测试码型产生误码信息,与采用误码仪进行测试相比,本实施例的测试装置与待测试装置直接连接,不需要通过同轴电缆连接器与误码仪连接,也不需要多次改变同轴电缆连接器的连接位置,能够简化测试操作,能够提高测试效率,而且能够降低测试成本。

16.结合第一方面,在一种可能的实现方式中,测试电路包括测试芯片,测试芯片的一端与测试接口耦合,测试芯片的另一端与接口电路耦合。

17.本技术实施例提供的测试装置,通过测试芯片根据测试信号产生测试结果,而不需要采用价格昂贵的示波器和误码仪以产生测试结果,因此能够降低测试成本。同时,与采用示波器或误码仪进行测试相比,本实施例的测试装置与待测试装置直接连接,不需要通过同轴电缆连接器与示波器或误码仪连接,也不需要多次改变同轴电缆连接器的连接位置,能够简化测试操作,能够提高测试效率。

18.结合第一方面,在一种可能的实现方式中,上述测试芯片包括高速时钟数据恢复芯片、信号驱动器芯片或选择芯片。

19.结合第一方面,在一种可能的实现方式中,测试电路还包括时钟电路和复位电路,时钟电路和复位电路分别与测试芯片耦合。

20.本技术实施例提供的测试装置,通过时钟电路为测试芯片提供时钟,通过复位电路在待测试装置中每一个通道测试完成时使测试芯片恢复初始状态,从而测试装置可以完

成对待测试装置中所有通道的测试,而不需要采用价格昂贵的示波器和误码仪以产生测试结果,因此能够降低测试成本。同时,与采用示波器或误码仪进行测试相比,本实施例的测试装置与待测试装置直接连接,不需要通过同轴电缆连接器与示波器或误码仪连接,也不需要多次改变同轴电缆连接器的连接位置,能够简化测试操作,能够提高测试效率。

21.结合第一方面,在一种可能的实现方式中,测试装置还包括电源电路,该电源电路的输入端与测试接口耦合,电源电路的输出端与接口电路和测试电路耦合。

22.本技术实施例提供的测试装置,通过电源电路对测试接口接收的供电电压进行处理,因此能够为接口电路和测试电路提供稳定的供电电压。

23.结合第一方面,在一种可能的实现方式中,上述测试接口包括高速串行计算机扩展总线接口、串行连接小型计算机系统接口、串行高级技术附件接口、卡机电接口、非易失性内存标准接口或开放核心协议接口。

24.本技术实施例提供的测试装置,通过根据待测试装置中插槽的类型设置不同类型的测试接口,因此能够支持测试装置对高速串行计算机扩展总线信号、串行连接小型计算机系统接口信号、串行高级技术附件信号、通用串行总线信号等高速信号进行测试。

25.结合第一方面,在一种可能的实现方式中,上述接口电路包括以太网接口电路、串行通信接口电路、通用串行总线接口电路或无线接口电路。

26.本技术实施例提供的测试装置,通过将接口电路设置为多个类型的接口电路,从而可以支持不同类型的控制装置,例如该控制装置可以为个人计算机、平板电脑、手机等。

27.本技术实施例第二方面,提供一种测试设备,该测试设备用于测试待测试装置,该测试设备包括控制装置和测试装置,控制装置的一端与测试装置耦合,控制装置的另一端用于连接待测试装置,所述测试装置的结构为如第一方面或第一方面的任一种可能的实现方式所述的测试装置的结构。其中,控制装置用于向待测试装置发送控制信号,测试装置用于接收待测试装置根据控制信号发送的测试信号,根据测试信号确定待测试装置的测试结果。控制装置还用于接收测试结果。

28.本技术中第二方面的描述,可以参考第一方面的详细描述;并且,第二方面的有益效果,可以参考第一方面的有益效果分析,此处不再赘述。

附图说明

29.图1为一种测试夹具的结构示意图;

30.图2为一种眼图曲线示意图;

31.图3为一种眼图测试电路的结构示意图;

32.图4为一种误码测试电路的结构示意图;

33.图5为本技术实施例提供的一种测试装置应用场景的示意图;

34.图6为本技术实施例提供的另一种测试装置应用场景的示意图;

35.图7为本技术实施例提供的一种测试装置的结构示意图;

36.图8为本技术实施例提供的一种测试设备应用场景的示意图;

37.图9为本技术实施例提供的一种测试设备的结构示意图。

具体实施方式

38.下文将详细论述各实施例的制作和使用。但应了解,本技术提供的许多适用发明概念可实施在多种具体环境中。所论述的具体实施例仅仅说明用以实施和使用本说明和本技术的具体方式,而不限制本技术的范围。

39.除非另有定义,否则本文所用的所有科技术语都具有与本领域普通技术人员公知的含义相同的含义。

40.各电路或其它组件可描述为或称为“用于”执行一项或多项任务。在这种情况下,“用于”用来通过指示电路/组件包括在操作期间执行一项或多项任务的结构(例如电路系统)来暗指结构。因此,即使当指定的电路/组件当前不可操作(例如未打开)时,该电路/组件也可以称为用于执行该任务。与“用于”措辞一起使用的电路/组件包括硬件,例如执行操作的电路等。

41.下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行描述。在本技术中,“至少一个”是指一个或者多个,“多个”是指两个或两个以上。“和/或”,描述关联对象的关联关系,表示可以存在三种关系,例如,a和/或b,可以表示:单独存在a,同时存在a和b,单独存在b的情况,其中a,b可以是单数或者复数。字符“/”一般表示前后关联对象是一种“或”的关系。“以下至少一项(个)”或其类似表达,是指的这些项中的任意组合,包括单项(个)或复数项(个)的任意组合。例如,a,b或c中的至少一项(个),可以表示:a,b,c,a和b,a和c,b和c或a、b和c,其中a、b和c可以是单个,也可以是多个。另外,在本技术的实施例中,“第一”、“第二”等字样并不对数量和次序进行限定。

42.需要说明的是,本技术中,“示例性的”或者“例如”等词用于表示作例子、例证或说明。本技术中被描述为“示例性的”或者“例如”的任何实施例或设计方案不应被解释为比其他实施例或设计方案更优选或更具优势。确切而言,使用“示例性的”或者“例如”等词旨在以具体方式呈现相关概念。

43.在介绍本技术实施例之前,首先对本技术涉及的背景技术进行介绍说明。

44.随着高速信号的不断发展,高速信号的链路设计的挑战越来越大,高速信号的测试也越来越重要。目前,一般通过示波器、误码仪和测试夹具,对高速信号进行相应的测试,比如,眼图测试和误码测试等。

45.其中,测试夹具用于在测量仪器(示波器或误码仪)无法与待测试装置直接耦合时,提供测试接口,以完成高速信号的测试。

46.例如,如图1所示为一种测试夹具100,该测试夹具100包括多个测试接口110和高速串行计算机扩展总线接口120。其中,高速串行计算机扩展总线接口120也可以称为金手指,高速串行计算机扩展总线接口120用于与待测试装置中的高速串行计算机扩展总线插槽耦合,该多个测试接口110与高速串行计算机扩展总线插槽中的多个通道对应,用于为示波器或误码仪提供测试接口。

47.具体的,眼图测试电路可以包括示波器和测试夹具,示波器可以通过测试夹具接收来自待测试装置的高速信号生成如图2所示的眼图,该眼图可以用于分析高速信号的占空比、噪声和抖动情况。误码测试电路可以包括误码仪和测试夹具,误码仪可以通过测试夹具向待测试装置发送或接收来自待测试装置的高速信号,根据发送和接收的高速信号的误差,可以得到误码率。为了进行稳定的、可重复性的测试,一般采用测试码型作为高速信号

进行上述眼图测试或误码测试。

48.例如,如图3所示为一种眼图测试电路300的结构图,该眼图测试电路300包括主板310、测试夹具320、示波器330和个人计算机(personal computer,pc)340。其中,主板310为待测试装置,主板310上设置有互相耦合的处理器311和高速串行计算机扩展总线插槽312,测试夹具320包括多个测试接口321和高速串行计算机扩展总线接口322。个人计算机340可以通过网线与主板310中的处理器311耦合,个人计算机340还可以通过网线与示波器330耦合,示波器330通过同轴电缆连接器350(或称为smp连接器)与测试夹具320中的一个测试接口321耦合,高速串行计算机扩展总线接口322与高速串行计算机扩展总线插槽312耦合。个人计算机340用于产生控制信号,处理器311根据该控制信号产生测试码型,示波器330通过同轴电缆连接器350接收测试码型,根据该测试码型生成眼图,从而个人计算机340可以根据眼图分析高速信号的占空比、噪声和抖动情况,确定处理器311与示波器330之间发送(transport x,tx)链路的质量。

49.再例如,将上述图3中的示波器330替换为误码仪360,构建如图4所示的误码测试电路400的结构图。其中,个人计算机340可以与误码仪360耦合,误码仪360通过同轴电缆连接器350和同轴电缆连接器370分别与测试夹具320中的2个测试接口321耦合。个人计算机340用于产生控制信号,误码仪360用于根据该控制信号产生第一测试码型,该第一测试码型通过同轴电缆连接器350传输至处理器311,处理器311根据该第一测试码型产生第二测试码型,该第二测试码型通过同轴电缆连接器370传输至误码仪360,误码仪360根据上述第一测试码型和第二测试码型确定误码仪360与处理器311之间环路传输高速信号时的误码率,个人计算机340可以根据该误码率判断误码仪360与处理器311之间接收(receive x,rx)链路的质量。

50.但是,由于处理器311和高速串行计算机扩展总线插槽312之间的链路包括多个通道,而示波器330和误码仪360的通道数量有限,需要通过改变同轴电缆连接器的连接位置,从而连接测试夹具320中的不同测试接口321,以完成上述多个通道的眼图测试或误码测试,操作比较复杂,测试效率较低。而且,根据上述图3和图4可以理解的,眼图测试与误码测试需要构建不同的测试电路,当需要同时对处理器311和高速串行计算机扩展总线插槽312之间的多个通道进行眼图测试和误码测试时,需要改变测试电路的结构,操作比较复杂,测试效率低,对测试操作人员的技能要求较高。同时,用于高速信号测试的示波器330、误码仪360和测试夹具320的价格昂贵,测试成本较高。

51.综上,上述图3或图4所示的测试电路在对高速信号进行测试时,操作比较复杂,测试效率较低,对测试人员的技能要求较高,并且测试成本较高。因此本技术实施例提供一种测试装置,能够提高测试的测试效率,并且操作方便。

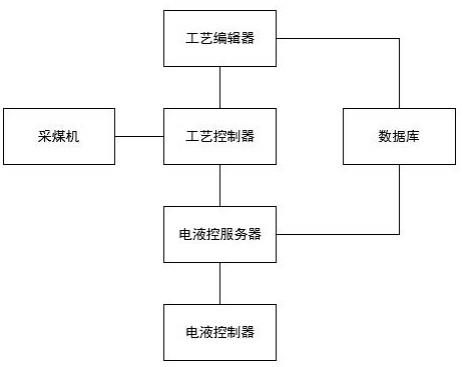

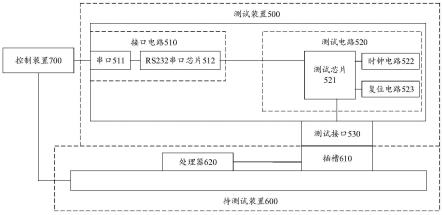

52.图5为本技术实施例提供的一种测试装置500应用场景的示意图,该测试装置500用于对待测试装置600中的信号进行测试,该测试装置500可以包括接口电路510、测试电路520和测试接口530,接口电路510、测试电路520和测试接口530耦合。

53.在一种可能的实施例中,如图5所示,该测试装置500可以包括依次耦合的接口电路510、测试电路520和测试接口530。在其他实施例中,接口电路510、测试电路520和测试接口530之间还可以两两之间耦合。

54.需要说明的是,上述图5中测试装置500的结构为示例性说明,其并不对本技术实

施例构成限定。

55.其中,测试接口530用于接收来自待测试装置600的测试信号。测试电路520用于根据该测试信号确定待测试装置600的测试结果。接口电路510用于发送测试结果。

56.可选的,待测试装置600可以包括服务器或存储设备,本技术实施例对于待测试装置600的具体类型并不限定。例如,该待测试装置600可以为固态硬盘。

57.本技术实施例提供的测试装置500的结构简单,包括测试电路520和测试接口530,测试接口530用于与待测试装置600对接,通过测试接口530接收来自待测试装置600的测试信号,测试电路520用于根据测试信号产生测试结果,该测试装置500的结构简单,测试方式简单,相比于采用价格昂贵的示波器和误码仪进行测试以产生测试结果,降低了测试成本,提高了测试的效率。同时,与采用示波器或误码仪进行测试相比,本实施例的测试装置与待测试装置直接连接,不需要通过同轴电缆连接器与示波器或误码仪连接,也不需要多次改变同轴电缆连接器的连接位置,因此能够简化测试操作,能够提高测试效率。

58.可选的,本技术实施例提供的测试装置500可以用于高速信号测试,或者,可以用于低速信号测试,本技术实施例对于测试装置500具体用高速信号测试还是低速信号测试并不限定,下述实施例以测试装置500用于高速信号测试为例进行示例性说明。

59.示例性的,当测试装置500用于高速信号测试时,上述待测试装置600可以包括互相耦合的插槽610和处理器620,插槽610与测试接口530耦合,测试装置500用于对插槽610和处理器620之间的链路进行高速信号测试。其中,插槽610为高速信号插槽。

60.可选的,上述测试信号可以为测试码型,采用测试码型能够进行稳定的、可重复性的测试,该测试码型可以包括以下的一种:伪随机二进制序列(pseudo-random binary sequence,prbs)31、prbs7、prbs9、prbs11、prbs15、prbs20和prbs23。

61.可选的,本技术实施例提供的测试装置500可以用于眼图测试,生成眼图和/或眼图测试结论以确定处理器620与测试电路520之间发送链路的质量是否合格。或者,测试装置500可以用于误码测试,确定误码率以判断处理器620与测试电路520之间接收链路的质量是否合格。

62.在一种可能的实施例中,如图5所示,当测试装置500用于眼图测试时,上述测试信号可以为第一测试码型,上述测试结果包括眼图数据(或者可以称为电子眼图)和/或眼图测试结论,眼图测试结论用于指示眼图数据是否满足预设眼图测试指标。

63.可选的,当测试结果为眼图数据时,测试电路520具体用于根据第一测试码型获取同步时钟信号,根据第一测试码型和同步时钟信号确定多个时钟周期的波形数据,根据多个时钟周期的波形数据确定眼图数据。当测试结果为眼图测试结论时,测试电路520还用于根据眼图数据和预设眼图测试指标确定眼图测试结论。

64.可以理解的,当测试结果为眼图数据时,控制装置700可以接收测试装置500发送的眼图数据,对该眼图数据进行分析处理以生成眼图测试结论,并显示眼图测试结论。当测试结果为眼图测试结论时,控制装置700可以接收该眼图测试结论,不需要经过分析处理,可以直接显示眼图测试结论。

65.示例的,插槽610和处理器620之间的链路可以包括多个通道,插槽610和测试接口530可以包括相同数量的多个通道。当测试结果为眼图数据时,待测试装置600中的处理器620可以接收第一控制信号,根据该第一控制信号产生第一测试码型,并通过插槽610的多

个通道中的任一个通道发送上述第一测试码型。测试电路520可以通过测试接口530中对应的通道接收第一测试码型,根据该第一测试码型确定眼图数据,并通过接口电路510发送该眼图数据。可以理解的,处理器620通过多次接收不同的控制信号,产生相应的测试码型,可以完成插槽610和测试接口530之间所有通道的眼图测试。

66.当测试结果为眼图测试结论时,测试电路520中可以存储有预设眼图测试指标,测试电路520可以根据上述眼图数据和预设眼图测试指标确定眼图测试结论,并通过接口电路510发送上述眼图数据和/或眼图测试结论。

67.可以理解的,本技术实施例提供的测试装置500在进行眼图测试时,通过测试接口530接收处理器620产生的测试信号,该测试接口530包括和插槽610相对应的多个通道。因此在进行眼图测试的过程中,处理器620通过不同通道发送的测试码型,测试电路520均可通过测试接口530中对应的通道接收到,从而能够完成插槽610和处理器620之间所有通道的眼图测试,而不需要多次改变同轴电缆连接器的连接位置,因此操作简单,能够提高测试效率,同时不需要采用价格昂贵的示波器330和测试夹具320,能够降低成本。

68.在另一种可能的实施例中,如图6所示,当测试装置500用于误码测试时,上述测试信号为第二测试码型,上述测试结果为误码信息(或称为误码率),接口电路510还用于接收第二控制信号,测试电路520用于根据该第二控制信号产生第三测试码型,测试接口530还用于向待测试装置600发送第三测试码型,第二测试码型是待测试装置600根据接收到的第三测试码型发送的。

69.当测试结果为误码信息时,测试电路520具体用于将第二测试码型和第三测试码型逐位比较,确定第二测试码型的误码的位数,根据误码的位数和第三测试码型的总位数的比值确定误码信息,从而判断处理器620与测试电路520之间接收链路的质量是否合格。

70.示例的,插槽610和处理器620之间的链路可以包括多个通道,插槽610和测试接口530可以包括相同数量的多个通道,测试装置500中的测试电路520可以接收第二控制信号,根据该第二控制信号产生第三测试码型,并通过测试接口530中的任一个通道发送该第三测试码型。待测试装置600中的处理器620可以通过插槽610中对应的通道接收第三测试码型,根据第三测试码型产生第二测试码型,并通过插槽610中的另一个通道发送该第二测试码型。测试电路520可以通过测试接口530中相对应的通道接收该第二测试码型,将第二测试码型和第三测试码型逐位比较,确定第二测试码型的误码的位数,根据误码的位数和第三测试码型的总位数的比值确定误码信息,并通过接口电路510发送该误码信息。测试电路520通过多次接收不同的控制信号,产生相应的测试码型,可以完成插槽610和测试接口530之间所有通道的误码测试。

71.可以理解的,本技术实施例提供的测试装置500在进行误码测试时,测试电路520通过测试接口530发送第三测试码型,通过测试接口530接收处理器620产生的第二测试码型,其中测试接口530包括和插槽610相对应的多个通道。因此在进行误码测试的过程中,测试电路520可以通过测试接口530中的不同通道向处理器620发送测试码型,或者接收处理器620产生的测试码型,从而能够完成插槽610和处理器620之间所有通道的误码测试,而不需要多次改变同轴电缆连接器的连接位置,因此操作简单,能够提高测试效率,同时不需要采用价格昂贵的误码仪360和测试夹具320,能够降低成本。

72.可选的,如图5和图6所示,上述第一控制信号和第二控制信号可以由控制装置700

产生。该控制装置700还可以用于接收上述眼图数据和/或眼图测试结论,生成并显示眼图和/或眼图测试结论,或者,用于接收上述误码数据显示误码率。该控制装置可以为电子设备,比如个人计算机、平板电脑、手机等。

73.示例性的,当测试装置500用于对待测试装置600中的高速信号进行眼图测试时,上述控制装置700可以与待测试装置600中的处理器620和接口电路510耦合,该控制装置700可以用于产生上述第一控制信号,还可以用于接收上述眼图数据生成并显示眼图,进一步的,控制装置700中可以存储有预设眼图测试指标,控制装置700可以根据眼图和预设眼图测试指标确定眼图测试结论;或者,控制装置700可以用于接收上述眼图测试结论并显示眼图测试结论;或者,控制装置700可以用于接收上述眼图数据和眼图测试结论,生成并显示眼图和眼图测试结论。当测试装置500用于对待测试装置600中的高速信号进行误码测试时,上述控制装置700可以与测试装置500的接口电路510耦合,该控制装置700可以用于产生上述第二控制信号,还可以用于接收上述误码信息显示误码率。

74.可选的,控制装置700可以包括控制软件,该控制软件用于启动、暂停、停止测试、收集、分析测试数据、输出测试报告,例如,该控制软件可以用于产生上述第一控制信号和第二控制信号等控制信号。具体的。测试操作人员可以通过点击控制软件中的虚拟按键,选择需要进行的测试,例如,操作人员可以选择眼图测试,或者,可以选择误码测试,以控制测试装置500和待测试装置600执行相应的指令,以完成眼图测试或误码测试等测试内容,接收测试装置500发送的测试结果,对该测试结果进行分析生成测试报告,从而完成对待测试装置600的测试。进一步的,测试人员还可以根据控制软件生成的测试报告,进行参数拉偏和参数优化,从而提高测试效率。

75.可选的,上述接口电路510可以为以太网接口电路、串行通信接口电路、通用串行总线(universal serial bus,usb)接口电路或无线接口电路,本技术实施例对于接口电路510的具体类型并不限定。

76.可以理解的,当接口电路510为无线接口电路时,接口电路510和控制装置700无线不需要通过有线连接,与有线连接相比,控制装置700和测试装置500的位置不受线缆的限制更灵活,控制装置700与测试装置500之间通信的建立更方便。

77.示例的,当接口电路510为以太网接口电路时,接口电路510可以包括以太网接口和以太网接口芯片;当接口电路510为串行通信接口电路时,接口电路510可以包括串行通信接口和串行通信接口芯片;当接口电路510为通用串行总线接口电路时,接口电路510可以包括通用串行总线接口和通用串行总线接口芯片;当接口电路为无线接口电路时,接口电路510可以包括无线芯片。

78.例如,当接口电路510包括以太网接口和以太网接口芯片时,该以太网接口可以为水晶头45(registered jack 45,rj-45)接口或水晶头11(registered jack 11,rj-11)接口,以太网接口芯片可以为物理层(physical layer,phy)芯片。当接口电路510包括串行通信接口和串行通信芯片时,该串行通信接口芯片可以为美国电子工业联盟232(recommended standard232,rs232)串口芯片,其中串行通信接口可以简称为串口。当接口电路510包括通用串行总线接口和通用串行总线接口芯片时,该通用串行总线接口可以为usb2.0接口或usb3.0接口,通用串行总线接口芯片可以为usb2.0接口芯片或者可以为usb3.0接口芯片。当接口电路510包括无线接口芯片时,该无线接口芯片可以为蓝牙

(bluetooth)芯片、无线保真(wireless fidelity,wifi)芯片或紫蜂(zigbee)芯片。图5和图6中以接口电路510为串行通信接口电路,该串行通信接口电路包括串口511和rs232串口芯片512为例进行实例性说明。

79.可选的,如图5和图6所示,上述测试电路520可以包括测试芯片521,测试芯片521的一端与接口电路510耦合,测试芯片521的另一端与测试接口530耦合,该测试芯片521用于根据测试信号确定待测试装置600的测试结果。

80.可选的,上述测试芯片521包括以下的一种:高速时钟数据恢复(clock and data recovery,cdr)芯片、信号驱动器(retimer)芯片和选择(switch)芯片,本技术实施例对于测试芯片521的具体类型并不限定。

81.可选的,如图5和图6所示,上述测试电路520还可以包括时钟电路522和复位电路523,时钟电路522和复位电路523分别与测试芯片521耦合。时钟电路522用于为测试芯片521提供时钟,复位电路523用于在待测试装置中每一个通道测试完成时使测试芯片521恢复初始状态,从而测试装置500可以完成对待测试装置600中所有通道的测试。

82.可选的,上述测试接口530(或称为金手指)与待测试装置600中插槽610的类型有关,可以根据插槽610的类型将测试接口530设计为不同类型的接口。测试接口530可以包括以下的一种:高速串行计算机扩展总线接口、串行连接小型计算机系统接口、串行高级技术附件接口、卡机电(card electromechanical,cem)接口、非易失性内存标准(non-volatile memory express,nvme)接口和开放核心协议(open core protocol,ocp)接口。从而能够支持测试装置500对高速串行计算机扩展总线信号、串行连接小型计算机系统接口信号、串行高级技术附件信号、通用串行总线信号等高速信号进行测试。

83.示例性的,当插槽610为高速串行计算机扩展总线插槽时,上述测试接口530可以为高速串行计算机扩展总线接口。

84.可选的,当测试接口530为高速串行计算机扩展总线接口时,该高速串行计算机扩展总线接口可以包括16个通道、8个通道、4个通道或1个通道,或者,可以包括更多个通道,本技术实施例对于该高速串行计算机扩展总线接口包括通道的具体数量并不限定。

85.可选的,本技术实施例提供的测试装置500可以根据测试接口的类型设置为不同的形态,从而能够更方便的用于测试待测试装置600,该测试装置500的形态可以包括以下的一种:高速串行计算机扩展总线板卡、接口和开放核心协议板卡、2.5寸硬盘、3.5寸硬盘或u盘等。

86.本技术实施例提供的测试装置500,通过测试接口530接收待测试装置600发送的测试信号,或者,通过测试接口530接收待测试装置600发送的测试信号,该测试接口530包括和待测试装置600中的插槽610相对应的多个通道,因此在测试的过程中,不需要多次改变测试电路的结构,测试电路520能够接收到多个通道中任一个通道发送的测试信号,根据该测试信号能够确定待测试装置600的测试结果。因此,在测试的过程中操作简单,能够提高测试效率,同时,不需要采用价格昂贵的示波器330、误码仪360和测试夹具320,能够降低成本。

87.在一种可能的实施例中,如图7所示,上述测试装置500还可以包括电源电路540,该电源电路540的输入端与测试接口530耦合,电源电路540的输出端与接口电路510和测试接口530耦合。

88.需要说明的是,上述图7中测试装置500的结构为示例性说明,其并不对本技术实施例构成限定。

89.该电源电路540用于为接口电路510和测试电路520供电。

90.具体的,电源电路540用于接收来自测试接口530的供电电压,在该供电电压与接口电路510和测试电路520所需的供电电压不同时,可以对接收到的供电电压进行电压变换,以产生接口电路510和测试电路520所需的供电电压。

91.可选的,接口电路510和测试电路520所需的供电电压可以相同,或者所需的供电电压可以不同,本技术实施例对此并不限定,下述实施例以接口电路510和测试电路520所需的供电电压为不同的供电电压为例进行示例性说明。

92.例如,结合图7,当接口电路510和测试电路520所需的供电电压为不同的供电电压不同时,电源电路540的第一输出端与接口电路510中的rs232串口芯片耦合,电源电路540的第二输出端与测试芯片521耦合。以电源电路540通过测试接口530接收待测试装置600提供的12v供电电压,接口电路510中的rs232串口芯片需要1.8v供电电压,测试芯片521需要3.3v供电电压为例,电源电路540根据该12v供电电压,可以产生接口电路510中的rs232串口芯片所需的1.8v供电电压,还可以产生测试芯片521所需的3.3v供电电压。

93.本技术实施例提供的测试装置500,通过电源电路540对测试接口530接收的供电电压进行处理,因此能够为接口电路510和测试电路520提供稳定的供电电压。

94.在其他实施例中,电源电路540可以与接口电路510耦合,接口电路510可以接收来自控制装置700的供电电压,在该供电电压与接口电路510和测试电路520所需的供电电压不同时,可以对接收到的供电电压进行电压变换,以产生接口电路510和测试电路520所需的供电电压。

95.在其他实施例中,电源电路540可以只给接口电路510提供稳定的供电电压,或者,电源电路540可以只给测试电路520提供稳定的供电电压。基于此,如图8所示,本技术实施例还提供一种测试设备800,该测试设备800用于测试待测试装置900,该测试设备800包括互相耦合的控制装置810和测试装置820。其中,控制装置810和测试装置820分别与待测试装置900耦合。该测试装置820的结构可以如图5、图6和图7所示的测试装置500的结构。

96.需要说明的是,上述图8中测试设备800的结构为示例性说明,其并不对本技术实施例构成限定。

97.上述控制装置810用于发送控制信号,待测试装置900用于根据控制信号发送测试信号,测试装置820用于根据测试信号确定待测试装置900的测试结果,控制装置810还用于接收测试结果。

98.可选的,本技术实施例提供的测试设备800可以用于高速信号测试,或者,可以用于低速信号测试,本技术实施例对于测试设备800具体用高速信号测试还是低速信号测试并不限定。

99.可选的,本技术实施例提供的测试设备800可以用于眼图测试,生成眼图和/或眼图测试结论以确定待测试装置900发送链路的质量,上述测试结果为眼图和/或眼图测试结论;或者,可以用于误码测试,确定误码信息(误码率)以判断待测试装置900接收链路的质量,上述测试结果为误码信息。

100.可选的,控制装置810可以包括控制软件,该控制软件用于启动、暂停、停止测试、

收集、分析测试数据、输出测试报告,例如,该控制软件可以用于产生上述第一控制信号和第二控制信号等控制信号。具体的。测试操作人员可以通过点击控制软件中的虚拟按键,选择需要进行的测试,例如,操作人员可以选择眼图测试,或者,可以选择误码测试,以控制测试装置820和待测试装置900执行相应的指令,以完成眼图测试或误码测试等测试内容,接收测试装置820发送的测试结果,对该测试结果进行分析生成测试报告,从而完成对待测试装置900的测试。进一步的,测试人员还可以根据控制软件生成的测试报告,进行参数拉偏和参数优化,从而提高测试效率。

101.示例性的,控制装置810可以根据上述眼图和/或眼图测试结论,以及误码率,调整预加重,提高待测试装置900传输高速信号的质量。其中预加重是指在发送高速信号时,对高速信号的高频分量进行补偿的信号处理方式,通过调整预加重,能够补偿高速信号在传输过程中的损耗,能够提高高速信号的质量。

102.可选的,上述控制装置810为电子设备。比如,该电子设备可以为个人计算机、平板电脑、手机等。

103.可选的,上述待测试装置900可以包括主板910,该主板910上可以设置有处理器911和插槽912。

104.上述测试装置820包括测试接口821,该测试接口821用于与待测试装置900中的插槽912耦合。

105.可选的,该测试接口821可以包括以下的一种:高速串行计算机扩展总线接口、串行连接小型计算机系统接口、串行高级技术附件接口、卡机电接口、非易失性内存标准接口和开放核心协议接口。从而能够支持测试设备900对高速串行计算机扩展总线信号、串行连接小型计算机系统接口信号、串行高级技术附件信号、通用串行总线信号等高速信号进行测试。

106.可选的,上述测试信号为测试码型,采用测试码型能够进行稳定的、可重复性的测试,该测试码型可以包括以下的一种:prbs31、prbs7、prbs9、prbs11、prbs15、prbs20和prbs23。

107.在一种可能的实施例中,如图9所示,上述控制装置810可以集成设置在测试装置820中,测试设备800还可以包括人机交互界面830,该人机交互界面830与控制装置810耦合,测试操作人员可以通过点击人机交互界面830中的虚拟按键,以控制测试设备对待测试装置900进行测试,该人机交互界面830还可以用于显示测试结果。

108.本技术实施例提供的测试设备800,通过测试装置820根据测试信号确定待测试装置900的测试结果,该测试装置820通过测试接口821和插槽912与待测试装置900耦合,测试接口821包括和插槽912相对应的多个通道,因此在测试的过程中,不需要多次改变测试电路的结构,测试装置820能够接收到待测试装置900中的测试信号,根据该测试信号能够确定测试结果,控制装置810根据该测试结果可以显示测试结果眼图和/眼图测试结论,或者,显示误码率,从而能够确定待测试装置900发送链路和接收链路的质量。与现有技术相比,在测试的过程中,不需要多次改变同轴电缆连接器的连接位置,因此操作简单,能够提高测试效率,同时,不需要采用价格昂贵的示波器330、误码仪360和测试夹具320,能够降低成本。需要说明的是,上述装置实施例关于测试装置500的相关描述均可对应援引到该测试设备800的实施例中,本技术实施例在此不再赘述。

109.以上所述,仅为本技术的具体实施方式,但本技术的保护范围并不局限于此,任何在本技术揭露的技术范围内的变化或替换,都应涵盖在本技术的保护范围之内。因此,本技术的保护范围应以所述权利要求的保护范围为准。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。