1.本发明是有关于一种电压追踪电路,特别是有关于一种用于高压电路的电压追踪电路以及电子电路。

背景技术:

2.一般而言,当n型金属氧化物半导体(n-type metal oxide semiconductor,nmos)用于一电子电路的高压侧时,可能会因为在其源/基极上发生过电压,使得nmos晶体管的寄生双极二级管导通,导致漏电流的发生。漏电流会导致电子电路过热,并且损坏电子电路。因此,如何能降低过电压发生时所引起的漏电流,是重要的议题。

技术实现要素:

3.有鉴于此,本发明提出一种电压追踪电路。此电压追踪电路用以追踪一第一电压端上的一第一电压与一第二电压端上的一第二电压中的一者以产生一输出电压。电压追踪电路包括一第一p型晶体管、一降压电路、以及一第二p型晶体管。第一p型晶体管具有一栅极、一漏极、以及一源极,第一p型晶体管的漏极耦接第一电压端。降压电路耦接于第一电压端与第一p型晶体管的栅极之间,且提供一调节电压。降压电路以调节电压来降低第一电压以产生一控制电压且将控制电压提供至第一p型晶体管的栅极。第二p型晶体管具有一栅极、一漏极、以及一源极。第二p型晶体管的栅极耦接第一电压端,且第二p型晶体管的漏极耦接第二电压端。第一p型晶体管的源极与第二p型晶体管的源极耦接电压追踪电路的一输出端,且输出电压产生于输出端。

4.本发明另提出一种电子电路。此电子电路包括一高压侧器件以及一电压追踪电路。高压侧器件具有一第一电极端以及一第二电极端,且由一隔离深阱所包围。电压追踪电路耦该第一电极端该第二电极端,用以追踪第一电极端上的一第一电压与第二电极端上的一第二电压中的一者以于一输出端上产生一输出电压,且将输出电压施加至包围高压侧器件的隔离深阱。电压追踪电路包括一第一p型晶体管、一降压电路、以及一第二p型晶体管。第一p型晶体管具有一栅极、一漏极、以及一源极。第一p型晶体管的漏极耦接第一电极端。降压电路耦接该第一电极端该第一p型晶体管的栅极之间,且提供一调节电压。降压电路以调节电压来降低第一电压以产生一控制电压,且将控制电压提供至第一p型晶体管的栅极。第二p型晶体管具有一栅极、一漏极、以及一源极。第二p型晶体管的栅极耦接第一电极端,且第二p型晶体管的漏极耦接第二电极端。第一p型晶体管的源极与第二p型晶体管的源极耦接电压追踪电路的输出端。

5.根据上述,通过电压追踪电路对施加于n型隔离深阱的输出电压vth的控制,可避免因漏电流所导致的高温度损坏了电子电路中电子器件的情况。

附图说明

6.图1表示本发明一实施例的电子电路。

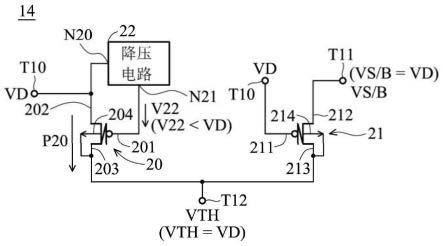

7.图2a~图2c表示根据本发明一实施例,在不同的电压条件下,图1的电压追踪电路的操作示意图。

8.图3表示根据本发明一实施例在图1的电压追踪电路,其内的降压电路具有第一架构。

9.图4表示根据本发明另一实施例在图1的电压追踪电路,其内的降压电路具有第二架构。

10.图5表示根据本发明一实施例在图1的电压追踪电路,其内的降压电路具有第三架构。

11.图6表示本发明另一实施例在图1的电子电路的电压追踪电路。

12.图7表示根据本发明一实施例在图6的电压追踪电路,其内的降压电路具有第一架构。

13.图8表示根据本发明另一实施例在图6的电压追踪电路,其内的降压电路具有第二架构。

14.图9表示根据本发明一实施例在图6的电压追踪电路,其内的降压电路具有第三架构。

15.图10表示图1中高压侧的nmos晶体管的结构剖面图。

16.附图标号

17.1:电子电路

18.10,11:nmos晶体管

19.12:输出入垫

20.13:电感器

21.14:电压追踪电路

22.20,21:pmos晶体管

23.22:降压电路

24.30~32:pmos晶体管

25.40~42:二级管

26.50~52:pmos晶体管

27.60:电阻器

28.100:n型隔离深阱

29.101,111,201,211,301,311,321,501,511,521:栅极

30.102,112,202,212,302,312,322,502,512,522:漏极

31.103,113,203,213,303,313,323,5603,513,523:源极

32.104,114,204,214,304,314,324,504,514,524:基极

33.105:p型阱

34.106:n型阱

35.107:n型掺杂区

36.108:p型掺杂区

37.109:p型阱

38.110:n型隔离深阱

39.gnd:接地端

40.n10:节点

41.n20:输入节点

42.n21:输入节点

43.n30,n31:节点

44.n40,n41:节点

45.n50,n51:节点

46.nbl:n型内埋层

47.p20,p21:电流路径

48.sub:p型衬底

49.t10,t11:电压端

50.t12:输出端

51.v22:控制电压

52.vd:电压

53.vs/b:电压

具体实施方式

54.为使本发明的上述目的、特征和优点能更明显易懂,下文特举一较佳实施例,并配合所附图式,作详细说明如下。

55.图1是表示根据本发明一实施例的电子电路。参阅图1,电子电路1包括位于高压侧的n型金属氧化物半导体(n-type metal oxide semiconductor,nmos)晶体管10(即,高压侧器件)、输出入垫(pad)12、电感器13、以及电压追踪电路14。在一实施例中电子电路1更包括位于低压侧的nmos晶体管11(即,低压侧器件)。在此实施例中,nmos晶体管10与11为n型横向扩散金属氧化物半导体(n-type laterally diffused metal oxide semiconductor,ldmos)晶体管,且各由一n型隔离深阱所包围。在图1中,符号“100”表示包围ldnmos晶体管10的n型隔离深阱,而符号“110”表示包围ldnmos晶体管11的n型隔离深阱。

56.ldnmos晶体管10包括四个电极端101~104,分别为栅极101、漏极102、源极103、以及基极(bulk)104。栅极101接收来自电子电路1中其他器件所产生的信号。漏极102耦接电压追踪电路14的电压端t10。源极103与基极104彼此耦接于节点n10。电压追踪电路14的电压端t11耦接节点n10,即耦接源/基极103/104。ldnmos晶体管11包括四个电极端111~114,分别为栅极111、漏极112、源极113、以及基极114。栅极111接收来自电子电路1中其他器件所产生的信号。漏极112耦接节点n10。源极113与基极114皆耦接于接地端gnd。电感器113耦接于节点n10与输出入垫12之间。

57.参阅图1,电压追踪电路14的电压端t10耦接ldnmos晶体管10的漏极102,其电压端t11耦接ldnmos晶体管10的源/基极103/104。当电子电路1操作时,电压追踪电路14根据漏极102上的电压vd与源/基极103/104上的电压vs/b中具有较高电平的一者,以于输出端t12上产生输出电压vth,换句话说,电压追踪电路14追踪,漏极102上的电压vd与源/基极103/104上的电压vs/b中具有较高电平的一者,且使输出电压vth等于追踪到的电压。因此可知,电压追踪电路14可根据电压vd与vs/b来改变输出电压vth。电压追踪电路14将所产生的输

出电压vth提供至包围ldnmos晶体管10的n型隔离深阱100。在一些情况下,当在输出入垫10发生一过电压事件时,电压vs/b通过电感器13而增加至高于电压vd。此时,通过电压追踪电路14的操作,输出电压vth随着电压vs/b而增加。输出电压vth的增加可关闭与n型隔离深阱100相关的寄生双极晶体管,或者可降低与n型隔离深阱100相关的寄生双极晶体管的导通效能,借此避免或减少漏电流。根据上述,通过电压追踪电路14对施加于n型隔离深阱100的输出电压vth的控制,可避免因漏电流所导致的高温度损坏了电子电路1中电子器件的情况。

58.以下将说明电压追踪电路14的各种实施例与操作。

59.参阅图2a、图2b、图2c,为根据本发明一实施例,电压追踪电路在不同的电压条件下的操作示意图。电压追踪电路14包括p型金属氧化物半导体(n-type metal oxide semiconductor,pmos)晶体管20与21以及降压电路22。pmos晶体管20包括四个电极端201~204,分别为栅极201、漏极202、源极203、以及基极204。漏极202耦接电压端t10,其源极203与基极204耦接输出端t12。降压电路22具有输入节点n20与输出节点n21。输入节点n20耦接电压端t10,且输出节点n21耦接pmos晶体管20的栅极201。pmos晶体管21包括四个电极端211~214,分别为栅极211、漏极212、源极213、以及基极214。栅极211耦接电压端t10,其漏极212耦接电压端t11,其源极213与基极214耦接输出端t12。

60.参阅图2a,当电子电路1操作时,电压追踪电路14通过电源端t10接收电压vd,且通过电源端t11接收电压vs/b。在图2a的实施例中,电压vs/b等于电压vd(vs/b=vd),例如,电压vd与电压vs/b都是44v。此时,pmos晶体管21关闭。降压电路22提供一调节电压。当降压电路22通过输入节点n20接收电压vd时,其执行一降压操作,以借由此调节电压来降低电压vd以于输出节点n21产生控制电压v22。换句话说,降压电路22根据电压vd产生控制电压v22,且控制电压v22小于电压vd(v22《vd),控制电压v22例如为41.9v。此时,pmos晶体管20的栅极201的电压等于控制电压v22。由于控制电压v22小于电压vd,pmos晶体管20导通以提供一电流路径p20。通过电流路径p20,输出端t12上的输出电压vth追随电压vd而增加,最终等于电压vd(vth=vd)。

61.参阅图2b,在一些情况下,电压vs/b小于电压vd(vs/b《vd)(例如,电压vd为44v,而电压vs/b为0v)。此时,pmos晶体管21关闭。降压电路22执行降压操作,以借由调节电压来降低电压vd以于输出节点n21产生控制电压v22。控制电压v22小于电压vd(v22《vd),控制电压v22例如为41.9v。此时,pmos晶体管20的栅极201的电压等于控制电压v22。由于控制电压v22小于电压vd,pmos晶体管20导通以提供一电流路径p20。通过电流路径p20,输出端t12上的输出电压vth追随电压vd而增加,最终等于电压vd(vth=vd)。

62.参阅图2c,在一些情况下,电压vs/b大于电压vd(vs/b》vd)(例如,电压vd为44v,而电压vs/b为46.5v)。降压电路22也进行上述的降压操作。此时,pmos晶体管21导通以提供一电流路径p21。通过电流路径p21,输出端t12上的输出电压vth追随电压vs/b而增加,最终等于电压vs/b(vth=vs/b)。

63.根据上述,电压追踪电路14根据电压vd与电压vs/b中具有较高电平的一者,以在输出端t12上产生输出电压vth。如此一来,输出电压vth是追随电压追踪电路14根据电压vd与电压vs/b中具有较高电平的一者。

64.本案的降压电路22包括多个串接于输入节点n20与输出节点n21之间的多个降压

器件,借此实现降压操作。降压器件有多种实施方式。以下将通过图3~图5来说明降压电路22的详细架构。

65.图3是表示根据本发明另一实施例的电压追踪电路14,其中,降压电路22的第一架构。参阅图3,降压电路22包括串接于输入节点n20与输出节点n21之间的pmos晶体管(降压器件)30~32,实际数量可依照实际需求调整,本发明并不以此为限。pmos晶体管30具有四个电极端301~304,分别为栅极301、漏极302、源极303、以及基极304。漏极302耦接输入节点n20。栅极301、源极303、以及基极304耦接节点n30。pmos晶体管31具有四个电极端311~314,分别为栅极311、漏极312、源极313、以及基极314。漏极312耦接节点n30。栅极311、源极313、以及基极314耦接节点n31。pmos晶体管32具有四个电极端321~324,分别为栅极321、漏极322、源极323、以及基极324。漏极322耦接节点n31。栅极311、源极313、以及基极314耦接输出节点n21。

66.举例而言,当电子电路1操作时,电压追踪电路14通过电源端t10接收电压vd,例如为44v,本发明并不以此为限。此时,pmos晶体管30~32为关断状态。由于pmos晶体管30~32存在寄生二级管,pmos晶体管30~32的每一者具有介于其漏极与源极之间的0.7v跨压。因此,降压电路22的输入节点n20与输出节点n21之间的电压差为2.1v(0.7vx3=2.1v)。介于输入节点n20与输出节点n21之间的电压差(2.1v)则作为降压电路22提供的调节电压。此时,输出节点n21上的控制电压v22为41.9v(44v-2.1v=41.9v),借此实现降压操作,即实现了以调节电压来降低电压vd以于输出节点n21产生控制电压v22。

67.图4是表示根据本发明另一实施例的电压追踪电路14,其中,降压电路22具有第二架构。参阅图4,降压电路22包括串接于输入节点n20与输出节点n21之间的二级管(降压器件)40~42,实际数量可依照实际需求调整,本发明并不以此为限。二级管40的阳极端耦接输入节点n20,且其阴极端耦接节点n40。二级管41的阳极端耦接节点n40,且其阴极端耦接节点n41。二级管42的阳极端耦接节点n41,且其阴极端耦接输出节点n21。

68.举例而言,当电子电路1操作时,电压追踪电路14通过电源端t10接收电压vd,例如为44v,本发明并不以此为限。此时,二级管40~42的每一者提供于其阳极端与阴极端之间的0.7v跨压。因此,降压电路22的输入节点n20与输出节点n21之间的电压差为2.1v(0.7vx3=2.1v)。介于输入节点n20与输出节点n21之间的电压差(2.1v)则作为降压电路22提供的调节电压。此时,输出节点n21上的控制电压v22为41.9v(44v-2.1v=41.9v),借此实现降压操作,即实现了以调节电压来降低电压vd以于输出节点n21产生控制电压v22。

69.图5是表示根据本发明另一实施例的电压追踪电路14,其中,降压电路22具有第三架构。参阅图5,降压电路22包括串接于输入节点n20与输出节点n21之间的pmos晶体管(降压器件)50~52,实际数量可依照实际需求调整,本发明并不以此为限。pmos晶体管50具有四个电极端501~504,分别为栅极501、漏极502、源极503、以及基极504。漏极502耦接输入节点n20。源极503以及基极504耦接节点n50。pmos晶体管51具有四个电极端511~514,分别为栅极511、漏极512、源极513、以及基极514。漏极512耦接节点n50。源极513以及基极514耦接节点n51。pmos晶体管52具有四个电极端521~524,分别为栅极521、漏极522、源极523、以及基极524。漏极522耦接节点n51。源极513以及基极514耦接输出节点n21。pmos晶体管50~53的栅极501、511、以及521接耦接输出端t12。

70.举例而言,当电子电路1操作时,电压追踪电路14通过电源端t10接收电压vd,例如

为44v,本发明并不以此为限。此时,pmos晶体管50~52为关断状态。由于pmos晶体管50~52存在寄生二级管,pmos晶体管50~52的每一者具有介于其漏极与源极之间的0.7v跨压。因此,降压电路22的输入节点n20与输出节点n21之间的电压差为2.1v(0.7vx3=2.1v)。介于输入节点n20与输出节点n21之间的电压差(2.1v)则作为降压电路22提供的调节电压。此时,输出节点n21上的控制电压v22为41.9v(44v-2.1v=41.9v),借此实现降压操作,即实现了以调节电压来降低电压vd以于输出节点n21产生控制电压v22。在此实施例中,由输出端t12上的输出电压vth是追随电压vd与电压vs/b中具有较高电平的一者,因此pmos晶体管50~53的栅极501、511、以及521具有较高的电压,使得pmos晶体管50~53能稳定地维持关断状态。

71.在一些实施例中,电子电路1操作时,为了能让电压追踪电路14中pmos晶体管20的栅极的电压能快速地朝电压vth增加,一电阻器耦接于降压电路22的输出端n21与接地端gnd之间,如图6所示。因此,在图3~图5所示降压电路22的各例子中,电阻器60耦接于降压电路22的输出端n21与接地端gnd之间,分别如图7~图9所示。如图7所示的第一架构,在图3的电压追踪电路更具有一电阻器60,耦接于降压电路22的输出端n21与接地端gnd之间;如图8所示的第二架构,在图4的电压追踪电路更具有一电阻器60,耦接于降压电路22的输出端n21与接地端gnd之间;如图9所示的第三架构,在图5的电压追踪电路更具有一电阻器60,耦接于降压电路22的输出端n21与接地端gnd之间。图6~图9所示的电压追踪电路的操作如前文所述,请参阅图2a~图5的说明。

72.图10是表示图1中高压侧的nmos晶体管10的结构剖面图。参阅图10,nmos晶体管10形成在p型衬底sub上。n型内埋层nbl与p型阱109形成在p型衬底sub内。n型隔离深阱100形成在n型内埋层nbl上,且介于p型阱109之间。p型阱105形成在n型隔离深阱100内。n型阱106形成在p型阱105内,以作为nmos晶体管10的漏极区。与n型阱106电连接的接触电极作为漏极电极102。n型掺杂区107形成在p型阱105内,以作为nmos晶体管10的源极区。p型掺杂区108形成在p型阱105内,以作为nmos晶体管10的基极区。分别与n型掺杂区107以及p型掺杂区108电连接的接触电极作为源极103与基极104。由于源极103与基极104彼此连接,图10仅显示单一接触电极。在p型阱105上形成栅极介电层与栅极层,且与栅极层电连接的接触电极作为栅极101。

73.根据图10的架构,存在数个寄生双极晶体管,包括形成在n型隔离深阱100、p型阱105、与n型阱106之间的寄生npn双极晶体管lnpn、形成在p型阱105、n型隔离深阱100、与p型阱109之间的寄生pnp双极晶体管lpnp、形成在n型阱106、p型阱105、与n型内埋层nbl之间的寄生npn双极晶体管vnpn、以及形成在p型阱105、n型内埋层nbl、与p型衬底sub之间的寄生pnp双极晶体管vpnp。

74.如图10所示,n型隔离深阱100未与漏极102连接在一起。n型隔离深阱100的电压与漏极102的电压各自独立。根据上述电压追踪电路14的操作,其所产生的控制电压vth是为电压vd与电压vs/b中具有较高电平的一者。借由施加控制电压vth至n型隔离深阱100,避免寄生二级管导通,举例而言,寄生二级管包括npn双极晶体管lnpn、寄生pnp双极晶体管lpnp、寄生npn双极晶体管vnpn、或寄生pnp双极晶体管vpnp,但本发明并不以此为限。在一实施例中,上述寄生二级管皆未导通。举例而言,当电压vs/b大于电压vd的情况下,由于电压追踪电路14产生与电压vs/b相等的控制电压vth,使得n型隔离深阱100与n型内埋层nbl

的电压接近或等于。因此,寄生npn双极晶体管vnpn与寄生pnp双极晶体管vpnp未导通,减少了经过衬底漏电流。

75.虽然本发明已以较佳实施例所述如上,但其并非用以限定本发明,任何本领域技术人员,在不脱离本发明的精神和范围内,当可作更动与修饰,因此本发明的保护范围当视前附的权利要求范围所界定者为准。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。