一种ram芯片的测试方法

技术领域

1.本发明涉及芯片测试技术领域,尤其涉及一种ram芯片的测试方法。

背景技术:

2.ram芯片是与cpu直接交换数据的内部存储器,通常作为操作系统或其他正在运行中的程序的临时数据存储介质。ram芯片已成为电子电路的常用品,其ram芯片的性能优良决定了整个电路的优良,因此对ram芯片的性能测试显的尤为重要。

3.现在测试ram芯片的方法不多,一般测试ram芯片的方法通常设置ram芯片的最差情形,它可以很快地保证器件满足设计规范,但是在有fail出现时无法直观地显示错误的来源或原因,即go-nogo测试,这种测试方法的特点是无法精确地记录芯片的测试结果。

技术实现要素:

4.为了克服现有技术的不足,本发明的目的在于提供一种ram芯片的测试方法,其能精确地记录ram芯片的测试结果。

5.本发明的目的采用以下技术方案实现:

6.一种ram芯片的测试方法,其特征在于,包括:

7.步骤a、在直流电下,通过参数测量模块对待测ram芯片进行io管脚通断测试,钳位电流下的性能测试,钳位电压下的性能测试;

8.步骤b、通过ram芯片的器件规格书中的各时序参数确定测试周期,再通过测试程序和所述测试周期生成测试向量;

9.步骤c、在交流电下,使用功能测试系统根据所述测试向量生成激励信号传输给被测ram芯片,并通过所述功能测试系统分析ram芯片输出的响应信号与期望信号在整个时序上是否一致,并得出测试结果;

10.步骤d、通过功能测试系统把测试结果传输给fpga芯片,而进行储存和进一步分析。

11.进一步地,在所述步骤a中,所述参数测量模块包括pmu单元、驱动单元和用于给待测ram芯片电源管脚供电的dps单元,所述pmu单元通过所述驱动单元与待测ram芯片电性连接。

12.进一步地,在所述步骤b中,所述测试周期包括写入数据周期和读取数据周期,所述测试向量包括与所述写入数据周期相对应的写周期时序和与所述读取数据周期相对应的读周期时序。

13.进一步地,在所述步骤c中,所述功能测试系统包括向量存储器、时序生成模块、驱动器模块、边沿信号发生器和时序控制模块,所述时序生成模块、所述边沿信号发生器和所述时序控制模块均分别信号连接所述向量存储器,所述时序生成模块通过所述驱动器模块与所述边沿信号发生器信号连接,所述向量存储器、所述时序生成模块和所述边沿信号发生器均分别与所述时序控制模块信号连接。

14.进一步地,所述向量存储器包括依次信号连接的输入数据单元、工作模式单元和输出状态单元。

15.进一步地,所述驱动器模块包括相互信号连接的输入驱动单元和输出驱动单元。

16.进一步地,所述输入驱动单元包括相互电连接的高低电平选择器和i/o开关,所述输出驱动单元包括并列的高电平放大器和低电平放大器,所述时序生成模块、所述高电平放大器和所述低电平放大器均电连接所述i/o开关。

17.进一步地,所述时序生成模块包括周期信号发生器,所述周期信号发生器的最大频率为100mhz。

18.进一步地,所述工作模式单元包括读数据模式、写数据模式和跳过模式。

19.进一步地,在所述步骤a中,所述电流钳位值为2ua、20ua、200ua或者2ma。

20.相比现有技术,本发明的有益效果在于:

21.本方法先在直流电下通过参数测量模块对待测ram芯片进行io管脚通断测试,电流钳位值的测试,电压钳位值的测试,再在交流电下对待测ram芯片进行功能测试,这样使用两种电流对ram芯片进行测试,可以全面的测试ram芯片的性能,且所述功能测试系统能对ram芯片输出的响应信号进行整个时序上的精确对比和分析,而可以精确地记录和分析ram芯片的测试结果;

22.最后通过功能测试系统把测试信息传输给fpga芯片,而可以进一步地精确记录和分析ram芯片的测试结果。

附图说明

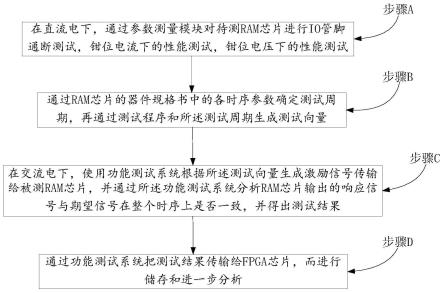

23.图1为本发明的ram芯片的测试方法的流程图;

24.图2为本发明的参数测量模块的功能示意图;

25.图3为本发明的功能测试系统的功能示意图。

具体实施方式

26.为了能够更清楚地理解本发明的具体技术方案、特征和优点,下面结合附图和具体实施方式对本发明进行进一步的详细描述。

27.如图1所示,本技术公开了一种ram芯片的测试方法,其特征在于,包括:

28.步骤a、在直流电下,通过参数测量模块对待测ram芯片进行io管脚通断测试,钳位电流下的性能测试,钳位电压下的性能测试;

29.在上述步骤中,所述参数测量模块包括pmu单元、驱动单元和用于给待测ram芯片电源管脚供电的dps单元,所述pmu单元通过所述驱动单元与待测ram芯片电性连接。所述pmu是一种高度集成的、针对便携式应用的电源管理方案,即将传统分立的若干电源管理器件整合在单个的封装之内,这样可实现更高的电源转换效率、更低功耗和更高集成度。所述pmu单元能满足被测ram芯片进行参数测试的功能要求通过设置内部寄存器可以选择不同的测量模式。所述驱动单元能把所述pmu单元输出的电压信号、电流信号或波形信号转换成适合ram芯片的信号。

30.如图2所示,所述pmu单元能长时间输出很稳定的钳位电流信号给待测ram芯片的io管脚,并能接收ram芯片输出的反馈信号,所述pmu单元或者用户可以通过反馈信号与期

望信号进行对比,而得出被测ram芯片(包括io管脚)在钳位电流持续通电状态下的性能好坏。同理,也可以通过该方法测试被测ram芯片在钳位电压下的性能。其中,所述电流钳位值最优为2ua、20ua、200ua或者2ma。

31.步骤b、通过ram芯片的器件规格书中的各时序参数确定测试周期,再通过测试程序和所述测试周期生成测试向量;

32.在上述步骤中,ram芯片的器件规格书中一般包括读时序参数trc、写时序参数twc和片选写时序参数tscs等,所述写入数据周期=ntwc,所述读入数据周期=ntrc,其中,n为正整数,所述测试周期包括写入数据周期和读取数据周期,所述测试向量包括与所述写入数据周期相对应的写周期时序和与所述读取数据周期相对应的读周期时序。所述测试程序为能把所述写入数据周期和所述读取数据周期分别仿真成写周期时序和读周期时序的仿真程序。

33.其中,所述测试向量包括写周期时序以及相对应的写时序数据和读周期时序以及相对应的读时序数据。

34.步骤c、在交流电下,使用功能测试系统根据所述测试向量生成激励信号传输给被测ram芯片,并通过所述功能测试系统分析ram芯片输出的响应信号与期望信号在整个时序上是否一致,并得出测试结果;

35.如图3所示,在所述步骤c中,所述功能测试系统包括向量存储器、时序生成模块、驱动器模块、边沿信号发生器和时序控制模块,所述时序生成模块、所述边沿信号发生器和所述时序控制模块均分别信号连接所述向量存储器,所述时序生成模块通过所述驱动器模块与所述边沿信号发生器信号连接,所述向量存储器、所述时序生成模块和所述边沿信号发生器均分别与所述时序控制模块信号连接。

36.其中,所述向量存储器根据所述测试向量生成写时序数据或者读时序数据给所述时序生成模块时,所述时序生成模块根据写时序数据或者读时序数据输出相应对的写数据时序或者读数据时序,生成的写数据时序或者读数据时序再通过所述驱动器模块进行高低电平的调整,适合测试ram芯片的激励信号,所述驱动器模块再把所述激励信号传输给待测ram芯片,所述ram芯片在激励信号的基础上输出响应信号,由于线路的长度,原响应信号的时序与期望信号的时序并不一致,所述响应信号再经过所述边沿信号发生器进行边沿波形的整合(边沿波形少的增加边沿波形,边沿波形多的减少边沿波形),而使响应信号的时序与期望信号的时序一致,所述边沿信号发生器再把时序一致的响应信号传输给向量存储器或者fpga,而利于响应信号与期望信号在整个时序内进行精确地分析对比,如果响应信号与期望信号不一致,表明功能测试失败,否则表明功能测试成功,并且所述向量存储器生成测试结果,并保存测试结果以供记录。

37.优选的,所述向量存储器包括依次信号连接的输入数据单元、工作模式单元和输出状态单元。所述工作模式单元包括读数据模式、写数据模式和跳过模式。所述向量存储器存储用于测试的写时序数据或者读时序数据和期望值,所述期望值包括逻辑信号、指令代码、时钟周期、信号时序波形等。一般所述期望值存储在所述输出状态单元内,所述输出状态单元能把期望值输出给所述边沿信号发生器,是否输出写时序数据或者读时序数据由所述工作模式单元决定。

38.优选的,所述驱动器模块包括相互信号连接的输入驱动单元和输出驱动单元。所

述输入驱动单元包括相互电连接的高低电平选择器和i/o开关,所述输出驱动单元包括并列的高电平放大器和低电平放大器,所述时序生成模块、所述高电平放大器和所述低电平放大器均电连接所述i/o开关。所述时序生成模块与所述输入驱动单元信号连接,所述高低电平选择器能把输入的写时序数据或者读时序数据整合成ram芯片所兼容的高低电平信号;所述i/o开关控制高低电平信号的输入或者输出,所述时序生成模块可以直接把写时序数据或者读时序数据通过所述i/o开关传输给ram芯片;所述输出驱动单元能把ram芯片输出的响应信号整合成高低电平的响应信号。

39.其中,所述时序生成模块包括周期信号发生器,所述周期信号发生器的最大频率为100mhz。该周期信号发生器能根据所述边沿信号发生器中的期望值生成期望信号,而与响应信号进行比较。

40.步骤d、通过功能测试系统把测试结果传输给fpga芯片,而进行储存和进一步分析。

41.在上述步骤中,所述测试结果包括步骤c中的成功或者失败信息以及期望信号和响应信号,所述fpga芯片可通过仿真软件对测试结果进行进一步地分析,便于记录和整理测试结果。

42.综述,本方法先在直流电下通过参数测量模块对待测ram芯片进行io管脚通断测试,电流钳位值的测试,电压钳位值的测试,再在交流电下对待测ram芯片进行功能测试,这样使用两种电流对ram芯片进行测试,可以全面的测试ram芯片的性能,且所述功能测试系统能对ram芯片输出的响应信号进行整个时序上的精确对比和分析,而可以精确地记录和分析ram芯片的测试结果;最后通过功能测试系统把测试信息传输给fpga芯片,而可以进一步地精确记录和分析ram芯片的测试结果。

43.可以理解地,本ram芯片的测试方法也可以测试其他芯片。

44.以上显示和描述了本发明的基本原理、主要特征和优点。本行业的技术人员应该了解,本发明不受上述实施例的限制,上述实施例和说明书中的描述的只是说明本发明的原理,在不脱离本发明精神和范围的前提下,本发明还会有各种变化和改进,这些变化和改进都落入要求保护的本发明范围内。本发明要求保护范围由所附的权利要求书及其等效物界定。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。