基于dsp芯片的实时时钟信息读取电路及变频控制器

技术领域

1.本实用新型涉及电子电路领域,尤其涉及一种基于dsp芯片的实时时钟信息读取电路及变频控制器。

背景技术:

2.本部分旨在为权利要求书中陈述的本实用新型实施例提供背景或上下文。此处的描述不因为包括在本部分中就承认是现有技术。

3.dsp芯片作为变频器的主控制芯片,能够利用集成程序包实现各种复杂算法,具有开发周期短的优点。现有技术中在读取时钟信息时需要利用dsp芯片内置的spi总线或者localbus总线、专用存储总线对时钟信息进行获取。但是,这一方法需要耗费大量的数据、地址信号线,占用了dsp芯片宝贵的外部管脚,同时,在电路板布线过程中需要对信号线的长度、排列位置进行细致处理,容易出现信号干扰,导致读取信息的错误。

4.因而,亟需一种可以克服上述问题的实时时钟信息读取方案。

技术实现要素:

5.本实用新型实施例中提供了一种基于dsp芯片的实时时钟信息读取电路,用以在cpu启动初始化过程中实现实时时钟信息的读取,该基于dsp芯片的实时时钟信息读取电路包括:dsp芯片和i2c总线实时时钟芯片;其中,所述i2c总线实时时钟芯片与所述dsp芯片连接,用于向dsp芯片提供实时时钟信息。

6.进一步地,所述i2c总线实时时钟芯片为pcf8563ts\5芯片;所述dsp芯片为tms320f28232芯片。

7.进一步地,所述tms320f28232芯片包括:sdaa数据信号管脚和scla时钟信号管脚;所述pcf8563ts\5芯片包括:sda数据信号管脚和scl时钟信号管脚;其中,所述tms320f28232芯片的sdaa数据信号管脚与所述pcf8563ts\5芯片的sda数据信号管脚连接;所述tms320f28232芯片的scla时钟信号管脚与所述pcf8563ts\5芯片的scl时钟信号管脚连接。

8.进一步地,基于dsp芯片的实时时钟信息读取电路还包括:石英晶体谐振器,与所述pcf8563ts\5芯片连接,用于提供时间日期时钟校正信息。

9.进一步地,基于dsp芯片的实时时钟信息读取电路还包括:纽扣电池,与所述pcf8563ts\5芯片连接,用于在外部供电中断时为pcf8563ts\5芯片供电。

10.本实用新型实施例中还提供了一种变频控制器,用以在cpu启动初始化过程中实现实时时钟信息的读取,该变频控制器包括:上述的基于dsp芯片的实时时钟信息读取电路。

11.进一步地,变频控制器还包括:fpga芯片,与dsp芯片连接,用于将dsp芯片输出的控制信号并行传输到多个外部变频设备。

12.进一步地,变频控制器还包括:外部扩展板,与fpga芯片连接,用于扩展出各种现

场总线或以太网总线。

13.进一步地,变频控制器还包括:中断信号传输接口,与fpga芯片连接,用于传输中断信号。

14.进一步地,fpga芯片用于扩展出如下任意一种接口:rs485总线接口、can总线接口、rs232总线接口、ssi编码器信号接口、增量编码器信号接口、数字量输入信号接口、数字量输出信号接口、模拟量输入信号接口和模拟量输出信号接口。

15.进一步地,变频控制器还包括:usb接口,与dsp芯片连接,用于与外部usb设备通信;usb-ttl,与dsp芯片连接,用于将usb数据转换为ttl数据。

16.进一步地,变频控制器还包括:cf卡接口,与dsp芯片连接,用于将数据存储至外部cf卡中或读取外部cf卡中的数据。

17.进一步地,变频控制器还包括:数码管驱动芯片和数码管;其中,数码管驱动芯片与dsp芯片连接,用于驱动数码管点亮或熄灭;数码管用于显示变频控制器的状态信息。

18.进一步地,变频控制器还包括:rtc时钟芯片,与dsp芯片连接,用于提供时钟信号。

19.进一步地,变频控制器还包括:ddr内存和mmc存储器;其中,ddr内存,与dsp芯片连接,用于存储内存数据;mmc存储器,与dsp芯片连接,用于存储数据。

20.本实用新型实施例中提供的基于dsp芯片的实时时钟信息读取电路及变频控制器,通过i2c总线实时时钟芯片与dsp芯片连接从而向dsp芯片提供实时时钟信息,从而在cpu启动初始化过程中实现实时时钟信息的读取,来对cpu时钟进行校准。

附图说明

21.为了更清楚地说明本实用新型实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本实用新型的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。在附图中:

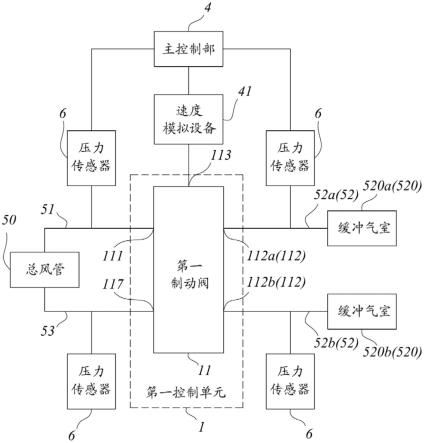

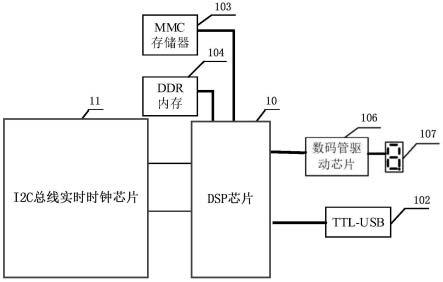

22.图1为本实用新型实施例中一种基于dsp芯片的实时时钟信息读取电路示意图;

23.图2为本实用新型实施例中一种tms320f28232芯片信号管脚示意图;

24.图3为本实用新型实施例中一种pcf8563ts\5芯片信号管脚示意图;

25.图4为本实用新型实施例中一种变频控制器示意图。

具体实施方式

26.为使本实用新型实施例的目的、技术方案和优点更加清楚明白,下面结合附图对本实用新型实施例做进一步详细说明。在此,本实用新型的示意性实施例及其说明用于解释本实用新型,但并不作为对本实用新型的限定。

27.本实用新型实施例中提供了一种基于dsp芯片的实时时钟信息读取电路,图1为本实用新型实施例中一种基于dsp芯片的实时时钟信息读取电路示意图,如图1所示,该实时时钟信息读取电路包括:dsp芯片10和i2c总线实时时钟芯片11;

28.其中,所述i2c总线实时时钟芯片11与所述dsp芯片10连接,用于向dsp芯片10提供实时时钟信息。

29.在一个实施例中,本实用新型实施例中提供的实时时钟信息读取电路中,i2c总线

实时时钟芯片11采用pcf8563ts\5芯片;所述dsp芯片10采用tms320f28232芯片。tms320f28232芯片一款高端dsp芯片,可以运行实时操作系统。pcf8563ts\5芯片为i2c总线实时时钟芯片,可以将实时时钟信息传输到dsp芯片中。

30.图2示出了本实用新型实施例中提供的一种dsp芯片的信号管脚,tms320f28232芯片的部分信号管脚定义如表1所示。图3示出了本实用新型实施例中提供的一种pcf8563ts\5芯片的信号管脚,pcf8563ts\5芯片的部分信号管脚定义如表2所示。

31.表1

32.序号管脚号名称含义174sdaa数据信号275scla时钟信号

33.表2

34.序号管脚号名称含义11osci无源晶振输入22osco无源晶振输出33int#中断信号44vss电源地55scl时钟信号66sda数据信号77clkout时钟输出信号88vdd电源正

35.在本实施例中,tms320f28232芯片包括:sdaa数据信号管脚和scla时钟信号管脚;pcf8563ts\5芯片包括:sda数据信号管脚和scl时钟信号管脚;其中,tms320f28232芯片的sdaa数据信号管脚与pcf8563ts\5芯片的sda数据信号管脚连接;tms320f28232芯片的scla时钟信号管脚与pcf8563ts\5芯片的scl时钟信号管脚连接。

36.在本实施例中,基于dsp芯片的实时时钟信息读取电路还包括:石英晶体谐振器12,与pcf8563ts\5芯片连接,用于提供时间日期时钟校正信息。

37.具体实施时,石英晶体谐振器12两端分别与pcf8563ts\5芯片的osci无源晶振输入管脚和osco无源晶振输出管脚连接。石英晶体谐振器采用32.768khz,为pcf8563ts\5芯片提供精准的时间日期时钟校正信息,从而使得芯片的时钟抖动减少,时钟漂移更小,定时更加准确。

38.在本实施例中,基于dsp芯片的实时时钟信息读取电路还包括:两个电容,分别与pcf8563ts\5芯片的osci无源晶振输入管脚和osco无源晶振输出管脚连接,所述电容可以为15pf电容,用于滤除石英晶体谐振器两端的电压波动。

39.在本实施例中,基于dsp芯片的实时时钟信息读取电路还包括:纽扣电池13,与所述pcf8563ts\5芯片连接,用于在外部供电中断时为pcf8563ts\5芯片供电。

40.具体实施时,pcf8563ts\5芯片的vdd管脚由纽扣电池和外部供电(3.3v)同时供电,当外部3.3v供电正常时,由外部3.3v为pcf8563ts\5芯片供电。当外部供电中断时,pcf8563ts\5芯片由纽扣电池供电。

41.在本实施例中,基于dsp芯片的实时时钟信息读取电路还包括:第一二极管,第二

二极管和电阻,所述第一二极管连接在pcf8563ts\5芯片的vdd管脚和外部3.3v供电之间,所述第二二极管与电阻连接后连接在pcf8563ts\5芯片的vdd管脚和纽扣电池之间。电阻(可以为1kω)用来限制纽扣电池的输出电流,同时也使得纽扣电池在vdd管脚输出的电压,比3.3v线路的供电电压稍低一些,从而实现了优先有外部3.3v供电的功能。二极管的工作目的是防止外部3.3v给纽扣电池供电,也防止纽扣电池给外部3.3v供电,实现了2路供电线路之间的供电隔离。

42.在本实施例中,基于dsp芯片的实时时钟信息读取电路还包括:第一电容,第二电容,分别连接在pcf8563ts\5芯片的vdd管脚。电容分别为10uf和0.1uf,使得vdd电源更加稳定,也减少了3.3v外部供电突然消失,导致的电压波动,使得纽扣电池输出电流更加平稳,延长了纽扣电池的寿命。

43.图4为本实用新型实施例中一种变频控制器示意图,如图4所示,本实用新型实施例中还提供了一种变频控制器,包括:上述任一项的基于dsp芯片的实时时钟信息读取电路。

44.在一个实施例中,本实用新型实施例中提供的变频控制器还包括:fpga芯片20,与dsp芯片10连接,用于将dsp芯片10输出的控制信号并行传输到多个外部变频设备。

45.在一个实施例中,本实用新型实施例中提供的变频控制器还包括:usb接口101,用于与外部usb设备通信;usb-ttl102,与所述dsp芯片10连接,用于将usb数据转换为ttl数据。

46.在一个实施例中,本实用新型实施例中提供的变频控制器还包括:ddr内存104和mmc存储器103;其中,ddr内存104,与dsp芯片10连接,用于存储内存数据;mmc存储器103,与dsp芯片10连接,用于存储数据。可选地,mmc存储器可以是mmc卡,通过mmc卡实现板载的数据存储,对于系统校验和加密数据,都需要保存在mmc卡中。由于mmc卡的读写速度快于cf卡读写,因此紧急保持的数据,可以存储在mmc卡中。本实用新型实施例提供的变频控制器中,dsp芯片通过ddr的的方式扩展ram,实现了大批量内存数据的存储和运算,支持当前各种主流ddr总线。

47.本实用新型实施例提供的变频控制器可以采用24v直流供电,通过底部的电源接口211与外部电源连接。可选地,电源接口211可以是电源端子。

48.在一个实施例中,本实用新型实施例中提供的变频控制器还包括:cf卡接口105,与dsp芯片10连接,用于将数据存储至外部cf卡中或读取外部cf卡中的数据。通过将dsp芯片扩展出cf卡存储功能,将系统数据或用户数据存储在cf卡中,能够方便通过cf卡进行系统和程序升级。

49.在一个实施例中,本实用新型实施例中提供的变频控制器还包括:数码管驱动芯片106和数码管107;其中,数码管驱动芯片106与dsp芯片10连接,用于驱动数码管107点亮或熄灭;数码管107用于显示变频控制器的状态信息。可选地,数码管107为一个8位led数码管,用来显示当前控制器状态,方便用户判断当前控制器内部软件的情况。可选地,数码管驱动芯片106可以是74hc595d串转并芯片,将dsp芯片的串行信号转换为驱动led数码管的并行信号。

50.在一个实施例中,本实用新型实施例中提供的变频控制器还包括:外部扩展板201,与fpga芯片20连接,用于扩展出各种现场总线或以太网总线。fpga芯片通过内部总线

扩展了外部扩展板,可以实现各种现场总线、实时以太网总线的支持,增强了系统的扩展性。

51.在一个实施例中,本实用新型实施例中提供的变频控制器还包括:中断信号传输接口212,与fpga芯片20连接,用于传输中断信号。

52.在一个实施例中,本实用新型实施例中提供的变频控制器中,fpga芯片20还可以用于扩展出如下任意一种接口can总线接口202、rs485总线接口203、rs232总线接口204、ssi编码器信号接口205、增量编码器信号接口206、数字量输入信号接口208、数字量输出信号接口207、模拟量输入信号接口210和模拟量输出信号接口209、电源接口211。通过扩展多种通信协议的数据传输接口,实现多通信协议的协调统一操作。其中,fpga芯片通过塑料光纤或者玻璃光纤的方式,扩展出接收或发送快速中断信号的中断信号传输接口,实现多个控制器之间的数据同步和信号同步。dsp芯片还支持中断触发功能,以便实现快速信号的紧急处理。

53.综上所述,本实用新型实施例中提供的基于dsp芯片的实时时钟信息读取电路及变频控制器,通过i2c总线实时时钟芯片与dsp芯片连接从而向dsp芯片提供实时时钟信息,从而在cpu启动初始化过程中实现实时时钟信息的读取,来对cpu时钟进行校准。本实用新型实施例仅仅通过2路信号线,在cpu启动的初始化过程中实现了读取实时时钟信息,来对cpu时钟进行校准。电路板停止供电后,采用纽扣电池对实时时钟芯片进行供电,保存当前时间和日期。同时,待机功率小,有助于延长纽扣电池供电的时间和寿命。

54.本领域内的技术人员应明白,本实用新型的实施例可提供为方法、系统、或计算机程序产品。因此,本实用新型可采用完全硬件实施例、完全软件实施例、或结合软件和硬件方面的实施例的形式。而且,本实用新型可采用在一个或多个其中包含有计算机可用程序代码的计算机可用存储介质(包括但不限于磁盘存储器、cd-rom、光学存储器等)上实施的计算机程序产品的形式。

55.本实用新型是参照根据本实用新型实施例的方法、设备(系统)、和计算机程序产品的流程图和/或方框图来描述的。应理解可由计算机程序指令实现流程图和/或方框图中的每一流程和/或方框、以及流程图和/或方框图中的流程和/或方框的结合。可提供这些计算机程序指令到通用计算机、专用计算机、嵌入式处理机或其他可编程数据处理设备的处理器以产生一个机器,使得通过计算机或其他可编程数据处理设备的处理器执行的指令产生用于实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能的装置。

56.这些计算机程序指令也可存储在能引导计算机或其他可编程数据处理设备以特定方式工作的计算机可读存储器中,使得存储在该计算机可读存储器中的指令产生包括指令装置的制造品,该指令装置实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能。

57.这些计算机程序指令也可装载到计算机或其他可编程数据处理设备上,使得在计算机或其他可编程设备上执行一系列操作步骤以产生计算机实现的处理,从而在计算机或其他可编程设备上执行的指令提供用于实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能的步骤。

58.以上所述的具体实施例,对本实用新型的目的、技术方案和有益效果进行了进一

步详细说明,所应理解的是,以上所述仅为本实用新型的具体实施例而已,并不用于限定本实用新型的保护范围,凡在本实用新型的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本实用新型的保护范围之内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。