1.本发明涉及数据处理技术领域,尤其涉及电压序列数据缓存方法及系统。

背景技术:

2.在数据处理领域,数据缓存是常见的数据处理方式,对于种类单一的数据流,只需要简单的储存以及读取就可以满足数据处理的一般要求。

3.随着数据种类的日趋复杂化,数据缓存技术越来越普及,数据流也从单一化转变为多元化,对于一些特定的多元化数据流,传统的数据缓存方式已无法满足多元化数据流的应用场景。

4.因此,针对特定的数据流,需要提出一种新的数据缓存方法。

技术实现要素:

5.本发明提供电压序列数据缓存方法及系统,用以解决现有技术中针对特定电压数据没有针对性数据缓存方法的缺陷。

6.第一方面,本发明提供一种电压序列数据缓存方法,包括:

7.缓存原始电压数据;

8.将所述原始电压数据中的控制指令数据和电压序列数据进行分离并分别进行缓存;

9.基于预设拼位处理后的控制指令数据对所述电压序列数据进行读操作,将所述电压序列数据重新排序并进行写操作,输出新的电压序列数据。

10.根据本发明提供的电压序列数据缓存方法,所述缓存原始电压数据,之前还包括:

11.采集获取所述原始电压数据。

12.根据本发明提供的电压序列数据缓存方法,所述缓存原始电压数据,包括:

13.将通过以太网口接收对应媒体存取控制位址mac地址的原始电压数据,缓存至芯片内部的随机存取存储器ram中。

14.根据本发明提供的电压序列数据缓存方法,所述将所述原始电压数据中的控制指令数据和电压序列数据进行分离并分别进行缓存,包括:

15.提取所述控制指令数据,分别获取所述原始电压数据中每个控制指令数据之前的数据个数,将每个控制指令数据与对应的数据个数进行拼位,分别缓存至ram中;

16.将所述电压序列数据中的各通道电压值以及延时值按照原有顺序缓存至先进先出fifo存储器中。

17.根据本发明提供的电压序列数据缓存方法,所述将所述原始电压数据中的控制指令数据和电压序列数据进行分离并分别进行缓存,还包括:

18.若所述电压序列数据中最后一个控制指令数据之后还包括若干电压序列数据,则采用预设补齐控制指令和对应的数据个数进行拼位,并缓存至ram中。

19.根据本发明提供的电压序列数据缓存方法,所述基于预设拼位处理后的控制指令

数据对所述电压序列数据进行读操作,将所述电压序列数据重新排序并进行写操作,输出新的电压序列数据,包括:

20.依次读取ram中经过拼位处理的控制指令数据,以及fifo存储器中对应的数据长度;

21.基于所述控制指令数据中的各通道开关状态以及各通道电压值,对所述电压序列数据进行取值和重新排序,得到写操作后的电压序列数据;

22.将所述写操作后的电压序列按照各通道分别存入多个ram中,得到所述新的电压序列数据。

23.第二方面,本发明还提供一种电压序列数据缓存系统,包括:

24.缓存模块,用于缓存原始电压数据;

25.分离模块,用于将所述原始电压数据中的控制指令数据和电压序列数据进行分离并分别进行缓存;

26.处理模块,用于基于预设拼位处理后的控制指令数据对所述电压序列数据进行读操作,将所述电压序列数据重新排序并进行写操作,输出新的电压序列数据。

27.第三方面,本发明还提供一种电子设备,包括存储器、处理器及存储在存储器上并可在处理器上运行的计算机程序,所述处理器执行所述程序时实现如上述任一种所述电压序列数据缓存方法的步骤。

28.第四方面,本发明还提供一种非暂态计算机可读存储介质,其上存储有计算机程序,该计算机程序被处理器执行时实现如上述任一种所述电压序列数据缓存方法的步骤。

29.第五方面,本发明还提供一种计算机程序产品,包括计算机程序,所述计算机程序被处理器执行时实现如上述任一种所述电压序列数据缓存方法的步骤。

30.本发明提供的电压序列数据缓存方法及系统,针对带有不同通道数据以及控制指令的电压数据流,采用分离缓存通道数据以及控制指令,根据控制指令的位置和状态对分离后的数据进行重排序,输出各通道对应的电压序列数据,增加了电压序列数据的易读取性和可操作性。

附图说明

31.为了更清楚地说明本发明或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作一简单地介绍,显而易见地,下面描述中的附图是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

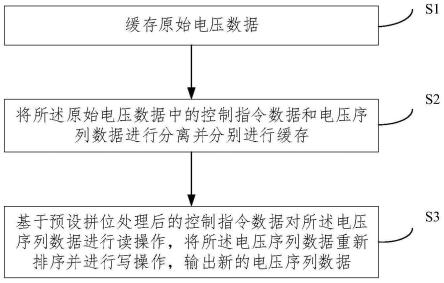

32.图1是本发明提供的电压序列数据缓存方法的流程示意图之一;

33.图2是本发明提供的电压序列数据缓存方法的流程示意图之二;

34.图3是本发明提供的电压序列数据缓存实施例示意图;

35.图4是本发明提供的电压序列数据缓存系统的结构示意图;

36.图5是本发明提供的电子设备的结构示意图。

具体实施方式

37.为使本发明的目的、技术方案和优点更加清楚,下面将结合本发明中的附图,对本

发明中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

38.本发明针对芯片中多通道的电压序列数据,该电压序列数据包含了电压数据本身、延时设置控制指令、通道控制指令和开始结束控制指令等数据,该电压序列数据包含多种数据类型,无法采用传统的针对单一数据进行缓存处理的数据缓存方法。因此,本发明提出新的电压序列数据缓存方法。

39.图1是本发明提供的电压序列数据缓存方法的流程示意图之一,如图1所示,包括:

40.s1,缓存原始电压数据;

41.s2,将所述原始电压数据中的控制指令数据和电压序列数据进行分离并分别进行缓存;

42.s3,基于预设拼位处理后的控制指令数据对所述电压序列数据进行读操作,将所述电压序列数据重新排序并进行写操作,输出新的电压序列数据。

43.具体地,首先将带有控制指令的电压数据里,按照原有顺序全部缓存,在不打乱原有电压数据顺序的基础上分离出控制指令数据和电压序列数据两大部分数据再次进行缓存。

44.此处,控制指令数据缓存的内容除了指令以外还记录了在序列中该控制指令前面的数据个数。当执行读操作时,依次按照每个控制指令数据缓存记录的数据个数,将对应的电压序列缓存数据分段,一段一段进行读取,且不能改变顺序。然后,将读取出来的电压序列数据按照各控制指令数据中的各通道开关状态以及电压序列中数据的通道号进行重新排序,构成每个通道的电压序列,输出最后得到的新的电压序列数据。

45.本发明针对特定的电压序列数据进行缓存及排序,采用分离缓存以及重排序的方式,分离缓存通道数据以及控制指令,根据控制指令的位置以及状态对分离后的数据进行重排序,组成多组新的电压序列数据。

46.在上述实施例的基础上,所述缓存原始电压数据,之前还包括:

47.采集获取所述原始电压数据。

48.具体地,如图2所示,首先进行原始电压数据的采集,将采集的原始电压数据进行缓存,然后再将缓存的原始电压数据进行分离,分别得到控制指令数据和电压序列数据,分别进行缓存。进一步地,对控制指令数据经过读控制器执行读操作,使电压序列数据按照控制指令数据的控制信息进行重新排序和取值,得到多个通道输出的电压序列数据。

49.本发明针对带有不同通道数据以及控制指令的电压数据流,采用分离缓存通道数据以及控制指令,根据控制指令的位置和状态对分离后的数据进行重排序,输出各通道对应的电压序列数据,增加了电压序列数据的易读取性和可操作性。

50.在上述实施例的基础上,所述缓存原始电压数据,包括:

51.将通过以太网口接收对应媒体存取控制位址mac地址的原始电压数据,缓存至芯片内部的随机存取存储器ram中。

52.需要说明的是,本发明采用16进制表示数据和指令,其中,指令一种有12种,每条指令数据中,高4位给出指令种类,低20位则对应于指令的具体数据,数据格式如下:

53.000000空命令;

54.xabcde设置第x个通道的电压,电压大小由abcde指定;

55.c000ab启动电压输出,通道编号由低8位数据ab指定,如10000111表示启动1,2,3,8四个通道;

56.dabcde等待abcde个时钟周期(时钟频率以具体设计为准);

57.f00000结束运行。

58.以一组简单的原始电压数据为例,依据上述数据格式,包括:[0x000000,0xd0000a(等10个时钟周期),0x10ffff(设置1通道电压),0x2ddddd(设置2通道电压),0xc00003(输出1、2通道),0xdfffff(等0xfffff个时钟周期),0xd000dd(等0xdd个时钟周期),0x100000(设置1通道电压),0x2eeeee(设置2通道电压),0xc00001(输出1通道),0xd000ff(等0xff个时钟周期),0xf00000(结束指令)]。

[0059]

如图3所示,首先通过以太网口接收对应mac(media access control address,媒体存取控制位址)地址的数据包,并将采集到的原始数据缓存到芯片内部的ram(random access memory,随机存取存储器)中,如图3中步骤(1)所示。

[0060]

本发明采用16进制数据格式表示电压序列数据,有效区分指令数据、延时指令数据和电压数据等数据类型,便于后续进行分组提取数据和缓存数据。

[0061]

在上述实施例的基础上,所述将所述原始电压数据中的控制指令数据和电压序列数据进行分离并分别进行缓存,包括:

[0062]

提取所述控制指令数据,分别获取所述原始电压数据中每个控制指令数据之前的数据个数,将每个控制指令数据与对应的数据个数进行拼位,分别缓存至ram中;

[0063]

将所述电压序列数据中的各通道电压值以及延时值按照原有顺序缓存至先进先出fifo存储器中。

[0064]

其中,所述将所述原始电压数据中的控制指令数据和电压序列数据进行分离并分别进行缓存,还包括:

[0065]

若所述电压序列数据中最后一个控制指令数据之后还包括若干电压序列数据,则采用预设补齐控制指令和对应的数据个数进行拼位,并缓存至ram中。

[0066]

具体地,在对原始电压数据进行缓存后,需要对数据进行分离,将控制指令以及记录当前指令前面的数据个数进行拼位后存入ram中,如图3中步骤(2)所示,仍然以前述实施例中12个数据的电压数据序列为例,提取其中的控制指令0xc00003(输出1、2通道)和0xc00001(输出1通道)。

[0067]

由于0xc00003指令前有4个数据,则将计数值4和控制指令0xc00003拼位存入ram,得到{0xc00003,4},同理,0xc00001前面也有4个数据,将计数值4和控制指令0xc00001拼位存入ram,得到{0xc00001,4}。此处,由于控制指令0xc00001之后还有两个数据,且不包括控制指令,本发明采用设置默认指令0xc00000,并加上剩余的数据个数,拼位得到{0xc00000,2},也就是所有通道状态为0。同时将其余的各通道电压值以及延时值依照原有的顺序存入fifo((first input first output)存储器,fifo存储器分为写入专用区和读取专用区,读操作与写操作可以异步进行,写入区上写入的数据按照写入的顺序从读取端的区中读出,类似于吸收写入端与读出端速度差的一种缓冲器。

[0068]

本发明通过对电压数据序列中的控制指令进行拼位处理,对电压数据序列的格式进行了简化,并采用空的控制指令对数据序列进行补齐,便于后续的读写操作和重排序的

正确处理。

[0069]

在上述实施例的基础上,所述基于预设拼位处理后的控制指令数据对所述电压序列数据进行读操作,将所述电压序列数据重新排序并写入对应随机存取存储器ram,输出新的电压序列数据,包括:

[0070]

依次读取ram中经过拼位处理的控制指令数据,以及fifo存储器中对应的数据长度;

[0071]

基于所述控制指令数据中的各通道开关状态以及各通道电压值,对所述电压序列数据进行取值和重新排序,得到写操作后的电压序列数据;

[0072]

将所述写操作后的电压序列按照各通道分别存入多个ram中,得到所述新的电压序列数据。

[0073]

具体地,如图3步骤(3)所示,执行读操作,依次读出ram中控制指令以及记录的数据个数,以及fifo中对应的数据长度,读取顺序为先ram数据,后fifo数据。

[0074]

将读取出来的电压序列数据按照控制指令中的各通道的开关状态以及各通道的电压值重新排序存入多个ram中,如图3步骤(4)所示,由于第二个控制指令为0xc00001,对应为读取1通道数值,所以第二通道的0x2eeeee电压值不输出,此处采用类似低电平的处理将该数值进行舍弃,而其余的延时控制指令等仍正常输出,得到步骤(5)中的两个通道的电压序列数据,分别为:

[0075]

1通道电压序列:0xd0000a,0x10ffff,0xdfffff,0xd000dd,0x100000,0xd000ff。

[0076]

2通道电压序列:0xd0000a,0x2ddddd,0xdfffff,0xd000dd,0xd000ff。

[0077]

最后,按照各自通道输出对应的电压数据序列。

[0078]

本发明通过获取拼位处理后的控制指令数据中的各通道开关状态以及各通道电压值,对原始的电压数据按照各自通道独立获取对应的电压数值,实现了分通道获取独立的电压数据序列,相比传统的统一进行单一数据流的缓存,提高了数据缓存的有效性和系统性。

[0079]

下面以完整的实施例来详细描述本发明对电压序列数据的缓存处理及排序的实现方式,结合图3中的各个步骤,具体包括:

[0080]

(1)通过以太网口接收对应mac地址的数据包,并将采集到的原始数据缓存到芯片内部的ram中;

[0081]

(2)分离原始数据,将控制指令以及记录当前指令前面的数据个数进行拼位存入ram,例如:0xc00003指令前有4个数据,则将计数值4和控制指令0xc00003拼位存入ram,最后一个{0xc00000,2}的意思是当数据最后没有控制指令时,默认为指令为0xc00000,也就是所有通道状态为0,同时将其余的各通道电压值以及延时值按原有的顺序存入fifo存储器;

[0082]

(3)执行读操作,依次读出ram中控制指令以及记录的数据个数,以及fifo中对应的数据长度,读取顺序为先ram数据,后fifo数据;

[0083]

(4)将读取出来的电压序列数据按照控制指令中的各通道的开关状态以及各通道的电压值重新排序存入多个ram中,由于第二个控制指令为0xc00001,对应输出为1通道,所以第二通道的0x2eeeee电压值不输出,但延时指令正常输出,最终得到2个通道的电压序列数据;

[0084]

(5)最后,按照各通道独立输出各自对应的电压序列数据。

[0085]

下面对本发明提供的电压序列数据缓存系统进行描述,下文描述的电压序列数据缓存系统与上文描述的电压序列数据缓存方法可相互对应参照。

[0086]

图4是本发明提供的电压序列数据缓存系统的结构示意图,如图4所示,包括:缓存模块41、分离模块42和处理模块43,其中:

[0087]

缓存模块41用于缓存原始电压数据;分离模块42用于将所述原始电压数据中的控制指令数据和电压序列数据进行分离并分别进行缓存;处理模块43用于基于预设拼位处理后的控制指令数据对所述电压序列数据进行读操作,将所述电压序列数据重新排序并进行写操作,输出新的电压序列数据。

[0088]

本发明针对带有不同通道数据以及控制指令的电压数据流,采用分离缓存通道数据以及控制指令,根据控制指令的位置和状态对分离后的数据进行重排序,输出各通道对应的电压序列数据,增加了电压序列数据的易读取性和可操作性。

[0089]

在上述实施例的基础上,该系统还包括获取模块44,所述获取模块44用于采集获取所述原始电压数据。

[0090]

本发明针对带有不同通道数据以及控制指令的电压数据流,采用分离缓存通道数据以及控制指令,根据控制指令的位置和状态对分离后的数据进行重排序,输出各通道对应的电压序列数据,增加了电压序列数据的易读取性和可操作性。

[0091]

在上述实施例的基础上,所述缓存模块41具体用于将通过以太网口接收对应媒体存取控制位址mac地址的原始电压数据,缓存至芯片内部的随机存取存储器ram中。

[0092]

本发明采用16进制数据格式表示电压序列数据,有效区分指令数据、延时指令数据和电压数据等数据类型,便于后续进行分组提取数据和缓存数据。

[0093]

在上述实施例的基础上,所述分离模块42包括第一分离子模块421、第二分离子模块422和补齐子模块423,其中:

[0094]

所述第一分离子模块421用于提取所述控制指令数据,分别获取所述原始电压数据中每个控制指令数据之前的数据个数,将每个控制指令数据与对应的数据个数进行拼位,分别缓存至ram中;所述第二分离子模块422用于将所述电压序列数据中的各通道电压值以及延时值按照原有顺序缓存至先进先出fifo存储器中;所述补齐子模块423用于若所述电压序列数据中最后一个控制指令数据之后还包括若干电压序列数据,则采用预设补齐控制指令和对应的数据个数进行拼位,并缓存至ram中。

[0095]

本发明通过对电压数据序列中的控制指令进行拼位处理,对电压数据序列的格式进行了简化,并采用空的控制指令对数据序列进行补齐,便于后续的读写操作和重排序的正确处理。

[0096]

在上述实施例的基础上,所述处理模块43包括:读取子模块431、写入子模块432和处理子模块433,其中:

[0097]

读取子模块431用于依次读取ram中经过拼位处理的控制指令数据,以及fifo存储器中对应的数据长度;写入子模块432用于基于所述控制指令数据中的各通道开关状态以及各通道电压值,对所述电压序列数据进行取值和重新排序,得到写操作后的电压序列数据;处理子模块433用于将所述写操作后的电压序列按照各通道分别存入多个ram中,得到所述新的电压序列数据。

[0098]

本发明通过获取拼位处理后的控制指令数据中的各通道开关状态以及各通道电压值,对原始的电压数据按照各自通道独立获取对应的电压数值,实现了分通道获取独立的电压数据序列,相比传统的统一进行单一数据流的缓存,提高了数据缓存的有效性和系统性。

[0099]

图5示例了一种电子设备的实体结构示意图,如图5所示,该电子设备可以包括:处理器(processor)510、通信接口(communications interface)520、存储器(memory)530和通信总线540,其中,处理器510,通信接口520,存储器530通过通信总线540完成相互间的通信。处理器510可以调用存储器530中的逻辑指令,以执行电压序列数据缓存方法,该方法包括:缓存原始电压数据;将所述原始电压数据中的控制指令数据和电压序列数据进行分离并分别进行缓存;基于预设拼位处理后的控制指令数据对所述电压序列数据进行读操作,将所述电压序列数据重新排序并进行写操作,输出新的电压序列数据。

[0100]

此外,上述的存储器530中的逻辑指令可以通过软件功能单元的形式实现并作为独立的产品销售或使用时,可以存储在一个计算机可读取存储介质中。基于这样的理解,本发明的技术方案本质上或者说对现有技术做出贡献的部分或者该技术方案的部分可以以软件产品的形式体现出来,该计算机软件产品存储在一个存储介质中,包括若干指令用以使得一台计算机设备(可以是个人计算机,服务器,或者网络设备等)执行本发明各个实施例所述方法的全部或部分步骤。而前述的存储介质包括:u盘、移动硬盘、只读存储器(rom,read-only memory)、随机存取存储器(ram,random access memory)、磁碟或者光盘等各种可以存储程序代码的介质。

[0101]

另一方面,本发明还提供一种计算机程序产品,所述计算机程序产品包括计算机程序,计算机程序可存储在非暂态计算机可读存储介质上,所述计算机程序被处理器执行时,计算机能够执行上述各方法所提供的电压序列数据缓存方法,该方法包括:缓存原始电压数据;将所述原始电压数据中的控制指令数据和电压序列数据进行分离并分别进行缓存;基于预设拼位处理后的控制指令数据对所述电压序列数据进行读操作,将所述电压序列数据重新排序并进行写操作,输出新的电压序列数据。

[0102]

又一方面,本发明还提供一种非暂态计算机可读存储介质,其上存储有计算机程序,该计算机程序被处理器执行时实现以执行上述各方法提供的电压序列数据缓存方法,该方法包括:缓存原始电压数据;将所述原始电压数据中的控制指令数据和电压序列数据进行分离并分别进行缓存;基于预设拼位处理后的控制指令数据对所述电压序列数据进行读操作,将所述电压序列数据重新排序并进行写操作,输出新的电压序列数据。

[0103]

以上所描述的装置实施例仅仅是示意性的,其中所述作为分离部件说明的单元可以是或者也可以不是物理上分开的,作为单元显示的部件可以是或者也可以不是物理单元,即可以位于一个地方,或者也可以分布到多个网络单元上。可以根据实际的需要选择其中的部分或者全部模块来实现本实施例方案的目的。本领域普通技术人员在不付出创造性的劳动的情况下,即可以理解并实施。

[0104]

通过以上的实施方式的描述,本领域的技术人员可以清楚地了解到各实施方式可借助软件加必需的通用硬件平台的方式来实现,当然也可以通过硬件。基于这样的理解,上述技术方案本质上或者说对现有技术做出贡献的部分可以以软件产品的形式体现出来,该计算机软件产品可以存储在计算机可读存储介质中,如rom/ram、磁碟、光盘等,包括若干指

令用以使得一台计算机设备(可以是个人计算机,服务器,或者网络设备等)执行各个实施例或者实施例的某些部分所述的方法。

[0105]

最后应说明的是:以上实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的精神和范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。