1.本实用新型涉及控制电路领域,尤其涉及上电时序控制电路。

背景技术:

2.当今社会,我们的生活越来越离不开各种各样的电子设备。电子设备已经渗透到衣食住行的方方面面。此外,电子设备的复杂度,内部所用芯片的集成度也越来越高。随着设备运行速率的不断提升,各类芯片的供电电压也越来越低。与此同时,芯片电源的复杂度也越来越高。例如,fpga、处理器芯片,手机芯片等,往往包含10路以上的电源。每款芯片对于上电时序都有着严格的要求,如果处理不当,往往会导致系统无法运行,上电初始电流过大等一系列的问题。鉴于此,系统设计中往往会包含电源管理芯片。但是,电源管理芯片控制电源通路较多,对于电源少的情况会造成不必要的浪费。另外,电源管理芯片需要烧录对应的控制软件,这对于软件开发成本,以及后期烧录生产成本也会有一定影响。

3.因此,期望提供一种上电时序控制电路,该上电时序控制电路,不需要使用电源管理芯片,同时解决上电复位的问题,结构简单,性能可靠,同时成本具有相对优势。

技术实现要素:

4.根据本实用新型的一些实施例的第一方面,提供了一种上电时序控制电路,所述电路可以包括电源端vdd,所述电源端vdd用于电路的供电;延时控制芯片,所述延时控制芯片为具有延时功能的芯片;n路控制电路,所述控制电路用于电源上电时序的控制;n个芯片,所述芯片包括电源类芯片power_ic,通过对应的控制电路依次上电,其中,n为大于等于2的整数。

5.在一些实施例中,所述芯片的vdd管脚使用常供电vdd,供电电压区间为1.7-6.5v。

6.在一些实施例中,所述芯片reset管脚输出的power_ic enable信号均为0。

7.在一些实施例中,所述电源类芯片power_ic包括dc-dc电源类芯片、ldo电源类芯片。

8.在一些实施例中,所述电源类芯片power_ic处于reset状态时为不输出电压状态。

9.在一些实施例中,第一个芯片的sense管脚通过电阻连接vdd,在系统上电,经过设定的延迟时间后,第一个power_ic enable信号开启,第一路power_ic上电。

10.在一些实施例中,第一路power_ic输出电平通过电阻分压后,连接至第二个芯片的sense管脚,经过设定的延迟时间后,第二个power_ic enable信号开启,第二路power_ic上电。

11.在一些实施例中,第n-1路power_ic输出电平通过电阻分压后,连接至第n个芯片的sense管脚,经过设定的延迟时间后,第n个power_ic enable信号开启,第n路power_ic上电;完成整个系统的上电进程。

12.在一些实施例中,当系统主芯片需要power on reset信号时,在所有上电完成后,通过最后一路第n路的芯片,释放系统主芯片的power on reset信号,完成上电复位功能。

13.在一些实施例中,所述延时控制芯片包括tps3808g01芯片。

14.因此,本实用新型的上电时序控制电路,不需要使用电源管理芯片,同时解决上电复位的问题,结构简单,性能可靠,同时成本具有相对优势。

附图说明

15.为更好地理解并阐述本实用新型的一些实施例,以下将结合附图参考实施例的描述,在这些附图中,同样的数字编号在附图中指示相应的部分。

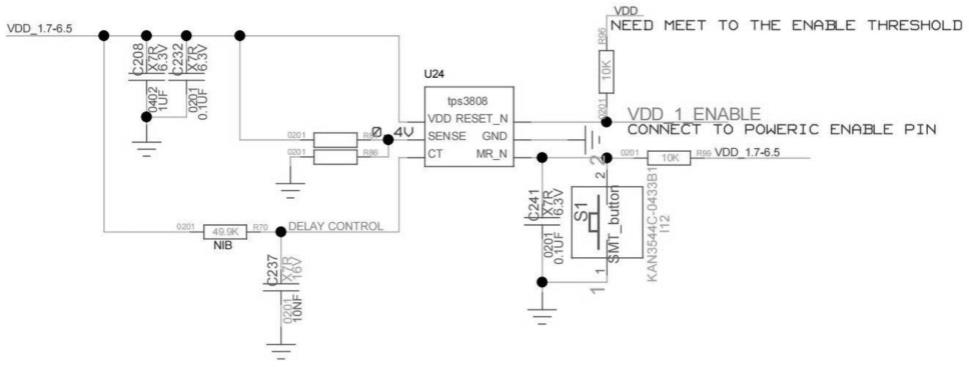

16.图1是根据本实用新型的一些实施例提供的上电时序控制电路第一路的示例性示意图。

17.图2是根据本实用新型的一些实施例提供的上电时序控制电路第二路的示例性示意图。

18.图3是根据本实用新型的一些实施例提供的上电时序控制电路第三路的示例性示意图。

19.图4是根据本实用新型的一些实施例提供的上电时序控制电路第n路的示例性示意图。

具体实施方式

20.以下参考附图的描述为便于综合理解由权利要求及其等效内容所定义的本实用新型的各种实施例。这些实施例包括各种特定细节以便于理解,但这些仅被视为示例性的。因此,本领域技术人员可以理解对在此描述的各种实施例进行各种变化和修改而不会脱离本实用新型的范围和精神。另外,为简要并清楚地描述本实用新型,本实用新型将省略对公知功能和结构的描述。

21.在以下说明书和权利要求书中使用的术语和短语不限于字面含义,而是仅为能够清楚和一致地理解本实用新型。因此,对于本领域技术人员,可以理解,提供对本实用新型各种实施例的描述仅仅是为说明的目的,而不是限制所附权利要求及其等效定义的本实用新型。

22.下面将结合本实用新型一些实施例中的附图,对本实用新型实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本实用新型一部分实施例,而不是全部的实施例。基于本实用新型中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本实用新型保护的范围。

23.需要说明的是,在本实用新型实施例中使用的术语是仅仅出于描述特定实施例的目的,而非旨在限制本实用新型。在本实用新型实施例和所附权利要求书中所使用的单数形式的“一”、“一个”、“一种”、“所述”和“该”也旨在包括多数形式,除非上下文清楚地表示其他含义。还应当理解,本实用新型中使用的术语“和/或”是指并包含一个或多个相绑定的列出项目的任何或所有可能组合。表达“第一”、“第二”、“所述第一”和“所述第二”是用于修饰相应元件而不考虑顺序或者重要性,仅仅被用于区分一种元件与另一元件,而不限制相应元件。

24.本实用新型实施例提供了一种上电时序控制电路。为了便于理解本实用新型实施例,以下将参考附图对本实用新型实施例进行详细描述。

25.图1是根据本实用新型的一些实施例提供的上电时序控制电路第一路的示例性示意图。如图1所示,本实用新型的上电时序控制电路,包括电源端vdd,所述电源端vdd用于电路的供电;延时控制芯片,所述延时控制芯片为具有延时功能的芯片;n路控制电路,所述控制电路用于电源上电时序的控制;n个芯片,所述芯片包括电源类芯片power_ic,通过对应的控制电路依次上电,其中,n为大于等于2的整数。

26.在一些实施例中,所述延时控制芯片可以包括但不限于tps3808g01芯片等其他具有相同功能的芯片。所述芯片的vdd管脚可以使用常供电vdd,供电电压区间为1.7-6.5v。所述芯片reset管脚输出的power_ic enable信号均为0。所述电源类芯片power_ic可以包括但不限于dc-dc电源类芯片、ldo电源类芯片等。所述电源类芯片power_ic处于reset状态时为不输出电压状态。

27.在一些实施例中,第一个芯片的sense管脚通过电阻连接vdd,在系统上电,经过设定的延迟时间后,第一个power_ic enable信号开启(如图所示的vdd_1_enable),第一路power_ic上电。

28.图2是根据本实用新型的一些实施例提供的上电时序控制电路第二路的示例性示意图。如图2所示,在一些实施例中,第一路power_ic输出电平通过电阻分压后,连接至第二个芯片的sense管脚,经过设定的延迟时间后,第二个power_ic enable信号开启(如图所示的vdd_2_enable),第二路power_ic上电。

29.图3是根据本实用新型的一些实施例提供的上电时序控制电路第三路的示例性示意图。如图3所示,在一些实施例中,第二路power_ic输出电平通过电阻分压后,连接至第三个芯片的sense管脚,经过设定的延迟时间后,第三个power_ic enable信号开启(如图所示的vdd_3_enable),第三路power_ic上电。以此类推(如图4所示),直至完成整个系统的上电流程。

30.图4是根据本实用新型的一些实施例提供的上电时序控制电路第n路的示例性示意图。如图4所示,在一些实施例中,第n-1路power_ic输出电平通过电阻分压后,连接至第n个芯片的sense管脚,经过设定的延迟时间后,第n个power_ic enable信号开启(如图所示的vdd_n_enable),第n路power_ic上电;完成整个系统的上电进程。

31.在一些实施例中,如图所示的“option for por”,当系统主芯片需要power on reset信号时,在所有上电完成后,通过最后一路第n路的芯片,释放系统主芯片的power on reset信号(por信号),完成上电复位功能。

32.在一些实施例中,对不同power_ic enable管脚的使能电平,本实用新型的上电时序控制电路可以每一路单独配置。相比通过直连,mos管,三极管等搭建的上电时序控制,本实用新型的上电时序控制电路可以完成最低0.4v电压的上电时序控制。本实用新型的上电时序控制电路可以通过硬件控制各路电源上电间隔;输出至power_ic enable信号电平可调;同时兼顾上电复位(por)功能,以及兼顾按键手动复位功能。本实用新型的上电时序控制电路无需使用电源管理芯片(pmic),相比通过电源管理芯片(pmic)完成的上电时序控制,减少了开发pmic控制软件的成本,同时在生产时大大减少了pmic软件烧录的各项成本;纯硬件控制,结构简单,性能可靠,同时多数环境中具有相应的成本优势。

33.需要说明的是,以上对于电路的描述,仅为描述方便,并不能把本实用新型限制在所举实施例的范围之内。可以理解,对于本领域技术人员,基于本系统的原理,可能在不背

离该原理的前提下,对各个操作进行任意组合,或者构成子流程与其它操作组合,对实施上述流程和操作的功能进行形式和细节上的各种修正和改变。例如,电路可以进一步包括其他类型芯片等结构。诸如此类的变形,均在本实用新型的保护范围之内。

34.综上所述,本实用新型的上电时序控制电路,不需要使用电源管理芯片,同时解决上电复位的问题,结构简单,性能可靠,同时成本具有相对优势。

35.需要注意的是,上述的实施例仅仅是用作示例,本实用新型不限于这样的示例,而是可以进行各种变化。

36.需要说明的是,在本说明书中,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、物品或者设备不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、物品或者设备所固有的要素。在没有更多限制的情况下,由语句“包括一个

……”

限定的要素,并不排除在包括所述要素的过程、方法、物品或者设备中还存在另外的相同要素。

37.最后,还需要说明的是,上述一系列处理不仅包括以这里所述的顺序按时间序列执行的处理,而且包括并行或分别地、而不是按时间顺序执行的处理。

38.本领域普通技术人员可以理解实现上述实施例方法中的全部或部分流程,是可以通过计算机程序指令相关的硬件来完成,所述的程序可存储于一计算机可读存储介质中,该程序在执行时,可包括如上述各方法的实施例的流程。其中,所述的存储介质可为磁碟、光盘、只读存储器(read-only memory,rom)或随机存储器(random access memory,ram)等。

39.以上所揭露的仅为本实用新型一些优选的实施例,不能以此来限定本实用新型之权利范围,本领域普通技术人员可以理解实现上述实施例的全部或部分流程,并依本实用新型权利要求所作的等同变化,仍属于本实用新型所涵盖的范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。