一种大功率使用场合的fpga供电电路

技术领域

1.本实用新型属于供电电路技术领域,具体涉及一种大功率使用场合的fpga供电电路。

背景技术:

2.fpga是在pal(可编程阵列逻辑)、gal(通用阵列逻辑)等可编程器件的基础上进一步发展的产物,是作为专用集成电路(asic)领域中的一种半定制电路而出现的,本身构成了半定制电路中的典型集成电路,其中含有数字管理模块、内嵌式单元、输出单元以及输入单元等,解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

3.现有方案中,国产fpga的供电,都是基于多种分立电源供电,各自提供vcc_int、vcc_bram、vcc_mgtavcc、vcc_mgtvccaux、vcc_aux、vcc_3v3各个部分的供电,电路设计相对复杂,硬件设计的复杂程度高,占用pcb板的面积较大,对于pcb板较小、布局紧张的电路板而言,布局压力太大,设计的可靠性和稳定性差,甚至无法实现。

技术实现要素:

4.为此,本实用新型提供一种大功率使用场合的fpga供电电路,解决现有大功率场合供电方案设计复杂程度高,可靠性和稳定性差的问题。

5.为了实现上述目的,本实用新型提供如下技术方案:一种大功率使用场合的fpga供电电路,包括主控芯片u20、主控芯片u21、主控芯片u22和负载芯片u23;

6.主控芯片u20配置有第一输入去耦电路、电阻r666、电容c256、电阻r948和第一输出去耦电路;第一输入去耦电路加在主控芯片u20的功率电源输入引脚;电阻r666加在主控芯片u20的反馈引脚;电容c256加在主控芯片u20的输出跟踪和软启动引脚上;电阻r948作为主控芯片u20的隔地电阻;第一输出去耦电路加在主控芯片u20的功率电源输出引脚;

7.主控芯片u21配置有第二输入去耦电路、电阻r956、电容c878、电阻r954和第二输出去耦电路;第二输入去耦电路加在主控芯片u21的功率电源输入引脚;电阻r956加在主控芯片u21的反馈引脚;电容c878加在主控芯片u21的输出跟踪和软启动引脚上;电阻r954作为主控芯片u21的隔地电阻;第二输出去耦电路加在主控芯片u21的功率电源输出引脚;

8.主控芯片u22配置有第三输入去耦电路、电阻r959、电容c897、电阻r958和第三输出去耦电路;第三输入去耦电路加在主控芯片u22的功率电源输入引脚;电阻r959加在主控芯片u22的反馈引脚;电容c897加在主控芯片u22的输出跟踪和软启动引脚上;电阻r958作为主控芯片u22的隔地电阻;第三输出去耦电路加在主控芯片u22的功率电源输出引脚;

9.主控芯片u20、主控芯片u21、主控芯片u22共同为负载芯片u23提供电源支持。

10.作为大功率使用场合的fpga供电电路优选方案,第一输入去耦电路包括去耦电容c232、去耦电容c233、去耦电容c234和去耦电容c235;

11.去耦电容c232、去耦电容c233、去耦电容c234和去耦电容c235相互并联后加在主控芯片u20的功率电源输入引脚;

12.第一输出去耦电路包括去耦电容c824、去耦电容c825、去耦电容c832、去耦电容c826、去耦电容c827、去耦电容c833、去耦电容c828、去耦电容c829、去耦电容c834、去耦电容c830、去耦电容c831和去耦电容c835;

13.去耦电容c824、去耦电容c825、去耦电容c832、去耦电容c826、去耦电容c827和去耦电容c833相互并联后加在主控芯片u20的功率电源输出引脚;

14.去耦电容c828、去耦电容c829、去耦电容c834、去耦电容c830、去耦电容c831和去耦电容c835相互并联后也加在主控芯片u20的功率电源输出引脚。

15.作为大功率使用场合的fpga供电电路优选方案,主控芯片u20还配置有电容c259,电容c259预置在主控芯片u20的电流阈值控制及相位补偿引脚。

16.作为大功率使用场合的fpga供电电路优选方案,第二输入去耦电路包括去耦电容c881、去耦电容c877、去耦电容c875和去耦电容c880;

17.去耦电容c881、去耦电容c877、去耦电容c875和去耦电容c880相互并联后加在主控芯片u21的功率电源输入引脚;

18.第二输出去耦电路包括去耦电容c869、去耦电容c866、去耦电容c872、去耦电容c867、去耦电容c868、去耦电容c874、去耦电容c870、去耦电容c871、去耦电容c865、去耦电容c863、去耦电容c864和去耦电容c862;

19.去耦电容c869、去耦电容c866、去耦电容c872、去耦电容c867、去耦电容c868、去耦电容c874相互并联后加在主控芯片u21的功率电源输出引脚;

20.去耦电容c870、去耦电容c871、去耦电容c865、去耦电容c863、去耦电容c864和去耦电容c862相互并联后也加在主控芯片u21的功率电源输出引脚。

21.作为大功率使用场合的fpga供电电路优选方案,主控芯片u21还配置有电阻r957、电容c882、电阻r955、电容c876;

22.电阻r957、电阻r955分别加在主控芯片u21另外通道的反馈引脚;

23.电容c882、电容c876分别加在主控芯片u21另外通道的输出跟踪和软启动引脚。

24.作为大功率使用场合的fpga供电电路优选方案,主控芯片u21还配置有电容c883、电容c873和电容c879;

25.电容c883、电容c873、电容c879分别加在主控芯片u21对应的电流阈值控制及相位补偿引脚。

26.作为大功率使用场合的fpga供电电路优选方案,第三输入去耦电路包括去耦电容c901、去耦电容c898、去耦电容c896和去耦电容c900;

27.去耦电容c901、去耦电容c898、去耦电容c896和去耦电容c900相互并联后加在主控芯片u22的功率电源输入引脚;

28.第三输出去耦电路包括去耦电容c889、去耦电容c886、去耦电容c894、去耦电容c887、去耦电容c888、去耦电容c895、去耦电容c890、去耦电容c891、去耦电容c884、去耦电容c892、去耦电容c893和去耦电容c885;

29.去耦电容c889、去耦电容c886、去耦电容c894、去耦电容c887、去耦电容c888、去耦电容c895相互并联后加在主控芯片u22的功率电源输出引脚;

30.去耦电容c890、去耦电容c891、去耦电容c884、去耦电容c892、去耦电容c893和去耦电容c885相互并联后也加在主控芯片u22的功率电源输出引脚。

31.作为大功率使用场合的fpga供电电路优选方案,主控芯片u22还配置有电容c899,电容c899预置在主控芯片u22的电流阈值控制及相位补偿引脚。

32.本实用新型具有以下优点:设有主控芯片u20、主控芯片u21、主控芯片u22和负载芯片u23;主控芯片u20配置有第一输入去耦电路、电阻r666、电容c256、电阻r948和第一输出去耦电路;第一输入去耦电路加在主控芯片u20的功率电源输入引脚;电阻r666加在主控芯片u20的反馈引脚;电容c256加在主控芯片u20的输出跟踪和软启动引脚上;电阻r948作为主控芯片u20的隔地电阻;第一输出去耦电路加在主控芯片u20的功率电源输出引脚;主控芯片u21配置有第二输入去耦电路、电阻r956、电容c878、电阻r954和第二输出去耦电路;第二输入去耦电路加在主控芯片u21的功率电源输入引脚;电阻r956加在主控芯片u21的反馈引脚;电容c878加在主控芯片u21的输出跟踪和软启动引脚上;电阻r954作为主控芯片u21的隔地电阻;第二输出去耦电路加在主控芯片u21的功率电源输出引脚;主控芯片u22配置有第三输入去耦电路、电阻r959、电容c897、电阻r958和第三输出去耦电路;第三输入去耦电路加在主控芯片u22的功率电源输入引脚;电阻r959加在主控芯片u22的反馈引脚;电容c897加在主控芯片u22的输出跟踪和软启动引脚上;电阻r958作为主控芯片u22的隔地电阻;第三输出去耦电路加在主控芯片u22的功率电源输出引脚;主控芯片u20、主控芯片u21、主控芯片u22共同为负载芯片u23提供电源支持。本实用新型适合国产fpga大功率使用场合,采用三颗芯片实现大功率多种电源供电,解决vcc_int、vcc_bram、vcc_mgtavcc、vcc_mgtvccaux、vcc_aux、vcc_3v3各个部分多种大功率电压供电的麻烦,并且能够实现上电时序的控制,满足上电时序要求,一方面降低硬件设计的复杂程度,另一方面减少占用pcb的面积,降低成本,提高设计的可靠性和系统整体的稳定性。

附图说明

33.为了更清楚地说明本实用新型的实施方式或现有技术中的技术方案,下面将对实施方式或现有技术描述中所需要使用的附图作简单地介绍。显而易见地,下面描述中的附图仅仅是示例性的,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据提供的附图引伸获得其它的实施附图。

34.本说明书所绘示的结构、比例、大小等,均仅用以配合说明书所揭示的内容,以供熟悉此技术的人士了解与阅读,并非用以限定本实用新型可实施的限定条件,故不具技术上的实质意义,任何结构的修饰、比例关系的改变或大小的调整,在不影响本实用新型所能产生的功效及所能达成的目的下,均应仍落在本实用新型所揭示的技术内容能涵盖的范围内。

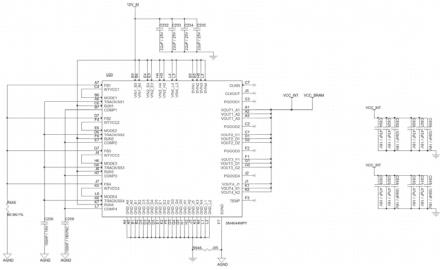

35.图1为本实用新型实施例中提供的大功率使用场合的fpga供电电路主控芯片u20电路示意图;

36.图2为本实用新型实施例中提供的大功率使用场合的fpga供电电路主控芯片u21电路示意图;

37.图3为本实用新型实施例中提供的大功率使用场合的fpga供电电路主控芯片u22电路示意图;

38.图4为本实用新型实施例中提供的大功率使用场合的fpga供电电路负载芯片u23第一部分电路示意图;

39.图5为本实用新型实施例中提供的大功率使用场合的fpga供电电路负载芯片u23第二部分电路示意图;

40.图6为本实用新型实施例中提供的大功率使用场合的fpga供电电路负载芯片u23第三部分电路示意图;

41.图7为本实用新型实施例中提供的大功率使用场合的fpga供电电路负载芯片u23第四部分电路示意图。

具体实施方式

42.以下由特定的具体实施例说明本实用新型的实施方式,熟悉此技术的人士可由本说明书所揭露的内容轻易地了解本实用新型的其他优点及功效,显然,所描述的实施例是本实用新型一部分实施例,而不是全部的实施例。基于本实用新型中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本实用新型保护的范围。

43.由于现有fpga供电电路设计相对复杂,占用pcb板的面积较大,对pcb板较小,布局紧张的板子而言,布局压力太大,甚至无法实现。为解决vcc_int、vcc_bram、vcc_mgtavcc、vcc_mgtvccaux、vcc_aux、vcc_3v3各个部分多种大功率电压供电的麻烦,并且能够实现上电时序的控制,满足上电时序要求,降低硬件设计的复杂程度,减少占用pcb的面积,降低成本,提高设计的可靠性和系统整体的稳定性。本实用新型提供如下具体实施方案。

44.参见图1、图2、图3、图4、图5、图6和图7,本实用新型实施例提供一种大功率使用场合的fpga供电电路,包括主控芯片u20、主控芯片u21、主控芯片u22和负载芯片u23;

45.主控芯片u20配置有第一输入去耦电路、电阻r666、电容c256、电阻r948和第一输出去耦电路;第一输入去耦电路加在主控芯片u20的功率电源输入引脚;电阻r666加在主控芯片u20的反馈引脚;电容c256加在主控芯片u20的输出跟踪和软启动引脚上;电阻r948作为主控芯片u20的隔地电阻;第一输出去耦电路加在主控芯片u20的功率电源输出引脚;

46.主控芯片u21配置有第二输入去耦电路、电阻r956、电容c878、电阻r954和第二输出去耦电路;第二输入去耦电路加在主控芯片u21的功率电源输入引脚;电阻r956加在主控芯片u21的反馈引脚;电容c878加在主控芯片u21的输出跟踪和软启动引脚上;电阻r954作为主控芯片u21的隔地电阻;第二输出去耦电路加在主控芯片u21的功率电源输出引脚;

47.主控芯片u22配置有第三输入去耦电路、电阻r959、电容c897、电阻r958和第三输出去耦电路;第三输入去耦电路加在主控芯片u22的功率电源输入引脚;电阻r959加在主控芯片u22的反馈引脚;电容c897加在主控芯片u22的输出跟踪和软启动引脚上;电阻r958作为主控芯片u22的隔地电阻;第三输出去耦电路加在主控芯片u22的功率电源输出引脚;

48.主控芯片u20、主控芯片u21、主控芯片u22共同为负载芯片u23提供电源支持。

49.本实施例中,第一输入去耦电路包括去耦电容c232、去耦电容c233、去耦电容c234和去耦电容c235;去耦电容c232、去耦电容c233、去耦电容c234和去耦电容c235相互并联后加在主控芯片u20的功率电源输入引脚;第一输出去耦电路包括去耦电容c824、去耦电容c825、去耦电容c832、去耦电容c826、去耦电容c827、去耦电容c833、去耦电容c828、去耦电容c829、去耦电容c834、去耦电容c830、去耦电容c831和去耦电容c835;去耦电容c824、去耦电容c825、去耦电容c832、去耦电容c826、去耦电容c827和去耦电容c833相互并联后加在主

控芯片u20的功率电源输出引脚;去耦电容c828、去耦电容c829、去耦电容c834、去耦电容c830、去耦电容c831和去耦电容c835相互并联后也加在主控芯片u20的功率电源输出引脚。主控芯片u20还配置有电容c259,电容c259预置在主控芯片u20的电流阈值控制及相位补偿引脚。

50.具体的,主控芯片u20采用sm4644mpy,可以提供四路4a电流,配置灵活,可根据实际需要配置,四通道并联使用,可提供单路16a电流,最大可提供20a峰值电流。

51.主控芯片u20的外围电路中采用的电子元件及功能如下:

52.去耦电容c232(22uf/25v):作为输入去耦电容,加在功率电源输入引脚,为了保证输入电源的低噪和稳定;

53.去耦电容c233(22uf/25v):作为输入去耦电容,加在功率电源输入引脚,为了保证输入电源的低噪和稳定;

54.去耦电容c234(22uf/25v):作为输入去耦电容,加在功率电源输入引脚,为了保证输入电源的低噪和稳定;

55.去耦电容c235(22uf/25v):作为输入去耦电容,加在功率电源输入引脚,为了保证输入电源的低噪和稳定。

56.电阻r666(90.9k/1%):主控芯片u20通道1、通道2、通道3和通道4的反馈引脚fb1、fb2、fb3、fb4(误差放大器的负输入引脚)。在主控芯片u20内部,该引脚通过一个60.4kr电阻连接到该通道的电压输出引脚。通过在fb1、fb2、fb3、fb4和地引脚之间,连接电阻r666(90.9k/1%),实现通道1、通道2、通道3和通道4电压输出1.0v的要求,最大输出电流可达20a;

57.电容c256(100nf/16v):在输出跟踪和软启动引脚上配置一个电容,提供软启动功能;

58.电容c259(100nf/16v):预留配置在电流阈值控制及相位补偿引脚,内部电流比较器阈值与该电压成比例,器件内部具有补偿,所以该电容预留设计,调试时可根据实际情况调整;

59.电阻r948(0r):隔地电阻,作为数字地和模拟地隔地设计,保证数字地和模拟地之间互不干扰,提高系统的稳定性和抗干扰能力;

60.去耦电容c824(47uf/16v):作为输出去耦电容,加在功率电源输出引脚,为了保证输出电源的低噪和稳定。

61.去耦电容c825(47uf/16v):作为输出去耦电容,加在功率电源输出引脚,为了保证输出电源的低噪和稳定。

62.去耦电容c832(100nf/16v):作为输出去耦电容,加在功率电源输出引脚,为了保证输出电源的低噪和稳定。

63.去耦电容c826(47uf/16v):作为输出去耦电容,加在功率电源输出引脚,为了保证输出电源的低噪和稳定。

64.去耦电容c827(47uf/16v):作为输出去耦电容,加在功率电源输出引脚,为了保证输出电源的低噪和稳定。

65.去耦电容c833(100nf/16v):作为输出去耦电容,加在功率电源输出引脚,为了保证输出电源的低噪和稳定。

66.去耦电容c828(47uf/16v):作为输出去耦电容,加在功率电源输出引脚,为了保证输出电源的低噪和稳定。

67.去耦电容c829(47uf/16v):作为输出去耦电容,加在功率电源输出引脚,为了保证输出电源的低噪和稳定。

68.去耦电容c834(100nf/16v):作为输出去耦电容,加在功率电源输出引脚,为了保证输出电源的低噪和稳定。

69.去耦电容c830(47uf/16v):作为输出去耦电容,加在功率电源输出引脚,为了保证输出电源的低噪和稳定。

70.去耦电容c831(47uf/16v):作为输出去耦电容,加在功率电源输出引脚,为了保证输出电源的低噪和稳定。

71.去耦电容c835(100nf/16v):作为输出去耦电容,加在功率电源输出引脚,为了保证输出电源的低噪和稳定。

72.本实施例中,第二输入去耦电路包括去耦电容c881、去耦电容c877、去耦电容c875和去耦电容c880;去耦电容c881、去耦电容c877、去耦电容c875和去耦电容c880相互并联后加在主控芯片u21的功率电源输入引脚;第二输出去耦电路包括去耦电容c869、去耦电容c866、去耦电容c872、去耦电容c867、去耦电容c868、去耦电容c874、去耦电容c870、去耦电容c871、去耦电容c865、去耦电容c863、去耦电容c864和去耦电容c862;去耦电容c869、去耦电容c866、去耦电容c872、去耦电容c867、去耦电容c868、去耦电容c874相互并联后加在主控芯片u21的功率电源输出引脚;去耦电容c870、去耦电容c871、去耦电容c865、去耦电容c863、去耦电容c864和去耦电容c862相互并联后也加在主控芯片u21的功率电源输出引脚。主控芯片u21还配置有电阻r957、电容c882、电阻r955、电容c876;电阻r957、电阻r955分别加在主控芯片u21另外通道的反馈引脚;电容c882、电容c876分别加在主控芯片u21另外通道的输出跟踪和软启动引脚。主控芯片u21还配置有电容c883、电容c873和电容c879;电容c883、电容c873、电容c879分别加在主控芯片u21对应的电流阈值控制及相位补偿引脚。

73.具体的,主控芯片u21采用sm4644mpy,可以提供四路4a电流,配置灵活,可根据实际需要配置,四通道并联使用,可提供单路16a电流,最大可提供20a峰值电流。

74.主控芯片u21的外围电路中采用的电子元件及功能如下:

75.去耦电容c881(22uf/25v):作为输入去耦电容,加在功率电源输入引脚,为了保证输入电源的低噪和稳定;

76.去耦电容c877(22uf/25v):作为输入去耦电容,加在功率电源输入引脚,为了保证输入电源的低噪和稳定;

77.去耦电容c875(22uf/25v):作为输入去耦电容,加在功率电源输入引脚,为了保证输入电源的低噪和稳定;

78.去耦电容c880(22uf/25v):作为输入去耦电容,加在功率电源输入引脚,为了保证输入电源的低噪和稳定;

79.电阻r956(60.4k/1%):主控芯片u21的通道1、通道2的反馈引脚fb1、fb2(误差放大器的负输入引脚)。在主控芯片u12内部,该引脚通过一个60.4kr电阻连接到该通道的电压输出引脚。通过在fb1、fb2和地引脚之间,连接电阻r956(60.4k/1%),实现通道1和通道2电压输出1.2v的要求,最大输出电流可达10a;

80.电容c878(100nf/16v):在输出跟踪和软启动引脚上配置一个电容,提供软启动功能;

81.电阻r957(30.1k/1%):主控芯片u21的通道3的反馈引脚fb3(误差放大器的负输入引脚)。在主控芯片u21内部,该引脚通过一个60.4kr电阻连接到该通道的电压输出引脚。通过在fb3和地引脚之间,连接电阻r957(30.1k/1%)实现通道3电压输出1.8v的要求,最大输出电流可达5a;

82.电容c882(100nf/16v):在输出跟踪和软启动引脚上配置一个电容,提供软启动功能;

83.电阻r955(13.3k/1%):主控芯片u21的通道4反馈引脚fb1、fb2(误差放大器的负输入引脚)。在主控芯片u21的内部,该引脚通过一个60.4kr电阻连接到该通道的电压输出引脚。通过在fb4和地引脚之间,连接电阻r955(13.3k/1%)实现通道4电压输出3.3v的要求,最大输出电流可达5a;

84.电容c876(100nf/16v):在输出跟踪和软启动引脚上配置一个电容,提供软启动功能;

85.电容c883(100nf/16v):预留配置在电流阈值控制及相位补偿引脚,内部电流比较器阈值与该电压成比例,器件内部具有补偿,所以该电容预留设计,调试时可根据实际情况调整;

86.电容c873(100nf/16v):预留配置在电流阈值控制及相位补偿引脚,内部电流比较器阈值与该电压成比例,器件内部具有补偿,所以该电容预留设计,调试时可根据实际情况调整;

87.电容c879(100nf/16v):预留配置在电流阈值控制及相位补偿引脚,内部电流比较器阈值与该电压成比例,器件内部具有补偿,所以该电容预留设计,调试时可根据实际情况调整;

88.电阻r954(0r):隔地电阻,作为数字地和模拟地隔地设计,保证数字地和模拟地之间互不干扰,提高系统的稳定性和抗干扰能力;

89.去耦电容c869(47uf/16v):作为输出去耦电容,加在功率电源输出引脚,为了保证输出电源的低噪和稳定。

90.去耦电容c866(47uf/16v):作为输出去耦电容,加在功率电源输出引脚,为了保证输出电源的低噪和稳定。

91.去耦电容c872(100nf/16v):作为输出去耦电容,加在功率电源输出引脚,为了保证输出电源的低噪和稳定。

92.去耦电容c867(47uf/16v):作为输出去耦电容,加在功率电源输出引脚,为了保证输出电源的低噪和稳定。

93.去耦电容c868(47uf/16v):作为输出去耦电容,加在功率电源输出引脚,为了保证输出电源的低噪和稳定。

94.去耦电容c874(100nf/16v):作为输出去耦电容,加在功率电源输出引脚,为了保证输出电源的低噪和稳定。

95.去耦电容c870(47uf/16v):作为输出去耦电容,加在功率电源输出引脚,为了保证输出电源的低噪和稳定。

96.去耦电容c871(47uf/16v):作为输出去耦电容,加在功率电源输出引脚,为了保证输出电源的低噪和稳定。

97.去耦电容c865(100nf/16v):作为输出去耦电容,加在功率电源输出引脚,为了保证输出电源的低噪和稳定。

98.去耦电容c863(47uf/16v):作为输出去耦电容,加在功率电源输出引脚,为了保证输出电源的低噪和稳定。

99.去耦电容c864(47uf/16v):作为输出去耦电容,加在功率电源输出引脚,为了保证输出电源的低噪和稳定。

100.去耦电容c862(100nf/16v):作为输出去耦电容,加在功率电源输出引脚,为了保证输出电源的低噪和稳定。

101.本实施例中,第三输入去耦电路包括去耦电容c901、去耦电容c898、去耦电容c896和去耦电容c900;去耦电容c901、去耦电容c898、去耦电容c896和去耦电容c900相互并联后加在主控芯片u22的功率电源输入引脚;第三输出去耦电路包括去耦电容c889、去耦电容c886、去耦电容c894、去耦电容c887、去耦电容c888、去耦电容c895、去耦电容c890、去耦电容c891、去耦电容c884、去耦电容c892、去耦电容c893和去耦电容c885;去耦电容c889、去耦电容c886、去耦电容c894、去耦电容c887、去耦电容c888、去耦电容c895相互并联后加在主控芯片u22的功率电源输出引脚;去耦电容c890、去耦电容c891、去耦电容c884、去耦电容c892、去耦电容c893和去耦电容c885相互并联后也加在主控芯片u22的功率电源输出引脚。主控芯片u22还配置有电容c899,电容c899预置在主控芯片u22的电流阈值控制及相位补偿引脚。

102.主控芯片u22采用sm4644mpy,可以提供四路4a电流,配置灵活,可根据实际需要配置,四通道并联使用,可提供单路16a电流,最大可提供20a峰值电流。

103.主控芯片u22的外围电路中采用的电子元件及功能如下:

104.去耦电容c901(22uf/25v):作为输入去耦电容,加在功率电源输入引脚,为了保证输入电源的低噪和稳定;

105.去耦电容c898(22uf/25v):作为输入去耦电容,加在功率电源输入引脚,为了保证输入电源的低噪和稳定;

106.去耦电容c896(22uf/25v):作为输入去耦电容,加在功率电源输入引脚,为了保证输入电源的低噪和稳定;

107.去耦电容c900(22uf/25v):作为输入去耦电容,加在功率电源输入引脚,为了保证输入电源的低噪和稳定;

108.电阻r959(90.9k/1%):主控芯片u22的通道1、通道2、通道3和通道4反馈引脚fb1、fb2、fb3、fb4(误差放大器的负输入引脚)。在主控芯片u22内部,该引脚通过一个60.4kr电阻连接到该通道的电压输出引脚。通过在fb1、fb2、fb3、fb4和地引脚之间,连接r959(90.9k/1%)实现通道1、通道2、通道3和通道4电压输出1.2v的要求,最大输出电流可达20a;

109.电容c897(100nf/16v):在输出跟踪和软启动引脚上配置一个电容,提供软启动功能;

110.电容c899(100nf/16v):预留配置在电流阈值控制及相位补偿引脚,内部电流比较

器阈值与该电压成比例,器件内部具有补偿,所以该电容预留设计,调试时可根据实际情况调整;

111.电阻r958(0r):隔地电阻,作为数字地和模拟地隔地设计,保证数字地和模拟地之间互不干扰,提高系统的稳定性和抗干扰能力;

112.去耦电容c889(47uf/16v):作为输出去耦电容,加在功率电源输出引脚,为了保证输出电源的低噪和稳定。

113.去耦电容c886(47uf/16v):作为输出去耦电容,加在功率电源输出引脚,为了保证输出电源的低噪和稳定。

114.去耦电容c894(100nf/16v):作为输出去耦电容,加在功率电源输出引脚,为了保证输出电源的低噪和稳定。

115.去耦电容c887(47uf/16v):作为输出去耦电容,加在功率电源输出引脚,为了保证输出电源的低噪和稳定。

116.去耦电容c888(47uf/16v):作为输出去耦电容,加在功率电源输出引脚,为了保证输出电源的低噪和稳定。

117.去耦电容c895(100nf/16v):作为输出去耦电容,加在功率电源输出引脚,为了保证输出电源的低噪和稳定。

118.去耦电容c890(47uf/16v):作为输出去耦电容,加在功率电源输出引脚,为了保证输出电源的低噪和稳定。

119.去耦电容c891(47uf/16v):作为输出去耦电容,加在功率电源输出引脚,为了保证输出电源的低噪和稳定。

120.去耦电容c884(100nf/16v):作为输出去耦电容,加在功率电源输出引脚,为了保证输出电源的低噪和稳定。

121.去耦电容c892(47uf/16v):作为输出去耦电容,加在功率电源输出引脚,为了保证输出电源的低噪和稳定。

122.去耦电容c893(47uf/16v):作为输出去耦电容,加在功率电源输出引脚,为了保证输出电源的低噪和稳定。

123.去耦电容c885(100nf/16v):作为输出去耦电容,加在功率电源输出引脚,为了保证输出电源的低噪和稳定。

124.综上所述,本实用新型设有主控芯片u20、主控芯片u21、主控芯片u22和负载芯片u23;主控芯片u20配置有第一输入去耦电路、电阻r666、电容c256、电阻r948和第一输出去耦电路;第一输入去耦电路加在主控芯片u20的功率电源输入引脚;电阻r666加在主控芯片u20的反馈引脚;电容c256加在主控芯片u20的输出跟踪和软启动引脚上;电阻r948作为主控芯片u20的隔地电阻;第一输出去耦电路加在主控芯片u20的功率电源输出引脚;主控芯片u21配置有第二输入去耦电路、电阻r956、电容c878、电阻r954和第二输出去耦电路;第二输入去耦电路加在主控芯片u21的功率电源输入引脚;电阻r956加在主控芯片u21的反馈引脚;电容c878加在主控芯片u21的输出跟踪和软启动引脚上;电阻r954作为主控芯片u21的隔地电阻;第二输出去耦电路加在主控芯片u21的功率电源输出引脚;主控芯片u22配置有第三输入去耦电路、电阻r959、电容c897、电阻r958和第三输出去耦电路;第三输入去耦电路加在主控芯片u22的功率电源输入引脚;电阻r959加在主控芯片u22的反馈引脚;电容

c897加在主控芯片u22的输出跟踪和软启动引脚上;电阻r958作为主控芯片u22的隔地电阻;第三输出去耦电路加在主控芯片u22的功率电源输出引脚;主控芯片u20、主控芯片u21、主控芯片u22共同为负载芯片u23提供电源支持。本实用新型适合国产fpga大功率使用场合,采用三颗芯片实现大功率多种电源供电,解决vcc_int、vcc_bram、vcc_mgtavcc、vcc_mgtvccaux、vcc_aux、vcc_3v3各个部分多种大功率电压供电的麻烦,并且能够实现上电时序的控制,满足上电时序要求,一方面降低硬件设计的复杂程度,另一方面减少占用pcb的面积,降低成本,提高设计的可靠性和系统整体的稳定性。

125.虽然,上文中已经用一般性说明及具体实施例对本实用新型作了详尽的描述,但在本实用新型基础上,可以对之作一些修改或改进,这对本领域技术人员而言是显而易见的。因此,在不偏离本实用新型精神的基础上所做的这些修改或改进,均属于本实用新型要求保护的范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。