1.本发明涉及一种高压半导体装置,尤其是涉及一种具有深阱区的高压半导体装置。

背景技术:

2.在具有高压处理能力的功率元件中,双扩散金属氧化物半导体(double-diffused mos,dmos)晶体管元件持续受到重视。常见的dmos晶体管元件有垂直双扩散金属氧化物半导体(vertical double-diffused mos,vdmos)与横向双扩散金属氧化物半导体(ldmos)晶体管元件。ldmos晶体管元件因具有较高的操作频宽与操作效率,以及易与其他集成电路整合的平面结构,现已广泛地应用于高电压操作环境中,例如中央处理器电源供应(cpu power supply)、电源管理系统(power management system)、直流/交流转换器(ac/dc converter)以及高功率或高频段的功率放大器等等。ldmos晶体管元件主要的特征为利用设置具有低掺杂浓度的横向扩散漂移区域来缓和源极端与漏极端之间的高电压,因此可使ldmos晶体管元件获得较高的击穿电压(breakdown voltage)。然而,随着相关产品的要求越来越高,如何通过在结构或/及制作工艺上的设计调整来改善高压半导体元件的电性表现、耐压能力或/及可靠度等仍是相关领域人员持续努力的方向。

技术实现要素:

3.本发明提供了一种高压半导体装置,利用在半导体基底中设置导电型态互补的多个深阱区来改善高压半导体装置的电性表现。

4.本发明的一实施例提供一种高压半导体装置,其包括一半导体基底、一第一深阱区、一第二深阱区、一第一阱区、一第二阱区以及一栅极结构。第一深阱区、第二深阱区、第一阱区以及第二阱区设置于半导体基底中。第二深阱区在一垂直方向上位于第一深阱区之上,第一阱区在垂直方向上位于第一深阱区之上,且第二阱区在垂直方向上位于第二深阱区之上。第二深阱区的导电型态与第一深阱区的导电型态互补,第二阱区的导电型态与第一阱区的导电型态互补,且第二阱区的导电型态与第二深阱区的导电型态互补。栅极结构设置于半导体基底上,且第一阱区的一部分以及第二阱区的一部分分别设置于栅极结构于一水平方向上的相对两侧。第二深阱区在水平方向上的长度大于或等于第二阱区在水平方向上的长度且小于第一深阱区在水平方向上的长度,且第一阱区与第一深阱区相连。

附图说明

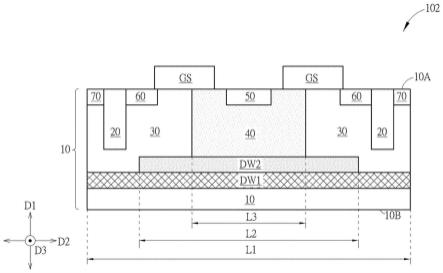

5.图1为本发明第一实施例的高压半导体装置的示意图;

6.图2为本发明一实施例的高压半导体装置的制作方法流程示意图;

7.图3为本发明第二实施例的高压半导体装置的示意图;

8.图4为本发明第三实施例的高压半导体装置的示意图;

9.图5为本发明另一实施例的高压半导体装置的制作方法流程示意图;

10.图6为本发明第四实施例的高压半导体装置的示意图;

11.图7为本发明第五实施例的高压半导体装置的示意图;

12.图8为本发明第六实施例的高压半导体装置的示意图;

13.图9为本发明第七实施例的高压半导体装置的示意图;

14.图10为本发明第八实施例的高压半导体装置的示意图;

15.图11为本发明第九实施例的高压半导体装置的示意图;

16.图12为本发明第十实施例的高压半导体装置的示意图;

17.图13为本发明第十一实施例的高压半导体装置的示意图;

18.图14为本发明第十二实施例的高压半导体装置的示意图;

19.图15为本发明第十三实施例的高压半导体装置的示意图;

20.图16为本发明第十四实施例的高压半导体装置的示意图。

21.主要元件符号说明

22.10

ꢀꢀꢀꢀꢀꢀ

半导体基底

23.10a

ꢀꢀꢀꢀꢀ

顶面

24.10b

ꢀꢀꢀꢀꢀ

底面

25.20

ꢀꢀꢀꢀꢀꢀ

第一隔离结构

26.30

ꢀꢀꢀꢀꢀꢀ

第一阱区

27.40

ꢀꢀꢀꢀꢀꢀ

第二阱区

28.42

ꢀꢀꢀꢀꢀꢀ

第三阱区

29.50

ꢀꢀꢀꢀꢀꢀ

漏极掺杂区

30.60

ꢀꢀꢀꢀꢀꢀ

源极掺杂区

31.70

ꢀꢀꢀꢀꢀꢀ

掺杂区

32.80

ꢀꢀꢀꢀꢀꢀ

第二隔离结构

33.101-114 高压半导体装置

34.d1

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一方向

35.d2

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二方向

36.d3

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第三方向

37.dw1

ꢀꢀꢀꢀ

第一深阱区

38.dw2

ꢀꢀꢀꢀ

第二深阱区

39.e1

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

边缘

40.e2

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

边缘

41.gs

ꢀꢀꢀꢀꢀꢀꢀꢀ

栅极结构

42.l1

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

长度

43.l2

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

长度

44.l3

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

长度

45.l4

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

长度

46.l5

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

长度

47.p11

ꢀꢀꢀꢀꢀ

第一部分

48.p12

ꢀꢀꢀꢀꢀ

第二部分

49.p21

ꢀꢀꢀꢀꢀ

第一部分

50.p22

ꢀꢀꢀꢀꢀ

第二部分

51.p31

ꢀꢀꢀꢀꢀ

第一部分

52.p32

ꢀꢀꢀꢀꢀ

第二部分

53.s11-s15 步骤

54.s21-s25 步骤

55.tk1

ꢀꢀꢀꢀꢀ

厚度

56.tk2

ꢀꢀꢀꢀꢀ

厚度

57.ts1

ꢀꢀꢀꢀꢀ

上表面

58.ts2

ꢀꢀꢀꢀ

上表面

具体实施方式

59.以下本发明的详细描述已披露足够的细节以使本领域的技术人员能够实践本发明。以下阐述的实施例应被认为是说明性的而非限制性的。对于本领域的一般技术人员而言显而易见的是,在不脱离本发明的精神和范围的情况下,可以进行形式及细节上的各种改变与修改。

60.在进一步的描述各实施例之前,以下先针对全文中使用的特定用语进行说明。

61.用语“在

…

上”、“在

…

上方”和“在

…

之上”的含义应当以最宽方式被解读,以使得“在

…

上”不仅表示“直接在”某物上而且还包括在某物上且其间有其他居间特征或层的含义,并且“在

…

上方”或“在

…

之上”不仅表示在某物“上方”或“之上”的含义,而且还可以包括其在某物“上方”或“之上”且其间没有其他居间特征或层(即,直接在某物上)的含义。

62.说明书与权利要求中所使用的序数例如“第一”、“第二”等用词,是用以修饰权利要求的元件,除非特别说明,其本身并不意含及代表该请求元件有任何之前的序数,也不代表某一请求元件与另一请求元件的顺序、或是制造方法上的顺序,该些序数的使用仅用来使具有某命名的一请求元件得以和另一具有相同命名的请求元件能作出清楚区分。

63.在下文中使用术语“形成”或“设置”来描述将材料层施加到基底的行为。这些术语旨在描述任何可行的层形成技术,包括但不限于热生长、溅射、蒸发、化学气相沉积、外延生长、电镀等。

64.请参阅图1。图1所绘示为本发明第一实施例的高压半导体装置101的示意图。如图1所示,高压半导体装置101包括一半导体基底10、一第一深阱区dw1、一第二深阱区dw2、一第一阱区30、一第二阱区40以及一栅极结构gs。第一深阱区dw1、第二深阱区dw2、第一阱区30以及第二阱区40设置于半导体基底10中。第二深阱区dw2在一垂直方向(例如图1中所示的第一方向d1)上位于第一深阱区dw1之上,第一阱区30在第一方向d1上位于第一深阱区dw1之上,且第二阱区40在第一方向d1上位于第二深阱区dw2之上。第二深阱区dw2的导电型态与第一深阱区dw1的导电型态互补(complementary),第二阱区40的导电型态与第一阱区30的导电型态互补,且第二阱区40的导电型态与第二深阱区dw2的导电型态互补。栅极结构gs设置于半导体基底10上,且第一阱区30的一部分以及第二阱区40的一部分分别设置于栅极结构gs在一水平方向(例如图1中所示的第二方向d2)上的相对两侧。第二深阱区dw2在第二方向d2上的长度l2大于或等于第二阱区40在第二方向d2上的长度l3且小于第一深阱区

dw1在第二方向d2上的长度l1,且第一阱区30与第一深阱区dw1相连。

65.在一些实施例中,半导体基底10的导电型态可与第一深阱区dw1的导电型态相同,而在第二阱区40与第一深阱区dw1之间设置第二深阱区dw2可达到隔离第二阱区40与位于第一深阱区dw1下方的半导体基底10的效果,且使第一阱区30与第一深阱区dw1相连可提升高压半导体装置的相关电性表现,例如可提升击穿电压(breakdown voltage)或/及降低导通电阻(drain-source on-state resistance,ron),但并不以此为限。换句话说,可不需通过增加高压半导体装置的所占面积即可达到改善相关电性表现的效果。

66.在一些实施例中,上述的第一方向d1可被视为半导体基底10的厚度方向,半导体基底10可于第一方向d1上具有相对的一顶面10a与一底面10b,而栅极结构gs可设置于顶面10a的一侧,但并不以此为限。与第一方向d1大体上正交的水平方向(例如图1中所示的第二方向d2与第三方向d3)可大体上与半导体基底10的顶面10a或/及底面10b平行,但并不以此为限。此外,在本文中所述在垂直方向(例如第一方向d1)上相对较高的位置或/及部件与半导体基底10的底面10b之间在第一方向d1上的距离大于在第一方向d1上相对较低的位置或/及部件与半导体基底10的底面10b之间在第一方向d1上的距离,各部件的下部或底部可比此部件的上部或顶部在第一方向d1上更接近半导体基底10的底面10b,在某个部件之上的另一部件可被视为在第一方向d1上相对较远离半导体基底10的底面10b,而在某个部件之下的另一部件可被视为在第一方向d1上相对较接近半导体基底10的底面10b。

67.在一些实施例中,高压半导体装置101可还包括一第一隔离结构20、一漏极掺杂区50以及一源极掺杂区60。漏极掺杂区50、源极掺杂区60以及第一隔离结构20的至少一部分可设置于半导体基底10中,漏极掺杂区50可位于第二阱区40中,而源极掺杂区60与第一隔离结构20的至少一部分可位于第一阱区30中。漏极掺杂区50的至少一部分以及源极掺杂区60的至少一部分可分别位于栅极结构gs在水平方向(例如第二方向d2)上的相对两侧,而源极掺杂区60的至少一部分可在第二方向d2上位于第二阱区40以及第一隔离结构20的至少一部分之间。

68.在一些实施例中,半导体基底10可包括硅基底、外延硅基底、硅锗基底、碳化硅基底、硅覆绝缘(silicon-on-insulator,soi)基底或其他适合的半导体材料或/及结构所形成的半导体基底。在一些实施例中,第一深阱区dw1、第二深阱区dw2、第一阱区30、第二阱区40、漏极掺杂区50以及源极掺杂区60可分别包括利用掺杂制作工艺(例如注入制作工艺)于半导体基底10中所形成的掺杂区。换句话说,第一深阱区dw1、第二深阱区dw2、第一阱区30、第二阱区40、漏极掺杂区50以及源极掺杂区60可分别具有半导体基底10的一部分(即与半导体基底10具有相同的材料)以及形成于半导体基底10中的掺杂物。在一些实施例中,半导体基底10较佳可具有一第一导电型态或包括有一第一导电型态的区域,第一深阱区dw1与第二阱区40可具有第二导电型态,第二深阱区dw2与第一阱区30可具有第一导电型态,且第二导电型态可与第一导电型态互补。举例来说,本实施例中的第一导电型态可为p型,第二导电型态可为n型,但并不以此为限。换句话说,半导体基底10可为p型半导体基底或具有p型掺杂区的半导体基底,第一深阱区dw1可为n型掺杂深阱区,第二深阱区dw2可为p型掺杂深阱区,第一阱区30可为p型掺杂阱区,而第二阱区40可为n型掺杂阱区,但并不以此为限。相对地,在一些实施例中,第一导电型态可为n型,而第二导电型态可为p型。此外,在一些实施例中,漏极掺杂区50与源极掺杂区60可分别包括第二导电型态的重掺杂区,但并不以此

为限。

69.在一些实施例中,第一深阱区dw1可包含第一掺杂物,第二深阱区dw2可包含第二掺杂物,第一阱区30可包含第三掺杂物,第二阱区40可包含第四掺杂物,漏极掺杂区50可包含第五掺杂物,而源极掺杂区60可包含第六掺杂物。当上述的第一导电型态为p型且第二导电型态为n型时,第一掺杂物、第四掺杂物、第五掺杂物以及第六掺杂物可分别为n型掺杂物,而第二掺杂物与第三掺杂物可分别为p型掺杂物,但并不以此为限。上述的n型掺杂物可包括磷(p)、砷(as)或其他适合的n型掺杂材料,而上述的p型掺杂物可包括硼(b)、镓(ga)或其他适合的p型掺杂材料。换句话说,相同导电型态的掺杂区中的掺杂物可为同一型态的掺杂物,但仍可视设计需要于相同导电型态的掺杂区中分别使用相同或不同的元素当作掺杂物。此外,在一些实施例中,漏极掺杂区50中的第五掺杂物的浓度与源极掺杂区60中的第六掺杂物的浓度可高于第二阱区40中的第四掺杂物的浓度,第二阱区40中的第四掺杂物的浓度可高于第一深阱区dw1中的第一掺杂物的浓度,而第一阱区30中的第三掺杂物的浓度可高于第二深阱区dw2中的第二掺杂物的浓度,但并不以此为限。

70.在一些实施例中,第一隔离结构20可包括单层或多层的绝缘材料例如氧化物绝缘材料(例如氧化硅)或其他适合的绝缘材料。栅极结构gs可包括栅极介电层(未绘示)、设置于栅极介电层上的栅极材料层(未绘示)以及设置于栅极材料层的侧壁上的间隙壁(未绘示)。栅极介电层可包括高介电常数(high-k)介电材料或其他适合的介电材料,而栅极材料层可包括非金属导电材料(例如经掺杂的多晶硅)或金属导电材料,例如由功函数层以及低电阻层所堆叠而成的金属栅极结构,但并不以此为限。上述的high-k介电材料可包括氧化铪(hafnium oxide,hfo

x

)、硅酸铪氧化合物(hafnium silicon oxide,hfsio4)、硅酸铪氮氧化合物(hafnium silicon oxynitride,hfsion)、氧化铝(aluminum oxide,al2o3)、氧化钽(tantalum oxide,ta2o5)、氧化锆(zirconium oxide,zro2)或其他适合的高介电常数材料。上述的功函数层可包括氮化钛(titanium nitride,tin)、碳化钛(titanium carbide,tic)、氮化钽(tantalum nitride,tan)、碳化钽(tantalum carbide,tac)、碳化钨(tungsten carbide,wc)、三铝化钛(titanium tri-aluminide,tial3)、氮化铝钛(aluminum titanium nitride,tialn)或其他适合的导电功函数材料,而上述的低电阻层可包括例如钨、铝、铜、铝化钛、钛或其他适合的低电阻材料。此外,上述的间隙壁可包括单层或多层的介电材料,例如氧化硅、氮化硅、氮氧化硅或其他适合的介电材料。

71.在一些实施例中,第二阱区40可被视为高压半导体装置中的漂移区(drift region),而在沿第一方向d1观看高压半导体装置101的状况下,栅极结构gs可与第一阱区30的一部分、源极掺杂区60的一部分以及第二阱区40的一部分重叠,而栅极结构gs可未与漏极掺杂区50重叠,但并不以此为限。此外,在一些实施例中,第一阱区30可分别与第一深阱区dw1以及第二深阱区dw2直接相连,而第二深阱区dw2可分别与第一深阱区dw1以及第二阱区40直接相连,但并不以此为限。此外,第一阱区30可视设计需要而与第二阱区40直接相连,或者部分的半导体基底10可位于第一阱区30与第二阱区40之间。

72.第二深阱区dw2的至少一部分(例如第一部分p21)可在第一方向d1上设置于第一深阱区dw1与第二阱区40之间,且第二深阱区dw2的至少一部分(例如第二部分p22)可在第一方向d1上设置于第一深阱区dw1与第一阱区30之间。此外,在一些实施例中,第一阱区30的第一部分p31可在第二方向d2上位于第二阱区40与第一隔离结构20之间,而第一阱区30

的第二部分p32可在第一方向d1上位于第一深阱区dw1与第一隔离结构20之间。在一些实施例中,第一阱区30的第一部分p31在第二方向d2上的长度l5可大于第二深阱区dw2的第二部分p22在第二方向d2上的长度l4,而第一阱区30的第二部分p32的厚度tk2可大于第二深阱区dw2的厚度tk1,由此使得第二深阱区dw2未延伸至第一隔离结构20的下方,且使得第二深阱区dw2未高于第一隔离结构20的底面,进而可避免第二深阱区dw2或/及第一隔离结构20影响第一阱区30与第一深阱区dw1之间的连接状况。此外,上述的厚度tk1与厚度tk2也可分别被视为第二深阱区dw2与第一阱区30的第二部分p32在第一方向d1上的长度。

73.请参阅图1与图2。图2所绘示为本发明一实施例的高压半导体装置的制作方法流程示意图。在一些实施例中,上述的高压半导体装置101的制作方法可包括但并不限于图2中所示的步骤。如图1与图2所示,高压半导体装置101的制作方法可包括下列步骤。首先,进行步骤s11,在半导体基底10中形成隔离结构(例如上述的第一隔离结构20)。然后,进行步骤s12,在半导体基底10中形成第一深阱区dw1。在形成第一深阱区dw1之后,进行步骤s13,在半导体基底10中形成第二深阱区dw2。在形成第二深阱区dw2之后,进行步骤s14,在半导体基底10中形成第一阱区30。在形成第一阱区30之后,进行步骤s15,在半导体基底10中形成第二阱区40。在一些实施例中,可在第二深阱区dw2形成之后以及第一阱区30形成之前(即在步骤s13与步骤s14之间)进行热处理(例如rapid thermal process,rtp),用以对第一深阱区dw1或/及第二深阱区dw2产生活化效果,但并不以此为限。在一些实施例中,也可在第一深阱区dw1形成之后以及第二深阱区dw2形成之前(即在步骤s12与步骤s13之间)进行热处理,用以先对第一深阱区dw1产生活化效果而降低形成第二深阱区dw2的制作工艺对于第一深阱区dw1的负面影响。在第二阱区40形成之后,可于半导体基底10上形成上述的栅极结构gs,并在半导体基底10中形成上述的漏极掺杂区50与源极掺杂区60。此外,上述的第一深阱区dw1、第二深阱区dw2、第一阱区30以及第二阱区40的制作顺序也可视需要应用于本发明的其他实施例中。

74.下文将针对本发明的不同实施例进行说明,且为简化说明,以下说明主要针对各实施例不同之处进行详述,而不再对相同之处作重复赘述。此外,本发明的各实施例中相同的元件是以相同的标号进行标示,以利于各实施例间互相对照。

75.请参阅图3。图3所绘示为本发明第二实施例的高压半导体装置102的示意图。如图3所示,高压半导体装置102可包括两个上述的栅极结构gs、两个上述的源极掺杂区60以及两个上述的第一隔离结构20。两个栅极结构gs、两个源极掺杂区60以及两个第一隔离结构20可分别位于漏极掺杂区50在第二方向d2上的相对两侧,第一阱区30可在第二方向d2以及第三方向d3上围绕第二阱区40。在一些实施例中,第二深阱区dw2可于第一方向d1上完全覆盖第二阱区40,由此确保第二深阱区dw2在第二阱区40与半导体基底10之间的隔离效果。此外,高压半导体装置102可还包括一掺杂区70设置于第一阱区30中,掺杂区70的导电型态可与源极掺杂区60的导电型态互补,例如掺杂区70可为第一导电型态的重掺杂区,而掺杂区70可用以调整第一阱区30的电位状况,但并不以此为限。此外,掺杂区70的一部分以及源极掺杂区60可分别设置于第一隔离结构20在第二方向d2上的相对两侧,但并不以此为限。

76.请参阅图4。图4所绘示为本发明第三实施例的高压半导体装置103的示意图。如图4所示,在高压半导体装置103中,第二深阱区dw2在第二方向d2上的长度l2可大体上等于第二阱区40在第二方向d2上的长度l3且小于第一深阱区dw1在第二方向d2上的长度l1。在一

些实施例中,在考虑可行的制作工艺变异控制的状况下,第二深阱区dw2在第二方向d2上的长度l2可以在宽容度为

±

10%的状况下大体上等于第二阱区40在第二方向d2上的长度l3,但并不以此为限。在一些实施例中,第二深阱区dw2的两相对边缘(例如在第二方向d2上相对的两个边缘e1或/及在第三方向d3上相对的两个边缘)可分别与第二阱区40的两相对边缘(例如在第二方向d2上相对的两个边缘e2或/及在第三方向d3上相对的两个边缘)对齐。在一些实施例中,第二阱区40在第一方向d1上的投影面积可大体上等于第二深阱区dw2在第一方向d1上的投影面积,例如第二阱区40在第一方向d1上的投影面积可以在宽容度为

±

10%的状况下大体上等于第二深阱区dw2在第一方向d1上的投影面积,但并不以此为限。

77.请参阅图4与图5。图5所绘示为本发明另一实施例的高压半导体装置的制作方法流程示意图。在一些实施例中,上述的高压半导体装置103的制作方法可包括但并不限于图5中所示的步骤。如图4与图5所示,高压半导体装置103的制作方法可包括下列步骤。首先,进行步骤s21,在半导体基底10中形成隔离结构(例如上述的第一隔离结构20)。然后,进行步骤s22,在半导体基底10中形成第一深阱区dw1。在形成第一深阱区dw1之后,进行步骤s23,在半导体基底10中形成第一阱区30。在形成第一阱区30之后,进行步骤s24,在半导体基底10中形成第二深阱区dw2。在形成第二深阱区dw2之后,进行步骤s25,在半导体基底10中形成第二阱区40。在一些实施例中,第二深阱区dw2与第二阱区40可利用形成在半导体基底10上的同一个图案化掩模进行不同的掺杂制作工艺而形成,由此使得第二阱区40可于第一方向d1上与第二深阱区dw2对应设置,且可由此达到制作工艺简化的效果,但并不以此为限。此外,上述的第一深阱区dw1、第一阱区30、第二深阱区dw2以及第二阱区40的制作顺序也可视需要应用于本发明的其他实施例中。

78.请参阅图6。图6所绘示为本发明第四实施例的高压半导体装置104的示意图。如图6所示,高压半导体装置104可还包括一第二隔离结构80设置于第二阱区40中,第二隔离结构80的至少一部分可在第二方向d2上位于第一阱区30以及漏极掺杂区50之间,且第二阱区40的一部分可在第一方向d1上位于第二隔离结构80与第二深阱区dw2之间。在一些实施例中,第二隔离结构80可包括单层或多层的绝缘材料例如氧化物绝缘材料(例如氧化硅)或其他适合的绝缘材料。在一些实施例中,第二隔离结构80与第一隔离结构20可利用同一制作工艺一并形成而具有相同的材料组成或/及相同的深度,但并不以此为限。在一些实施例中,也可视设计需要以不同的制作工艺或/及材料分别形成第一隔离结构20与第二隔离结构80。通过第二隔离结构80的设置,可产生较大的空乏区而减少电场效应,进而可改善高压半导体装置的电性表现,例如可提升高压半导体装置的击穿电压,但并不以此为限。值得说明的是,本实施例的第二隔离结构80也可视需要应用于本发明的其他实施例中。

79.请参阅图7。图7所绘示为本发明第五实施例的高压半导体装置105的示意图。如图7所示,在高压半导体装置105中,第二隔离结构80可设置于半导体基底10中并位于第二阱区40中,而第二深阱区dw2在第二方向d2上的长度l2可大体上等于第二阱区40在第二方向d2上的长度l3,且第二深阱区dw2在第二方向d2上相对的两个边缘e1可分别与第二阱区40在第二方向d2上相对的两个边缘e2对齐。

80.请参阅图8。图8所绘示为本发明第六实施例的高压半导体装置106的示意图。如图8所示,在高压半导体装置106中,掺杂区70的一部分可在第二方向d2上设置于源极掺杂区60与第一隔离结构20之间,且设置于源极掺杂区60与第一隔离结构20之间的掺杂区70可与

源极掺杂区60直接连接,但并不以此为限。通过本实施例的掺杂区70的设置方式,可有助于更准确地调整接近源极掺杂区60的第一阱区30的电位状况,而本实施例的掺杂区70的设置方式也可视需要应用于本发明的其他实施例中。

81.请参阅图9。图9所绘示为本发明第七实施例的高压半导体装置107的示意图。如图9所示,在高压半导体装置107中,第一深阱区dw1在第二方向d2上可未超出第一隔离结构20以外的区域,而第一深阱区dw1在第二方向d2上的两相对边缘可分别位于两个第一隔离结构20在第一方向d1上的下方,由此可控制第一深阱区dw1的范围而避免第一深阱区dw1在超出第一隔离结构20之外的区域产生负面影响。

82.请参阅图10。图10所绘示为本发明第八实施例的高压半导体装置108的示意图。如图10所示,在高压半导体装置108中,第一深阱区dw1可包括一第一部分p11以及一第二部分p12,第二部分p12设置于第一部分p11之上,而第二部分p12可被视为第一深阱区dw1在第一方向d1上的凸出部,但并不以此为限。在一些实施例中,第一深阱区dw1的第二部分p12可在水平方向(例如第二方向d2或/及第三方向d3)上围绕第二深阱区dw2,且第一深阱区dw1的第二部分p12的上表面ts1可在第一方向d1上高于第二深阱区dw2的上表面ts2或与第二深阱区dw2的上表面ts2大体上共平面,由此可避免因为设置第二深阱区dw2而造成第一深阱区dw1的上表面过低的状况。在一些实施例中,第一深阱区dw1的第二部分p12的上表面ts1以及第二深阱区dw2的上表面ts2可分别为第二部分p12与第二深阱区dw2在第一方向d1上的最上(topmost)表面。

83.请参阅图11。图11所绘示为本发明第九实施例的高压半导体装置109的示意图。如图11所示,在高压半导体装置109中,第一深阱区dw1的第二部分p12可在水平方向上围绕第二深阱区dw2,且第一深阱区dw1的第二部分p12的上表面ts1可在第一方向d1上高于第二深阱区dw2的上表面ts2或与第二深阱区dw2的上表面ts2大体上共平面。此外,第一深阱区dw1在第二方向d2上可未超出第一隔离结构20以外的区域,而第一深阱区dw1在第二方向d2上的两相对边缘(例如第二部分p12的外侧边缘)可分别位于两个第一隔离结构20在第一方向d1上的下方。此外,第二深阱区dw2在第二方向d2上的长度l2可大体上等于第二阱区40在第二方向d2上的长度l3,且第二深阱区dw2在第二方向d2上相对的两个边缘e1可分别与第二阱区40在第二方向d2上相对的两个边缘e2对齐。在一些实施例中,第二深阱区dw2在第二方向d2上相对的两个边缘e1可被第一深阱区dw1的第二部分p12覆盖,但并不以此为限。

84.请参阅图12。图12所绘示为本发明第十实施例的高压半导体装置110的示意图。如图12所示,在高压半导体装置110中,第一深阱区dw1的第二部分p12可在水平方向上围绕第二深阱区dw2,且第一深阱区dw1的第二部分p12的上表面ts1可在第一方向d1上高于第二深阱区dw2的上表面ts2或与第二深阱区dw2的上表面ts2大体上共平面。此外,第一深阱区dw1在第二方向d2上可未超出第一隔离结构20以外的区域,而第一深阱区dw1在第二方向d2上的两相对边缘(例如第二部分p12的外侧边缘)可分别位于两个第一隔离结构20在第一方向d1上的下方。

85.请参阅图13。图13所绘示为本发明第十一实施例的高压半导体装置111的示意图。如图13所示,在高压半导体装置111中,第一深阱区dw1的第二部分p12可在水平方向上围绕第二深阱区dw2,且第一深阱区dw1的第二部分p12的上表面ts1可在第一方向d1上高于第二深阱区dw2的上表面ts2。此外,第一深阱区dw1的第二部分p12可直接与第一隔离结构20相

连,由此对部分的第一阱区30(例如靠近源极掺杂区60的第一阱区30)形成隔离效果,但并不以此为限。

86.请参阅图14。图14所绘示为本发明第十二实施例的高压半导体装置112的示意图。如图14所示,在高压半导体装置112中,第一深阱区dw1的第二部分p12可在水平方向上围绕第二深阱区dw2,且第一深阱区dw1的第二部分p12的上表面ts1可在第一方向d1上高于第二深阱区dw2的上表面ts2。此外,第一深阱区dw1的第二部分p12可直接与第一隔离结构20相连,且第一阱区30的一部分可于第二方向d2上位于第二深阱区dw2与第一深阱区dw1的第二部分p12之间,但并不以此为限。

87.请参阅图15。图15所绘示为本发明第十三实施例的高压半导体装置113的示意图。如图15所示,高压半导体装置113可还包括一第三阱区42设置于半导体基底10中,而第三阱区42可在第一方向d1上位于第一隔离结构20与第一深阱区dw1之间。在一些实施例中,第三阱区42可为具有第二导电型态的掺杂阱区,故第三阱区42的导电型态可与第一阱区30的导电型态互补。此外,设置于第一隔离结构20与第一深阱区dw1之间的第三阱区42可分别与第一隔离结构20以及第一深阱区dw1直接相连,由此对部分的第一阱区30(例如靠近源极掺杂区60的第一阱区30)形成隔离效果,但并不以此为限。在一些实施例中,第一深阱区dw1与第三阱区42可具有相同的导电型态但由不同的制作工艺步骤分别形成,故第三阱区42中的掺杂物或/及掺杂物浓度可不同于第一深阱区dw1中的掺杂物或/及掺杂物浓度,但并不以此为限。此外,第一阱区30的一部分可在第二方向d2上位于第三阱区42与第二深阱区dw2之间。

88.请参阅图16。图16所绘示为本发明第十四实施例的高压半导体装置114的示意图。如图16所示,在高压半导体装置114中,第一深阱区dw1的第二部分p12可在水平方向上围绕第二深阱区dw2,且第一深阱区dw1的第二部分p12的上表面ts1可在第一方向d1上高于第二深阱区dw2的上表面ts2或与第二深阱区dw2的上表面ts2大体上共平面。此外,第三阱区42可在第一方向d1上位于第一隔离结构20与第一深阱区dw1的第二部分p12之间,且第三阱区42可分别与第一隔离结构20以及第一深阱区dw1的第二部分p12直接相连,由此对部分的第一阱区30(例如靠近源极掺杂区60的第一阱区30)形成隔离效果,但并不以此为限。

89.综上所述,在本发明的高压半导体装置中,可利用在第一深阱区与第二阱区之间设置第二深阱区并使第二深阱区的范围小于第一深阱区的范围,故可使第一阱区与第一深阱区相连,由此在对第二阱区与半导体基底之间形成隔离效果的状况下达到提升高压半导体装置电性表现的效果。例如可在相对较小的高压半导体装置所占面积状况下达到改善导通电阻的效果。

90.以上所述仅为本发明的优选实施例,凡依本发明权利要求所做的均等变化与修饰,都应属本发明的涵盖范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。