1.本技术涉及电子设备技术领域,尤其涉及一种电路板组件、电子设备和电路板组件的加工方法。

背景技术:

2.目前,折叠屏手机、平板手机、平板电脑等电子设备的设计越来越注重整体的薄型化,这些电子设备内,电路板组件的厚度为限制整机厚度的主要因素之一。

3.现有技术中,电路板组件包括印制电路板以及设置于印制电路板上的电子元器件。随着电子设备功能的逐渐丰富以及性能的逐渐提升,印制电路板上所需设置的电子元器件的数量越来越多。为了在不增加印制电路板的面积的同时,增大印制电路板上集成的电子元器件的数量,可以采用叠层封装(package on package,pop)技术将至少两个电子元器件层叠封装在印制电路板上的同一区域位置,但是,这样又大幅度增大了电路板组件的厚度。在此基础上,如何降低电路板组件的厚度,以实现电子设备的薄型化设计,是各厂商研究的重要方向。

技术实现要素:

4.本技术的实施例提供一种电路板组件、电子设备和电路板组件的加工方法,能够减小电路板组件的厚度,以实现电子设备的薄型化设计。

5.为达到上述目的,本技术的实施例采用如下技术方案:

6.第一方面,本技术一些实施例提供一种电路板组件,该电路板组件包括电路板和第一电子元器件;电路板的表面设有凹槽,凹槽的底面阵列设有多个第一焊盘;第一电子元器件具有第一表面,第一表面与凹槽的底面相对,第一表面阵列设有多个第一导电件,该多个第一导电件向靠近凹槽的底面的方向凸出,且多个第一导电件的靠近凹槽的底面的端部分别与多个第一焊盘相接,多个第一导电件的位于第一表面与第一焊盘之间的部分在与电路板垂直的方向上的高度h满足:h<(0.21

×

lnd 0.36)mm;其中,d为多个第一导电件在第一表面的阵列间距。

7.在本技术实施例提供的电路板组件中,由于电路板的表面设有凹槽,凹槽的底面阵列设置有多个第一焊盘,第一电子元器件通过多个第一导电件与该多个第一焊盘相接。因此,至少第一导电件沉入凹槽内设置,在第一导电件的高度不变的前提下,能够减小第一电子元器件凸出电路板表面的高度,降低电路板组件的厚度,有利于电子设备的薄型化设计。同时,由于多个第一导电件的位于第一表面与第一焊盘之间的部分在与电路板垂直的方向上的高度h满足:h<0.21

×

lnd 0.36,单位:mm,该h小于现有技术中采用锡膏印刷工艺焊接时焊接区域的高度h0(h0≥0.21

×

lnd0 0.36),其中,针对同一电子元器件,d=d0。因此,能够进一步减小电路板组件的厚度。

8.在第一方面的一种可能的实现方式中,第一电子元器件为晶圆级封装结构,第一导电件内锡的质量占比大于或者等于95.5%%,并小于95.71%。也即是,第一导电件内sn

的质量占比的区间为[95.5%,95.71%)。由于晶圆级封装结构的引脚通常为sac405焊球,sac405焊球内sn的质量占比为95.5%。因此第一导电件内sn的质量占比的区间为[95.5%,95.71%),则可以确定,第一电子元器件通过自身引脚直接与第一焊盘相接,未在第一电子元器件的引脚与第一焊盘之间设置锡膏,因此多个第一导电件的位于第一表面与第一焊盘之间的部分在与电路板垂直的方向上的高度较小,能够进一步减小第一电子元器件凸出电路板表面的高度,降低电路板组件的厚度,有利于电子设备的薄型化设计。

[0009]

在第一方面的一种可能的实现方式中,第一电子元器件为扇入型晶圆级芯片尺寸封装结构或扇出型晶圆级芯片尺寸封装结构。

[0010]

在第一方面的一种可能的实现方式中,第一电子元器件为非晶圆级封装结构,第一导电件内锡的质量占比大于97.89%,并小于或者等于98.25%。也即是,第一导电件内sn的质量占比的区间为(97.89%,98.25%]。由于非晶圆级封装结构的引脚通常为lf35焊球,lf35焊球内sn的质量占比为98.25%。同时由于现有技术中采用锡膏印刷工艺将lf35焊球焊接于电路板上之后形成的焊接部分内sn的质量占比通常为97.89%,因此若第一导电件内sn的质量占比的区间为(97.89%,98.25%],则可以确定,第一电子元器件通过自身引脚直接与第一焊盘相接,未在第一电子元器件的引脚与第一焊盘之间设置锡膏,因此多个第一导电件的位于第一表面与第一焊盘之间的部分在与电路板垂直的方向上的高度h较小,能够进一步减小第一电子元器件凸出电路板表面的高度,降低电路板组件的厚度,有利于电子设备的薄型化设计。

[0011]

在第一方面的一种可能的实现方式中,第一电子元器件为倒装芯片型芯片尺寸封装结构、倒装芯片型球栅格阵列封装结构或引线键合型球栅格阵列封装结构。

[0012]

在第一方面的一种可能的实现方式中,电路板包括由金属层和绝缘介质层依次交替并堆叠而成的多层布线结构;凹槽贯穿多层布线结构的至少一层金属层和至少一层绝缘介质层,且多个第一焊盘位于多层布线结构的一层金属层内。这样,由多层布线结构的一层金属层形成该多个第一焊盘,无需再另外设置焊盘,因此能够降低电路板组件的结构复杂度和加工难度。

[0013]

在第一方面的一种可能的实现方式中,电路板还包括设置于多层布线结构的表面的阻焊层,凹槽还贯穿该阻焊层。

[0014]

在第一方面的一种可能的实现方式中,凹槽贯穿多层布线结构的一层金属层和一层绝缘介质层。

[0015]

在第一方面的一种可能的实现方式中,凹槽贯穿多层布线结构的两层金属层和两层绝缘介质层。

[0016]

在第一方面的一种可能的实现方式中,第一电子元器件还具有与第一表面背对的第二表面,第二表面阵列设有多个第二焊盘;电路板组件还包括第二电子元器件,该第二电子元器件位于第二表面的远离第一表面的一侧,第二电子元器件具有第三表面,该第三表面与所述第二表面相对,且第三表面阵列设有多个第二导电件,多个第二导电件向靠近第二表面的方向凸出,且多个第二导电件的靠近第二表面的端部分别与多个第二焊盘相接。这样,将两个电子元器件(包括第一电子元器件和第二电子元器件)层叠设置于电路板上的同一区域位置,能够在不增大电路板的面积的前提下,使得电路板能够承载更多的电子元器件。

[0017]

在第一方面的一种可能的实现方式中,第一电子元器件为处理器芯片,第二电子元器件为存储器芯片。

[0018]

在第一方面的一种可能的实现方式中,第一电子元器件为ap,第二电子元器件为ddr。

[0019]

在第一方面的一种可能的实现方式中,多个第二导电件的位于第三表面与第二焊盘之间的部分在与电路板垂直的方向上的高度h2满足:h2<0.21

×

lnd2 0.36,单位:mm。其中,d2为多个第二导电件在第三表面的阵列间距。该h2小于现有技术中采用锡膏印刷工艺焊接时焊接区域的高度h0(h0≥0.21

×

lnd0 0.36),其中,针对同一电子元器件,d2=d0。因此,能够在一定程度上减小第一电子元器件与第二电子元器件组成的层叠结构凸出电路板的高度,减小电路板组件的厚度。

[0020]

在第一方面的一种可能的实现方式中,电路板的表面阵列设有多个第三焊盘,该多个第三焊盘与凹槽位于电路板的同一表面;电路板组件还包括第三电子元器件,该第三电子元器件和第一电子元器件位于电路板的同一侧;第三电子元器件具有第四表面,该第四表面朝向电路板,且第四表面阵列设有多个第三导电件,该多个第三导电件向靠近电路板的方向凸出,且多个第三导电件的靠近电路板的端部分别与多个第三焊盘相接,多个第三导电件的位于第四表面与第三焊盘之间的部分在与电路板垂直的方向上的高度h1满足:h1≥(0.21

×

lnd1 0.36)mm;其中,d1为多个第三导电件在第四表面的阵列间距。这样,该第三电子元器件在电路板上采用了锡膏印刷工艺实现焊接,锡膏印刷工艺焊接时的效率较高,能够同时兼顾电路板组件的厚度和加工效率。

[0021]

第二方面,本技术一些实施例提供一种电子设备,该电子设备包括壳体、功能器件和如上任一技术方案所述的电路板组件;功能器件设置于壳体内;电路板组件设置于壳体内,且电路板组件与功能器件电连接。

[0022]

由于本技术实施例提供的电子设备包括如上任一技术方案所述的电路板组件,因此二者能够解决相同的技术问题,并达到相同的技术效果。

[0023]

第三方面,本技术一些实施例提供一种电路板组件的加工方法,其中,电路板组件包括电路板和第一电子元器件;电路板的表面设有凹槽,该凹槽的底面阵列设有多个第一焊盘;第一电子元器件具有第一表面,第一表面阵列设有多个第一引脚,电路板组件的加工方法包括:在多个第一引脚的表面设置助焊剂;通过助焊剂将该多个第一引脚分别粘接于多个第一焊盘上;加热熔融多个第一引脚,并使助焊剂挥发,以使多个第一引脚分别与多个第一焊盘相接成一个整体,每个第一引脚与残留于该第一引脚上的助焊剂形成第一导电件。

[0024]

在本技术实施例提供的电路板组件的加工方法中,由于第一电子元器件的多个第一引脚通过助焊剂分别粘接于多个第一焊盘上,且在加热熔融多个第一引脚时,助焊剂挥发,因此,第一电子元器件与多个第一焊盘之间的导电结构(也即是第一导电件的位于第一表面与第一焊盘之间的部分)的体积较小,可以降低第一电子元器件凸出电路板的高度,减小电路板组件的厚度,有利于电子设备的薄型化设计。同时,由于在本技术实施例提供的电路板组件的加工方法中,未在凹槽底面的第一焊盘上印刷或者喷涂锡膏,因此无需设置阶梯钢网进行锡膏印刷,也无需引进精度较高的喷锡设备,因此不会大幅度增加电路板组件的加工成本。

[0025]

在第三方面的一种可能的实现方式中,电路板的表面阵列设有多个第三焊盘,该多个第三焊盘与凹槽位于电路板的同一表面;电路板组件还包括第三电子元器件,该第三电子元器件具有第四表面,该第四表面阵列设有多个第二引脚;电路板组件的加工方法还包括:在多个第三焊盘上设置锡膏;通过锡膏将多个第二引脚分别粘接于多个第三焊盘上;加热熔融多个第二引脚和多个第三焊盘上的锡膏,以使多个第二引脚分别与多个第三焊盘上的锡膏熔合成一个整体,每个第二引脚与对应的第三焊盘上的锡膏熔合后形成的结构为第三导电件。由于多个第三焊盘设置于电路板的表面,因此可以采用锡膏印刷工艺实现锡膏在该多个第三焊盘上的设置,以提高电路板组件的加工效率。

[0026]

在第三方面的一种可能的实现方式中,在多个第三焊盘上设置锡膏包括:采用锡膏印刷工艺在所述多个第三焊盘上设置锡膏。由于锡膏印刷工艺的效率较高,因此能够提高电路板组件的加工效率。

附图说明

[0027]

图1为本技术一些实施例提供的电子设备的立体图;

[0028]

图2为图1所示电子设备的爆炸图;

[0029]

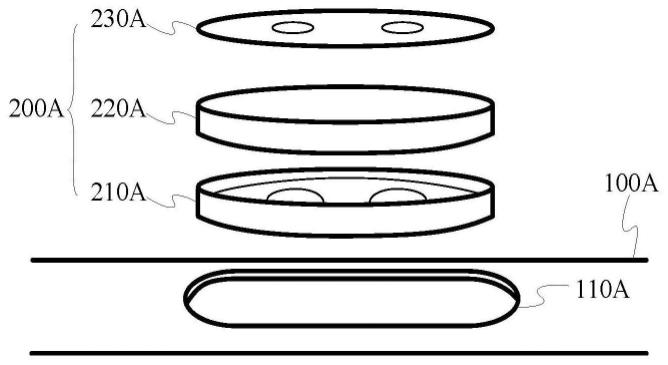

图3a为本技术一些实施例提供的电路板组件的立体图;

[0030]

图3b为图3a所示电路板组件的截面结构示意图;

[0031]

图4为本技术又一些实施例提供的电路板组件的截面结构示意图;

[0032]

图5为图4所示电路板组件中电路板的一种截面结构示意图;

[0033]

图6为图5所示电路板的俯视图;

[0034]

图7为图4所示电路板组件中电路板的又一种截面结构示意图;

[0035]

图8为图4的局部放大图;

[0036]

图9为图8中区域i的局部放大图;

[0037]

图10为本技术又一些实施例提供的电路板组件的结构示意图;

[0038]

图11为本技术又一些实施例提供的电路板组件的结构示意图;

[0039]

图12为本技术又一些实施例提供的电路板组件的结构示意图;

[0040]

图13为本技术一些实施例提供的电路板组件的加工方法的流程图。

具体实施方式

[0041]

在本技术实施例中,术语“第一”、“第二”、“第三”、“第四”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”、“第三”、“第四”的特征可以明示或者隐含地包括一个或者更多个该特征。

[0042]

在本技术实施例中,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、物品或者装置不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、物品或者装置所固有的要素。在没有更多限制的情况下,由语句“包括一个

……”

限定的要素,并不排除在包括该要素的过程、方法、物品或者装置中还存在另外的相同要素。

[0043]

本技术提供一种电子设备,该电子设备为追求厚度薄型化的一类电子设备,具体地,该电子设备可以是折叠屏手机、平板手机、平板电脑、平板导航仪等等。

[0044]

请参阅图1和图2,图1为本技术一些实施例提供的电子设备的立体图,图2为图1所示电子设备的爆炸图。在本实施例中,电子设备为平板手机,平板手机的厚度越小,手感越好。具体地,电子设备包括壳体10、功能器件20和电路板组件30。

[0045]

壳体10为由前盖板(图中未示出)、边框11和后盖12拼接形成的壳体结构,用于保护电子设备内的功能器件20和电路板组件30。

[0046]

功能器件20设置于壳体10内,功能器件20用于实现电子设备的某一项或者多项功能。功能器件20包括但不限于摄像头模组、显示屏、扬声器、受话器、天线、麦克风、通用串行总线(universal serial bus,usb)接口、用户标识模块(subscriber identification module,sim)卡接口、按键等等。

[0047]

电子设备内的功能器件20的数量可以为一个,也可以为多个。当电子设备内的功能器件20的数量为一个时,该功能器件20可以为摄像头模组、显示屏、扬声器、受话器、天线、麦克风、usb接口、sim卡接口、按键中的一个。当电子设备内的功能器件20的数量为多个时,该多个功能器件20可以分别为摄像头模组、显示屏、扬声器、受话器、天线、麦克风、usb接口、sim卡接口、按键中的多个。在图1和图2所示的实施例中,功能器件20的数量为3个,该3个功能器件20均为摄像头模组。

[0048]

电路板组件30设置于壳体10内,且电路板组件30与功能器件20电连接。电路板组件30用于对功能器件20进行信号控制、数据信号处理以及数据信号存储等操作。电路板组件30可以为电子设备的主板,也可以为电子设备的其他电路板,比如为平板手机内用于承载扬声器(speaker)和usb接口的电路板,在此不作具体限定。以下以电路板组件30为电子设备的主板为例进行说明,这并不能认为是对本技术构成的特殊限制。

[0049]

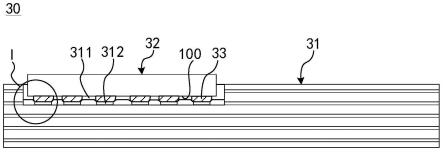

请参阅图3a和图3b,图3a为本技术一些实施例提供的电路板组件30的立体图,图3b为图3a所示电路板组件30的截面结构示意图。在本实施例中,电路板组件30为图2所示电子设备中的电路板组件30。具体地,电路板组件30包括电路板31以及设置于电路板31上的多个电子元器件a。

[0050]

电子元器件a包括但不限于电阻、电容、电感、电位器、电子管、散热器、机电元件、连接器、半导体分立器件、电声器件、激光器件、电子显示器件、光电器件、传感器、电源、开关、微特电机、电子变压器、继电器、印制电路板、集成电路器件等。需要说明的是,本技术实施例不对电子元器件a在电路板31上的设置数量以及排布方式进行限定,图3a和图3b仅给出了电子元器件a在电路板31上的一种设置数量及排布方式示例。

[0051]

电路板31用于承载该多个电子元器件a,并实现该多个电子元器件a之间的电连接。电路板31包括但不限于印制电路板(printed circuit board,pcb)和柔性电路(flexible printed circuit,fpc)板。在图3a和图3b所示的实施例中,电路板31为pcb板。电路板31的形状包括但不限于矩形、正方形、多边形、圆形等等,在图3a和图3b所示的实施例中,电路板31的形状近似为矩形。

[0052]

现有技术中,为了减小电路板组件30的体积,通常将电子元器件a的多个引脚阵列布局在该电子元器件的一个表面,并采用表面贴装技术(surface mounted technology,smt)将该表面的引脚贴装并焊接于电路板31的焊盘上。这样,电子元器件a在电路板31上的占用面积较小,且电子元器件a与电路板31之间的焊接部位在与电路板31垂直的方向上的高度较小,能够减小电路板组件30的体积。

[0053]

在上述实施例的基础上,为了提高多个电子元器件a在电路板31上的安装效率,通常采用锡膏印刷工艺一次性在电路板31的一个表面的所有焊盘上印刷锡膏,然后将多个电子元器件a的引脚分别贴装于焊盘的锡膏上,并采用回流焊工艺将多个电子元器件a的引脚与锡膏熔融并固化为一体,由此能够提高多个电子元器件a在电路板31上的安装效率。

[0054]

在上述实施例中,锡膏印刷工艺的原理为将锡膏通过平面钢网上的孔印置于电路板31的焊盘上。由于在电路板31的焊盘上印刷了锡膏,因此电子元器件a与电路板31之间的焊接区域为引脚与锡膏的叠加,因此焊接区域的高度h0较大,通常h0≥0.21

×

lnd0 0.36,单位:mm,d0表示电子元器件a的引脚的阵列间距。其中,当电子元器件a的引脚均匀阵列时,电子元器件a的引脚的阵列间距是指任意相邻两个引脚之间的距离;当电子元器件a的引脚非均匀阵列时,电子元器件a的引脚的阵列间距是指距离最近的两个引脚之间的距离。这样,电子元器件a凸出电路板31表面的高度较大,电路板组件30的厚度较大,不利于电子设备的薄型化设计。为了降低电路板组件30的厚度,可以在电路板31的表面设置凹槽,并将焊盘设置于凹槽的底面,然后将电子元器件a沉设于该凹槽内,并采用上述smt将电子元器件a焊接于凹槽底面的焊盘上。但是,由于凹槽底面的焊盘与电路板表面的焊盘不共面,因此不能采用平面钢网在电路板上印刷锡膏,而需要定制特殊的阶梯钢网进行锡膏印刷,或者,引进精度较高的喷锡设备将锡膏喷涂至凹槽底面的焊盘上,电路板表面的焊盘则采用传统的锡膏印刷工艺印刷锡膏。无论是定制特殊的阶梯钢网,还是引进精度较高的喷锡设备,都不可避免地分别增大了电路板组件的加工工序或加工成本。

[0055]

为了在不大幅度增大电路板组件的加工成本的同时,降低电路板组件的厚度,请参阅图4,图4为本技术又一些实施例提供的电路板组件30的截面结构示意图。在本实施例中,电路板组件30包括电路板31和第一电子元器件32。

[0056]

电路板31包括但不限于pcb板和fpc板。一些实施例中,电路板31为pcb板,具体地,请参阅图5和图6,图5为图4所示电路板组件30中电路板31的一种截面结构示意图,图6为图5所示电路板31的俯视图,电路板31包括由金属层31a和绝缘介质层31b依次交替并堆叠而成的多层布线结构。一些实施例中,电路板31还包括设置于多层布线结构的表面的阻焊层31c。

[0057]

电路板31的表面设有凹槽311,凹槽311的底面阵列设置有多个第一焊盘312,该多个第一焊盘312用于焊接第一电子元器件32。

[0058]

一些实施例中,请继续参阅图5和图6,电路板31为pcb板,凹槽311贯穿多层布线结构的至少一层金属层31a和至少一层绝缘介质层31b。具体地,凹槽311可以贯穿多层布线结构的一层金属层31a和一层绝缘介质层31b,也可以贯穿多层布线结构的两层金属层31a和两层绝缘介质层31b,还可以贯穿多层布线结构的三层金属层31a和三层绝缘介质层31b,具体可以根据电路板31的厚度以及电路板31内金属层31a和绝缘介质层31b的层数进行综合确定,只要该凹槽311所贯穿的金属层31a和绝缘介质层31b的层数不影响电路板31的结构强度即可,在此不作具体限定。在图5和图6所示的实施例中,凹槽311贯穿了多层布线结构的一层金属层31a和一层绝缘介质层31b。在又一些实施例中,请参阅图7,图7为图4所示电路板组件30中电路板31的又一种截面结构示意图,在本实施例中,凹槽311贯穿了多层布线结构的两层金属层31a和两层绝缘介质层31b。

[0059]

需要说明的是,当电路板31还包括设置于多层布线结构的表面的阻焊层31c时,凹

槽311还贯穿该阻焊层31c。

[0060]

进一步地,多个第一焊盘312位于多层布线结构的一层金属层31a内。这样,由多层布线结构的一层金属层31a形成该多个第一焊盘312,无需再另外设置焊盘,因此能够降低电路板组件30的结构复杂度和加工难度。

[0061]

一些实施例中,请参阅图5或图7,凹槽311的底面还设有阻焊层31c,该阻焊层31c未覆盖多个第一焊盘312。

[0062]

第一电子元器件32包括但不限于电阻、电容、电感、电位器、电子管、散热器、机电元件、连接器、半导体分立器件、电声器件、激光器件、电子显示器件、光电器件、传感器、电源、开关、微特电机、电子变压器、继电器、印制电路板、集成电路器件等。

[0063]

一些实施例中,第一电子元器件32为集成电路器件(integrated circuit,ic),具体地,第一电子元器件32包括但不限于应用处理器(application processor,ap)、双倍速率同步动态随机存储器(double data rate,ddr)和通用闪存存储(universal flash storage,ufs)。在此基础上,第一电子元器件32的封装方式可以为晶圆级封装(wafer level package,wlp),也可以为非晶圆级封装。其中,晶圆级封装包括但不限于扇入型晶圆级芯片尺寸封装(fan-in wafer level chip scale package,fan-in wlcsp)和扇出型晶圆级芯片尺寸封装(fan-out wafer level chip scale package,fan-out wlcsp)。非晶圆级封装包括但不限于倒装芯片型芯片尺寸封装(flip chip-chip scale package,fc-csp)、倒装芯片型球栅格阵列(flip chip-ball grid array,fcbga)封装和引线键合型球栅格阵列(wire bonding-ball grid array,wbbga)封装,在此不作具体限定。

[0064]

请参阅图8和图9,图8为图4的局部放大图,图9为图8中区域i的局部放大图。在本实施例中,电路板31为图5所示的电路板31,可以理解的是,该电路板31也可以为图7所示的电路板31,在此不作具体限定。第一电子元器件32具有第一表面100,第一表面100与凹槽311的底面相对。需要说明的是,第一表面100与凹槽311的底面相对,是指:第一表面100朝向凹槽311的底面,且第一表面100在凹槽311的底面上的正投影与凹槽311的底面有交叠。

[0065]

第一表面100阵列设有多个第一导电件33,该多个第一导电件33用于引出第一电子元器件32的内部电路。

[0066]

多个第一导电件33向靠近凹槽311的底面的方向凸出,且该多个第一导电件33的靠近凹槽311的底面的端部分别与多个第一焊盘312相接。其中,“相接”表示接合并形成一个整体。

[0067]

需要说明的是,多个第一导电件33分别与多个第一焊盘312相接,包括以下三种实现方式中的一种或者多种组合;具体地,该三种实现方式包括:一个第一导电件33与一个第一焊盘312对应相接,多个第一导电件33与一个第一焊盘312对应相接,一个第一导电件33与多个第一焊盘312对应相接。图8仅给出了多个第一导电件33的数量与多个第一焊盘312的数量相等,且多个第一导电件33与多个第一焊盘312一一对应相接的示例,这并不能认为是对本技术构成的特殊限制。

[0068]

多个第一导电件33的位于第一表面100与第一焊盘312之间的部分在与电路板31垂直的方向(也即是方向z)上的高度h满足:h<0.21

×

lnd 0.36,单位:mm。d为多个第一导电件33在第一表面100的阵列间距。其中,当多个第一导电件33在第一表面100上均匀阵列时,多个第一导电件33在第一表面100的阵列间距是指:相邻两个第一导电件33在第一表面

100上的占用区域的中心之间的距离。当多个第一导电件33在第一表面100上非均匀阵列时,该多个第一导电件33在第一表面100的阵列间距是指:多个第一导电件33中,距离最近的两个第一导电件300在第一表面100上的占用区域的中心之间的距离。

[0069]

在本技术实施例提供的电路板组件30中,由于电路板31的表面设有凹槽311,凹槽311的底面阵列设置有多个第一焊盘312,第一电子元器件32通过多个第一导电件33与该多个第一焊盘312相接。因此,至少第一导电件33沉入凹槽311内设置,在第一导电件33的高度不变的前提下,能够减小第一电子元器件32凸出电路板31表面的高度,降低电路板组件30的厚度,有利于电子设备的薄型化设计。同时,由于多个第一导电件33的位于第一表面100与第一焊盘312之间的部分在与电路板31垂直的方向上的高度h满足:h<0.21

×

lnd 0.36,单位:mm,该h小于现有技术中采用锡膏印刷工艺焊接时焊接区域的高度h0(h0≥0.21

×

lnd0 0.36),其中,针对同一电子元器件,d=d0。因此,能够进一步减小电路板组件30的厚度,同时可以确定第一电子元器件32在与电路板31焊接过程中未在第一焊盘312上印刷或者喷涂锡膏,因此无需设置阶梯钢网进行锡膏印刷,也无需引进精度较高的喷锡设备,因此可以不大幅度增加电路板组件的加工成本。

[0070]

一些实施例中,第一电子元器件32为晶圆级封装结构。一些实施例中,第一电子元器件32为fan-in wlcsp结构或者fan-out wlcsp结构。第一导电件33内锡(化学符号:sn)的质量占比大于等于95.5%,并小于95.71%。也即是,第一导电件33内sn的质量占比的区间为[95.5%,95.71%)。

[0071]

由于晶圆级封装结构的引脚通常为sac405焊球,sac405焊球内sn的质量占比为95.5%。因此第一导电件33内sn的质量占比的区间为[95.5%,95.71%),则可以确定,第一电子元器件32通过自身引脚直接与第一焊盘312相接,未在第一电子元器件32的引脚与第一焊盘312之间设置锡膏,因此多个第一导电件33的位于第一表面100与第一焊盘312之间的部分在与电路板31垂直的方向上的高度h较小,能够进一步减小第一电子元器件32凸出电路板31表面的高度,降低电路板组件30的厚度,有利于电子设备的薄型化设计。

[0072]

在另一些实施例中,第一电子元器件32为非晶圆级封装结构。一些实施例中,第一电子元器件32为fc-csp结构、fcbga封装结构或者wbbga封装结构。第一导电件33内sn的质量占比大于97.89%,并小于或者等于98.25%。也即是,第一导电件33内sn的质量占比的区间为(97.89%,98.25%]。

[0073]

由于非晶圆级封装结构的引脚通常为lf35焊球,lf35焊球内sn的质量占比为98.25%。同时由于现有技术中采用锡膏印刷工艺将lf35焊球焊接于电路板上之后形成的焊接部分内sn的质量占比通常为97.89%,因此若第一导电件33内sn的质量占比的区间为(97.89%,98.25%],则可以确定,第一电子元器件32通过自身引脚直接与第一焊盘312相接,未在第一电子元器件32的引脚与第一焊盘312之间设置锡膏,因此多个第一导电件33的位于第一表面100与第一焊盘312之间的部分在与电路板31垂直的方向上的高度h较小,能够进一步减小第一电子元器件32凸出电路板31表面的高度,降低电路板组件30的厚度,有利于电子设备的薄型化设计。

[0074]

为了在不增大电路板31的面积的前提下,使得电路板31能够承载更多的电子元器件,在一些实施例中,请参阅图10,图10为本技术又一些实施例提供的电路板组件30的结构示意图。在本实施例中,第一电子元器件32除了具有第一表面100之外,还具有与第一表面

100背对的第二表面200,第二表面200阵列设有多个第二焊盘313。电路板组件30除了包括电路板31和第一电子元器件32之外,还包括第二电子元器件34。该第二电子元器件34位于第二表面200的远离第一表面100的一侧。第二电子元器件34具有第三表面300,该第三表面300与第二表面200相对。第三表面300阵列设有多个第二导电件35,该多个第二导电件35用于引出第二电子元器件34的电路。多个第二导电件35向靠近第二表面200的方向凸出,且多个第二导电件35的靠近第二表面200的端部分别与多个第二焊盘313相接。这样,将两个电子元器件(包括第一电子元器件32和第二电子元器件34)层叠设置于电路板31上的同一区域位置,能够在不增大电路板31的面积的前提下,使得电路板31能够承载更多的电子元器件。

[0075]

其中,需要说明的是,多个第二导电件35分别与多个第二焊盘313相接,包括以下三种实现方式中的一种或者多种组合;具体地,该三种实现方式包括:一个第二导电件35与一个第二焊盘313对应相接,多个第二导电件35与一个第二焊盘313对应相接,一个第二导电件35与多个第二焊盘313对应相接。图10仅给出了多个第二导电件35的数量与多个第二焊盘313的数量相等,且多个第二导电件35与多个第二焊盘313一一对应相接的示例,这并不能认为是对本技术构成的特殊限制。

[0076]

一些实施例中,第一电子元器件32为处理器芯片,第二电子元器件34为存储器芯片。具体地,第一电子元器件32包括但不限于ap,第二电子元器件34包括但不限于ddr。

[0077]

一些实施例中,多个第二导电件35的位于第三表面300与第二焊盘313之间的部分在与电路板31垂直的方向上的高度h2满足:h2<0.21

×

lnd2 0.36,单位:mm。其中,d2为多个第二导电件35在第三表面300的阵列间距。该h2小于现有技术中采用锡膏印刷工艺焊接时焊接区域的高度h0(h0≥0.21

×

lnd0 0.36),其中,针对同一电子元器件,d2=d0。因此,能够在一定程度上减小第一电子元器件32与第二电子元器件34组成的层叠结构凸出电路板31的高度,减小电路板组件30的厚度。

[0078]

电路板31的表面除了设有凹槽311,以减小第一电子元器件32凸出电路板31的高度之外,通常还设有其他焊盘以连接其他电子元器件,该其他焊盘的数量以及所需连接的电子元器件的数量较多,可以采用锡膏印刷工艺来保证电路板组件30的加工效率。

[0079]

一些实施例中,请参阅图11,图11为本技术又一些实施例提供的电路板组件30的结构示意图。在本实施例中,电路板31的表面阵列设有多个第三焊盘314,一些实施例中,多个第三焊盘314由多层布线结构的一层金属层形成。多个第三焊盘314与凹槽311位于电路板31的同一表面。电路板组件30还包括第三电子元器件36,该第三电子元器件36和第一电子元器件32位于电路板31的同一侧。第三电子元器件36具有第四表面400,该第四表面400朝向电路板31。第四表面400阵列设有多个第三导电件37,该多个第三导电件37向靠近电路板31的方向凸出,且多个第三导电件37的靠近电路板31的端部分别与多个第三焊盘314相接。

[0080]

其中,需要说明的是,多个第三导电件37分别与多个第三焊盘314相接,包括以下三种实现方式中的一种或者多种组合;具体地,该三种实现方式包括:一个第三导电件37与一个第三焊盘314对应相接,多个第三导电件37与一个第三焊盘314对应相接,一个第三导电件37与多个第三焊盘314对应相接。图11仅给出了多个第三导电件37的数量与多个第三焊盘314的数量相等,且多个第三导电件37与多个第三焊盘314一一对应相接的示例,这并

不能认为是对本技术构成的特殊限制。

[0081]

另外,多个第三导电件37的位于第四表面400与第三焊盘314之间的部分在与电路板31垂直的方向上的高度h1满足:h1≥(0.21

×

lnd1 0.36),单位:mm;其中,d1为多个第三导电件37在第四表面400的阵列间距。这样,该第三电子元器件36在电路板31上采用了锡膏印刷工艺实现焊接,锡膏印刷工艺焊接时的效率较高,能够同时兼顾电路板组件30的厚度和加工效率。

[0082]

第三电子元器件36包括但不限于卡座、电阻、电容、电感、电位器、电子管、散热器、机电元件、连接器、半导体分立器件、电声器件、激光器件、电子显示器件、光电器件、传感器、电源、开关、微特电机、电子变压器、继电器、印制电路板、集成电路器件等。在图11所示的实施例中,第三电子元器件36为ufs。

[0083]

电路板31上设置的第三电子元器件36的数量可以为一个,也可以为多个,在此不做具体限定。图11仅给出了电路板31上设置的第三电子元器件36的数量为一个的示例,这并不能认为是对本技术构成的特殊限制。另一些实施例中,请参阅图12,图12为本技术又一些实施例提供的电路板组件的结构示意图。在本实施例中,第三电子元器件36的数量为两个,该两个第三电子元器件36分别为ufs和卡座。

[0084]

一些实施例中,请继续参阅图12,电路板31上还设有第四电子元器件38和第五电子元器件39。第四电子元器件38和第五电子元器件39的数量可以为一个,也可以为多个,在此不作具体限定。一些实施例中,第四电子元器件38为连接器,该第四电子元器件38用于将射频(radio frequency,rf)电路板组件40电连接至电路板31上。第五电子元器件39包括但不限于卡座、电阻、电容、电感、电位器、电子管、散热器、机电元件、连接器、半导体分立器件、电声器件、激光器件、电子显示器件、光电器件、传感器、电源、开关、微特电机、电子变压器、继电器、印制电路板、集成电路器件等。第四电子元器件38和第三电子元器件36分别位于电路板31的相对两侧,第五电子元器件39与第四电子元器件38位于电路板31的同一侧。第四电子元器件38和第五电子元器件39采用锡膏印刷工艺焊接于电路板31上。

[0085]

本技术还提供一种电路板组件30的加工方法,该电路板组件30包括电路板31和第一电子元器件32。电路板31的表面设有凹槽311,凹槽311的底面阵列设有多个第一焊盘312。第一电子元器件32具有第一表面100,第一表面100阵列设有多个第一引脚,该多个第一引脚用于引出第一电子元器件32的电路。请参阅图13,图13为本技术一些实施例提供的电路板组件30的加工方法的流程图。在本实施例中,电路板组件30的加工方法包括:

[0086]

s100:在多个第一引脚的表面设置助焊剂;其中,助焊剂通常是以松香为主要成分的混合物,是保证焊接过程顺利进行的辅助材料,助焊剂具有一定的黏性,且在加热至预设温度时容易挥发。

[0087]

s200:通过助焊剂将多个第一引脚分别粘接于多个第一焊盘312上;

[0088]

s300:加热熔融多个第一引脚,并使助焊剂挥发,以使多个第一引脚321分别与多个第一焊盘312相接成一个整体。其中,每个第一引脚与残留于该第一引脚上的助焊剂形成第一导电件33。另外,可以采用回流焊工艺加热熔融多个第一引脚,并使助焊剂挥发。

[0089]

在本技术实施例提供的电路板组件30的加工方法中,由于第一电子元器件32的多个第一引脚通过助焊剂分别粘接于多个第一焊盘312上,且在加热熔融多个第一引脚时,助焊剂挥发,因此,第一电子元器件32与多个第一焊盘312之间的导电结构(也即是第一导电

件33的位于第一表面100与第一焊盘312之间的部分)的体积较小,可以降低第一电子元器件32凸出电路板31的高度,减小电路板组件30的厚度,有利于电子设备的薄型化设计。同时,由于在本技术实施例提供的电路板组件30的加工方法中,未在凹槽311底面的第一焊盘312上印刷或者喷涂锡膏,因此无需设置阶梯钢网进行锡膏印刷,也无需引进精度较高的喷锡设备,因此不会大幅度增加电路板组件的加工成本。

[0090]

一些实施例中,电路板31的表面阵列设有多个第三焊盘314,该多个第三焊盘314与凹槽311位于电路板31的同一表面。电路板组件30还包括第三电子元器件36,该第三电子元器件36具有第四表面400,该第四表面400阵列设有多个第二引脚。多个第二引脚用于引出,第三电子元器件36的内部电路。电路板组件30的加工方法还包括:在多个第三焊盘314上设置锡膏;通过锡膏将多个第二引脚分别粘接于多个第三焊盘314上;加热熔融多个第二引脚和多个第三焊盘314上的锡膏,以使多个第二引脚分别与多个第三焊盘314上的锡膏熔合成一个整体,每个第二引脚与对应的第三焊盘314上的锡膏熔合后形成的结构为第三导电件37。

[0091]

由于多个第三焊盘314设置于电路板31的表面,因此可以采用锡膏印刷工艺实现锡膏在该多个第三焊盘314上的设置,以提高电路板组件30的加工效率。

[0092]

具体地,在上述实施例中,在多个第三焊盘314上设置锡膏包括:采用锡膏印刷工艺在多个第三焊盘314上设置锡膏。由于锡膏印刷工艺的效率较高,因此能够提高电路板组件30的加工效率。

[0093]

在本说明书的描述中,具体特征、结构、材料或者特点可以在任何的一个或多个实施例或示例中以合适的方式结合。

[0094]

最后应说明的是:以上实施例仅用以说明本技术的技术方案,而非对其限制;尽管参照前述实施例对本技术进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本技术各实施例技术方案的精神和范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。