技术特征:

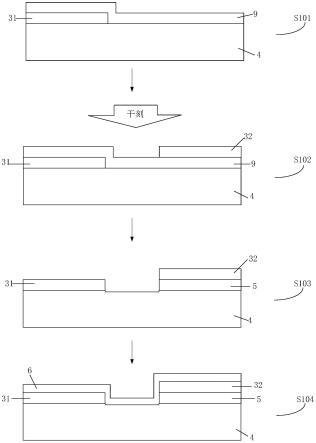

1.一种阵列基板的制备方法,其中,包括:在基底上制备像素驱动电路;在完成上述步骤的所述基底上制备绝缘平坦层;在完成上述步骤的所述基底上制备多个像素电极;所述多个像素电极分别通过开设在所述绝缘平坦层中的过孔连接所述像素驱动电路;所述多个像素电极排布呈阵列;沿所述阵列的行方向和/或列方向,任意相邻两个所述像素电极之间的间隔距离小于或等于设定值;第2n-1个像素电极为第一像素电极;第2n个像素电极为第二像素电极;制备所述像素电极包括:所述第一像素电极通过第一次构图工艺制备;所述第二像素电极通过第二次构图工艺制备;其中,n为正整数。2.根据权利要求1所述的阵列基板的制备方法,其中,制备所述第一像素电极和所述第二像素电极,包括:采用构图工艺在所述绝缘平坦层上形成所述第一像素电极的图形;沉积第一绝缘层膜;采用构图工艺在所述第一绝缘层膜上形成所述第二像素电极的图形;以所述第二像素电极的图形为掩膜,刻蚀形成第一绝缘层的图形。3.根据权利要求1所述的阵列基板的制备方法,其中,制备所述第一像素电极和所述第二像素电极,包括:采用构图工艺在所述绝缘平坦层上形成所述第一像素电极的图形;沉积第一绝缘层膜;通过刻蚀工艺对所述第一绝缘层膜的局部区域进行减薄;所述局部区域为所述第一绝缘层膜的除覆盖所述第一像素电极的图形以外的区域;采用构图工艺在所述第一绝缘层膜减薄的区域形成所述第二像素电极的图形;以所述第二像素电极的图形为掩膜,刻蚀形成第一绝缘层的图形。4.根据权利要求1所述的阵列基板的制备方法,其中,制备所述第一像素电极和所述第二像素电极,包括:采用构图工艺在所述绝缘平坦层上形成所述第一像素电极的图形;对所述第一像素电极进行退火处理,使所述第一像素电极结晶;沉积形成第二像素电极膜层;采用构图工艺形成所述第二像素电极的图形。5.根据权利要求1所述的阵列基板的制备方法,其中,制备所述第一像素电极和所述第二像素电极,包括:采用构图工艺在所述绝缘平坦层上形成所述第一像素电极的图形,同时保留所述第一像素电极的图形上的第一光刻胶图形;所述第一光刻胶图形在所述基底上的正投影只覆盖所述第一像素电极的图形;沉积形成第二像素电极膜层;采用曝光工艺形成第二光刻胶图形;所述第二光刻胶图形在所述基底上的正投影只覆盖所述第二像素电极的图形;刻蚀去除所述第二光刻胶图形覆盖区域以外区域的所述第二像素电极膜层,形成所述

第二像素电极的图形;显影去除所述第一光刻胶图形和所述第二光刻胶图形。6.根据权利要求1所述的阵列基板的制备方法,其中,制备所述第一像素电极和所述第二像素电极,包括:在所述绝缘平坦层上沉积像素电极膜层;采用曝光工艺在所述像素电极膜层上形成正性光刻胶图形;所述正性光刻胶图形在所述基底上的正投影只覆盖所述第一像素电极的图形;采用曝光工艺在所述像素电极膜层上形成负性光刻胶图形;所述负性光刻胶图形在所述基底上的正投影只覆盖所述第二像素电极的图形;刻蚀形成所述第一像素电极的图形和所述第二像素电极的图形;显影去除所述正性光刻胶图形和所述负性光刻胶图形。7.根据权利要求1-6任意一项所述的阵列基板的制备方法,其中,还包括:在所述第一像素电极的图形和所述第二像素电极的图形的背离所述基底的一侧沉积形成第二绝缘层。8.一种阵列基板,其中,包括:基底;像素驱动电路,位于所述基底上;绝缘平坦层,位于所述像素驱动电路背离所述基底的一侧;所述绝缘平坦层的背离所述基底的一侧表面为水平表面;多个像素电极,位于所述绝缘平坦层背离所述基底的一侧,且分别通过开设在所述绝缘平坦层中的过孔连接所述像素驱动电路;所述多个像素电极排布呈阵列;沿所述阵列的行方向和/或列方向,任意相邻两个所述像素电极之间的间隔距离小于或等于2μm;任意相邻的两个所述像素电极分别为第一像素电极和第二像素电极;所述第一像素电极的背离所述基底的一侧表面与所述基底之间的距离和所述第二像素电极的背离所述基底的一侧表面与所述基底之间的距离之差的绝对值范围为0~1500埃。9.根据权利要求8所述的阵列基板,其中,所述像素电极包括第一子部和第二子部,所述第一子部沿所述阵列的行方向延伸,所述第二子部沿所述阵列的列方向延伸,且所述第一子部和所述第二子部连接;所述第一子部的延伸长度小于所述第二子部的延伸长度;所述绝缘平坦层中的过孔在所述基底上的正投影位于所述第一子部在所述基底上的正投影内,所述第一子部通过所述绝缘平坦层中的过孔连接所述像素驱动电路。10.根据权利要求9所述的阵列基板,其中,所述第一像素电极的所述第二子部与所述第二像素电极的所述第二子部的厚度相等;所述第一像素电极与所述绝缘平坦层的水平表面接触;所述第二像素电极与所述绝缘平坦层的水平表面之间还设置有第一绝缘层;所述第一绝缘层在所述基底上的正投影与所述第二像素电极在所述基底上的正投影重合;或者,所述第二像素电极与所述绝缘平坦层的水平表面接触。11.根据权利要求9所述的阵列基板,其中,所述第一像素电极的所述第二子部的厚度大于所述第二像素电极的所述第二子部的厚度;

所述第一像素电极与所述绝缘平坦层的水平表面接触;所述第二像素电极与所述绝缘平坦层的水平表面之间还设置有第一绝缘层;所述第一绝缘层在所述基底上的正投影与所述第二像素电极在所述基底上的正投影重合;所述第一像素电极的所述第二子部的厚度与所述第二像素电极的所述第二子部和所述第一绝缘层的厚度之和相等。12.根据权利要求10-11任意一项所述的阵列基板,其中,还包括第二绝缘层,位于所述像素电极背离所述基底的一侧,所述第二绝缘层在所述基底上的正投影覆盖整个所述基底。13.一种显示装置,其中,包括权利要求8-12任意一项所述的阵列基板。

技术总结

本公开实施例提供一种阵列基板的制备方法,其中,包括:在基底上制备像素驱动电路;在完成上述步骤的所述基底上制备绝缘平坦层;在完成上述步骤的所述基底上制备多个像素电极;所述多个像素电极分别通过开设在所述绝缘平坦层中的过孔连接所述像素驱动电路;所述多个像素电极排布呈阵列;沿所述阵列的行方向和/或列方向,任意相邻两个所述像素电极之间的间隔距离小于或等于设定值;第2n-1个像素电极为第一像素电极;第2n个像素电极为第二像素电极;制备所述像素电极包括:所述第一像素电极通过第一次构图工艺制备;所述第二像素电极通过第二次构图工艺制备;其中,n为正整数。n为正整数。n为正整数。

技术研发人员:谢蒂旎 王久石 姚舜禹 王利波 吴仲远 董学 于静

受保护的技术使用者:京东方科技集团股份有限公司

技术研发日:2022.05.20

技术公布日:2022/8/19

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。