iii族/氮化物磊晶结构及其主动元件与其积体化的制作方法

1.本技术为分案申请,原母案申请号2017104184188,申请日2017-06-06,发明名称iii族/氮化物磊晶结构及其主动元件与其积体化的制作方法。

技术领域

2.本发明是关于一种磊晶结构,特别是关于一种iii族/氮化物半导体系列成长的磊晶结构,其好处是氮化镓铝阻障层(i-algan barrier layer)在具有氮化镓铝缓冲层(i-algan buffer layer)的成长环境下会有较少的缺陷进而降低氮化镓铝阻障层(i-algan barrier layer)的表面缺陷(surface traps)。至于氮化镓铝缓冲层(i-algan buffer layer)正好可以阻挡缓冲层缺陷(buffer trap)的电子进入通道层(channel layer)进而降低电流崩塌效应(current collapse)的问题的崭新的主动元件与其积体化的制作方法。

背景技术:

3.在过去的习知技艺中,以磊晶结构来达到加强型氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管最常见的方式就是1.镓解理面(ga-face)p型氮化镓闸极(p-gan gate)加强型(e-mode)高速电子迁移率晶体管结构(hemt structure)、2.氮化镓铝闸极(al(x)gan gate)加强型(e-mode)高速电子迁移率晶体管结构(hemt structure),但正如两者组件的命名方式就可知只有闸极(gate)的区域会保留p型氮化镓(p-gan)或氮化镓铝(al(x)gan)。

4.最常见的制程方式就是在传统的空乏型(d-mode)氮化镓铝/氮化镓高速电子迁移率晶体管(algan/gan hemt)磊晶结构上额外成长一层p型氮化镓(p-gan)层,的后再将闸极(gate)区域以外的p型氮化镓(p-gan)以干式蚀刻的方式蚀刻掉,并尽量保持下一层氮化镓铝(algan)磊晶层厚度的完整性,因为当下一层氮化镓铝(algan)磊晶层被蚀刻掉太多的话会连带造成镓解理面(ga-face)p型氮化镓闸极(p-gan gate)加强型高速电子迁移率晶体管(e-mode hemt structure)结构的氮化镓铝/氮化镓(algan/gan)接口的二维电子气(2-deg)无法形成。因此,以干式蚀刻的方式其实难度很高因为:1.蚀刻深度难掌控、2.磊芯片上每一个磊晶层的厚度还是会有不均匀的;此外,此磊晶结构与一般空乏型(d-mode)氮化镓铝/氮化镓高速电子迁移率晶体管(algan/gan hemt)磊晶结构皆有电流崩塌效应(current collapse)的问题必须去解决,例如:缓冲层的缺陷(buffer traps)及表面缺陷(surface traps)。

5.有鉴于此,本发明针对上述的缺失,提出一种崭新的iii族/氮化物磊晶结构与以及利用该磊晶结构的后所形成的主动元件与其积体化的制作方法。

技术实现要素:

6.本发明的主要目的在于提供一种崭新的iii族/氮化物磊晶结构与利用该磊晶结构所形成的主动元件与其积体化的制作方法,以解决磊晶结构在高速电子迁移率晶体管所遇到的制程瓶颈,并且本发明的iii族/氮化物磊晶结构在制程后可一次性形成数种能够在

高电压高速操作的主动元件。

7.本发明的另一目的在于藉由一氟离子结构使氮化镓通道层(i-gan channel)的二维电子气(2-deg)在氟离子结构呈现空乏状态,藉此制作出氮化镓加强型氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管、混合型萧特基位障二极管或混合型组件。

8.为达上述目的,本发明提出一种的氮化镓铝/氮化镓(algan/gan)磊晶结构,其包含有一基底;一位于基底上的氮化镓高阻值层(碳掺杂)(i-gan(c-doped));一位于氮化镓高阻值层(碳掺杂)(i-gan(c-doped))上的氮化镓铝缓冲层(i-algan buffer layer);一位于氮化镓铝缓冲层(i-algan buffer layer)上的氮化镓通道层(i-gan channel);一位于氮化镓通道层(i-gan channel)上的氮化镓铝阻障层(i-algan barrier layer);一位于氮化镓铝阻障层(i-algan barrier layer)内的氟离子结构;以及一位于氟离子结构上的第一闸极绝缘介电层。

9.本发明更提出数种使用该氮化镓铝/氮化镓(algan/gan)磊晶结构所制得的具有氟离子结构的高速电子迁移率晶体管及萧特基位障二极管组件,与其积体化的制作方法。

附图说明

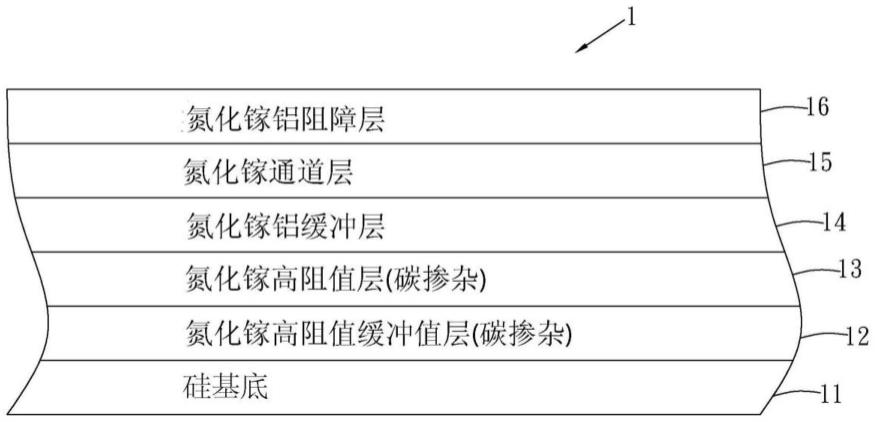

10.图1a,其为本发明所设计的氮化镓铝/氮化镓高速电子迁移率晶体管(algan/gan hemt)磊晶结构的第一结构图;

11.图1b,其为本发明所设计的氮化镓铝/氮化镓高速电子迁移率晶体管(algan/gan hemt)磊晶结构的第二结构图;

12.图2a,其为本发明的氮化镓铝/氮化镓(algan/gan)萧特基位障二极管的第一结构图;

13.图2b,其为本发明的氮化镓铝/氮化镓(algan/gan)萧特基位障二极管的第二结构图;

14.图2c,其为本发明的氮化镓铝/氮化镓(algan/gan)萧特基位障二极管的俯视图;

15.图3a,其为本发明的氟离子注入加强型氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管的第一结构示意图;

16.图3b,其为本发明的氟离子注入加强型氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管的第二结构示意图;

17.图3c,其为本发明的氟离子注入加强型氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管的俯视图;

18.图4a,其为本发明的氮化镓铝/氮化镓(algan/gan)磊晶结构上形成源极欧姆接触电极及汲极欧姆接触电极的示意图;

19.图4b-1,其为本发明的组件隔离制程的第一实施例的示意图;

20.图4b-2,其为本发明的组件隔离制程的第二实施例的示意图;

21.图4c-1,其为图4b-1结构上形成氟离子结构的示意图;

22.图4c-2,其为图4b-2结构上形成氟离子结构的示意图;

23.图4d-1,其为图4c-1结构上形成第一闸极绝缘介电层的示意图;

24.图4d-2,其为图4c-2结构上形成第一闸极绝缘介电层的示意图;

25.图4e-1,其为图4d-1结构上形成第一闸极电极金属、源极连接金属与汲极连接金

属的示意图;

26.图4e-2,其为图4d-2结构上形成第一闸极电极金属、源极连接金属与汲极连接金属的示意图;

27.图5a,其为本发明的氟离子注入加强型氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管串接空乏型不具有闸极绝缘介电层氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管的混合型加强型氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管的第一结构图;

28.图5b,其为本发明的氟离子注入加强型氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管串接空乏型不具有闸极绝缘介电层氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管的混合型加强型氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管的第二结构图;

29.图5c,其为本发明的氟离子注入加强型氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管串接空乏型不具有闸极绝缘介电层氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管的混合型加强型氮化镓铝/氮化镓(algan/gan)高电子迁移率晶体管的俯视图;

30.图5d:其系为本发明第二实施例之等效电路图;

31.图6a,其为本发明的氮化镓铝/氮化镓(algan/gan)磊晶结构上形成源极欧姆接触电极及汲极欧姆接触电极的示意图;

32.图6b-1,其为本发明的组件隔离制程的第一实施例的示意图;

33.图6b-2,其为本发明的组件隔离制程的第二实施例的示意图;

34.图6c-1,其为本发明的图6b-1的结构形成氟离子结构的示意图;

35.图6c-2,其为本发明的图6b-2的结构形成氟离子结构的示意图;

36.图6d-1,其为本发明的图6c-1的结构形成闸极氧化层的示意图;

37.图6d-2,其为本发明的图6c-2的结构形成闸极氧化层的示意图;

38.图6e-1,其为本发明的图6d-1的结构形成闸极电极金属与连接金属的示意图;

39.图6e-2,其为本发明的图6d-2的结构形成闸极电极金属与连接金属的示意图;

40.图7a,其为本发明的氟离子注入加强型氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管串接空乏型具有闸极绝缘介电层氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管的混合型加强型氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管的第一结构图;

41.图7b,其为本发明的加氟离子注入强型氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管串接空乏型具有闸极绝缘介电层氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管的混合型加强型氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管的第二结构图;

42.图7c,其为本发明的氟离子注入加强型氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管串接空乏型具有闸极绝缘介电层氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管的混合型加强型氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管的俯视图;

43.图7d:其系为第三实施例之等效电路图;

44.图8a,其为本发明的氮化镓铝/氮化镓(algan/gan)磊晶结构上形成源极欧姆接触电极及汲极欧姆接触电极的示意图;

45.图8a-1,其为本发明的组件隔离制程的第一实施例的示意图;

46.图8a-2,其为本发明的组件隔离制程的第二实施例的示意图;

47.图8b-1,其为本发明的图8a-1的结构形成氟离子结构与闸极氧化层的示意图;

48.图8b-2,其为本发明的图8a-2的结构形成氟离子结构与闸极氧化层的示意图;

49.图8c-1,其为本发明的图8b-1的结构形成闸极电极金属与连接金属的示意图;

50.图8c-2,其为本发明的图8b-2的结构形成闸极电极金属与连接金属的示意图;

51.图9a-1,其为本发明的氟离子注入加强型氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管串接一氮化镓铝/氮化镓(algan/gan)萧特基位障二极管(萧特基位障二极管)的混合型萧特基位障二极管的第一结构图;

52.图9a-2,其为本发明的氟离子注入加强型氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管串接氮化镓铝/氮化镓(algan/gan)萧特基位障二极管(萧特基位障二极管)的混合型萧特基位障二极管的第二结构图;

53.图9b,其为本发明的氟离子注入加强型氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管串接氮化镓铝/氮化镓(algan/gan)萧特基位障二极管(萧特基位障二极管)的混合型萧特基位障二极管的俯视图。

54.图9c,其为本发明的氟离子注入加强型氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管串接氮化镓铝/氮化镓(algan/gan)萧特基位障二极管(萧特基位障二极管)的混合型萧特基位障二极管的等效电路示意图。

55.图10a-1,其为本发明的空乏型氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管串接氮化镓铝/氮化镓(algan/gan)萧特基位障二极管(萧特基位障二极管)的混合型萧特基位障二极管的第一结构图;

56.图10a-2,其为本发明的空乏型氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管串接氮化镓铝/氮化镓(algan/gan)萧特基位障二极管(萧特基位障二极管)的混合型萧特基位障二极管的第二结构图;

57.图10b,其为本发明的空乏型氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管串接氮化镓铝/氮化镓(algan/gan)萧特基位障二极管(萧特基位障二极管)的混合型萧特基位障二极管的效电路示意图。

58.【图号对照说明】

59.1 磊晶结构

60.11 硅基底

61.12 氮化镓高阻值缓冲值层(碳掺杂)

62.13 氮化镓高阻值层(碳掺杂)

63.14 氮化镓铝缓冲层

64.15 氮化镓通道层

65.150 二维电子气

66.16 氮化镓铝阻障层

67.160 氟离子结构

68.2 磊晶结构

69.21 氮化镓铝缓冲层(铝含量渐进式变化至与第14层相同)

70.30 第一源极电极金属

71.31 第一汲极电极金属

72.32 第二源极电极金属

73.33 第二汲极电极金属

74.34 阴极电极金属

75.40 离子布植

76.41 离子布植

77.42 干式蚀刻

78.43 干式蚀刻

79.44 离子布植

80.45 离子布植

81.46 干式蚀刻

82.47 干式蚀刻

83.50 第一闸极绝缘介电层

84.51 侧向电容

85.52 侧向电容

86.53 第二闸极绝缘介电层

87.60 第一闸极电极金属

88.601 闸极电极连接金属

89.61 第一源极电极连接金属

90.62 第一汲极电极连接金属

91.63 第二闸极电极金属

92.64 第二源极电极连接金属

93.65 第二汲极电极连接金属

94.66 阴极电极连接金属

95.67 第一闸极电极连接金属

96.68 第一阳极电极

97.681 第一阳极电极(68)连接金属

98.682 第一阳极电极打线区域

99.70 绝缘保护介电层

100.80 第一闸极电极打线区域

101.81 阴极电极打线区域

102.82 源极电极打线区域

103.83 汲极电极打线区域

104.90 阳极(含阳极电极金属)

105.901 阳极电极金属

106.91 阴极

107.92 阳极场板绝缘介电层

108.93 阴极金属

109.aa

’ꢀ

剖面线

110.d 汲极

111.g 闸极

112.l1 左侧区域

113.r1 右侧区域

114.s 源极

具体实施方式

115.为了使本发明的结构特征及所达成的功效有更进一步的了解与认识,特用较佳的实施例及配合详细的说明,说明如下:

116.如图1a所示,其为本发明所设计的氮化镓铝/氮化镓高速电子迁移率晶体管(algan/gan hemt)磊晶结构1的第一结构图。此磊晶结构1依序包含有一硅基底(silicon substrate)11、一氮化镓高阻值缓冲层(碳掺杂)(buffer layer(c-doped))12,一氮化镓高阻值层(碳掺杂)(igan layer(c-doped))13,一氮化镓铝缓冲层(i-algan buffer layer)14,一氮化镓通道层(igan channel layer)15,以及一氮化镓铝阻障层(i-algan barrier layer)16,其中氮化镓铝缓冲层(i-algan buffer layer)14主要的功用是阻挡缓冲层缺陷(buffer trap)的电子进入氮化镓通道层(igan channel layer 15)进而降低组件电流崩塌(current collapse)的现象。如下图1b所示,为本发明所设计的氮化镓铝/氮化镓高速电子迁移率晶体管(algan/gan hemt)磊晶结构2的第二结构图,主要是考虑氮化镓铝缓冲层(i-algan buffer layer)14直接成长在氮化镓高阻值层(碳掺杂)(i-gan layer(c-doped)13会有过大的晶格不匹配问题,因此加入铝氮镓缓冲层(铝含量渐进式变化至与第14层相同)(i-algan grading buffer layer)21。

117.请参阅图2a,其为本发明的氟离子注入氮化镓铝/氮化镓(algan/gan)萧特基位障二极管的第一结构图。如图所示,本发明利用氟离子(f-)植入以“氟离子结构160”成长在图1a(或图1b)的氮化镓铝/氮化镓(algan/gan)磊晶结构1。由于有成长氟离子结构160的区域,其下方的二维电子气(2-deg)150会被空乏掉,因此氮化镓铝/氮化镓(algan/gan)萧特基位障二极管可以利用被空乏掉的二维电子气(2-deg)来减低在电路应用上当成受逆向偏压时所产生的逆向漏电流,并且同时增加逆向崩溃电压。请参阅图2b,其为本发明的氟离子注入氮化镓铝/氮化镓(algan/gan)萧特基位障二极管的第二结构图。图2b与图2a差异在于2a图为利用多重能量破坏性离子布植(ion-implant)40、41方式完成萧特基位障二极管(sbd)的组件隔离(device isolation),图2b为利用干式蚀刻(dry etching)42、43的方式,蚀刻氮化镓铝/氮化镓(algan/gan)磊晶结构1的氮化镓铝阻障层(i-algan barrier layer)16、氮化镓通道层(i-gan channel)15及氮化镓铝缓冲层(i-algan buffer layer)14以及部分的氮化镓高阻值缓冲层(碳掺杂)(i-gan(c-doped)层13来完成萧特基位障二极管(sbd)的组件隔离(device isolation)。

118.请参阅图2c,其为本发明的氟离子注入氮化镓铝/氮化镓(algan/gan)萧特基位障二极管的俯视图。如图所示,图2c仅绘出第一闸极电极金属(于萧特基位障二极管可以称为阳极电极金属)68上方的绝缘保护介电层70。再者,以俯视图来看,制作萧特基位障二极管时会同时制作第一阳极电极(68)连接金属681(具有第一阳极电极打线区域682)、阴极电极

连接金属66具有阴极电极打线区域81)。

119.第1a及1b图的结构更可以用于制作实施例一:氟离子注入加强型氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管。

120.如图3a所示,其为本发明的氟离子注入氮化镓铝阻障层(i-algan barrier layer)16内,形成氟离子注入加强型氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管第一结构示意图。如图所示,本发明的加强型氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管的特征在于包含有本发明所设计的氮化镓铝/氮化镓(algan/gan)磊晶结构1(或2);以及一氟离子结构160,其位于氮化镓铝阻障层(i-algan barrier layer)16内,其中二维电子气(2-deg)150虽形成在氮化镓铝阻障层(i-algan barrier layer)16/氮化镓通道层(igan channel layer)15接面的氮化镓通道层(igan channel layer)15内,但因为氟离子结构160的存在,使得位于氮化镓通道层(igan channel layer)15内的二维电子气(2-deg)150位于氟离子结构160下方处将是呈现空乏状态。

121.本发明的加强型氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管的结构,于氮化镓铝/氮化镓(algan/gan)磊晶结构1上形成有一第一源极欧姆接触电极(即第一源极电极金属)30与一第一汲极欧姆接触电极(即第一汲极电极金属)31,且分设于氮化镓铝/氮化镓(algan/gan)磊晶结构1的氮化镓铝阻障层(i-algan barrier layer)16的表面,的后经由氟离子注入后形成氟离子结构160,在来就是在氟离子结构160上形成一第一闸极绝缘介电层50,并且位于其上形成一第一闸极金属60,并且同步形成与第一源极欧姆接触电极30及第一汲极欧姆接触电极31连接的源极电极连接金属61、汲极电极连接金属62与门极电极连接金属601等,其中图号61、62、601皆属于与图号60的相同金属层,但为了方便示意则以不同图号61、62、601表示各电极的连接金属,的后则是在整个磊芯片表面附盖一层绝缘保护介电层70,最后则是在绝缘保护介电层70上蚀刻出源极、汲极与门极的打线区域以及磊芯片上组件与组件之间的切割道。另外图3b同样是本发明的氟离子注入加强型氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管的第二结构示意图,其与图3a的差异同样是在利用多重能量破坏性离子布植(ion-implant)40、41方式或是利用干式蚀刻(dry etching)42、43方式的差异。

122.参阅图3c,其为本发明的氟离子注入加强型氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管的俯视图。如图所示,图3c与图2c差异在于一个为高速电子迁移率晶体管而另一个为萧特基位障二极管,所以,图3c具有第一闸极电极打线区域80、一源极电极打线区域82与一汲极电极打线区域83,而图2c的第一闸极电极打线区域80与阴极打线区域81。再者,图3c同样可以看到氮化镓铝阻障层(i-algan barrier layer)16、第一源极电极金属30、第一汲极电极金属31、一第一闸极绝缘介电层50、第一闸极电极金属60、第一源极电极连接金属61与第一汲极电极连接金属62的位置。

123.以下是此实施例一的制作方法,但并不因此拘限本实施例仅可以此方式制作,而其金属线路布局方式也是如此。

124.请参阅图4a,其为本发明的氮化镓铝/氮化镓(algan/gan)磊晶结构上形成源极欧姆接触电极及汲极欧姆接触电极的示意图。步骤s11:形成源极欧姆接触电极30以及汲极欧姆接触电极31。此步骤利用金属蒸镀的方式,于氮化镓铝/氮化镓(algan/gan)磊晶结构1上镀上金属层,例如一般为钛/铝/钛/金(ti/al/ti/au)或钛/铝/镍/金(ti/al/ni/au)所组成

的金属层,再利用金属掀离的方式将所镀上的金属层图案化为所设定的图形,以形成位于磊芯片(氮化镓铝/氮化镓(algan/gan)磊晶结构1)上的第一源极电极金属30以及第一汲极电极金属31,的后再经过700~900℃,30秒的热处理,使得第一源极电极金属30以及第一汲极电极金属31成为欧姆接触电极。

125.请参阅图4b-1,其为本发明的组件隔离制程的第一实施例的示意图。步骤s12:组件隔离制程。此步骤利用多重能量破坏性离子布植(ion-implant)40、41,一般使用硼或氧(boron或oxygen)等重原子,使得组件与组件隔离,或者如图4b-2,其为本发明的组件隔离制程的第二实施例的示意图。采用干式蚀刻(dry etching)42、43,蚀刻氮化镓铝/氮化镓(algan/gan)磊晶结构1的氮化镓铝阻障层(i-algan barrier layer)16、氮化镓通道层(i-gan channel)15及氮化镓铝缓冲层(i-algan buffer layer)14而至高阻值的氮化镓高阻值层(碳掺杂)(igan layer(c-doped))13,使得组件与组件隔离。

126.请参阅图4c-1,其为图4b-1结构上形成氟离子结构的示意图。步骤s13:氟离子植入制程。此步骤以f-植入在欲形成第一闸极电极金属60(如图4e-1所示)的位置的下方氮化镓铝阻障层(i-algan barrier layer)16内使其下方区域氮化镓通道层(igan channel layer)15无法形成二维电子气(2-deg)150,的后再经过425℃、600秒的热处理的后,氟离子结构160会稳定的占据氮化镓铝阻障层(i-algan barrier layer)16内的空间。

127.再者,氟离子植入制程更包含,利用黄光曝光显影定义氮化镓铝阻障层(i-algan barrier layer)16的氟离子注入的区域,利用cf4在干式蚀刻系统或离子布植机系统内产生氟离子电浆,在特定电场(或特定电压)下将氟离子(f-)注入氮化镓铝阻障层(i-algan barrier layer)16内后,再经过425℃、600秒的热处理,使氟离子结构160稳定的占据氮化镓铝阻障层(i-algan barrier layer)16内的空间。此外,图4c-2,其为图4b-2结构上形成氟离子结构的示意图,其与图4c-1相同,所以不再覆述。

128.请参阅图4d-1,其为图4c-1结构上形成第一闸极绝缘介电层的示意图。步骤14:闸极绝缘介电层制程。此步骤利用电浆辅助化学气相沉积(pecvd)沉积一层绝缘介电层,其材质可以为氧化硅、氮氧化硅(siox、sioxny)或氮化硅(sinx),用来作为第一闸极绝缘介电层50,厚度=10~100nm,接下来利用光阻(photo resist)以曝光显影的方式定义出第一闸极绝缘介电层50的区域;最后再使用氧化物缓冲蚀刻液(boe(buffered oxide etchant))利用湿式蚀刻的方式将第一闸极绝缘介电层50的区域以外的绝缘介电层蚀刻掉,只保留欲形成第一闸极绝缘介电层50的区域,的后再将光阻以去光阻液蚀刻掉。此外,图4d-2,其为图4c-2结构上形成第一闸极绝缘介电层的示意图,其与图4d-1相同,所以不再覆述。

129.请参阅图4e-1,其为图4d-1结构上形成第一闸极电极金属、源极连接金属与汲极连接金属的示意图。步骤s15:金属线路布局制程。此步骤包含有进行金属镀膜,利用金属蒸镀结合金属掀离方式将材质为/镍/金(ni/au)的金属层图案化形成一第一闸极电极金属60、闸极电极连接金属601(包含形成图3c的第一闸极电极打线区域(bonding pad)80)、源极电极连接金属(包含源极电极打线区域(bonding pad)82)61与汲极电极连接(interconnection)金属62(包含汲极电极打线区域(bonding pad)83)。而在金属线路布局上,举例来说,位于氟离子结构160及第一闸极绝缘介电层50上的第一闸极电极金属60与第一闸极电极打线区域80连接。此外,图4e-2,其为图4d-2结构上形成第一闸极电极金属、源极连接金属与汲极连接金属的示意图,其与图4e-1相同,所以不再覆述。

130.接着步骤s16:介电层的沉积与图案化。此步骤是利用电浆辅助化学气相沉积(pecvd)成长一层绝缘保护介电层70,其材质可以为氧化硅、氮氧化硅(siox、sioxny)或氮化硅(sinx)。最后再对绝缘保护介电层70进行图案化,以显露出各打线区域82、83(亦显露出图3c的第一闸极电极打线区域80),举例来说以氧化物缓冲蚀刻液(boe(buffered oxide etchant))以湿式蚀刻(wet etching)的方式将打线的区域(bonding pad region)蚀刻出来成为的后打线的区域。此步骤完成后,就形成如第3a、3b图的具有氟离子注入加强型氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管。

131.此外,第4e-1、4e-2图的虚线圈围处的地方会形成一个具有侧向的电容,此侧向电容51、52会形成场板效应(field plate effect),其主要功能是利用此侧向电容51、52的电场将第一闸极电极金属60下方高密度的电场均匀分散开来,其用处除了高速电子迁移率晶体管的汲极至源极的崩溃电压(vds),也可以抑制第一闸极电极金属60下方的电子捕捉效应(electron trapping effect)进而降低高速电子迁移率晶体管(hemt)在工作时的电流崩塌效应(current collapse)。

132.实施例二:如图5a、5b,为本发明的氟离子注入加强型氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管串接空乏型不具有闸极绝缘介电层氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管所形成的氟离子注入混合型加强型氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管的第一结构图与第二结构图。如图5a、5b所示,以氟离子(f-)植入在第一闸极电极金属60下方氮化镓铝阻障层(i-algan barrier layer)16内形成加强型氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管串接一个空乏型不具有闸极绝缘介电层(gate dielectric)氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管而成的“氟离子注入混合型加强型氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管”。

133.本发明的氟离子注入混合型加强型氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管可以解决一般氮化镓铝/氮化镓加强型高速电子迁移率晶体管(algan/gan e-mode hemt)常会出现的问题,也就是组件操作在饱和区时(闸极电压(vg)固定),导通电流(ids)会随着汲源极电压(vds)提升而增加的现象,其主要原因是来自于空乏区没有截止(pinch-off)掉整个信道(氮化镓信道层(igan channel layer)15),因此藉由串接(cascode)一个空乏型高速电子迁移率晶体管(d-mode hemt),而利用空乏型高速电子迁移率晶体管(d-mode hemt)的饱和电流来限制加强型高速电子迁移率晶体管(e-mode hemt)的饱和电流正好可以解决此问题。

134.如图5a、5b所示,实施例二的氟离子注入混合型加强型氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管包含有本发明所设计的氮化镓铝/氮化镓(algan/gan)磊晶结构在后的组件结构图,其区分为一左侧区域l1与一右侧区域r1。左侧区域l1形成有一氮化镓加强型氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管,此氮化镓加强型氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管包含有一氟离子结构160,其中二维电子气(2-deg)150虽形成在氮化镓铝阻障层(i-algan barrier layer)16/氮化镓通道层(igan channel layer)15接面的氮化镓通道层(igan channel layer)15内,但因为氟离子结构160的存在,使得氮化镓通道层(igan channel layer)15内的二维电子气(2-deg)150位于氟离子结构160下方处将是呈现空乏状态。右侧区域r1形成有一空乏型不具有闸极绝缘介电层氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管。

135.请参阅图5c,其为本发明的氟离子注入加强型氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管串接空乏型不具有闸极绝缘介电层的氟离子注入混合型加强型氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管的俯视图。如图所示,氟离子注入加强型氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管的第一源极电极金属30上形成源极电极连接金属61,且第一源极电极金属30透过源极电极连接金属61与空乏型不具有闸极绝缘介电层氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管的第二闸极电极金属63连接,另外第一汲极电极连接金属与第二源极电极连接金属是电性相连接的。于混合型加强型氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管中,图5c中的s为其一源极、g为其一闸极及d为其一汲极。

136.此实施例的制程方式,首先,如图6a,其为本发明的氮化镓铝/氮化镓(algan/gan)磊晶结构上形成源极欧姆接触电极及汲极欧姆接触电极的示意图。提供一本发明的氮化镓铝/氮化镓(algan/gan)磊晶结构,并将左侧区域l1设定为制作氟离子注入加强型氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管,将右侧区域r1设定为是制作空乏型不具有闸极绝缘介电层氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管。当然左右两侧区域l1、r1的设定可依需求变更,这是无庸置疑的。

137.接续,如同先前所述的步骤11的制作方法,于本发明的氮化镓铝/氮化镓(algan/gan)磊晶结构上利用金属蒸镀的方式结合金属掀离的方式形成第一源极电极金属30、第一汲极电极金属31、第二源极电极金属32及第二汲极电极金属33,的后再经过700~900℃,历时约30秒的热处理使得第一源极电极金属30、第一汲极电极金属31、第二源极电极金属32及第二汲极电极金属33成为第一源极欧姆接触电极30、第一汲极欧姆接触电极31、第二源极欧姆接触电极32及第二汲极欧姆接触电极33。

138.请参阅图6b-1,其为本发明的组件隔离制程的第一实施例的示意图。利用如图6b-1所示的破坏性离子布植40、41、44、45或者如图6b-2所示的干式蚀刻氮化镓铝/氮化镓(algan/gan)磊晶结构42、43、46、47至高阻值的氮化镓高阻值层(碳掺杂)(igan layer(c-doped))13,来施行组件(左侧区域l1的晶体管)与组件(右侧区域r1的晶体管)间的隔离制程。再者,图6b-2为本发明的组件隔离制程的第二实施例的示意图,其与图6b-1相似于此不再覆述。

139.请参阅图6c-1,其为本发明的图6b-1的结构形成氟离子结构的示意图。如图所示,利用f-植入在欲形成第一闸极金属60的位置的下方氮化镓铝阻障层(i-algan barrier layer)16内使其下方区域氮化镓通道层(igan channel layer)15无法形成二维电子气(2-deg)150,之后再经过425℃、600秒的热处理之后,氟离子结构会稳定的占据氮化镓铝层(ialgan layer)内的空间。图6c-2为本发明的图6b-2的结构形成氟离子结构的示意图,其与图6c-1相似于此不再覆述。

140.请参阅图6d-1,其为本发明的图6c-1的结构形成闸极绝缘介电层50的示意图。如图所示,利用电浆辅助化学气相沉积(pecvd)沉积一层绝缘介电层,其材质可以为氧化硅、氮氧化硅(siox、sioxny)或氮化硅(sinx),用来作为第一闸极绝缘介电层50,厚度=10~100nm,接下来利用光阻(photo resist)以曝光显影的方式定义出第一闸极绝缘介电层的区域;最后再使用氧化物缓冲蚀刻液(boe(buffered oxide etchant))利用湿式蚀刻的方式将第一闸极绝缘介电层50的区域以外的绝缘介电层蚀刻掉,只保留欲形成第一闸极绝缘

介电层50的区域,的后再将光阻以去光阻液蚀刻掉。图6d-2为本发明的图6c-2的结构形成闸极绝缘介电层50的示意图,其与图6c-1相似于此不再覆述。

141.请参阅图6e-1,其为本发明的图6d-1的结构形成闸极电极金属与连接金属的示意图。如图所示,利用金属蒸镀结合金属掀离的方式形成第一闸极电极金属60、第一源极电极连接金属(具有如图5c所示具有源极电极打线区域82)61及第一汲极电极连接金属62、第二闸极电极金属63、第二源极电极连接金属64及第二汲极电极连接金属(具有如图5c所示具有汲极电极打线区域83)65。当然也可于此步骤同时形成与第一闸极电极金属层60电性连接的第一闸极电极连接金属67(具有如图5c所示具有第一闸极电极打线区域80),另外第一闸极电极金属60、第一源极电极连接金属61、第一汲极电极连接金属62、第二闸极电极金属63、第二源极电极连接金属64及第二汲极电极连接金属65皆是一次性金属镀膜完成,其中第一源极电极连接金属61与第二闸极电极金属63是电性相连接的,而第一汲极电极连接金属62与第二源极电极连接金属64是电性相连接的。图6e-2为本发明的图6d-2的结构形成闸极电极金属与连接金属的示意图,其与图6e-1相似于此不再覆述。

142.同样接着利用电浆辅助化学气相沉积(pecvd)沉积一层绝缘保护介电层(passivation dielectric)70,最后再对绝缘保护介电层70进行图案化,以显露出图5c的各打线区域80、82、83而完成图5a、5b的结构。

143.如图5a所示,同样的,虚线圈起来的地方会形成一个具有侧向的电容,此侧向电容51、52会形成场板效应(field plate effect),其主要功能是利用此侧向电容51、52的电场将第一闸极电极金属60下方高密度的电场均匀分散开来,其用处除了增加高速电子迁移率晶体管汲极至源极的崩溃电压(vds),也可以抑制第一闸极电极金属60下方的电子捕捉效应(electron trapping effect)进而降低高速电子迁移率晶体管在工作时的电流崩塌效应(current collapse)。

144.请参阅图7a、7b,其为本发明的氟离子注入加强型氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管串接空乏型具有闸极绝缘介电层(50)氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管的混合型加强型氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管的第一结构图与第二结构图。如图所示,本发明的实施例三:以f-植入在第一闸极电极金属60下方氮化镓铝阻障层(i-algan barrier layer)16内形成加强型氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管串接一个空乏型具有闸极绝缘介电层50(gate dielectric)氮化镓铝层(algan/gan)高速电子迁移率晶体管而成的“氟离子注入混合型加强型氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管”的积体化制作方式。

145.如图7a、7b所示,实施例三的氟离子注入混合型加强型氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管包含有本发明所设计的氮化镓铝/氮化镓(algan/gan)磊晶结构,其区分为左侧区域l1与右侧区域r1。左侧区域l1形成有一氟离子注入加强型氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管,此氟离子注入加强型氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管包含有一氟离子结构160,其中二维电子气(2-deg)150虽形成在氮化镓铝阻障层(i-algan barrier layer)16/氮化镓通道层(igan channel layer)15接面的氮化镓通道层(igan channel layer)15内,但因为氟离子结构160的存在,使得氮化镓通道层(igan channel layer)15内的二维电子气(2-deg)150位于氟离子结构160下方处将是呈现空乏状态。右侧区域r1形成有一空乏型具有闸极绝缘介电层氮化镓铝/

氮化镓(algan/gan)高速电子迁移率晶体管,其具有一第二闸极绝缘介电层53。

146.请参阅图7c,其为本发明的氟离子注入加强型氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管串接空乏型具有闸极绝缘介电层氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管的氟离子注入混合型加强型氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管的俯视图。如图所示,空乏型具有闸极绝缘介电层氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管具有第二闸极绝缘介电层53,其余与图5c相似,不再覆述。

147.请参阅图8a,其为本发明的氮化镓铝/氮化镓(algan/gan)磊晶结构上形成源极欧姆接触电极及汲极欧姆接触电极的示意图。如图所示,提供一本发明的氮化镓铝/氮化镓(algan/gan)磊晶结构,并将左侧区域l1设定为制作氟离子注入加强型氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管,将右侧区域r1设定为是制作空乏型具有闸极绝缘介电层氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管。当然左右两侧区域l1、r1的设定可依需求变更,这是无庸置疑的。

148.请参阅图8a-1,其为本发明的组件隔离制程的第一实施例的示意图。此实施例的制程方式,首先,如实施例二的步骤,提供一本发明的氮化镓铝/氮化镓(algan/gan)磊晶结构,并将左侧区域l1设定为制作氟离子注入加强型氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管,将右侧区域r1设定为是制作空乏型具有闸极绝缘介电层氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管。接续,如同先前所述的制作方法,于本发明的氮化镓铝/氮化镓(algan/gan)磊晶结构上形成第一源极电极金属30、第一汲极电极金属31、第二源极电极金属32及第二汲极电极金属33,然后施行组件与组件间的隔离制程。再者,图8a-2,其为本发明的组件隔离制程的第二实施例的示意图,其与图8a-1相似,不再覆述。

149.请参阅图8b-1,其为本发明的图8a-1的结构形成氟离子结构与闸极绝缘介电层的示意图。随后,进行左侧区域l1加强型高速电子迁移率晶体管(e-mode hemt)的第一闸极绝缘介电层50及右侧区域空乏型高速电子迁移率晶体管(d-mode hemt)的第二闸极绝缘介电层53制作,其步骤包含有:利用电浆辅助化学气相沉积(pecvd)沉积一层绝缘介电层,其材质可以为氧化硅、氮氧化硅(siox、sioxny)或氮化硅(sinx),厚度为10~100nm,接下来利用光阻(photo resist)以曝光显影的方式定义出加强型高速电子迁移率晶体管(e-mode hemt)第一闸极绝缘介电层50的区域及空乏型高速电子迁移率晶体管(d-mode hemt)的第二闸极绝缘介电层53的区域,最后再使用氧化物缓冲蚀刻液(boe(buffered oxide etchant))利用湿式蚀刻的方式将第一闸极绝缘介电层50的区域及第二闸极绝缘介电层53的区域以外的绝缘介电层蚀刻掉,只保留加强型高速电子迁移率晶体管(e-mode hemt)第一闸极绝缘介电层50的区域及空乏型高速电子迁移率晶体管(d-mode hemt)的第二闸极绝缘介电层53的区域,的后再将光阻以去光阻液蚀刻掉。再者,图8b-2,其为本发明的图8a-2的结构形成氟离子结构与闸极绝缘介电层的示意图,其与图8b-1相似,不再覆述。

150.请参阅图8c-1,其为本发明的图8b-1的结构形成闸极电极金属与连接金属的示意图。如图所示,利用金属蒸镀(一般为镍/金(ni/au)) 金属掀离的方式形成第一闸极电极金属60、第一源极电极连接金属61、第一汲极电极连接金属62、第二闸极电极金属63、第二源极电极连接金属64及第二汲极电极连接金属65。此时,同样可一并形成组件运作所需的线路金属部分,例如与第一闸极电极金属60连接的第一闸极电极打线区域80。但不以本发明图式中的上视图作为权利范畴的局限。再者,第8c-2,其为本发明的图8b-2的结构形成闸极

电极金属与连接金属的示意图,其与图8c-1相似,不再覆述。

151.接着同样接着利用电浆辅助化学气相沉积(pecvd)沉积一层绝缘保护介电层(passivation dielectric)70,其材质可以选自于氧化硅、氮氧化硅(siox、sioxny)或氮化硅(sinx),最后再对绝缘保护介电层70进行图案化,以将各打线区域蚀刻显露出来,形成如第7a、7b图所示的结构。

152.同样得由于第一闸极电极金属60与第一闸极绝缘介电层50会形成侧向电容51、52,此侧向电容51、52会形成场板效应(field plate effect),利用此侧向电容51、52的电场将第一闸极电极金属60与第二闸极电极金属63下方高密度的电场均匀分散开来,其用处除了增加高速电子迁移率晶体管汲极至源极的崩溃电压(vds),也可以抑制第一闸极电极金属60与第二闸极电极金属63下方的电子捕捉效应(electron trapping effect)进而降低高速电子迁移率晶体管在工作时的电流崩塌效应(current collapse)。

153.请参阅图9a-1,其为本发明的氟离子注入加强型氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管串接一氮化镓铝/氮化镓(algan/gan)萧特基位障二极管(sbd)的氟离子注入混合型氮化镓铝/氮化镓(algan/gan)萧特基位障二极管的第一结构图。本发明的实施例四:一氟离子注入加强型氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管串接一氮化镓铝/氮化镓(algan/gan)萧特基位障二极管(sbd)而成的氟离子注入混合型萧特基位障二极管。其中萧特基位障二极管(sbd)的阳极(anode)90与第一闸极是藉由第一闸极电极金属(gate)60在电性上相连接的,其中第一闸极电极金属60、阳极电极金属901、阴极金属93及其之间的阴极电极连接金属66可以是同步完成。当氮化镓铝/氮化镓(algan/gan)萧特基位障二极管(sbd)的阳极(anode)90给予正电压时,除了萧特基位障二极管(sbd)会导通之外,阳极(anode)90同时也给予第一闸极电极金属(gate)60正电压,也因此氟离子注入加强型氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管是属于完全导通的状态,如此一来电流便可顺利的送到阴极(cathode)91。当阴极91(阴极金属93)给予正电压时,加强型氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管的闸极电压(vgs)是个“负值”,因此氟离子注入加强型氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管是呈现关闭状态,如此一来可以保护氮化镓铝/氮化镓萧特基位障二极管((algan/gan)sbd)不会在逆向电压崩溃。除此之外由于氟离子注入加强型氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管是“电流负温度系数的组件”而氮化镓铝/氮化镓萧特基位障二极管((algan/gan)sbd)是“电流正温度系数的组件”,因此两者互相串接的后有互补作用进而使得此“混合组件”在给予固定电压工作时,其电流不容易受到温度影响而改变。

154.此氟离子注入混合型氮化镓铝/氮化镓(algan/gan)萧特基位障二极管的特色在于第一闸极电极金属60下方如先前所述是无法存在二维电子气(2-deg)150的,除非给予正电压才能够使得二维电子气(2-deg)150恢复。也因此阴极91在承受逆电压时可以有效的提升反向崩溃电压并且抑制逆向漏电流。

155.如第9a-1、9a-2图所示,实施例四的氟离子注入混合型氮化镓铝/氮化镓(algan/gan)萧特基位障二极管主要包含有本发明所设计的氮化镓铝/氮化镓(algan/gan)磊晶结构,其区分为一左侧区域l1与一右侧区域r1。左侧区域l1形成有一氟离子注入加强型氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管,此氟离子注入加强型氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管包含有一氟离子结构160,其中二维电子气(2-deg)虽

形成在氮化镓铝阻障层(i-algan barrier layer)16/氮化镓通道层(igan channel layer)15接面的氮化镓通道层(igan channel layer)15内,但因为氟离子结构160的存在,使得氮化镓通道层(igan channel layer)15内的二维电子气(2-deg)150位于氟离子结构160下方处将是呈现空乏状态。右侧区域r1形成有一具有阳极场板(field plate)氮化镓铝/氮化镓(algan/gan)萧特基位障二极管。

156.实施例四的制程上与前述实施例在于,于本发明所设计的氮化镓铝/氮化镓(algan/gan)磊晶结构上施行氟离子植入制程后,于左侧区域l1形成第一源极欧姆接触电极30与第一汲极欧姆接触电极31,同步于右侧区域r1形成萧特基位障二极管(sbd)的阴极欧姆接触电极(阴极电极金属)34。再于右侧区域r1上形成一阳极场板绝缘介电层92,此时也在左侧区域l1形成第一闸极绝缘介电层50。

157.接续,如同先前所述,形成第一闸极电极金属60与各连接金属,例如:氟离子注入混合型氮化镓铝/氮化镓(algan/gan)萧特基位障二极管的第一闸极电极连接金属、第一源极电极连接金属及氮化镓铝/氮化镓萧特基位障二极管((algan/gan)sbd)的阳极电极连接金属,以及相关的线路布局金属导线部分,并于磊晶层(氮化镓铝/氮化镓(algan/gan)磊晶结构)上形成一层图案化绝缘保护介电层70,以显露出部分绝缘介电层,形成如图9b所示的俯视图。

158.图9b为本发明的氟离子注入加强型氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管串接一氮化镓铝/氮化镓(algan/gan)萧特基位障二极管(sbd)的氟离子注入混合型氮化镓铝/氮化镓(algan/gan)萧特基位障二极管的俯视图。如图所示,氟离子注入混合型氮化镓铝/氮化镓(algan/gan)萧特基位障二极管(sbd)的阳极电极与第一闸极电极金属60是以第一闸极电极金属60作为连接金属并且电性上相连接的(位于绝缘保护介电层70下)。再者,混合型氮化镓铝/氮化镓(algan/gan)萧特基位障二极管(sbd)的阳极电极连接金属具有阳极电极打线区域83,阴极电极金属93具有源极电极打线区域82。

159.如第10a-1、10a-2图所示,实施例四的混合型氮化镓铝/氮化镓(algan/gan)萧特基位障二极管主要包含有本发明所设计的氮化镓铝/氮化镓(algan/gan)磊晶结构,其区分为一左侧区域l1与一右侧区域r1。左侧区域l1形成有一空乏型氮化镓铝/氮化镓(algan/gan)高速电子迁移率晶体管。右侧区域r1形成有一具有阳极场板(field plate)氮化镓铝/氮化镓(algan/gan)萧特基位障二极管。

160.当阴极91给予正电压时,氮化镓铝/氮化镓(algan/gan)空乏型高速电子迁移率晶体管(d-mode hemt)的闸极电压(vgs)是个“负值”,因此氮化镓铝/氮化镓(algan/gan)空乏型高速电子迁移率晶体管(d-mode hemt)是呈现关闭状态,如此一来可以保护氮化镓铝/氮化镓萧特基位障二极管((algan/gan)sbd)不会在逆向电压崩溃。

161.上文仅为本发明的较佳实施例而已,并非用来限定本发明实施的范围,凡依本发明权利要求范围所述的形状、构造、特征及精神所为的均等变化与修饰,均应包括于本发明的权利要求范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。