1.本发明涉及数模转换器技术领域,特别指一种高精度数模转换方法、系统、设备及介质。

背景技术:

2.数模转换器,又称d/a转换器,简称dac,它是把数字量转变成模拟的器件。随着科技的进步,在电路设计时对输出精度的要求也越来越高,即对数模转换器的分辨率提出了更高的要求。

3.例如16位的数模转换器,其基准电压是2.5v,输出精度(分辨率)为0.15mv,若要将输出精度提升至0.1mv,传统上需要采用更高位数的数模转换器,例如采用32位的数模转换器来提升输出精度,但更高位数的数模转换器的价格不仅会昂贵很多,而且现货少购买周期长。

4.因此,如何提供一种高精度数模转换方法、系统、设备及介质,实现降低数模转换器高精度输出的成本,成为一个亟待解决的技术问题。

技术实现要素:

5.本发明要解决的技术问题,在于提供一种高精度数模转换方法、系统、设备及介质,实现降低数模转换器高精度输出的成本。

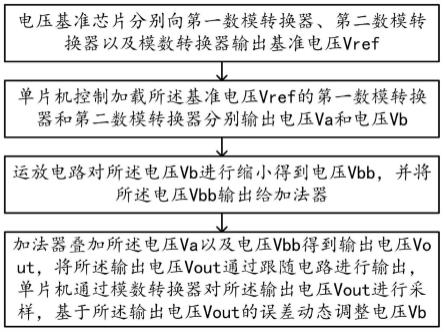

6.第一方面,本发明提供了一种高精度数模转换方法,包括如下步骤:

7.步骤s1、电压基准芯片分别向第一数模转换器、第二数模转换器以及模数转换器输出基准电压vref;

8.步骤s2、单片机控制加载所述基准电压vref的第一数模转换器和第二数模转换器分别输出电压va和电压vb;

9.步骤s3、运放电路对所述电压vb进行缩小得到电压vbb,并将所述电压vbb输出给加法器;

10.步骤s4、加法器叠加所述电压va以及电压vbb得到输出电压vout,将所述输出电压vout通过跟随电路进行输出,单片机通过模数转换器对所述输出电压vout进行采样,基于所述输出电压vout的误差动态调整电压vb。

11.进一步地,所述步骤s1中,所述第一数模转换器和第二数模转换器的位数均为n,所述模数转换器的位数为m,n和m均为正整数,且m大于n。

12.进一步地,所述步骤s3具体为:

13.运放电路对所述电压vb进行缩小2k倍得到电压vbb,并将所述电压vbb输出给加法器;k为正整数,且0<k≤n。

14.进一步地,所述步骤s4中,所述输出电压vout的输出精度dip的计算公式如下:

15.dip=vref/2

n k

。

16.第二方面,本发明提供了一种高精度数模转换系统,包括如下模块:

17.基准电压输出模块,用于电压基准芯片分别向第一数模转换器、第二数模转换器以及模数转换器输出基准电压vref;

18.数模转换模块,用于单片机控制加载所述基准电压vref的第一数模转换器和第二数模转换器分别输出电压va和电压vb;

19.缩放模块,用于运放电路对所述电压vb进行缩小得到电压vbb,并将所述电压vbb输出给加法器;

20.高精度输出模块,用于加法器叠加所述电压va以及电压vbb得到输出电压vout,将所述输出电压vout通过跟随电路进行输出,单片机通过模数转换器对所述输出电压vout进行采样,基于所述输出电压vout的误差动态调整电压vb。

21.进一步地,所述基准电压输出模块中,所述第一数模转换器和第二数模转换器的位数均为n,所述模数转换器的位数为m,n和m均为正整数,且m大于n。

22.进一步地,所述缩放模块具体为:

23.运放电路对所述电压vb进行缩小2k倍得到电压vbb,并将所述电压vbb输出给加法器;k为正整数,且0<k≤n。

24.进一步地,所述高精度输出模块中,所述输出电压vout的输出精度dip的计算公式如下:

25.dip=vref/2

n k

。

26.第三方面,本发明提供了一种高精度数模转换设备包括存储器、处理器及存储在存储器上并可在处理器上运行的计算机程序,所述处理器执行所述程序时实现第一方面所述的方法。

27.第四方面,本发明提供了一种高精度数模转换介质,其上存储有计算机程序,该程序被处理器执行时实现第一方面所述的方法。

28.本发明实施例中提供的一个或多个技术方案,至少具有如下技术效果或优点:

29.1、通过加法器将n位第一数模转换器输出的电压va和n位第二数模转换器输出的电压vb缩小2k倍得到的电压vbb进行叠加,得到输出电压vout,通过对电压vb缩小2k倍使输出电压vout的输出精度提升了k位,达到vref/2

n k

,即使用两个位数一致的数模转换器也可提升输出精度,无需像传统上采用更高位数的数模转换器,进而极大的降低了数模转换器高精度输出的成本,并能实现线性输出vout,即分辨率是线性的。

30.2、通过使用两个位数一致的数模转换器来提升输出精度,即可使用已经验证和熟悉的数模转换器,无需重新挑选更高位数的数模转换器并进行验证,极大的缩短了开发周期。

31.3、通过设置位数高于第一数模转换器和第二数模转换器的模数转换器对加法器的输出进行采样,当输出电压vout的误差不满足预设的精度时,动态调整第二数模转换器输出的电压vb,直至输出电压vout的误差满足预设的精度,进而保障了数模转换器的输出精度。

32.上述说明仅是本发明技术方案的概述,为了能够更清楚了解本发明的技术手段,而可依照说明书的内容予以实施,并且为了让本发明的上述和其它目的、特征和优点能够更明显易懂,以下特举本发明的具体实施方式。

附图说明

33.下面参照附图结合实施例对本发明作进一步的说明。

34.图1是本发明一种高精度数模转换方法的流程图。

35.图2是本发明一种高精度数模转换系统的结构示意图。

36.图3是本发明一种高精度数模转换设备的结构示意图。

37.图4是本发明一种高精度数模转换介质的结构示意图。

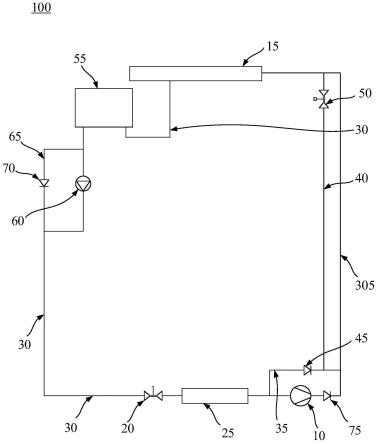

38.图5是本发明的硬件架构图。

具体实施方式

39.本技术实施例通过提供一种高精度数模转换方法、系统、设备及介质,实现降低数模转换器高精度输出的成本。

40.本技术实施例中的技术方案,总体思路如下:通过运放电路对第二数模转换器输出的电压vb缩小2k倍得到电压vbb,再利用加法器叠加电压vbb和第一数模转换器输出的电压va,以提升输出精度,无需采用更高位数的数模转换器,进而降低数模转换器高精度输出的成本。

41.实施例一

42.本实施例提供一种高精度数模转换方法,如图1、5所示,包括如下步骤:

43.步骤s1、电压基准芯片分别向第一数模转换器(dac)、第二数模转换器(dac)以及模数转换器(adc)输出基准电压vref;

44.步骤s2、单片机(mcu)控制加载所述基准电压vref的第一数模转换器和第二数模转换器分别输出电压va和电压vb;

45.步骤s3、运放电路对所述电压vb进行缩小得到电压vbb,并将所述电压vbb输出给加法器;即第一数模转换器负责mv级别的加载,第二数模转换器和运放电路负责uv级别的加载,以实现更小分辨率的输出;

46.步骤s4、加法器叠加所述电压va以及电压vbb得到输出电压vout,将所述输出电压vout通过跟随电路进行输出,单片机通过模数转换器对所述输出电压vout进行采样,基于所述输出电压vout的误差动态调整电压vb。

47.所述步骤s1中,所述第一数模转换器和第二数模转换器的位数均为n,所述模数转换器的位数为m,n和m均为正整数,且m大于n;例如选取型号为ltc1655的16位数模转换器,型号为ads1241的24位模数转换器。

48.所述步骤s3具体为:

49.运放电路对所述电压vb进行缩小2k倍得到电压vbb,并将所述电压vbb输出给加法器;k为正整数,且0<k≤n。

50.所述步骤s4中,所述输出电压vout的输出精度dip的计算公式如下:

51.dip=vref/2

n k

,即dip=(vref/2n)/2k,相对于单个数模转换器,输出精度提升了k位;

52.当vref=2500mv,n=16,k=10时,dip=(2.5v/2

16

)/2

10

=0.00003725mv。

53.实施例二

54.本实施例提供一种高精度数模转换系统,如图2、5所示,包括如下模块:

55.基准电压输出模块,用于电压基准芯片分别向第一数模转换器(dac)、第二数模转换器(dac)以及模数转换器(adc)输出基准电压vref;

56.数模转换模块,用于单片机(mcu)控制加载所述基准电压vref的第一数模转换器和第二数模转换器分别输出电压va和电压vb;

57.缩放模块,用于运放电路对所述电压vb进行缩小得到电压vbb,并将所述电压vbb输出给加法器;即第一数模转换器负责mv级别的加载,第二数模转换器和运放电路负责uv级别的加载,以实现更小分辨率的输出;

58.高精度输出模块,用于加法器叠加所述电压va以及电压vbb得到输出电压vout,将所述输出电压vout通过跟随电路进行输出,单片机通过模数转换器对所述输出电压vout进行采样,基于所述输出电压vout的误差动态调整电压vb。

59.所述基准电压输出模块中,所述第一数模转换器和第二数模转换器的位数均为n,所述模数转换器的位数为m,n和m均为正整数,且m大于n;例如选取型号为ltc1655的16位数模转换器,型号为ads1241的24位模数转换器。

60.所述缩放模块具体为:

61.运放电路对所述电压vb进行缩小2k倍得到电压vbb,并将所述电压vbb输出给加法器;k为正整数,且0<k≤n。

62.所述高精度输出模块中,所述输出电压vout的输出精度dip的计算公式如下:

63.dip=vref/2

n k

,即dip=(vref/2n)/2k,相对于单个数模转换器,输出精度提升了k位;

64.当vref=2500mv,n=16,k=10时,dip=(2.5v/2

16

)/2

10

=0.00003725mv。

65.基于同一发明构思,本技术提供了实施例一对应的电子设备实施例,详见实施例三。

66.实施例三

67.本实施例提供了一种高精度数模转换设备,如图3、5所示,包括存储器、处理器及存储在存储器上并可在处理器上运行的计算机程序,处理器执行计算机程序时,可以实现实施例一中任一实施方式。

68.由于本实施例所介绍的电子设备为实施本技术实施例一中方法所采用的设备,故而基于本技术实施例一中所介绍的方法,本领域所属技术人员能够了解本实施例的电子设备的具体实施方式以及其各种变化形式,所以在此对于该电子设备如何实现本技术实施例中的方法不再详细介绍。只要本领域所属技术人员实施本技术实施例中的方法所采用的设备,都属于本技术所欲保护的范围。

69.基于同一发明构思,本技术提供了实施例一对应的存储介质,详见实施例四。

70.实施例四

71.本实施例提供一种高精度数模转换介质,如图4、5所示,其上存储有计算机程序,该计算机程序被处理器执行时,可以实现实施例一中任一实施方式。

72.本技术实施例中提供的技术方案,至少具有如下技术效果或优点:

73.1、通过加法器将n位第一数模转换器输出的电压va和n位第二数模转换器输出的电压vb缩小2k倍得到的电压vbb进行叠加,得到输出电压vout,通过对电压vb缩小2k倍使输出电压vout的输出精度提升了k位,达到vref/2

n k

,即使用两个位数一致的数模转换器也可

提升输出精度,无需像传统上采用更高位数的数模转换器,进而极大的降低了数模转换器高精度输出的成本,并能实现线性输出vout,即分辨率是线性的。

74.2、通过使用两个位数一致的数模转换器来提升输出精度,即可使用已经验证和熟悉的数模转换器,无需重新挑选更高位数的数模转换器并进行验证,极大的缩短了开发周期。

75.3、通过设置位数高于第一数模转换器和第二数模转换器的模数转换器对加法器的输出进行采样,当输出电压vout的误差不满足预设的精度时,动态调整第二数模转换器输出的电压vb,直至输出电压vout的误差满足预设的精度,进而保障了数模转换器的输出精度。

76.本领域内的技术人员应明白,本发明的实施例可提供为方法、系统、或计算机程序产品。因此,本发明可采用完全硬件实施例、完全软件实施例、或结合软件和硬件方面的实施例的形式。而且,本发明可采用在一个或多个其中包含有计算机可用程序代码的计算机可用存储介质(包括但不限于磁盘存储器、cd-rom、光学存储器等)上实施的计算机程序产品的形式。

77.本发明是参照本发明实施例的方法、设备(系统)、和计算机程序产品的流程图和/或方框图来描述的。应理解可由计算机程序指令实现流程图和/或方框图中的每一流程和/或方框、以及流程图和/或方框图中的流程和/或方框的结合。可提供这些计算机程序指令到通用计算机、专用计算机、嵌入式处理机或其他可编程数据处理设备的处理器以产生一个机器,使得通过计算机或其他可编程数据处理设备的处理器执行的指令产生用于实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能的装置。

78.这些计算机程序指令也可存储在能引导计算机或其他可编程数据处理设备以特定方式工作的计算机可读存储器中,使得存储在该计算机可读存储器中的指令产生包括指令装置的制造品,该指令装置实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能。

79.这些计算机程序指令也可装载到计算机或其他可编程数据处理设备上,使得在计算机或其他可编程设备上执行一系列操作步骤以产生计算机实现的处理,从而在计算机或其他可编程设备上执行的指令提供用于实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能的步骤。

80.虽然以上描述了本发明的具体实施方式,但是熟悉本技术领域的技术人员应当理解,我们所描述的具体的实施例只是说明性的,而不是用于对本发明的范围的限定,熟悉本领域的技术人员在依照本发明的精神所作的等效的修饰以及变化,都应当涵盖在本发明的权利要求所保护的范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。