一种基于dice单元的双工作模式单粒子双点翻转加固锁存器

技术领域

1.本发明涉及集成电路设计技术领域,尤其涉及一种基于dice单元的双工作模式单粒子双点翻转加固锁存器。

背景技术:

2.电平敏感锁存器是数字电路系统中的基本单元,它们通常用于构建边沿触发的主从触发器。传统的锁存器通常使用两个反相器组成的环路来保存逻辑值,但是这种结构容易发生由粒子轰击造成的单粒子翻转(seu,single event upset)。高能辐射粒子在电路的一个或多个敏感区域上沉积电荷,使节点的电势产生变动,最终锁存器的逻辑状态发生了从“0”到“1”或者从“1”到“0”的改变,即单粒子翻转。一般来说单粒子翻转不会造成永久性的伤害,因此也被称为软错误。

3.对于许多包括锁存器在内的存储单元,有一些经典的抗辐射加固设计技术,如三模冗余(tmr,triple modular redundancy),但其只能消除单个节点上由辐射造成的单粒子翻转。然而,随着器件尺寸进入纳米级以及工作电压越来越低,单粒子事件可以通过电荷共享效应同时影响多个节点。其中单粒子双点翻转(dnu,double node upset),是指高能辐射粒子入射,由于电荷共享效应,导致存储单元中两个状态节点的逻辑值同时发生翻转。

4.单粒子双点翻转对电子电路已造成严重威胁,因为它们可以额外增加软错误率(sers,soft error rates),而传统的抗辐射加固设计方法可能无法完全消除它们的影响。因此,对于先进工艺的半导体电路,设计先进的容忍双点翻转的电路尤为重要。

技术实现要素:

5.本发明旨在至少在一定程度上解决相关技术中的技术问题之一。为此,本发明的一个目的在于提出一种基于dice单元的双工作模式单粒子双点翻转加固锁存器,实现完全容忍单粒子双点翻转的功能。

6.根据本发明提出的一种基于dice单元的双工作模式单粒子双点翻转加固锁存器,包括输入电路、工作模式切换电路、锁存电路、输入信号d、输出节点q,所述输入信号d分别与所述输入电路信号输入端、所述工作模式切换电路信号输入端电信号连接,所述输入电路信号输出端分别与所述锁存电路信号输入端、所述输出节点q电信号连接,所述锁存电路信号输入端还与所述工作模式切换电路信号输出端电信号连接,所述锁存电路信号输出端与所述输出节点q电信号连接。

7.优选地,所述锁存电路包括第一pmos管、第二pmos管、第三pmos管、第四pmos管、第五pmos管、第六pmos管、第七pmos管、第八pmos管、第九pmos管、第十pmos管、第十一pmos管、第十二pmos管、第十三pmos管、第十四pmos管、第一nmos管、第二nmos管、第三nmos管、第四nmos管、第五nmos管、第六nmos管、第七nmos管、第八nmos管、第九nmos管、第十nmos管、第十一nmos管、第十二nmos管、第十三nmos管、第十四nmos管、节点n2、节点n3、节点n4、节点n5、节点n6、节点n7、节点n8、节点cs、节点csf;

所述节点q分别与所述第一pmos管的栅极、所述第五nmos管的栅极、第五pmos管的漏极、所述第一nmos管的漏极连接;所述节点n2分别与所述第四pmos管的栅极、所述第一nmos管的栅极、所述第二nmos管的栅极、所述第一pmos管的漏极、所述第十一pmos管的漏极、所述第四nmos管的漏极连接;所述节点n3分别与所述第二pmos管的栅极、所述第三nmos管的栅极、所述第三pmos管的漏极、所述第十一nmos管的漏极连接;所述节点n4分别与所述第三pmos管的栅极、所述第七nmos管的栅极、所述第十二pmos管的漏极、所述第三nmos管的漏极连接;所述节点n5分别与所述第六pmos管的栅极,所述第七pmos管的栅极、所述第四nmos管的栅极、所述第八nmos管的栅极、所述第四pmos管的漏极、所述第十三pmos管的漏极、所述第六nmos管的漏极、所述第十二nmos管的漏极连接;所述节点n6分别与所述第八pmos管的栅极、所述第十nmos管的栅极、所述第十pmos管的漏极、所述第十三nmos管的漏极连接;所述节点n7分别与所述第十pmos管的栅极、所述第九nmos管的栅极、所述第十四pmos管的漏极、所述第十nmos管的漏极连接;所述节点n8分别与所述第五pmos管的栅极、所述第九pmos管的栅极、所述第六nmos管的栅极、所述第六pmos管的漏极、所述第五nmos管的漏极、所述第十四nmos管的漏极连接;所述节点cs分别与所述第十一pmos管的栅极、所述第十二pmos管的栅极、所述第十三nmos管的栅极、所述第十四nmos管的栅极连接;所述第十一pmos管的源极与所述第二pmos管的漏极连接,所述第十二pmos管的源极与所述第七pmos管的漏极连接,所述第十三nmos管的源极与所述第八nmos管的漏极连接,所述第十四nmos管的源极与所述第九nmos管的漏极连接;所述节点csf分别与所述第十三pmos管的栅极、所述第十四pmos管的栅极、所述第十一nmos管的栅极、所述第十二nmos管的栅极连接;所述第十三pmos管的源极与所述第八pmos管的漏极连接,所述第十四pmos管的源极与所述第九pmos管的漏极相连接,所述第十一nmos管的源极与所述第二nmos管的漏极连接,所述第十二nmos管的源极与所述第七nmos管的漏极连接;所述第一pmos管、第二pmos管、第三pmos管、第四pmos管、第五pmos管、第六pmos管、第七pmos管、第八pmos管、第九pmos管、第十pmos管的源极均与电源电压vdd相连接;所述第一nmos管、第二nmos管、第三nmos管、第四nmos管、第五nmos管、第六nmos管、第七nmos管、第八nmos管、第九nmos管、第十nmos管的源极均与地gnd相连接。

8.优选地,所述锁存电路包括交叉互锁单元与受控交叉互锁单元。

9.优选地,所述交叉互锁单元为六组,六组所述交叉互锁单元分别为所述第一pmos管、第一nmos管;所述第三pmos管、第三nmos管;所述第四pmos管、第四nmos管;所述第五pmos管、第五nmos管;所述第六pmos管、第六nmos管;所述第十pmos管、第十nmos管;所述受控交叉互锁单元为四组,四组所述受控交叉互锁单元分别为所述第二pmos管、第十一pmos管、第二nmos管、第十一nmos管;所述第七pmos管、第十二pmos管、第七nmos

管、第十二nmos管;所述第八pmos管、第十三pmos管、第八nmos管、第十三nmos管;所述第九pmos管、第十四pmos管、第九nmos管、第十四nmos管。

10.优选地,所述输入电路包括第一反相器、第一传输门、第二传输门、第三传输门、第四传输门,所述第一传输门、第二传输门、第三传输门、第四传输门的信号输入端与所述输入信号d电信号连接,所述第一传输门、第二传输门、第三传输门、第四传输门的信号输出端分别与所述节点q、节点n3、节点n5、节点n7连接,所述第一反相器外接有时钟信号clk,所述时钟信号clk通过所述反相器()生成时钟信号clkf,所述第一传输门、第二传输门、第三传输门、第四传输门中的pmos管的栅极均与所述时钟信号clk连接,所述第一传输门、第二传输门、第三传输门、第四传输门中的nmos管的栅极均与所述时钟信号clkf连接。

11.优选地,所述工作模式切换电路包括第五传输门、第二反相器,所述第五传输门的信号输入端与所述输入信号d电信号连接,所述第五传输门的信号输出端为控制信号cs,所述控制信号cs通过所述第二反相器生成控制信号csf,所述第五传输门中的pmos管的栅极与所述时钟信号clk连接,所述第五传输门中的nmos管的栅极与所述时钟信号clkf连接。

12.本发明中的有益效果是:运用冗余-反馈原则,容错原理清晰易懂,能完全容忍单粒子双点翻转,容错能力强,是一种自恢复型的双点加固锁存器。与其他基于dice单元的多点加固锁存器相比,如运用经典三模冗余加固方法的基于dice单元的单粒子三点翻转加固锁存器,本发明所提出的加固锁存器根据锁存的逻辑值决定锁存器的工作模式,实现工作模式的切换,利用了两种工作模式下的锁存电路各自的优势。且在目前存在的双点翻转加固锁存器中功耗较低,d到q的快速通路使延迟相比其他双点翻转加固锁存器相比有优势,是一种低开销、高速的双点翻转加固锁存器。

附图说明

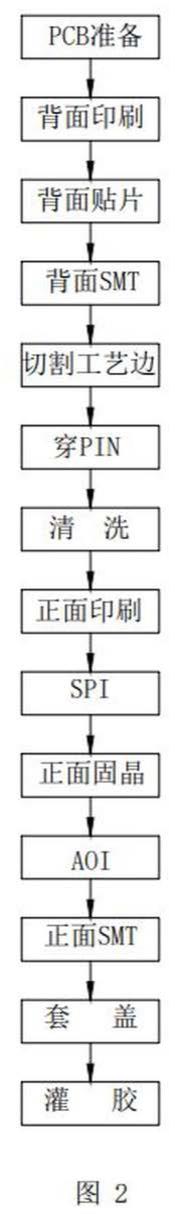

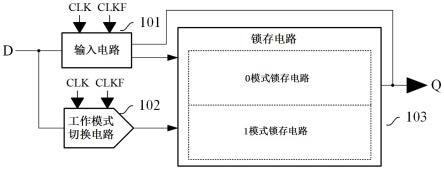

13.附图用来提供对本发明的进一步理解,并且构成说明书的一部分,与本发明的实施例一起用于解释本发明,并不构成对本发明的限制。在附图中:图1为本发明提出的一种基于dice单元的双工作模式单粒子双点翻转加固锁存器的结构框图。

14.图2为本发明提出的图1中输入电路的电路原理图。

15.图3为本发明提出的图1中工作模式切换电路的电路原理图。

16.图4为本发明提出的图1中锁存电路的电路原理图。

17.图5为本发明提出的cs=0时0模式锁存电路的等效电路图。

18.图6为本发明提出的cs=1时1模式锁存电路的等效电路图。

19.图7为本发明提出的容忍单点翻转和双点翻转的工作波形图。

20.图中:101-输入电路、102-工作模式切换电路、103-锁存电路、201-第一反相器、202-第一传输门、203-第二传输门、204-第三传输门、205-第四传输门、301-第五传输门、302-第二反相器、401-第一pmos管、402-第二pmos管、403-第三pmos管、404-第四pmos管、405-第五pmos管、406-第六pmos管、407-第七pmos管、408-第八pmos管、409-第九pmos管、410-第十pmos管、411-第一nmos管、412-第二nmos管、413-第三nmos管、414-第四nmos管、415-第五nmos管、416-第六nmos管、417-第七nmos管、418-第八nmos管、419-第九nmos管、420-第十nmos管、421-第十一pmos管、422-第十二pmos管、423-第十三pmos管、424-第十四

pmos管、425-第十一nmos管、426-第十二nmos管、427-第十三nmos管、428-第十四nmos管。

具体实施方式

21.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。

22.参照图1,一种基于dice单元的双工作模式单粒子双点翻转加固锁存器,由输入电路101、工作模式切换电路102和锁存电路103构成,锁存电路103又根据工作模式的不同分为0模式锁存电路和1模式锁存电路。锁存电路103的输出信号q作为双点翻转加固锁存器的输出信号。当时钟信号clk=0时,锁存器处于透明期,输入电路将外部输入信号d传输到输出节点q,同时也分别传输到工作模式切换电路102和锁存电路103的输入节点,使工作模式切换电路102和锁存电路103的内部节点偏置。当时钟信号clk=1时,锁存器处于锁存期,工作模式切换电路102输出的控制信号cs保持前一状态,即与输出信号q的逻辑值相同,当q=0时,cs=0,锁存电路103受控处在0工作模式,实现锁存功能的是0模式锁存电路;当q=1时,cs=1,锁存电路103受控处在1工作模式,实现锁存功能的是1模式锁存电路。当高能粒子撞击锁存器内部节点造成单粒子翻转时,由于0模式锁存电路和1模式锁存电路分别在相应的工作模式下具有完全容忍双点翻转的能力,从而输出q始终能恢复到正确的逻辑值。

23.输入电路101由1个反相器和4个传输门组成;工作模式切换电路101由1个传输门级联一个反相器组成;锁存电路103由一个dice单元和两个受控dice单元组成直角结构构成。dice单元由四个交叉互锁单元构建,每个交叉互锁单元由一个pmos管和一个nmos管组成。受控dice单元是将dice单元一组对边的交叉互锁单元替换为受控交叉互锁单元,每个受控交叉互锁单元由两个pmos管和两个nmos管组成。

24.如图2所示,输入电路101包括第一反相器201、第一传输门202、第二传输门203、第三传输门204、第四传输门205,第一传输门202、第二传输门203、第三传输门204、第四传输门205的信号输入端与输入信号d电信号连接,第一传输门202、第二传输门203、第三传输门204、第四传输门205的信号输出端分别与节点q、节点n3、节点n5、节点n7连接,第一反相器201外接有时钟信号clk,时钟信号clk通过反相器(201)生成时钟信号clkf,第一传输门202、第二传输门203、第三传输门204、第四传输门205中的pmos管的栅极均与时钟信号clk连接,第一传输门202、第二传输门203、第三传输门204、第四传输门205中的nmos管的栅极均与时钟信号clkf连接;如图3所示,工作模式切换电路102包括第五传输门301、第二反相器302,第五传输门301的信号输入端与输入信号d电信号连接,第五传输门301的信号输出端为控制信号cs,控制信号cs通过第二反相器302生成控制信号csf,第五传输门301中的pmos管的栅极与时钟信号clk连接,第五传输门301中的nmos管的栅极与时钟信号clkf连接。

25.如图4所示,锁存电路103包括第一pmos管401、第二pmos管402、第三pmos管403、第四pmos管404、第五pmos管405、第六pmos管406、第七pmos管407、第八pmos管408、第九pmos管409、第十pmos管410、第十一pmos管421、第十二pmos管422、第十三pmos管423、第十四pmos管424、第一nmos管411、第二nmos管412、第三nmos管413、第四nmos管414、第五nmos管415、第六nmos管416、第七nmos管417、第八nmos管418、第九nmos管419、第十nmos管420、第十一nmos管425、第十二nmos管426、第十三nmos管427、第十四nmos管428、节点n2、节点n3、

节点n4、节点n5、节点n6、节点n7、节点n8、节点cs、节点csf;节点q分别与第一pmos管401的栅极、第五nmos管415的栅极、第五pmos管405的漏极、第一nmos管411的漏极连接;节点n2分别与第四pmos管404的栅极、第一nmos管411的栅极、第二nmos管412的栅极、第一pmos管401的漏极、第十一pmos管421的漏极、第四nmos管414的漏极连接;节点n3分别与第二pmos管402的栅极、第三nmos管413的栅极、第三pmos管403的漏极、第十一nmos管425的漏极连接;节点n4分别与第三pmos管403的栅极、第七nmos管417的栅极、第十二pmos管422的漏极、第三nmos管413的漏极连接;节点n5分别与第六pmos管406的栅极,第七pmos管407的栅极、第四nmos管414的栅极、第八nmos管418的栅极、第四pmos管404的漏极、第十三pmos管423的漏极、第六nmos管416的漏极、第十二nmos管426的漏极连接;节点n6分别与第八pmos管408的栅极、第十nmos管420的栅极、第十pmos管410的漏极、第十三nmos管427的漏极连接;节点n7分别与第十pmos管410的栅极、第九nmos管419的栅极、第十四pmos管424的漏极、第十nmos管420的漏极连接;节点n8分别与第五pmos管405的栅极、第九pmos管409的栅极、第六nmos管416的栅极、第六pmos管406的漏极、第五nmos管415的漏极、第十四nmos管428的漏极连接;节点cs分别与第十一pmos管421的栅极、第十二pmos管422的栅极、第十三nmos管427的栅极、第十四nmos管428的栅极连接;第十一pmos管421的源极与第二pmos管402的漏极连接,第十二pmos管422的源极与第七pmos管407的漏极连接,第十三nmos管427的源极与第八nmos管418的漏极连接,第十四nmos管428的源极与第九nmos管419的漏极连接;节点csf分别与第十三pmos管423的栅极、第十四pmos管424的栅极、第十一nmos管425的栅极、第十二nmos管426的栅极连接;第十三pmos管423的源极与第八pmos管408的漏极连接,第十四pmos管424的源极与第九pmos管409的漏极相连接,第十一nmos管425的源极与第二nmos管412的漏极连接,第十二nmos管426的源极与第七nmos管417的漏极连接;第一pmos管401、第二pmos管402、第三pmos管403、第四pmos管404、第五pmos管405、第六pmos管406、第七pmos管407、第八pmos管408、第九pmos管409、第十pmos管410的源极均与电源电压vdd相连接;第一nmos管411、第二nmos管412、第三nmos管413、第四nmos管414、第五nmos管415、第六nmos管416、第七nmos管417、第八nmos管418、第九nmos管419、第十nmos管420的源极均与地gnd相连接。

26.图5为图1中0模式锁存电路的结构原理图,同时也是图4锁存电路处于0工作模式时的等效电路原理图。在图4中,当锁存器处于锁存期,cs=0时,csf=1,第十一pmos管421,第十二pmos管422,第十一nmos管425和第十二nmos管426导通,包含上述晶体管的两个受控交叉互锁单元可以简化为两个交叉互锁单元;第十三pmos管423,第十四pmos管424,第十三nmos管427和第十四nmos管428关断,此时n6与n7节点的逻辑值变化无法影响到n5与n8节

点,因此节点q的逻辑值与n6,n7节点无关,此情况下实现锁存功能的是0模式锁存电路,故可以将n6,n7节点以及与其相连接的两个受控交叉互锁单元和一个交叉互锁单元简化掉。通过上述简化后,图4所示的锁存电路结构原理图就简化为了图5所示的0模式锁存电路的结构原理图。0模式锁存电路由7个交叉互锁单元构成。7个交叉互锁单元分别由第一pmos管401、第一nmos管411,第二pmos管402、第二nmos管412,第三pmos管403、第三nmos管413,第四pmos管404、第四nmos管414,第五pmos管405、第五nmos管415,第六pmos管406,第六nmos管416,第七pmos管407、第七nmos管417组成。输入电路将输入信号d传输到节点q、n3和n5,节点q也是0模式锁存电路的输出节点。节点q分别连接第一pmos管401和第五nmos管415的栅极,第五pmos管405和第一nmos管411的漏极;节点n2分别连接第四pmos管404、第一nmos管411和第二nmos管412的栅极,第一pmos管401、第二pmos管402和第四nmos管414的漏极;节点n3分别连接第二pmos管402和第三nmos管413的栅极,第三pmos管403和第二nmos管412的漏极;节点n4分别连接第三pmos管403和第七nmos管417的栅极,第七pmos管407和第三nmos管413的漏极;节点n5分别连接第六pmos管406、第七pmos管407和第四nmos管414的栅极,第四pmos管404、第六nmos管416和第七nmos管417的漏极;节点n8分别连接第五pmos管405和第六nmos管416的栅极,第六pmos管406和第五nmos管415的漏极。第一pmos管401、第二pmos管402、第三pmos管403、第四pmos管404、第五pmos管405、第六pmos管406、第七pmos管407的源极均与电源电压vdd相连接。第一nmos管411、第二nmos管412、第三nmos管413、第四nmos管414、第五nmos管415、第六nmos管416、第七nmos管41的源极均与地gnd相连接。

27.图6为图1中1模式锁存电路的结构原理图,同时也是图4锁存电路处于1工作模式时的等效电路原理图。在图4中,当锁存器处于锁存期,cs=1时,csf=0,第十三pmos管423,第十四pmos管424,第十三nmos管427和第十四nmos管428导通,包含上述晶体管的两个受控交叉互锁单元可以简化为两个交叉互锁单元;第十一pmos管421,第十二pmos管422,第十一nmos管425和第十二nmos管426关断,此时n3与n4节点的逻辑值变化无法影响到n2与n5节点,因此节点q的逻辑值与n3,n4节点无关,此情况下实现锁存功能的是1模式锁存电路,故可以将n3,n4节点以及与其相连接的两个受控交叉互锁单元和一个交叉互锁单元简化掉。通过上述简化后,图4所示的锁存电路结构原理图就简化为了图6所示的1模式锁存电路的结构原理图。1模式锁存电路由7个交叉互锁单元构成。7个交叉互锁单元分别由第一pmos管401、第一nmos管411,第四pmos管404、第四nmos管414,第五pmos管405、第五nmos管415,第六pmos管406、第六nmos管416,第八pmos管408、第八nmos管418,第九pmos管409,第九nmos管419,第十pmos管410、第十nmos管420组成。输入电路将输入信号d传输到节点q、n5和n7,节点q也是1模式锁存电路的输出节点。节点q分别连接第一pmos管401和第五nmos管415的栅极,第五pmos管405和第一nmos管411的漏极;节点n2分别连接第四pmos管404和第一nmos管411的栅极,第一pmos管401和第四nmos管414的漏极;节点n5分别连接第六pmos管406、第四nmos管414和第八nmos管418的栅极,第四pmos管404、第八pmos管408和第六nmos管416的漏极;节点n6分别连接第八pmos管408和第十nmos管420的栅极,第十pmos管410和第八nmos管418的漏极;节点n7分别连接第十pmos管410和第九nmos管419的栅极,第九pmos管409和nmos管(420)的漏极;节点n8分别连接第五pmos管405、第九pmos管409和第六nmos管416的栅极,第六pmos管406、第九nmos管419和第五nmos管415的漏极。第一pmos管401,第四pmos管404,第五pmos管405,第六pmos管406,第八pmos管408,第九pmos管409,第十pmos管410的

源极均与电源电压vdd相连接。第一nmos管411,第四nmos管414,第五nmos管415,第六nmos管416,第八nmos管418,第九nmos管419,第十nmos管420的源极均与地gnd相连接。

28.下面分析本发明对单点翻转和双点翻转的抵抗能力:当时钟信号clk=0时,锁存器处于透明期,输入电路将外部输入信号d传输到输出节点q,同时也分别传输到工作模式控制电路和锁存电路的输入节点,使工作模式控制电路和锁存电路的内部节点偏置。当时钟信号clk=1时,锁存器处于锁存期,工作模式控制电路输出的控制信号cs保持前一状态,即与输出信号q的逻辑值相同。

29.当q=0时,cs=0,csf=1,第十一pmos管421,第十二pmos管422,第十一nmos管425和第十二nmos管426导通;第十三pmos管423,第十四pmos管424,第十三nmos管427和第十四nmos管428关断,根据前文可知此时实现锁存功能的是0模式锁存电路。0工作模式下0模式锁存电路的内部节点q=n3=n5=0,n2=n4=n8=1。(1)6个内部节点中任何一个因高能粒子撞击发生逻辑值翻转,故障只能在翻转节点纵向传播,不能横向传播,仍然有四个内部节点保持正确逻辑值,在故障脉冲消亡后,两个错误的节点通过与正确节点连接的横向交叉互锁单元恢复正确逻辑值;(2)内部节点中任何两个因高能粒子撞击发生逻辑值翻转,至少存在两个节点保持正确逻辑值,因为0模式下故障仅能纵向传播,不能横向传播。在故障脉冲消亡后,两个错误节点通过与正确节点连接的横向交叉互锁单元恢复正确逻辑值,恢复正确逻辑值后的两个错误节点继续通过与其余错误节点连接的横向交叉互锁单元恢复其余错误节点的逻辑值。

30.当q=1时,cs=1,csf=0,第十三pmos管423,第十四pmos管424,第十三nmos管427和第十四nmos管428导通;第十一pmos管421,第十二pmos管422,第十一nmos管425和第十二nmos管426关断,根据前文可知此时实现锁存功能的是1模式锁存电路。1工作模式下1模式锁存电路的内部节点q=n5=n7=1,n2=n6=n8=0。(3)6个内部节点中任何一个因粒子撞击发生逻辑值翻转,故障只能在翻转节点横向传播,不能纵向传播,仍然有四个内部节点保持正确逻辑值,在故障脉冲消亡后,两个错误的节点通过与正确节点连接的纵向交叉互锁单元恢复正确逻辑值;(4)6个内部节点中任何两个节点因高能粒子撞击发生逻辑值翻转,至少有两个节点保持正确逻辑值,因为1工作模式下故障仅能横向传播,不能纵向传播。在故障脉冲消亡后,两个错误节点通过与正确节点连接的纵向交叉互锁单元恢复正确逻辑值,恢复正确逻辑值后的两个错误节点继续通过与其余错误节点连接的纵向交叉互锁单元恢复其余错误节点的逻辑值。

31.若单点翻转发生在cs节点或csf节点,将会改变加固锁存器的工作模式,但锁存电路内部节点的逻辑值没有发生改变,所以加固锁存器输出信号q也不会发生改变;若双点翻转的其中一点发生在cs节点或csf节点,同样将会改变加固锁存器的工作模式,但是无论实现锁存功能的是0模式锁存电路还是1模式锁存电路,根据上文的分析可知它们都能完全免疫单点翻转。综上,本发明所提出的加固锁存器能够完全容忍双点翻转。

32.图7为本发明在不同情况下容忍单点翻转和双点翻转的工作波形示意图。在仿真软件hspice中用16纳米ptm工艺模型在25℃下进行模拟,电源电压vdd为0.7v,波形示意图从上到下所代表的分别是时钟信号clk,输入信号d,控制信号csf,内部节点n3,内部节点n5,内部节点n6,内部节点n7,内部节点n8,电路输出信号q。故障注入的模型为双指数电流源。

33.首先分析不同情况下容忍单点翻转的仿真结果2ns时,时钟信号clk为1,电路进入锁存期,锁存前一时刻输入信号d的逻辑值0,所以内部节点n3,内部节点n5,内部节点n7,控制信号cs,电路输出信号q均为0;内部节点n2,内部节点n4,内部节点n6,内部节点n8,控制信号csf均为1,锁存电路处在0工作模式,所示波形示意图与本发明提出的加固锁存器的期望工作状态一致。

34.2.5ns时,电路仍处于锁存期,在内部节点n3注入了一个正向故障脉冲,因为锁存电路工作在0工作模式,因此故障只能纵向传播到内部节点n4,无法影响到输出节点q,并在故障脉冲消亡之后,n3和n4节点分别通过保持正确逻辑值的n2和n5节点恢复。

35.在4ns时,时钟信号clk为1,电路进入锁存期,锁存前一时刻输入信号d的逻辑值1,所以内部节点n3,内部节点n5,内部节点n7,控制信号cs,电路输出信号q均为1;内部节点n2,内部节点n4,内部节点n6,内部节点n8,控制信号csf均为0,锁存电路处在1工作模式。4.5ns时,在内部节点n7注入了一个负向故障脉冲,故障只能横向传播到内部节点n6,无法影响到输出节点q,并在故障脉冲消亡之后,n6和n7节点分别通过保持正确逻辑值的n5和n8节点恢复。

36.在6ns时,时钟信号clk为1,电路进入锁存期,锁存的逻辑值为0,即输出信号q为0,锁存电路处在0工作模式。6.5ns时,在控制信号csf上注入了一个负向故障脉冲,锁存电路的工作模式切换,但内部节点的逻辑值未受影响,所以输出节点q仍保持正确的逻辑值。

37.然后分析不同情况下容忍双点翻转的仿真结果在8ns时,时钟信号clk为1,电路进入锁存期,锁存的逻辑值为0,即输出信号q为0,锁存电路处在0工作模式。8.5ns时,在内部节点n3和n8分别注入一个正向故障脉冲和一个负向故障脉冲,因为锁存电路工作在0工作模式,因此故障只能纵向传播到内部节点n4和输出信号q,在故障脉冲消亡之后,n3节点和输出信号q通过保持正确逻辑值的n2节点恢复,n8节点和n4节点通过保持正确逻辑值的n5节点恢复。从仿真波形图上可以看到,输出信号q在8.5ns仅产生了一个小毛刺。

38.在10ns时,时钟信号clk为1,电路进入锁存期,锁存的逻辑值为1,即输出信号q为1,锁存电路处在1工作模式。10.5ns时,在内部节点n5和n6分别注入一个负向故障脉冲和一个正向故障脉冲,因为锁存电路工作在1工作模式,因此故障只能纵向传播到内部节点n8和内部节点n7,在故障脉冲消亡之后,n5和n8节点分别通过保持正确逻辑值的内部节点n2和输出信号q恢复,然后n6和n7节点再分别通过恢复正确逻辑值的n5和n8节点恢复。

39.在16ns时,时钟信号clk为1,电路进入锁存期,锁存的逻辑值为1,即输出信号q为1,锁存电路处在1工作模式。16.5ns时,在控制信号csf和输出信号q上分别注入一个正向故障脉冲和一个负向故障脉冲,控制信号csf的变化导致锁存电路的工作模式发生切换,但正如之前分析的,无论实现锁存功能的是0模式锁存电路还是1模式锁存电路,它们都能完全免疫单点翻转,所以输出信号q只是出现了一个毛刺,很快又恢复为正确的逻辑值。

40.综合上述分析可知,本发明所提出的双点加固锁存器能够完全容忍双点翻转。

41.本发明所提出的基于dice单元的双工作模式单粒子双点翻转加固锁存器运用冗余-反馈原则,容错原理清晰易懂,能完全容忍单粒子双点翻转,容错能力强,是一种自恢复型的双点加固锁存器。与其他基于dice单元的多点加固锁存器相比,如运用经典三模冗余加固方法的基于dice单元的单粒子三点翻转加固锁存器,本发明所提出的加固锁存器根据

锁存的逻辑值决定锁存器的工作模式,实现工作模式的切换,利用了两种工作模式下的锁存电路各自的优势。且在目前存在的双点翻转加固锁存器中功耗较低,d到q的快速通路使延迟相比其他双点翻转加固锁存器相比有优势,是一种低开销、高速的双点翻转加固锁存器。

42.以上所述,仅为本发明较佳的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,根据本发明的技术方案及其发明构思加以等同替换或改变,都应涵盖在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。