1.本发明涉及芯片模块,尤其涉及芯片模块结构的实施例以及用于设计芯片模块的方法、套件、以及系统的实施例。

背景技术:

2.芯片模块是一种电子组合件。它可包括一个或多个集成电路(integrated circuit;ic)芯片以及装设该芯片的封装件。封装件配置可变化。然而,不管配置如何,将射频(radio frequency;rf)ic芯片纳入封装件中通常导致芯片性能退化,尤其,因各种寄生而导致频率退化。此外,在消费者需求日益增加的较高操作频率应用中(例如,在毫米波(mmwave)应用及太赫兹(terahertz;thz)应用中),此频率退化更大。

技术实现要素:

3.本文中揭示用于设计芯片模块的方法的实施例,该芯片模块包括至少一个射频集成电路(radio frequency integrated circuit;rfic)芯片以及用于该rfic芯片的封装件。具体地说,该方法可包括设计芯片。该芯片的设计可包括该射频前端(radio frequency front end;rffe)的片上分段的设计。具体而言,该片上分段可包括具有第一差分端口的片上放大器(on-chip amplifier)。该方法还可包括针对该芯片设计封装件。该封装件的设计可包括该rffe的片外(off-chip)分段的设计。具体而言,该片外分段可包括具有与该片上放大器的该第一差分端口电性连接的第二差分端口的片外被动装置及匹配网络。设计该rffe的该片外分段可包括例如获取该片上放大器的设计细节,并基于该设计细节,配置该rffe的该片外分段,以使该片外被动装置及匹配网络的该第二差分端口在给定带宽内的不同频率与该第一差分端口功率匹配。

4.更具体地说,在设计用于芯片的封装件期间,尤其在设计将要被包括于该封装件中的rffe的片外分段期间,可基于复功率匹配过程的结果来配置片外被动装置及匹配网络,该复功率匹配过程使用端口电压反射系数(而不是标准阻抗目标),以在给定带宽内的不是一个而是多个不同频率,功率匹配该片外被动装置及匹配网络的第二差分端口与该rffe的片上分段中的片上放大器。此外,此复功率匹配过程可导致芯片功率要求降低。因此,还可在芯片-封装件协同优化过程中迭代重复设计该芯片以及设计该封装件。也就是说,鉴于通过该复功率匹配过程实现的该芯片功率要求的该降低,可重新设计该芯片,以减小片上装置的尺寸(例如,减小晶体管尺寸),从而减小整体芯片尺寸。这样新的芯片设计会带来新的端口电压反射系数。因此,鉴于该新的芯片设计,尤其该新的端口电压反射系数等,可重新设计该封装件,以再次功率匹配该第二差分端口与该第一差分端口。

5.本文中还揭示用于设计芯片模块的系统的实施例,该芯片模块包括至少一个射频集成电路(rfic)芯片以及用于该rfic芯片的封装件。该系统可包括处理器以及储存媒体,该储存媒体可由该处理器读取并储存程序指令。这些程序指令可由该处理器执行,以执行上述方法。

6.最后,本文中还揭示依据上述方法设计并随后制造的芯片模块结构的实施例。此芯片模块结构可包括射频集成电路(rfic)芯片。对于射频前端(rffe),该rfic芯片可包括具有第一差分端口的片上放大器。该芯片模块结构还可包括用于该rfic芯片的封装件。对于该rffe,此封装件可包括具有与该片上放大器的该第一差分端口电性连接的第二差分端口的片外被动装置及匹配网络。该片外被动装置及匹配网络可组合于单个装置例如巴伦(balun)中。或者,该片外被动装置及匹配网络可为分立的电性连接组件(例如,变压器及匹配网络;移相器及匹配网络等)。在任何情况下,具体而言,可基于复功率匹配过程配置该片外被动装置及匹配网络,以使该第二差分端口在给定带宽内的不同频率与该第一差分端口功率匹配。

附图说明

7.通过参照附图自下面的详细说明将更好地理解本发明,该些附图并不一定按比例绘制,且其中:

8.图1显示包括具有片上射频前端(rffe)的射频集成电路(rfic)芯片以及用于该rfic的封装件的示例射频(rf)芯片模块的示意图;

9.图2显示在组装前及组装后在图1的rffe中从功率放大器传递至巴伦(balun)的差分信号的示例正向电压增益(s21)图;

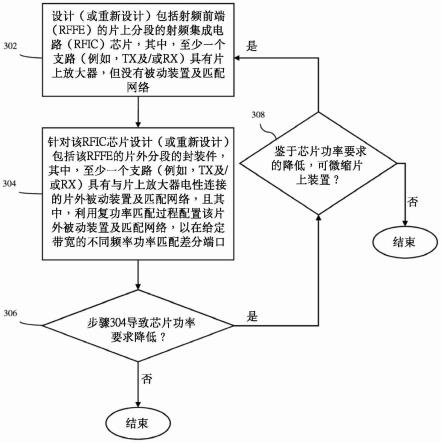

10.图3显示一种方法的实施例的流程图;

11.图4a-4c显示依据该方法生成的替代rfic芯片设计的示意图;

12.图5a-5c显示依据该方法生成的分别用于图4a-4c的rfic芯片设计的替代封装件设计的示意图;

13.图6显示鉴于依据该方法的芯片模块设计,在组装前及组装后从片上功率放大器传递至片外被动装置及匹配网络的差分信号的示例正向电压增益(s21)图;

14.图7及图8分别显示用于实施该方法的计算机辅助设计(cad)系统及代表性硬件环境的示意图;

15.图9a-9c显示依据该方法生成的替代芯片模块设计的布局图;以及

16.图10显示片外被动装置及匹配网络位于封装件衬底(substrate)上的示例实施例的剖视图;以及

17.图11显示片外被动装置及匹配网络位于中介层上(该中介层安装于封装件衬底上)的示例实施例的剖视图。

具体实施方式

18.图1显示示例射频(rf)芯片模块100的图。此rf芯片模块100包括一个或多个rf集成电路(ic)芯片102以及装设rfic芯片102的封装件101。各rfic芯片102可包括用于至少一个rf通信装置(例如,用于发射器、接收器及/或收发器)的射频前端(rffe)150以及额外特征(未显示)。用于收发器的示例rffe 150可包括例如发射器(tx)支路160及接收器(rx)支路170。tx支路160可包括例如功率放大器165,以及串联连接于功率放大器165与tx天线169之间的巴伦(balun)161(在本文中也称为匹配变压器)。功率放大器165可向巴伦161输出差分信号(也就是,平衡信号)。巴伦161可将所接收的差分信号转换为阻抗匹配的单端信号

(也就是,阻抗匹配不平衡信号),并可输出该阻抗匹配的单端输出信号,以经由tx天线169发射。rx支路170可包括低噪声放大器175,以及串联连接于rx天线179与低噪声放大器175之间的巴伦171(在本文中也称为匹配变压器)。巴伦171可从rx天线179接收单端信号(也就是,不平衡信号),可将该单端信号转换为阻抗匹配的差分信号,并可将该阻抗匹配的差分信号输入低噪声放大器175,以供后续片上处理(on-chip processing)。如上所述,tx支路160及rx支路170分别具有分立的天线169及179。不过,应当理解,作为替代,tx支路160及rx支路170可经由开关158与共享天线159连接,该开关经配置以选择性连接tx支路160的巴伦161至共享天线159以发射信号,或选择性连接rx支路170的巴伦171至共享天线159以接收信号。

19.本领域的技术人员将意识到,由不匹配阻抗引起的信号反射可导致显著的性能退化。因此,通过巴伦161及171在tx支路160及rx支路170中进行阻抗匹配是rfic芯片设计的重要部分。通常,为简化阻抗匹配,rfic芯片设计者选择标准阻抗(例如,50欧姆),接着设计rffe组件(例如,tx支路160的功率放大器165及巴伦161以及低噪声放大器175;rx支路170的巴伦171)。在设计期间采用此标准阻抗进行阻抗匹配的决策影响芯片功率要求、片上装置尺寸(例如晶体管尺寸)等,并因此影响性能。而且,当rfic芯片102被纳入芯片模块100中时,因各种寄生因素而不可避免地发生性能退化,尤其是频率退化。在消费者需求日益增加的较高操作频率应用中(例如,毫米波(mmwave)应用及太赫兹(terahertz;thz)应用),此频率退化更大。

20.例如,图2显示针对传统rffe的tx支路160,在封装组装之前(参见曲线201(组装前))及封装组装之后(参见曲线202(组装后))在rffe 150中从功率放大器165传递至巴伦161的差分信号的示例正向电压增益(s21)图。由于功率放大器165及巴伦161与标准阻抗(例如,50欧姆)的阻抗匹配,因此在封装组装之前,在特定频率(例如,在77ghz)获得由23db的正向电压增益(s21)标示的峰值205功率传输,且在封装组装之后,在同一特定频率获得21db的峰值功率传输。不过,在组装之前及组装之后,正向电压增益(s21)在低于及高于该特定频率的频率都降至峰值205以下。而且,由于封装内寄生(in-package parasitics),正向电压增益(s21)在封装组装之后比其在封装组装之前以更大的速率从峰值205下降(例如,参见在83ghz的曲线201与曲线202的正向电压增益(s21)的差)。rx支路170基本也如此。也就是说,由于低噪声放大器175及巴伦171与标准阻抗的阻抗匹配,因此在封装组装之前及之后在特定频率可获得峰值功率传输(在此情况下,反向电压增益(s12))。不过,在封装组装之前及封装组装之后,该反向电压增益(s12)在所有其它频率都下降。而且,由于封装内寄生,该反向电压增益(s12)在封装组装之后比其在封装组装之前以更大的速率从峰值下降。

21.鉴于上述,本文中揭示芯片模块结构的实施例以及用于设计芯片模块的方法及系统,该芯片模块包括至少一个射频集成电路(rfic)芯片以及用于该rfic芯片的封装件。该方法及系统采用芯片-封装件协同优化(co-optimization)过程,不仅避免因封装寄生导致的芯片性能退化,而且提升性能并促进减小芯片尺寸。具体地说,在该方法及系统中,执行芯片设计及封装件设计,以在该芯片与该封装件之间分配射频前端(rffe)。该芯片包括至少一个片上放大器(例如,用于发射器的功率放大器及/或用于接收器的低噪声放大器),分别具有第一差分端口,且该封装件包括对应的片外(off-chip)被动装置及匹配网络(例如,

巴伦,变压器及匹配网络,移相器及匹配网络等),其具有与该第一差分端口电性连接的第二差分端口。通过将该rffe的该被动装置及匹配网络从该芯片移至该封装件,可微缩(scale)芯片尺寸。而且,该片外被动装置及匹配网络通过使用复功率匹配过程来设计,而不是选择标准阻抗目标(例如,50欧姆)并设计与该目标匹配的rffe组件。在此复功率匹配过程中,该片外被动装置及匹配网络的该第二差分端口基于在该第一差分端口且与给定带宽内的不同频率(也就是,在特定的宽频带内)关联的端口电压反射系数与该片上放大器的该第一差分端口功率匹配。此复功率匹配过程可用以针对该宽频带内的所有频率获得相同的峰值功率传输(也就是,而非仅针对一个特定频率的峰值功率传输)。此复功率匹配过程还可导致芯片功率要求的降低。若该芯片功率要求降低,则可微缩该芯片内的装置(例如晶体管)的尺寸。因此,设计该芯片以及设计该封装件可为迭代的芯片-封装件协同优化过程。也就是说,鉴于通过该复功率匹配过程实现的芯片功率要求的降低,可重新设计该芯片,以减小片上装置尺寸,从而减小整个芯片尺寸。该新的芯片设计将针对该宽频带中的该不同频率在该第一差分端口带来新的端口电压反射系数。因此,鉴于该新的芯片设计,尤其该新的端口电压反射系数等,还可重新设计该封装件。本文中还揭示利用上述设计实施例设计的芯片模块结构的实施例。

22.请参照图3的流程图,本文中揭示用于设计芯片模块的方法的实施例,该芯片模块包括一个或多个射频集成电路(rfic)芯片以及用于该rfic芯片的封装件。

23.可利用例如为过程设计及组装设计两者配置的过程及组装设计套件(process and assembly design kit;padk)(也就是,包括过程设计套件(pdk)及组装设计套件(adk)两者的设计套件)实施该芯片模块的设计。出于此揭示的目的,pdk是指一组电子文档(包括数据及脚本文档),它是(例如,由半导体代工厂)为其客户开发的,以便于以该代工厂支持的特定技术节点设计集成电路(ic)芯片。在设计流程的不同阶段,可通过在计算机网络(例如,在计算机辅助设计(computer-aided design;cad)系统上)上执行的一个或多个电子设计自动化(electronic design automation;eda)工具获取该电子文档。示例pdk电子文档可包括但不限于该特定技术节点的模拟模型、符号及技术文档,库(例如,标准单元库、参数化单元(pcell)库等)及设计规则组(design rule deck)等,用于芯片设计流程的不同阶段(例如,用于平面规划(floorplanning)、电源规划、输入/输出引脚布置、库元件布置、时钟规划、布线、布局与原理图(layout versus schematic;lvs)检查、3d仿真、模拟等)。adk是指一组电子文档(包括数据及脚本文档),是为便于此类芯片的封装设计而开发的。该adk电子文档可类似地包括但不限于该特定技术节点的模拟模型、符号及技术文档,库,设计规则组等,用于封装设计流程的不同阶段。

24.该方法可包括设计rfic芯片402(参见过程步骤302及图4a、4b或4c)。传统上,rfic芯片经设计以包括至少一个rf通信装置以及用于该rf通信装置的射频前端(rffe)。例如,该rfic芯片可包括rf通信装置,该rf通信装置可为接收器、发射器或收发器。本领域的技术人员将意识到,用于发射器的该rffe是指从功率放大器至天线的所有电路。用于接收器的该rffe是指从天线至低噪声放大器的所有电路。用于收发器的该rffe包括从功率放大器至tx天线(或者,可选地,经由开关至公共天线)的tx支路内的所有电路,以及从低噪声放大器至rx天线(或者,可选地,经由开关至公共天线)的rx支路内的所有电路。与传统rfic芯片设计不同,本文中揭示的设计方法包括在rfic芯片402与封装件之间分配rffe 450,从而在最

终芯片模块设计中,rffe 450将包括位于rfic芯片402上的片上分段450.1以及位于该封装件中的片外分段450.2。因此,在过程步骤302,rfic芯片402经设计以仅包括用于rf通信装置的rffe 450的片上分段450.1。此片上分段450.1可经设计以包括具有第一差分端口的至少一个放大器,且不具有与该放大器电性连接的任何rffe被动装置。

25.出于说明目的,该方法在下面进行进一步说明,并就收发器的rffe 450显示于附图中。rffe 450的片上分段450.1的设计可包括:对于tx支路460,具有差分输出端口464的功率放大器465;以及,对于rx支路470,具有差分输入端口474的低噪声放大器475。用于该收发器的rffe 450的片上分段450.1的设计还可不具有任何被动装置或匹配网络,如图4a中所示。或者,rffe 450的片上分段450.1的设计可包括具有被动装置及匹配网络的一个支路(该被动装置及匹配网络具有与该放大器的该第一差分端口电性连接的第二差分端口),以及不具有任何被动装置及匹配网络的另一个支路。例如,参见图4b中的rffe 450的片上分段450.1,其中,rx支路470包括被动装置及匹配网络471,其具有与低噪声放大器475的第一差分端口474电性连接的第二差分端口472,且其中,tx支路460不具有任何被动装置及匹配网络。或者,参见图4c中的rffe 450的片上分段450.1,其中,tx支路460包括被动装置及匹配网络461,其具有与功率放大器465的第一差分端口464电性连接的第二差分端口462,且其中,rx支路470不具有任何被动装置及匹配网络。

26.在任何情况下,通常,rffe 450中的放大器(例如,功率放大器465及低噪声放大器475)将经选择(例如,从库中)或定制设计以满足标准阻抗(例如,50欧姆)。不过,由于该方法包括将就片外被动装置及匹配网络与片上放大器之间的任何端口至端口连接而在过程步骤304(下面说明)执行的复功率匹配过程,因此,在rffe 450中且与片外被动装置及匹配网络电性连接的任何片上放大器不需要满足标准阻抗(例如50欧姆)。相反,可以协同优化的最佳负载,针对最佳性能等选择此类片上放大器。此外,由于rffe 450的至少一个支路的被动装置被移出芯片,因此,在过程步骤302的设计期间,可显著微缩该rfic芯片的总体尺寸。例如,rfic芯片(例如图1中所示的rfic芯片102,其包括整个rffe 150)可包括约800平方微米(um2)的总面积,巴伦161、171分别具有约90um2的面积。因此,仅将一个巴伦移离芯片将导致10%以上的面积节约。

27.应当理解,在过程步骤302的rfic芯片402的设计还将包括额外片上电路480(例如,信号处理器等)的设计。此类特征为本领域熟知,因此自本说明书省略,以使读者关注所揭示的实施例的显著态样。

28.在任何情况下,在过程步骤302结束时,rfic芯片402的设计将标示各种芯片设计细节,包括但不限于片上装置的描述(例如,包括晶体管类型、尺寸等)、该芯片的总体尺寸、该芯片的功率要求,以及与rffe 450的片上分段450.1中的放大器的端口关联的s参数。对于功率放大器465,该s参数可包括针对给定带宽的不同频率的输出端口电压反射系数(s22s)。对于低噪声放大器475,该s参数可包括针对相同给定带宽的不同频率的输入端口电压反射系数(s11s)。本领域的技术人员将意识到,包括s22及s11的s参数以及其它s参数(例如,正向电压增益(s21)、反向电压增益(s12)等)是复数。每个s参数包括实部(a)及虚部(jx)(例如,a jx),并随着向各自端口的信号输入或来自各自端口的信号输出的频率变化而变化。因此,例如,与功率放大器465的差分输出端口464关联的s22s将随输出差分信号(也就是,发射的差分信号)的频率变化而变化,而与低噪声放大器475的差分输入端口474

关联的s11s将随输入差分信号(也就是,接收的差分信号)的频率变化而变化。本领域的技术人员将意识到,此类s参数通常通过模拟来确定。

29.请再次参照图3,该方法还可包括从过程步骤302获取该rfic芯片设计(包括上述各种芯片设计细节),并基于该rfic设计及那些芯片设计细节,针对rfic芯片402设计包括rffe 450的片外分段450.2的封装件401(参见过程步骤304)。

30.具体地说,在过程步骤304可设计封装件401,以包括封装件衬底(例如,层压衬底)。例如,该封装件衬底可在背面具有球栅阵列(ball brid array;bga),以便于将该封装件衬底安装于印刷电路板(printed circuit board;pcb)上,并进一步提供在该封装件衬底与该pcb之间的电性连接(例如,用于电源供应、信号传输等)以及围绕这些电性连接的隔离。该封装件衬底可包括过孔及导线(例如,电源迹线、信号迹线等),以提供封装件内及封装件至pcb的电性连接。封装件401还可经设计以包括芯片安装层。该芯片安装层是指将要在其上安装rfic芯片402或包括rfic芯片402的多个芯片(若适用)的层。此芯片安装层可为该封装件衬底本身。也就是说,一个或多个芯片可被直接安装于与背面相对的该封装件衬底的正面上(例如,通过受控塌陷芯片连接(c4连接))。或者,该芯片安装层可为安装于与背面相对的该封装件衬底的正面上的中介层(例如,通过c4连接),且该芯片可被安装于该中介层上(例如,也通过c4连接),以使该中介层堆叠于该封装件衬底与该芯片之间。理想地,该中介层用于多芯片模块,且包括过孔及线路(例如,电源迹线、信号迹线等),以提供芯片至芯片的电性连接以及芯片至衬底的电性连接。

31.在任何情况下,封装件401可经设计以使其包括位于该封装件衬底上或该中介层上(若适用)的rffe 450的片外分段450.2。片外分段450.2可包括具有与片上放大器的第一差分端口电性连接的第二差分端口的至少一个被动装置及匹配网络。

32.例如,考虑图5a中的片外分段450.2,它是在考虑图4a的片上分段450.1的情况下设计的。对于收发器的rffe 450的tx支路460,可在过程步骤304设计片外分段450.2,以包括具有与功率放大器465的差分输出端口464电性连接的差分输入端口462的至少一个片外被动装置及匹配网络461。在一些实施例中,片外被动装置及匹配网络461可组合于具有差分输入端口462的单个装置例如巴伦中。该巴伦可从功率放大器465的差分输出端口464接收差分信号,可将所接收的差分信号转换为阻抗匹配的单端信号(也就是,阻抗匹配不平衡信号),并可通过开关将该阻抗匹配的单端信号输出至天线以供发射。在其它实施例中,片外被动装置及匹配网络461可为电路,其包括:差分输入端口462,用于自功率放大器465接收差分信号;匹配网络,用于执行阻抗匹配;以及被动装置(例如,变压器、移相器等),与该匹配网络连接,以在通过可选的巴伦及开关传递至天线以供发射之前执行其它信号处理(例如,变压、移相等)。类似地,对于收发器的rffe 450的rx支路470,片外分段450.2可包括具有与低噪声放大器475的差分输入端口474电性连接的差分输出端口472的至少一个片外被动装置及匹配网络471。在一些实施例中,片外被动装置及匹配网络471可组合于具有差分输出端口472的单个装置例如巴伦中。该巴伦可经由开关自天线接收单端信号(也就是,不平衡信号),可将该单端信号转换成阻抗匹配的差分信号,并可将该阻抗匹配的差分信号施加于低噪声放大器475的差分输入端口474,以供后续片上处理。

33.如上所述,理想地,rffe 450的片上分段450.1的设计将没有任何被动装置及匹配网络,因此,rffe 450的片外分段450.2的设计将包括针对tx支路460及rx支路470的被动装

置及匹配网络,如所示那样。不过,作为替代,片上分段450.1的设计可在一个支路(例如,tx支路或rx支路)中包括被动装置及匹配网络,并因此,在rffe 450的片外分段450.2的设计中,仅另一个支路会包括被动装置及匹配网络(例如,参见图5b中的片外分段450.2,它是在考虑图4b中所示的片上分段450.1的情况下设计;另请参见图5c中的片外分段450.2,它是在考虑图4c中所示的片上分段450.1的情况下设计的)。

34.在任何情况下,在过程步骤304,片外分段450.2中的各片外被动装置及匹配网络(例如,tx支路460中的461及/或rx支路470中的471)可基于复功率匹配过程的结果来配置,该复功率匹配过程使用rfic芯片设计的s参数(而不是标准阻抗目标),以在给定带宽内的不是一个而是多个不同频率,功率匹配该片外被动装置及匹配网络的差分端口与该片上放大器的差分端口。

35.例如,在tx支路460中(其中,片外分段450.2的片外被动装置及匹配网络461(例如,如图5a或5b中所示)为巴伦),该巴伦可经配置以使差分输入端口462基于给定带宽内的不同频率的差分信号的先前确定的s22值(也就是,不同的输出端口电压反射系数)与功率放大器465的差分输出端口464功率匹配。在rx支路470中(其中,片外分段450.2的被动装置及匹配网络471(例如,如图5a或5c中所示)类似地包括巴伦),该巴伦可经配置以使差分输出端口472基于给定带宽内的不同频率的差分信号的先前确定的s11值(也就是,不同的输入端口电压反射系数)与低噪声放大器475的差分输入端口474功率匹配。

36.为达成此复功率匹配过程,通常,一位组件设计师常常定义后继组件的输入阻抗,它通常为离散阻抗,更传统为50欧姆。在功率匹配而不是将一个组件的一个输入阻抗值与相邻组件的输出阻抗匹配的情况下,执行复共轭匹配。更具体地说,若一个组件(例如,差分功率放大器)的输出阻抗为(a jb)欧姆且若后继组件为巴伦,则其差分输入阻抗需要为(a-jb)欧姆,从而使复部相互抵消。此复阻抗的一个方面是它的频率依赖性,其中,(a jb)欧姆对于给定的频率是固定的,而对于感兴趣的整个频率带宽无效。术语宽频带复功率匹配是指利用ic与封装件一起的协同优化方法针对整个频率带宽进行功率匹配的方法。

37.由于此复功率匹配过程,电压增益(例如,s21或s12)可在较宽的带宽上保持于其峰值。例如,给定带宽的高截止频率与低截止频率的差可高达5ghz或更高,且可针对特定应用定制。例如,在一些实施例中,给定带宽的频率范围可从约77ghz延伸至约83ghz—这是汽车雷达的最佳范围。具体地说,图6显示专门针对tx支路460的片外分段450.2的此复功率匹配过程的结果图。此图显示在封装组装之前(参见曲线601(组装前))及封装组装之后(参见曲线602(组装后))从功率放大器465传递至rffe 450的片外分段450.2中的巴伦461的不同频率的差分信号的示例正向电压增益(s21)。在封装组装之前,在特定频率(例如,77ghz)实现峰值功率传输(例如,23db正向电压增益(s21)),但在所有其它频率下降(参见曲线601)。然而,由于在该方法中采用该复功率匹配过程,因此在封装组装之后,频率性能实际上提升。也就是说,在封装组装之后,正向电压增益(s21)在77ghz以上的频率不会降至23db以下,而是在整个给定带宽650上在23db保持基本不变(例如,从约77ghz的低截止频率605至约83ghz的高截止频率606)(参见曲线602)。对于rx支路460,基本上也是如此。

38.应当注意,由于由上述复功率匹配过程(例如,与片上分段450.1的功率放大器465及/或低噪声放大器475)导致的性能提升,所以可降低芯片的功率要求(先前在过程步骤302被确定为rfic芯片设计的一部分)。因此,该方法可包括比较新的芯片功率要求与先前

的芯片功率要求,以确定在过程步骤304执行的该复功率匹配过程是否已导致芯片功率要求降低(参见过程步骤306)。若否,该方法可结束。不过,若是,该方法可包括在芯片-封装件协同优化过程中迭代重复设计该芯片以及设计该封装件。也就是说,该方法可包括,鉴于芯片功率要求降低,确定装置尺寸微缩(例如,晶体管尺寸微缩)是否可行,并因此确定整体芯片尺寸微缩是否可行(参见过程步骤308)。若否,该方法可结束。若是,则可迭代重复设计该芯片(参见过程步骤302)以及设计该封装件(参见过程步骤304)的过程。也就是说,可重复过程步骤302,以减小至少一些片上装置(例如,至少一些晶体管)的尺寸,从而减小整体芯片尺寸。该新的芯片设计将标示各种设计细节,包括但不限于片上装置的更新描述(例如,包括晶体管类型、尺寸等)、该芯片的总体尺寸、该芯片的功率要求,以及与rffe 450的片上分段450.1中的放大器的端口关联的s参数。

39.接着可重复过程步骤304,包括重新设计rffe 450的片外分段450.2,其包括基于该新的芯片设计(尤其新的s参数,尤其新的端口电压反射系数)的复功率匹配过程。也就是,可重新配置片外分段450.2的各片外被动装置及匹配网络,以使其差分端口基于新的端口电压反射系数而与片上放大器的差分端口功率匹配。例如,在tx支路460中,可重新配置片外被动装置及匹配网络461,以使其差分输入端口462基于新的输出电压反射系数(s22s)与功率放大器465的差分输出端口464功率匹配;而在rx支路470中,可重新配置片外被动装置及匹配网络471,以使其差分输出端口472基于新的输入端口电压反射系数(s11s)而与低噪声放大器475的差分输入端口474功率匹配。

40.此类迭代处理可在芯片功率要求不再降低、装置尺寸微缩不再可行、或者迭代处理已执行某给定时段时(在该时段内,观察到功率降低、性能及/或尺寸微缩没有显著变化)结束。

41.应当注意,上述芯片模块设计方法可通过使用计算机辅助设计(cad)系统及/或作为计算机程序产品而全部或部分实施。

42.具体地说,请参照图7,本文中还揭示用于依据上述方法设计芯片模块的计算机辅助设计(cad)系统700的实施例。该cad系统可包括一个或多个处理器720、一个或多个显示器730,以及可由处理器720读取的一个或多个储存媒体710(例如,储存装置)。cad系统700的各种组件(包括但不限于处理器720、显示器730,以及储存媒体710)可通过系统总线701(如所示那样)以及/或者通过有线或无线网络(未显示)互连。而且,可协同定位该cad系统的各种组件。或者,该cad系统可为具有中央服务器及多个网络工作站的客户端-服务器系统。或者,该cad系统可为分布式系统,其组件分布于不同的网络计算机上。在任何情况下,出于说明目的,图7中将该cad系统显示为仅包含单个处理器720、单个显示器730,以及单个储存媒体710。但是,应当理解,作为替代,该cad系统可包含多个处理器720,以执行如上所述的设计流程中的一个或多个不同步骤;多个显示器730;以及任意数目的一个或多个储存媒体,其储存在该设计流程中的不同步骤期间所使用的数据及工具。储存媒体710可储存过程及组装设计套件(padk)715(参见上面的详细讨论),并且还可储存各种指令程序(例如,电子设计自动化(eda)工具714)。处理器720可执行该指令程序,并且通过使用来自padk 715的数据及其它信息,可执行包括在芯片-封装件协同优化过程中迭代重复芯片设计及封装件设计的上述芯片模块设计方法。储存媒体710还可储存芯片及封装件设计718-719,该些设计在该芯片模块设计方法期间由处理器720生成,且在该芯片-封装件协同优化过程中

迭代重复芯片设计及封装件设计时还可由处理器720获取。

43.计算机程序产品可包括计算机可读储存媒体(或多个媒体),其上具有用计算机可读程序指令,以使处理器执行本发明的态样。

44.该计算机可读储存媒体可为有形装置(也就是,非暂时性储存媒体),其可保持并储存指令以供指令执行装置使用。该计算机可读储存媒体可为例如但不限于电子储存装置、磁储存装置、光储存装置、电磁储存装置、半导体储存装置,或上述任意合适的组合。该计算机可读储存媒体的更具体的例子的非详尽无遗的列表包括以下:便携式计算机磁盘、硬盘、随机访问存储器(random access memory;ram)、只读存储器(read-only memory;rom)、可擦除可编程只读存储器(erasable programmable read-only memory;eprom或闪速存储器)、静态随机访问存储器(sram)、便携式压缩光盘只读存储器(cd-rom)、数字多功能光盘(dvd)、存储棒、软盘、机械编码装置例如打孔卡或凹槽中的突起结构(其上记录指令),以及上述任意组合。本文中所使用的计算机可读储存媒体在本质上不被解释为暂时信号,例如无线电波或其它自由传播的电磁波、经过波导或其它传输媒体传播的电磁波(例如通过光纤线缆的光脉冲)、或通过导线传输的电性信号。

45.本文中所述的计算机可读程序指令可自计算机可读储存媒体下载至各自的计算/处理装置或通过网络例如因特网、局域网、广域网以及/或者无线网络下载至外部计算机或外部储存装置。该网络可包括铜传输线缆、传输光纤、无线传输、路由器、防火墙、开关、网关计算机以及/或者边缘服务器。各计算/处理装置中的网络适配卡或网络接口自该网络接收计算机可读程序指令并转发该计算机可读程序指令以储存于各自的计算机/处理装置内的计算机可读储存媒体中。

46.用以执行本发明的操作的计算机可读程序指令可为汇编指令、指令集架构(instruction-set-architecture;isa)指令、机器指令、机器依赖指令、微代码、固件指令、状态设置数据、或以一种或多种编程语言的任意组合写的源代码或对象代码,该编程语言包括面向对象的编程语言例如smalltalk、c 等,以及传统的过程编程语言,例如“c”编程语言或类似编程语言。该计算机可读程序指令可完全执行于用户的计算机上,部分执行于用户的计算机上,作为独立软件包,部分执行于用户的计算机上并部分执行于远程计算机上或者完全执行于该远程计算机或服务器上。在后一种情况下,该远程计算机可通过任意类型的网络与该用户的计算机连接,包括局域网(local area network;lan)或广域网(wide area network;wan),或者可与外部计算机建立连接(例如使用internet service provider(因特网服务提供商)通过internet(因特网))。在一些实施例中,包括例如可编程逻辑电路、现场可编程门阵列(field-programmable gate array;fpga)或可编程逻辑阵列(programmable logic array;pla)的电子电路可通过使用该计算机可读程序指令的状态信息执行该计算机可读程序指令,以个性化该电子电路,从而执行本发明的态样。

47.本文中参照依据本发明的实施例的方法、装置(系统)以及计算机程序产品的流程图及/或方块图来说明本发明的态样。应当理解,该流程图及/或方块图的各方块以及该流程图及/或方块图中的方块的组合可由计算机程序指令实施。

48.可向通用计算机、专用计算机或其它可编程数据处理装置的处理器提供这些计算机可读程序指令以产生机器,从而使该些指令(通过该计算机或其它可编程数据处理装置的处理器执行)创建用以实施该流程图及/或方块图方块中所指定的功能/动作的方式。这

些计算机可读程序指令也可储存于计算机可读储存媒体中,其可引导计算机、可编程数据处理装置以及/或者其它装置以特定方式作用,以使其中储存有计算机指令的该计算机可读储存媒体包括制造物品,该制造物品包括实施该流程图和/或方块图方块中所指定的功能/动作的态样的指令。

49.该些计算机可读程序指令也可被加载至计算机、其它可编程数据处理装置或其它装置上,以在该计算机、其它可编程数据处理装置或其它装置上执行一系列操作步骤,从而产生计算机实施过程,以使执行于该计算机、其它可编程数据处理装置或其它装置上的该些指令实施该流程图及/或方块图方块中所指定的功能/动作。

50.附图中的流程图及方块图显示依据本发明的各种实施例的系统、方法及计算机程序产品的可能实施的架构、功能及操作。在此方面,该流程图或方块图中的各方块可表示模块、片段或部分指令,其包括一个或多个可执行指令以实施指定的逻辑功能。在一些替代实施中,方块中所示的功能可在附图中所示的顺序之外发生。例如,连续显示的两个方块实际上可基本同时执行,或者有时可以相反顺序执行该些方块,取决于所涉及的功能。还应当注意,该方块图和/或流程图的各方块以及该方块图和/或流程图中的方块的组合可通过基于专用硬件的系统实施,该系统执行指定功能或动作或执行专用硬件与计算机指令的组合。

51.图8中显示用于实施上述设计方法、系统以及计算机程序产品的的代表性硬件环境(也就是,计算机系统)。此示意图显示依据本文中的实施例的信息处理/计算机系统的硬件配置。该系统包括至少一个处理器或中央处理单元(central processing unit;cpu)10。cpu 10通过系统总线12与各种装置例如随机访问存储器(ram)14、只读存储器(rom)16以及输入/输出(i/o)适配器18互连。i/o适配器18可连接周边装置,例如磁盘单元11及磁带驱动器13,或者可由该系统读取的其它程序储存装置。该系统可读取该程序储存装置上的发明指令并遵循这些指令来执行本文中的实施例的方法。该系统还包括用户接口适配器19,其将键盘15、鼠标17、扬声器24、麦克风22以及/或者其它用户接口装置例如触屏装置(未显示)与总线12连接,以收集用户输入。此外,通信适配器20将总线12与数据处理网络25连接,且显示适配器21将总线12与显示装置23连接,该显示装置可实施为输出装置,例如监视器、打印机或发射器。

52.本文中还揭示芯片模块结构900a-900c的实施例(分别参见图9a-9c,另参见图10及11)。芯片模块结构900a-900c可依据上述方法设计并随后制造。

53.此芯片模块结构900a-900c可包括:射频集成电路(rfic)芯片902;可选地,一个或多个额外芯片;以及针对rfic芯片902及任意其它芯片的封装件901。

54.rfic芯片902可包括片上电路980(例如,信号处理器等)。此类特征为现有技术所熟知,因此自本说明书省略,以使读者关注所揭示的实施例的显著态样。

55.请参照图10及11,封装件901可包括封装件衬底999(例如,层压衬底)。封装件衬底999可在背面具有例如球栅阵列(bga),以便将该封装件衬底安装于印刷电路板(pcb)上,并进一步提供在该模块衬底与该pcb之间的电性连接(例如,用于电源供应、信号传输等)以及围绕这些电性连接的隔离。封装件衬底999可包括过孔及导线(例如,电源迹线、信号迹线等),以提供封装件内以及封装件至pcb的电性连接。封装件901可包括芯片安装层。该芯片安装层是指将要在其上安装rfic芯片902或包括rfic芯片402的多个芯片(若适用)的层。此芯片安装层可为该封装件衬底本身(如图10中所示)。也就是说,包括rfic芯片902的一个或

多个芯片可被直接安装于与背面相对的该模块衬底的正面上(例如,通过受控塌陷芯片连接(c4连接))。或者,该封装件901还可包括中介层998,且此中介层998可为芯片安装层(参见图11)。也就是说,中介层998可被安装于与背面相对的封装件衬底999的正面上(例如,通过c4连接),且包括rfic芯片902的该一个或多个芯片可被安装于中介层998上(例如,也通过c4连接),以使中介层998堆叠于该封装件衬底999与该一个或多个芯片之间。理想地,该中介层用于多芯片模块,且包括过孔及线路(例如,电源迹线、信号迹线等),以提供芯片至芯片的电性连接以及芯片至衬底的电性连接。

56.芯片模块900a-900c可包括用于rf通信装置的射频前端(rffe)950。该rf通信装置可为接收器、发射器或收发器。本领域的技术人员将意识到,用于发射器的该rffe是指从功率放大器至天线的所有电路。用于接收器的该rffe是指从天线至低噪声放大器的所有电路。出于说明目的,该rf通信装置在下面说明并在附图中显示为收发器。用于收发器的rffe 950可包括例如发射器(tx)支路960及接收器(rx)支路970。例如,tx支路960可包括功率放大器965,以及串联连接于功率放大器965与tx天线969之间的被动装置及匹配网络961。rx支路970可包括低噪声放大器975,以及串联连接于rx天线979与低噪声放大器975之间的被动装置及匹配网络971。如图所示,tx支路960及rx支路970可分别具有分立的天线969及979。或者,tx支路960及rx支路970可经由开关958与共享天线959连接,该开关经配置以选择性连接tx支路960的被动装置及匹配网络961至共享天线959以发射信号,或连接rx支路970的被动装置及匹配网络971至共享天线959以接收信号。

57.在任何情况下,rffe 950可包括片上分段950.1(也就是,rfic芯片902本身上的分段)以及片外分段950.2(也就是,封装件901中的分段)。片上分段950.1可包括具有第一差分端口的至少一个放大器,且片外分段950.2可包括具有与该放大器电性连接的第二差分端口的被动装置及匹配网络。

58.例如,如图9a的芯片模块结构900a中所示,对于收发器的rffe950的tx支路960,片上分段950.1可包括具有差分输出端口964的功率放大器965。对于收发器的rffe 950的rx支路970,片上分段950.1可包括具有差分输入端口974的低噪声放大器975。对于收发器的rffe 950的tx支路960,片外分段950.2可包括具有与功率放大器965的差分输出端口964电性连接的差分输入端口962的至少一个片外被动装置及匹配网络961。在一些实施例中,片外被动装置及匹配网络961可组合于具有差分输入端口962的单个装置例如巴伦中。该巴伦可从功率放大器965的差分输出端口964接收差分信号,可将所接收的差分信号转换为阻抗匹配的单端信号(也就是,阻抗匹配不平衡信号),并可将该阻抗匹配的单端信号输出至天线(可选地,通过开关)以供发射。在其它实施例中,片外被动装置及匹配网络961可为电路,其包括差分输入端口962,用于自功率放大器965接收差分信号;匹配网络,用于执行阻抗匹配;以及被动装置(例如,变压器、移相器等),与该匹配网络连接,以在(例如,通过可选的巴伦及/或开关)传递至天线以供发射之前执行其它信号处理(例如,变压、移相等)。类似地,对于收发器的rffe 950的rx支路970,片外分段950.2可包括具有与低噪声放大器975的差分输入端口974电性连接的差分输出端口972的至少一个片外被动装置及匹配网络971。在一些实施例中,片外被动装置及匹配网络971可组合于具有差分输出端口972的单个装置例如巴伦中。该巴伦可自天线(可选地,通过开关)接收单端信号(也就是,不平衡信号),可将该单端信号转换成阻抗匹配的差分信号,并可将该阻抗匹配的差分信号施加于低噪声放大

器975的差分输入端口974,以供后续片上处理。

59.或者,如图9b的芯片模块结构900b或图9c的900c所示,rffe950的一个支路可在片上分段950.1中包括被动装置及匹配网络,且rffe 950的另一个支路可在片外分段中包括被动装置及匹配网络。应当注意,如上所述,rffe 950的片外分段950.2的特征(例如,tx支路960的被动装置及匹配网络961及/或rx支路970的被动装置及匹配网络971)可位于封装件衬底999上(如图10中所示)或(若适用)中介层998上(如图11中所示)。

60.由于上述芯片模块方法包括关于片外被动装置及网络与片上放大器之间的任何端口至端口连接执行的复功率匹配过程,因此,位于rffe 950的片上分段950.1中且与片外分段950.2中的片外被动装置及匹配网络电性连接的任何片上放大器将无需满足标准阻抗(例如,50欧姆)。相反,可针对最佳性能等选择此类片上放大器。由于rffe950的至少一个支路的被动装置被包括于片外分段950.2中,因此,与rffe完全位于片上的rfic芯片相比,可在设计期间显著微缩该rfic芯片的总体尺寸。此外,由于片外分段950.2中的各片外被动装置及匹配网络(例如,tx支路960中的961及/或rx支路970中的971)是基于使用该rfic芯片设计的s参数(而不是标准阻抗目标)的复功率匹配过程的结果来配置的,因此,该片外被动装置及匹配网络的差分端口在给定带宽内的不是一个而是多个不同频率与该片上放大器的差分端口功率匹配。也就是说,在rff e950的tx支路960中(其中,片外被动装置及匹配网络961为巴伦),该巴伦的差分输入端口962可针对给定带宽内的不同频率的差分信号与功率放大器965的差分输出端口964功率匹配。类似地,在rffe 950的rx支路970中(其中,片外被动装置及匹配网络971为巴伦),该巴伦的差分输出端口972可针对相同给定带宽内的不同频率的差分信号与低噪声放大器975的差分输入端口974功率匹配。电压增益(例如,s21或s12)在其峰值保持稳定的该给定带宽可较宽。例如,该给定带宽的高截止频率与低截止频率的差可高达5ghz或更高,并可针对特定的应用定制。在一些实施例中,该给定带宽的频率范围可从约77ghz延伸至约83ghz—汽车雷达的最佳范围(例如,参见上面图6的详细讨论)。

61.针对射频前端(rffe),rfic芯片902可包括具有第一差分端口的片上放大器。该芯片模块结构还可包括针对该rfic芯片的封装件。对于该rffe,该封装件可包括具有与该片上放大器的该第一差分端口电性连接的第二差分端口的片外被动装置及匹配网络。该片外被动装置及匹配网络可组合于单个装置例如巴伦中。或者,该片外被动装置及匹配网络可为分立的电性连接组件(例如,变压器及匹配网络;移相器及匹配网络等)。在任何情况下,具体而言,可基于复功率匹配过程配置该片外被动装置及匹配网络,以使该第二差分端口在给定带宽内的不同频率与该第一差分端口功率匹配。

62.应当理解,本文中所使用的术语是出于说明所揭示的结构及方法的目的,并非意图限制。例如,除非上下文中另外明确指出,否则这里所使用的单数形式“一个”以及“该”也意图包括复数形式。另外,本文中所使用的术语“包括”表明所述特征、整体、步骤、操作、元件和/或组件的存在,但不排除存在或添加一个或多个其它特征、整体、步骤、操作、元件、组件,和/或其群组。另外,本文中所使用的术语例如“右”、“左”、“垂直”、“水平”、“顶部”、“底部”、“上方”、“下方”、“正上方”、“正下方”、“平行”、“垂直”等意图说明当它们以附图中取向并显示时的相对位置(除非另外指出),且术语如“接触”、“直接接触”、“毗邻”、“紧邻”等意图表示至少一个元件物理接触另一个元件(没有其它元件隔开所述元件)。本文中所使用的

术语“横向”说明当元件以附图中取向并显示时该些元件的相对位置,尤其表示一个元件位于另一个元件的侧边而不是另一个元件的上方或下方。例如,一个元件横向邻近另一个元件将在该另一个元件旁边,一个元件横向紧邻另一个元件将直接在该另一个元件旁边,以及一个元件横向围绕另一个元件将邻近并环绕该另一个元件的外侧壁。下面的权利要求中的所有手段或步骤加功能元素的相应结构、材料、动作及等同意图包括执行该功能的任意结构、材料或动作结合具体请求保护的其它请求保护的元素。

63.对本发明的各种实施例所作的说明是出于示例目的,而非意图详尽无遗或限于所揭示的实施例。许多修改及变更将对于本领域的普通技术人员显而易见,而不背离所述实施例的范围及精神。本文中所使用的术语经选择以最佳解释所述实施例的原理、实际应用或在市场已知技术上的技术改进,或者使本领域的普通技术人员能够理解本文中所揭示的实施例。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。