1.本发明涉及低压差线性稳压技术领域,尤其涉及一种低压差线性稳压电路。

背景技术:

2.ldo(low dropout regulator)是指低压差线性稳压器,是一种集成电路稳压器,相对于传统的线性稳压器来说的,它通常具有极低的自有噪声和较高的电源抑制比psrr(power supply rejection ratio)。ldo是一个自耗很低的微型片上系统,因其诸多优点得到广泛应用。

3.但现有的ldo电路只能实现单方向的抗干扰能力,即当负载存在输入大电流的干扰时,其电路不能使得输出电压稳定,即ldo失效,且抗干扰的响应速度很慢。

技术实现要素:

4.针对现有技术中存在的问题,本发明提供一种低压差线性稳压电路,包括:

5.第一基准电流源,所述第一基准电流源的输入端连接一电源,所述第一基准电流源的输出端通过一第一开关管连接一基准电路,以提供一基准电压;

6.所述第一开关管的漏极分别连接所述第一基准电流源的输出端和所述第一开关管的栅极,所述第一开关管的源极连接所述基准电路;

7.第二开关管,所述第二开关管的漏极连接所述电源,所述第二开关管的栅极连接所述第一开关管的栅极,所述第二开关管的源极连接一稳压输出端口;

8.当外部向所述稳压输出端口施加向外流出的干扰电流时,通过控制所述第一开关管和所述第二开关管的方式,控制所述稳压输出端口的输出电压相对所述基准电压保持稳定;

9.反馈电路,所述反馈电路分别连接所述基准电路、所述稳压输出端口和地;

10.当外部向所述稳压输出端口施加向内流入的干扰电流时,所述反馈电路用于控制所述稳压输出端口的输出电压相对所述基准电压保持稳定。

11.优选的,所述反馈电路包括:

12.第三开关管,所述第三开关管的源极连接所述稳压输出端口,所述第三开关管的栅极连接所述基准电路;

13.第四开关管,所述第四开关管的栅极连接所述第三开关管的漏极,所述第四开关管的漏极分别连接所述第三开关管的源极和所述稳压输出端口,所述第四开关管的源极接地;

14.第一电阻,所述第一电阻的一端分别连接所述第三开关管的漏极和所述第四开关管的栅极,所述第一电阻的另一端接地。

15.优选的,所述基准电路包括:

16.第五开关管,所述第五开关管的栅极分别连接所述第三开关管的栅极和所述第五开关管的漏极;

17.第二基准电流源,所述第二基准电流源的一端分别连接所述第三开关管的栅极和所述第五开关管的漏极,所述第二基准电流源的另一端接地;

18.第二电阻,所述第二电阻的一端分别连接所述第一开关管的源极和所述第五开关管的源极,所述第二电阻的另一端接地。

19.优选的,所述第三开关管和所述第五开关管为镜像设置的pmos管,所述第三开关管和所述第五开关管的栅极导通电压相同。

20.优选的,所述第四开关管为nmos管。

21.优选的,还包括一第一电容,所述第一电容的一端分别连接所述第三开关管的栅极、所述第五开关管的栅极、所述第五开关管的漏极和所述第二基准电流源的一端,所述第一电容的另一端接地。

22.优选的,所述基准电压的计算公式如下:

[0023]vref

=(i

ref1-i

ref2

)*r2[0024]

其中,v

ref

用于表示所述基准电压,i

ref1

用于表示所述第一基准电流源提供的一第一基准电流值,i

ref2

用于表示所述第二基准电流源提供的一第二基准电流值,r2用于表示所述第二电阻的电阻值。

[0025]

优选的,还包括一第二电容,所述第二电容的一端分别连接所述第一开关管的栅极、所述第二开关管的栅极和所述第一基准电流源的输出端,所述第二电容的另一端接地。

[0026]

优选的,所述第一开关管和所述第二开关管为镜像设置的nmos管,所述第一开关管和所述第二开关管的栅极导通电压相同。

[0027]

优选的,还包括一负载电流源,所述负载电流源的一端连接所述稳压输出端口,所述负载电流源的另一端接地。

[0028]

上述技术方案具有如下优点或有益效果:可以实现输出双向强抗干扰性;电路面积小;针对输出变化,反馈电压能够按照开关管的过驱动电压的平方率变化,大大加快了电路的响应速度。

附图说明

[0029]

图1为本发明的较佳的实施例中,一种低压差线性稳压电路的示意图;

[0030]

图2为本发明的较佳的实施例中,当电路发生干扰时,电路关键点的电压波形示意图。

具体实施方式

[0031]

下面结合附图和具体实施例对本发明进行详细说明。本发明并不限定于该实施方式,只要符合本发明的主旨,则其他实施方式也可以属于本发明的范畴。

[0032]

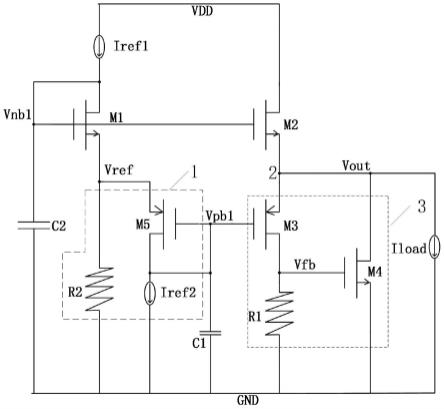

本发明的较佳的实施例中,基于现有技术中存在的上述问题,现提供一种低压差线性稳压电路,如图1所示,包括:

[0033]

第一基准电流源iref1,第一基准电流源iref1的输入端连接一电源vdd,第一基准电流源iref1的输出端通过一第一开关管m1连接一基准电路1,以提供一基准电压vref;

[0034]

第一开关管m1的漏极分别连接第一基准电流源iref1的输出端和第一开关管m1的栅极,第一开关管m1的源极连接基准电路1;

[0035]

第二开关管m2,第二开关管m2的漏极连接电源vdd,第二开关管m2的栅极连接第一开关管m1的栅极,第二开关管m2的源极连接一稳压输出端口2;

[0036]

当外部向稳压输出端口2施加向外流出的干扰电流时,通过控制第一开关管m1和第二开关管m2的方式,控制稳压输出端口2的输出电压相对基准电压保持稳定;

[0037]

反馈电路3,反馈电路3分别连接基准电路1、稳压输出端口2和地,反馈电路3用于在外部向稳压输出端口2施加向内流入的干扰电流时,控制稳压输出端口2的输出电压相对基准电压保持稳定。

[0038]

具体地,本实施例中,采用本技术方案的低压差线性稳压电路,使得该电路工作在静态,即正常工作,不存在外部干扰时,保持稳压输出端口2的输出电压vout与基准电压vref相等,实现稳压。进一步当稳压输出端口2受到外部强烈干扰时,例如存在很强的cmti电流时,该cmti电流的电流值可达10ma,持续20ns,电流的方向随机,该低压差线性稳压电路仍然保持较稳的输出电压vout。换言之,无论外部干扰电流的方向如何,本技术方案的低压差线性稳压电路均能够有效控制稳压输出端口2的输出电压vout相对基准电压vref保持稳定,实现输出双向强抗干扰性。

[0039]

本发明的较佳的实施例中,反馈电路3包括:

[0040]

第三开关管m3,第三开关管m3的源极连接稳压输出端口2,第三开关管m3的栅极连接基准电路1;

[0041]

第四开关管m4,第四开关管m4的栅极连接第三开关管m3的漏极,第四开关管m4的漏极分别连接第三开关管m3的源极和稳压输出端口2,第四开关管的m4源极接地;

[0042]

第一电阻r1,第一电阻r1的一端分别连接第三开关管m3的漏极和第四开关管m4的栅极,第一电阻r1的另一端接地。

[0043]

本发明的较佳的实施例中,基准电路1包括:

[0044]

第五开关管m5,第五开关管m5的栅极分别连接第三开关管m3的栅极和第五开关管m5的漏极;

[0045]

第二基准电流源iref2,第二基准电流源iref2的一端分别连接第三开关管m3的栅极和第五开关管m5的漏极,第二基准电流源iref2的另一端接地;

[0046]

第二电阻r2,第二电阻r2的一端分别连接第一开关管m1的源极和第五开关管m5的源极,第二电阻r2的另一端接地。

[0047]

本发明的较佳的实施例中,第三开关管m3和第五开关管m5为镜像设置的pmos管,第三开关管m3和第五开关管m5的栅极导通电压相同。

[0048]

本发明的较佳的实施例中,第四开关管m4为nmos管。

[0049]

本发明的较佳的实施例中,还包括一第一电容c1,第一电容c1的一端分别连接第三开关管m3的栅极、第五开关管m5的栅极、第五开关管m5的漏极和第二基准电流源iref2的一端,第一电容c1的另一端接地。

[0050]

本发明的较佳的实施例中,基准电压的计算公式如下:

[0051]vref

=(i

ref1-i

ref2

)*r2[0052]

其中,v

ref

用于表示基准电压,i

ref1

用于表示第一基准电流源iref1提供的一第一基准电流值,i

ref2

用于表示第二基准电流源iref2提供的一第二基准电流值,r2用于表示第二电阻r2的电阻值。

[0053]

本发明的较佳的实施例中,还包括一第二电容c2,第二电容c2的一端分别连接第一开关管m1的栅极、第二开关管m2的栅极和第一基准电流源iref1的输出端,第二电容c2的另一端接地。

[0054]

本发明的较佳的实施例中,第一开关管m1和第二开关管m2为镜像设置的nmos管,第一开关管m1和第二开关管m2的栅极导通电压相同。

[0055]

本发明的较佳的实施例中,还包括一负载电流源iload,负载电流源iload的一端连接稳压输出端口2,负载电流源iload的另一端接地。

[0056]

具体地,本技术方案的低压差线性稳压电路工作在静态,即正常工作,不存在外部干扰时,控制第一开关管m1和第五开关管m5导通,且第一开关管m1和第五开关管m5均采用栅极和漏极短接的二极管接法,相当于二极管且具有较小的电压降,基于此,第一基准电流源iref1和第二基准电流源iref2通过第二电阻r2产生基准电压vref,其计算公式如下:

[0057]vref

=(i

ref1-i

ref2

)*r2[0058]

其中,v

ref

用于表示基准电压,i

ref1

用于表示第一基准电流源iref1提供的一第一基准电流值,i

ref2

用于表示第二基准电流源iref2提供的一第二基准电流值,r2用于表示第二电阻r2的电阻值。

[0059]

由于第二开关管m2和第一开关管m1为镜像设置的相同的两个nmos管,则第二开关管m2的栅源电压和第一开关管m1的栅源电压相同。同理,由于第三开关管m3和第五开关管m5为镜像设置的相同的两个pmos管,则第三开关管m3的栅源电压和第五开关管m5的栅源电压相同,因此,在本技术方案的低压差线性稳压电路工作在静态时,稳压输出端口2的输出电压vout与基准电压vref相等。

[0060]

当稳压输出端口2受到外部强烈干扰时,例如在数字隔离器的应用中,存在很强的cmti电流,其电流可达10ma,持续20ns,电流向外流出,控制第二开关管m2和第一开关管m1导通,第三开关管m3和第四开关管m4截止,由于电容c2的存在保持着节点电压vnb1不动,根据如下所示的nmos管的饱和区电流公式:

[0061][0062]

其中,i

ds

表示nmos管的源漏电流,β表示nmos管的跨导系数,v

gs

表示nmos管的栅源电压,v

th

表示nmos管的阈值电压,v

ov

表示nmos管的过驱动电压。

[0063]

可以得到如下所示的稳压输出端口的输出电压vout的改变量的计算公式:

[0064][0065]

其中,δv

out

表示输出电压vout的改变量,i

ds2

表示外部施加向外流出的电流干扰时nmos管的源漏电流,i

ds

表示静态时,nmos管的源漏电流,k表示外部加干扰时,nmos管的源漏电流的改变量,例如,设计nmos管的过驱动电压v

ov

为50mv,静态工作时nmos管的源漏电流为200ua,cmti干扰的干扰电流为10.2ma时,nmos管的源漏电流的改变量k=(10.2-0.2)/0.2=50;则δvout=0.35v。

[0066]

可以看出,采用本技术方案的低压差线性稳压电路,能够实现即使输出电流变化50倍,其vout的输出电压变化很小。

[0067]

当稳压输出端口2受到外部强烈干扰时,例如存在很强的反向cmti电流(第二干扰

电流),其电流可达10ma,持续20ns,电流向内流入,由于电容c1的存在保持着节点电压vpb1不动,这时vout快速产生一个向上的电压,根据如下所示的节点电压v

fb

(反馈电压)的计算公式:

[0068]vfb

=i

dsp

·

r1=0.5

·

r1·

β

p

·

(v

gsp-v

thp

)2[0069]

其中,i

dsp

表示流过第三开关管m3的源漏电流,β

p

表示第三开关管m3的跨导系数,v

gsp

表示第三开关管m3的源栅电压,v

thp

表示第三开关管m3的阈值电压。

[0070]

在静态时,优选将v

fb

设置成0.7vth,其中,vth为第四开关管m4的阈值电压,此时,第四开关管m4处于关闭状态,只要输出电压vout变化超过4个v

ovp

(第三开关管m3的过驱动电压v

ovp

,v

ovp

=v

gsp-v

thp

),则i

dsp

的电流变化为16倍,则导致v

fb

的电压变成11.2vth;此时,第四开关管m4开启,迅速把干扰的cmti电流通过第四开关管m4流走,从而保持输出电压vout的变化很小。可以理解的是,上述v

fb

的值并不限定为0.7vth,可以根据需求进行配置。可以看出,针对输出变化,反馈电压v

fb

能够按照过驱动电压v

ovp

(v

ovp

=v

gsp-v

thp

)的平方率变化,大大加快了电路的响应速度。

[0071]

进一步具体地,考虑到反馈电路采用pmos管时,其若采用与第一开关管m1和第二开关管m2的两个nmos管相同的结构,由于pmos管需要更大的面积,且pmos管的漏源电流ids很小,会导致输出电压变化更大,再者,若采用很大的pmos管,为了保持节点电压vpb1的电压不动,需要配置很大的电容c1,其也需要很大面积;基于pmos管存在上述问题,本发明电路采用第三开关管m3、第一电阻r1和第四开关管m4组成反馈电路,这时pmos管可以采用很小的面积,进而实现本技术方案的低压差线性稳压电路相对现有的低压差线性稳压电路具有更小的电路面积。

[0072]

如图2所示,本发明电路在t0~t1的时间内,其工作在静态的情况下,即负载电流iload为i0(其值可以较小,例如200ua),当时间到达t1时刻,负载电流iload由于外部干扰突然变化到imax(其值可以很大,例如10ma),如nmos管的过驱动电压v

ov

为50mv,静态工作时nmos管的源漏电流为200ua,cmti干扰的第一干扰电流为10.2ma,经上述分析可知,此时,vout向下变化0.35v,第三开关管m3关闭,反馈电压v

fb

迅速变成0v,当时间到达t2时刻时,电流恢复到正常情况;当时间达到t3时刻,负载电流iload由于外部干扰使得稳压输出端口灌入大电流而突然变化到imin,如第三开关管m3的过驱动电压v

ovp

为50mv,若输出电压vout增加0.2v,则反馈电压v

fb

迅速增加至3v,同时快速开启第四开关管m4;当时间达到t4时刻,则电路恢复到静态,即反馈电压v

fb

=0.7vth,输出电压vout恢复到正常值。

[0073]

可以看出,无论外部干扰电流的方向如何,本技术方案的低压差线性稳压电路均能够有效控制稳压输出端口2的输出电压vout相对基准电压vref保持稳定,实现输出双向强抗干扰性。

[0074]

以上所述仅为本发明较佳的实施例,并非因此限制本发明的实施方式及保护范围,对于本领域技术人员而言,应当能够意识到凡运用本说明书及图示内容所作出的等同替换和显而易见的变化所得到的方案,均应当包含在本发明的保护范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。