1.本实用新型涉及液晶显示驱动技术领域,具体涉及一种用于液晶显示装置的数据线驱动电路。

背景技术:

2.在液晶显示器中,通过使用扫描线驱动电路扫描扫描线,电压通过分别布置在各个像素的有源元件从数据线驱动电路被施加给液晶电容,从而控制液晶的旋转角度,不同的旋转角度对应到不同的亮度,由于数据线驱动电路由很多输出驱动线,以4k tv来说,数据线驱动电路需要输出11520条线,如果线跟线之间的电压的偏离量过大,就会让液晶的旋转角度产生差异,这样就会在液晶面板上看到亮度不均的现象,因此为了避免液晶显示上出现上述问题,对显示线的输出电压有很严格的偏离量要求。

技术实现要素:

3.本实用新型提供一种在液晶电容极性转换的时候使用同一组输入级,以减少放大器电路输出级电压偏离量的不一致性,从而降低显示器显示不均机率的液晶显示装置的数据线驱动电路。

4.为解决上述技术问题,本实用新型采用如下技术方案:

5.一种用于液晶显示装置的数据线驱动电路,包括多条第一数据线和多条第二数据线,每条所述第一数据线和第二数据线均包括输入级、中间级以及输出级,还包括:

6.切换开关,所述切换开关连接在输入级与中间级之间,所述切换开关包括用于实现同一数据线中输入级与中间级连接或中断的开关组一以及用于在输出级极性转换时实现相邻第一数据线和第二数据线中输入级与中间级连接或中断的开关组二,且开关组一和开关组二切换分离。

7.优选的,所述开关组一包括开关k1和开关k2;所述开关组二包括开关k3和开关k4,所述开关k1一端与输入级第一输出端o1相连,开关k1另一端与中间级第一输入端o3相连,所述开关k2一端与输入级第二输出端o2相连,开关k2另一端与中间级第二输入端o4相连;所述开关k3与开关k1并联且开关k3一端与输入级第一输出端相连,开关k3另一端与相邻数据线中中间级第一输入端o3相连,所述开关k4与开关k2并联且开关k4一端与输入级第二输出端o2相连,开关k4另一端与相邻数据线中中间级第二输入端o4相连;其中,所述开关k1和开关k2切换同步,所述开关k3和开关k4切换同步。

8.优选的,所述输入级包括薄膜晶体管vt1、薄膜晶体管vt2和薄膜晶体管vt3;所述中间级包括薄膜晶体管vt4、薄膜晶体管vt5、薄膜晶体管vt6、薄膜晶体管vt7、控制电路q1、控制电路q2、薄膜晶体管vt8、薄膜晶体管vt9、薄膜晶体管vt10、薄膜晶体管vt11、薄膜晶体管vt12、薄膜晶体管vt13;所述薄膜晶体管vt1源极接地,漏极与薄膜晶体管vt2和薄膜晶体管vt3的源极相连,所述薄膜晶体管vt2的漏极与开关k1的一端相连,开关k1的另一端与薄膜晶体管vt4和薄膜晶体管vt6相连,所述薄膜晶体管vt3的漏极与开关k2的一端相连,开关

k2的另一端与薄膜晶体管vt5和薄膜晶体管vt7相连,所述开关k3与开关k1并联,且开关k3的一端与薄膜晶体管vt2漏极相连,开关k3另一端与相邻数据线中开关k1另一端同薄膜晶体管vt4源极和薄膜晶体管vt6漏极交汇点之间的节点相连,所述开关k4与开关k2并联,且开关k4的一端与薄膜晶体管vt3的漏极相连,开关k4的另一端与相邻数据线中开关k2另一端同薄膜晶体管vt5源极和薄膜晶体管vt7漏极交汇点之间的节点相连。

9.优选的,所述薄膜晶体管vt4的栅极与薄膜晶体管vt5的栅极相连,且薄膜晶体管vt4的漏极与薄膜晶体管vt5的漏极相连,所述薄膜晶体管vt6的栅极与薄膜晶体管vt7的栅极相连,且薄膜晶体管vt6的源极与控制电路q1的输入端相连,所述控制电路q1的输出端与薄膜晶体管vt8的漏极相连,所述薄膜晶体管vt8的源极与薄膜晶体管vt10的漏极相连,所述薄膜晶体管vt10的源极接地,所述薄膜晶体管vt7的源极与控制电路q2的输入端相连,所述控制电路q2的输出端与薄膜晶体管vt9的漏极相连,所述薄膜晶体管vt9的栅极与薄膜晶体管vt8的栅极相连,所述薄膜晶体管vt9的源极与薄膜晶体管vt11的漏极相连,所述薄膜晶体管vt11的栅极与薄膜晶体管vt10的栅极相连,所述薄膜晶体管vt11的源极接地,所述薄膜晶体管vt12的栅极与薄膜晶体管vt7的源极和控制电路q2的输入端之间的节点相连,所述薄膜晶体管vt12的源极与薄膜晶体管vt13的漏极相连。

10.优选的,所述输出级包括开关k5、开关k6和像素电容c,所述开关k5的一端与薄膜晶体管vt12源极和薄膜晶体管vt13漏极之间的节点相连,开关k5的另一端与像素电容c相连,所述开关k6与开关k5并联,且开关k6的一端与薄膜晶体管vt12源极和薄膜晶体管vt13漏极之间的节点相连,开关k6的另一端与相邻数据线中开关k5另一端和像素电容之间的节点相连。

11.由以上技术方案可知,本实用新型具有如下有益效果:本实用新型通过设置包含开关组一和开关组二的切换开关,当数据线输出端的像素电容极性转换时,通过开关组一中的开关一和开关二同步断开,开关组二中的开关三和开关四同步闭合,从而实现相邻数据线中输入级与中间级之间的连接,从而在输出端像素电容极性转换时,始终使用同一组输入级放大器进行充电,这样一来,可以保证输出端的像素电容在正负极性时具有接近的电压偏离量,从而使得液晶面板在换页面换极性时会显示一样的亮度,可有效降低液晶显示不均的问题。

附图说明

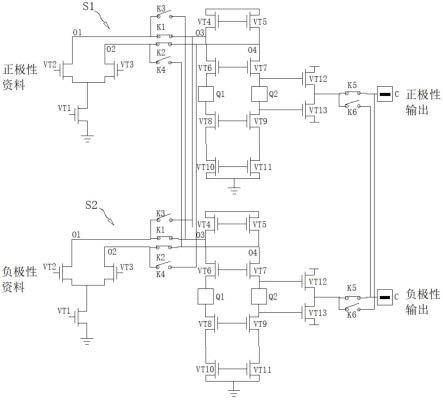

12.图1为本实用新型实施例中数据线s1和数据线s2分别输出正、负极性的电路图;

13.图2为图1中数据线s1和数据线s2输出端极性转换时的电路图;

14.图3为现有技术中数据线s1和数据线s2分别输出正、负极性的电路图;

15.图4为图3中数据线s1和数据线s2输出端极性转换时的电路图。

具体实施方式

16.下面结合附图对本实用新型的一种优选实施方式作详细的说明。

17.鉴于数据线驱动电路中线与线之间电压的偏离量太大会让液晶的旋转角产生差异,从而在液晶面板上产生亮度不均的问题,因此对显示线的输出电压有严格的偏离量要求。由液晶极性原理可知,为了让液晶在旋转不同房像的时候旋转角度一样,数据线驱动电

路在正极性和负极性的偏离量不能差异过大,不然在换页面的时候会有明显的亮暗差异,从而产生亮度不均的问题。

18.在数据线驱动电路里面负责驱动液晶面板的是放大器电路,为了避免产生亮度不均的问题,因此对于放大器电路的输出电压的偏离量要尽可能小,由于放大器电路由三部分组成,输入级、中间级以及输出级,而对于放大器电路来说,其输出端的电压偏离量主要来自于输入级的不协调造成的。因此,为了让液晶在不同方向的时候旋转角度一致,所以希望放大器电路输出级的电压偏离量在正负极性的时候可以一样。又由于输出级的电压偏移量主要来源于输入级,因此可让放大器电路在输出正负极性的时候都使用同一组的输入级,这样就能保持正负极性有接近的电压偏离量,从而使得液晶面板的像素电容在换页面换极性的时候就会显示一样的亮度。

19.基于此,参照图1、图2,本实用新型提供了一种用于液晶显示装置的数据线驱动电路,包括多条第一数据线和多条第二数据线,现以一条第一数据线和一条第二数据线为例进行说明,分别命名为第一数据线s1和第二数据线s2,但本实用新型提供的液晶显示装置的数据线驱动电路并不限于两条,每条第一数据线和第二数据线均包括输入级、中间级以及输出级,其中,在输入级与中间级之间还设有切换开关,所述切换开关包括开关组一和开关组二,开关组一用于实现同一数据线中输入级与中间级之间的连接或中断,开关组二用于在输出级的像素电容极性转换时实现相邻第一数据线和第二数据线中输入级与中间级之间的连接或中断,且开关组一和开关组二切换分离。由此,通过上述的开关组一和开关组二的切换功能,可使得放大器电路输出级的像素电容在极性转换时,始终使用同一组输入级,从而大幅降低放大器输出级电压偏离量的不一致性,从而降低液晶显示亮度不均发生的机率。

20.进一步的,所述输入级包括薄膜晶体管vt1、薄膜晶体管vt2和薄膜晶体管vt3;所述开关组一包括开关k1和开关k2;所述开关组二包括开关k3和开关k4;所述中间级包括薄膜晶体管vt4、薄膜晶体管vt5、薄膜晶体管vt6、薄膜晶体管vt7、控制电路q1、控制电路q2、薄膜晶体管vt8、薄膜晶体管vt9、薄膜晶体管vt10、薄膜晶体管vt11、薄膜晶体管vt12、薄膜晶体管vt13;所述输出级包括开关k5、开关k6和像素电容c,其中,所述开关k1和开关k2切换同步,所述开关k3和开关k4切换同步,即开关k1和开关k2同时闭合或断开,开关k3和开关k4同时闭合或断开。

21.进一步的,所述薄膜晶体管vt1源极接地,漏极与薄膜晶体管vt2和薄膜晶体管vt3的源极相连,所述薄膜晶体管vt2的漏极与开关k1的一端相连,开关k1的另一端与薄膜晶体管vt4和薄膜晶体管vt6相连,所述薄膜晶体管vt3的漏极与开关k2的一端相连,开关k2的另一端与薄膜晶体管vt5和薄膜晶体管vt7相连,所述开关k3与开关k1并联,且开关k3的一端与薄膜晶体管vt2漏极相连,开关k3另一端与相邻数据线中开关k1另一端同薄膜晶体管vt4源极和薄膜晶体管vt6漏极交汇点之间的节点相连,所述开关k4与开关k2并联,且开关k4的一端与薄膜晶体管vt3的漏极相连,开关k4的另一端与相邻数据线中开关k2另一端同薄膜晶体管vt5源极和薄膜晶体管vt7漏极交汇点之间的节点相连。

22.进一步的,所述薄膜晶体管vt4的栅极与薄膜晶体管vt5的栅极相连,且薄膜晶体管vt4的漏极与薄膜晶体管vt5的漏极相连,所述薄膜晶体管vt6的栅极与薄膜晶体管vt7的栅极相连,且薄膜晶体管vt6的源极与控制电路q1的输入端相连,所述控制电路q1的输出端

与薄膜晶体管vt8的漏极相连,所述薄膜晶体管vt8的源极与薄膜晶体管vt10的漏极相连,所述薄膜晶体管vt10的源极接地,所述薄膜晶体管vt7的源极与控制电路q2的输入端相连,所述控制电路q2的输出端与薄膜晶体管vt9的漏极相连,所述薄膜晶体管vt9的栅极与薄膜晶体管vt8的栅极相连,所述薄膜晶体管vt9的源极与薄膜晶体管vt11的漏极相连,所述薄膜晶体管vt11的栅极与薄膜晶体管vt10的栅极相连,所述薄膜晶体管vt11的源极接地,所述薄膜晶体管vt12的栅极与薄膜晶体管vt7的源极和控制电路q2的输入端之间的节点相连,所述薄膜晶体管vt12的源极与薄膜晶体管vt13的漏极相连。

23.进一步的,所述开关k5的一端与薄膜晶体管vt12源极和薄膜晶体管vt13漏极之间的节点相连,开关k5的另一端与像素电容c相连,所述开关k6与开关k5并联,且开关k6的一端与薄膜晶体管vt12源极和薄膜晶体管vt13漏极之间的节点相连,开关k6的另一端与相邻数据线中开关k5另一端和像素电容c之间的节点相连。

24.当需要数据线s1输出端的像素电容为正极性输出时,需满足数据线s1输入级的正极性放大器对像素电容充电;当需要数据线s2输出端的像素电容为负极性输出时,需满足数据线s2输入级的负极性放大器对像素电容充电,由于开关k1和开关k2切换同步,而开关k3和开关k4切换同步,因此当开关k1和开关k2同时闭合,开关k3和开关k4同时断开,此时开关k5闭合,可实现同一数据线中的输入级与输出级的导通,即第一数据线s1和第二数据线s2中各自的输入级与输出级导通,从而将同一数据线中输入级输出的电压施加给输出级的像素电容,每个像素电容的透射率根据电压进行变化。

25.如图1、图2,数据线输出端的像素电容极性转换情况如下,当开关k3和开关k4同时闭合,开关k1和开关k2同时断开,此时开关k6闭合,开关k5断开,可实现输入级与相邻数据线中输出级的像素电容的导通,从而将输入级输出的电压施加给相邻数据线中的像素电容,即当需要数据线s1输出端的像素电容为负极性输出时,数据线s1输入级转换为负极性放大器,并通过开关k3和开关k4与数据线s2中的中间级电连接,通过数据线s1中输入级的负极性放大器对该像素电容充电;而当需要数据线s2输出端的像素电容为正极性输出时,数据线s2输入级转换为正极性放大器,并通过开关k3和开关k4与数据线s1中的中间级电连接,通过数据线s2中输入级的负极性放大器对该像素电容充电。

26.需要说明的是,本实用新型中液晶面板极性转换的时候,驱动器集成电路前端的集成电路时序控制器会向驱动器集成电路传输一个极性转换信号,根据这个信号电平的高低来切换开关开闭。

27.由以上数据线s1和数据线s2输出端的像素电容极性转换的情况可知,在数据线输出端像素电容极性转换时,虽然像素电容对应到的中间级不一样了,但是输入级是一样的,由于数据线驱动电路输出端的电压偏离量主要来自于输入级(占比约为70-80%),因此这样可以大幅减少放大器电路输出端电压偏离量的不一致性,从而降低液晶显示亮度不均发生的机率。

28.而现有技术中的数据线驱动电路如图3、图4所示,就传统的数据线驱动电路而言,当数据线s1输出端的像素电容c为正极性输出时,通过开关k5闭合,可实现同一数据线中输入级与输出级之间的导通,即通过数据线s1输入端的正极性放大器对输出端的像素电容进行充电,相应的,数据线s2输入端的负极性放大器对输出端的像素电容充电,使得数据线s2输出端的像素电容为负极性输出。而在输出端的像素电容极性转换时,即数据线s1输出端

的像素电容c为负极性输出时,此时,开关k6闭合,通过相邻数据线s2输入级的负极性放大器对该像素电容充电;相应的,数据线s2输出端的像素电容c为正极性输出时,通过相邻数据线s1输入级的正极性放大器对该像素电容充电。由上述极性转换的情况可知,数据线s1和数据线s2输出端的像素电容对应到的输入级放大器不同了,由于不同的输入级放大器具有不同的输出电压,因此就会导致输出端的像素电容旋转角度不同,进而会在液晶面板上造成亮暗不均的问题。

29.以上所述实施方式仅仅是对本实用新型的优选实施方式进行描述,并非对本实用新型的范围进行限定,在不脱离本实用新型设计精神的前提下,本领域普通技术人员对本实用新型的技术方案作出的各种变形和改进,均应落入本实用新型的权利要求书确定的保护范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。