1.本发明涉及一种电介质组合物及电子部件。

背景技术:

2.近年来,在车载用途等的电子部件中,寻求在宽的温度范围,显示高的相对介电常数的电介质组合物。

技术实现要素:

3.发明所要解决的问题

4.本发明是鉴于这种实际状况而开发的,其目的在于,提供一种在宽的温度范围,相对介电常数高的新的电介质组合物。

5.用于解决问题的技术方案

6.本发明的电介质组合物包含锶及钽作为主成分。

7.根据本发明的电介质组合物,能够在宽的温度范围显示高的相对介电常数。

8.优选的是,还包含钡作为主成分。

9.优选的是,本发明的电介质组合物实际上不包含钛、铌、碱金属及铅。

10.作为显示高的相对介电常数的电介质组合物,可举出以钛(ti)为主成分的batio3、以铌(nb)为主成分的(sr、ba)nb2o6、包含碱金属的(na、k)nbo3、包含pb的pb(zr、ti)o3。

11.本发明的电介质组合物实际上不包含钛及铌,由此,不易产生氧缺陷。换言之,抑制价态的变化。因此,因为与贱金属同时进行烧结,所以认为即使进行还原烧结,价态也不易变化,并且抑制电阻率的降低,能够在宽的温度范围显示高的电阻率。另外,基于同样的理由,认为能够显示低介电损耗。

12.另外,本发明的电介质组合物实际上不包含碱金属,因此,能够防止碱金属的蒸发导致的、电介质组合物的组成偏差、或炉的污染。

13.另外,铅的使用被rohs(restriction of hazardous substances directive(关于危险物质的限制令))等限制,但本发明的电介质组合物实际上不包含铅。

14.优选的是,所述主成分由{ba

x

sr

(1-x)

}mta4o

12

表示,x为0.75以下。由此,相对介电常数变得更高,并且密度及电阻率变高,介电损耗变低。

15.进一步优选的是,x为0.1~0.75。由此,相对介电常数进一步变高。

16.优选的是,m为1.9~2.1。由此,相对介电常数变得更高,并且密度及电阻率变得更高,介电损耗变得更低。

17.优选的是,所述主成分的晶体的晶系为正方晶系。

18.另外,本发明的电子部件具备上述的电介质组合物。

附图说明

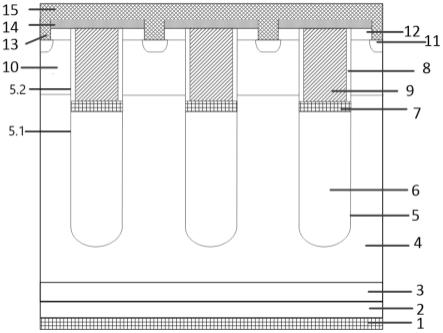

19.图1是本发明的一个实施方式的层叠陶瓷电容器的概略截面图。

20.图2是本发明的一个实施方式的薄膜电容器的概略截面图。

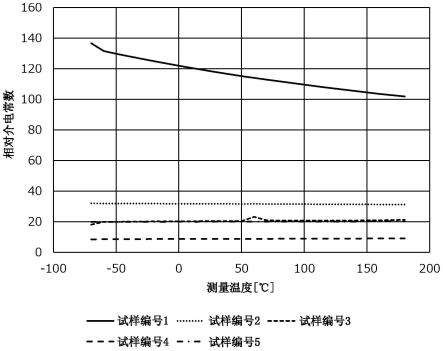

21.图3是表示试样编号1~5的测定温度和相对介电常数的关系的图表。

22.图4是表示电介质组合物的密度和相对介电常数的关系的图表。

23.图5是表示电介质组合物的密度和介电损耗的关系的图表。

24.图6是表示电介质组合物的密度和电阻率的关系的图表。

具体实施方式

25.[第一实施方式]

[0026]

<层叠陶瓷电容器>

[0027]

作为本实施方式的电子部件的一例的层叠陶瓷电容器1在图1中示出。层叠陶瓷电容器1具有交替层叠有电介质层2和内部电极层3的结构的元件主体10。在该元件主体10的两端部,形成有与在元件主体10的内部交替配置的内部电极层3分别导通的一对外部电极4。元件主体10的形状没有特别限制,但通常为长方体状。另外,元件主体10的尺寸也没有特别限制,只要根据用途设为适当的尺寸即可。

[0028]

<电介质层>

[0029]

电介质层2由后述的本实施方式的电介质组合物构成。

[0030]

电介质层2的每1层的厚度(层间厚度)没有特别限定,能够根据期望的特性或用途等进行设定。通常,层间厚度优选为30μm以下,更优选为15μm以下,进一步优选为10μm以下。

[0031]

<内部电极层>

[0032]

在本实施方式中,内部电极层3以各端部在元件主体10的相对的2个端面的表面交替露出的方式层叠。

[0033]

作为内部电极层3中包含的导电材料,没有特别限定。作为用作导电材料的贵金属,例如可举出钯(pd)、铂(pt)、银(ag)-pd合金等。作为用作导电材料的贱金属,例如可举出镍(ni)、ni类合金、铜(cu)、cu类合金等。此外,ni、ni类合金、cu或cu类合金中,也可以包含0.1质量%程度以下的磷(p)和/或硫(s)等各种微量成分。另外,内部电极层3也可以使用市售的电极用膏体来形成。内部电极层3的厚度只要根据用途等适当确定即可。

[0034]

<外部电极>

[0035]

外部电极4中包含的导电材料没有特别限定。例如只要使用镍(ni)、铜(cu)、锡(sn)、ag、pd、pt、金(au)或它们的合金、导电性树脂等公知的导电材料即可。外部电极4的厚度只要根据用途等适当确定即可。

[0036]

<电介质组合物>

[0037]

构成本实施方式的电介质层2的电介质组合物包含锶(sr)及钽(ta)作为主成分。本实施方式的电介质组合物优选还包含钡(ba)作为主成分。

[0038]

本实施方式的电介质组合物的主成分由{ba

x

sr

(1-x)

}mta4o

12

表示。

[0039]

x优选为0.75以下,更优选为0.1~0.75。

[0040]

m优选为1.8~2.2,更优选为1.9~2.1。

[0041]

本实施方式的电介质组合物的主成分的晶体的晶系没有特别限定,优选为正方晶

系或斜方晶系,更优选为正方晶系。

[0042]

此外,主成分是指在将电介质组合物中所含的氧以外的元素设为100摩尔份时,占80~100摩尔份的成分,优选为占90~100摩尔份的成分。

[0043]

另外,本实施方式的电介质组合物实际上不包含钛(ti)、铌(nb)、碱金属及铅(pb)。“实际上不包含钛、铌、碱金属及铅”是指,在将电介质组合物中所含的氧以外的元素设为100摩尔份时,“钛、铌、碱金属及铅”的合计为10摩尔份以下,优选为5摩尔份以下。

[0044]

本实施方式的电介质组合物也可以包含钒(v)、铝(al)、镁(mg)、硅(si)、钙(ca)、锰(mn)、铬(cr)、稀土元素等作为副成分。

[0045]

本实施方式的电介质组合物的密度优选为5.72g/cm3以上,更优选为5.75~7.85g/cm3。此外,将电介质组合物的密度设为上述的范围内的方法没有特别限定,例如可举出调整电介质组合物的烧结温度的方法、调整预烧粉末的粒径的方法或添加烧结助剂的方法等。此外,为了将密度设为上述的范围内,优选将烧结温度设为1380~1600℃。

[0046]

<层叠陶瓷电容器的制造方法>

[0047]

接着,对图1所示的层叠陶瓷电容器1的制造方法的一例进行说明。

[0048]

在本实施方式中,准备构成上述的电介质组合物的主成分的预烧粉末。作为构成主成分的各元素的原料没有特别限定,能够使用各元素的氧化物。另外,能够使用可以通过烧结而得到各元素的氧化物的各种化合物。

[0049]

在将主成分的原料以规定的比例称量之后,使用球磨机等进行规定时间的湿式混合。在将混合粉干燥后,在大气中,在700~1300℃的范围进行热处理,得到主成分的预烧粉末。另外,预烧粉末使用球磨机等进行规定时间的粉碎。

[0050]

接着,制备用于制作生芯片的膏体。将得到的主成分的预烧粉末和溶剂混炼而涂料化,制备电介质层用膏体。粘合剂及溶剂只要使用公知的材料即可。

[0051]

电介质层用膏体根据需要也可以包含增塑剂或分散剂等添加物。

[0052]

内部电极层用膏体将上述的导电材料的原料、粘合剂、以及溶剂混炼而得到。粘合剂及溶剂只要使用公知的材料即可。内部电极层用膏体根据需要也可以包含共同材料(common material)或增塑剂等添加物。

[0053]

外部电极用膏体能够与内部电极层用膏体同样地制备。

[0054]

使用得到的各膏体,形成生片及内部电极图案,将它们层叠而得到生芯片。

[0055]

对得到的生芯片根据需要进行脱粘合剂处理。脱粘合剂处理条件例如将保持温度优选设为200~350℃。

[0056]

在脱粘合剂处理后,进行生芯片的烧结,得到元件主体10。在本实施方式中,烧结时的气氛没有特别限定,可以为空气中,也可以为还原气氛下。在本实施方式中,烧结时的保持温度例如为1380~1600℃。

[0057]

在烧结后,对得到的元件主体10根据需要进行再氧化处理(退火)。退火条件例如优选将退火时的氧分压设为比烧结时的氧分压高的氧分压,将保持温度设为1150℃以下。

[0058]

构成如上述得到的元件主体10的电介质层2的电介质组合物为上述的电介质组合物。对该元件主体10实施端面研磨,涂布外部电极用膏体并烧附,形成外部电极4。然后,根据需要通过镀敷等在外部电极4的表面形成包覆层。

[0059]

这样,制造本实施方式的层叠陶瓷电容器1。

[0060]

根据本实施方式,通过包含锶及钽作为主成分,能够得到在宽的温度范围内相对介电常数恒定并且高的电介质组合物。具体而言,根据本实施方式的电介质组合物,在-55~150℃的温度范围,能够显示75以上的相对介电常数,在-70~180℃的温度范围,能够显示70以上的相对介电常数。

[0061]

另外,根据本实施方式的电介质组合物,在-55~150℃的温度范围内,能够将基准温度设为25℃,将容量变化率设为

±

22%以内,因此,能够满足x8s特性。进而,在-70~180℃的温度范围,能够将基准温度设为25℃,将容量变化率设为

±

22%以内。

[0062]

另外,根据本实施方式,能够得到实际上不包含的钛、铌、碱金属及铅,而显示高密度、高相对介电常数、低介电损耗及高电阻率的电介质组合物。

[0063]

本实施方式的电介质组合物包含钽,并且实际上不包含铌及钛。另一方面,现有的电介质组合物不包含钽,并且包含铌及钛。本实施方式的电介质组合物与现有的电介质组合物相比,具有显示高电阻率及低介电损耗的倾向。作为其理由,认为氧化钽(ta2o5)与氧化铌(nb2o5)及氧化钛(tio2)相比,不易产生氧缺陷。

[0064]

介电特性是以作为绝缘体为前提的特性。因此,要求电介质组合物具有高的电阻,以使电介质组合物不会半导体化或导体化。而且,如上述,氧化钽(ta2o5)与氧化铌(nb2o5)及氧化钛(tio2)相比,不易产生氧缺陷。换言之,抑制价态的变化。因此,认为可以抑制电阻率的降低,在宽的温度范围显示高的电阻率。另外,基于同样的理由,认为能够显示低介电损耗。

[0065]

[第二实施方式]

[0066]

<薄膜电容器>

[0067]

本实施方式的薄膜电容器11的示意图在图2中示出。图2所示的薄膜电容器11在基板111上依次形成下部电极112、电介质薄膜113,在电介质薄膜113的表面具备上部电极114。

[0068]

基板111的材质没有特别限制,但使用si单晶基板作为基板111在易获得性及成本性方面优异。在重视灵活性的情况下,也能够使用ni箔或cu箔作为基板。

[0069]

下部电极112及上部电极114的材质没有特别限制,只要作为电极起作用即可。例如,可举出pt、ag、ni等。下部电极112的厚度没有特别限定,例如为0.01~10μm。上部电极114的厚度也没有特别限定,例如为0.01~10μm。

[0070]

构成本实施方式的电介质薄膜113的电介质组合物的组成及主成分的晶系与第一实施方式相同。

[0071]

电介质薄膜113的厚度没有特别限制,优选为10nm~1μm。

[0072]

<薄膜电容器的制造方法>

[0073]

接着,对薄膜电容器11的制造方法进行说明。

[0074]

最终成为电介质薄膜113的薄膜的成膜方法没有特别限制。例如,示例真空蒸镀法、溅射法、pld法(脉冲激光蒸镀法)、mo-cvd法(有机金属化学气相沉积法)、mod法(有机金属分解法)、溶胶-凝胶法、csd法(化学溶液堆积法)等。

[0075]

另外,虽然有时在成膜时使用的原料中包含微少的杂质或副成分,但只要为不会大幅损害薄膜的性能的程度的量,则没有特别的问题。另外,本实施方式的电介质薄膜113也可以以不会大幅损害性能的程度包含微少的杂质或副成分。

[0076]

在本实施方式中,对基于pld法的成膜方法进行说明。

[0077]

首先,准备si单晶基板作为基板111。接着,在si单晶基板上依次成膜sio2、tio

x

、pt,形成由pt构成的下部电极112。形成下部电极112的方法没有特别限制。例如,可举出溅射法或cvd法等。

[0078]

接着,在下部电极112上通过pld法成膜电介质薄膜113。另外,为了使下部电极112的一部分露出,也可以使用金属掩模来形成薄膜部分未成膜的区域。

[0079]

在pld法中,首先,将包含作为目的的电介质薄膜113的构成元素的靶材设置于成膜室内。接着,在靶材的表面上照射脉冲激光。通过脉冲激光的强的能量使靶材的表面瞬间蒸发。然后,在以与靶材相对的方式配置的基板上堆积蒸发物,成膜电介质薄膜113。

[0080]

靶材的种类没有特别限制,除包含制作的电介质薄膜113的构成元素的金属氧化物烧结体以外,还能够使用合金等。另外,靶材中,优选各元素平均地分布,但在不会对得到的电介质薄膜113的品质造成影响的范围,分布也可以存在不均。

[0081]

靶材不一定必须是一个,也可以准备多个包含电介质薄膜113的构成元素的一部分的靶材用于成膜。靶材的形状也没有限制,只要设为适于使用的成膜装置的形状即可。

[0082]

另外,在pld法时,为了使成膜的电介质薄膜113结晶化,优选在成膜时通过红外线激光对基板111进行加热。基板111的加热温度根据电介质薄膜113及基板111的构成元素及组成等而变化,但例如,以成为600~800℃的方式加热进行成膜。通过将基板111的温度设为适当温度,电介质薄膜113容易结晶化,并且,能够防止在冷却时产生的裂纹的发生。

[0083]

最后,通过在电介质薄膜113上形成上部电极114,能够制造薄膜电容器11。此外,上部电极114的材质没有特别限制,能够使用ag、au、cu等。另外,上部电极114的形成方法也没有特别限制。例如,能够通过蒸镀或溅射法而形成。

[0084]

以上,对本发明的实施方式进行了说明,但本发明完全不限定于上述实施方式,在不脱离本发明的宗旨的范围内能够以各种不同的方式实施,这是不言而喻的。

[0085]

在上述的实施方式中,对本发明的电子部件为层叠陶瓷电容器或薄膜电容器的情况进行了说明,但本发明的电子部件不限定于层叠陶瓷电容器或薄膜电容器,只要具有上述的电介质组合物的电子部件则可以是任意的。

[0086]

例如,也可以为在由上述的电介质组合物构成的单层的电介质基板上形成有一对电极的单板型的陶瓷电容器。

[0087]

另外,本发明的电子部件除电容器以外,也可以为滤波器、双工器、谐振器、振子、天线等。

[0088]

实施例

[0089]

以下,使用实施例及比较例,对本发明进行更详细地说明。但是,本发明不限定于以下的实施例。

[0090]

[实验1]

[0091]

<试样编号1~5>

[0092]

在试样编号1~5中,作为电介质组合物的起始原料,准备通过烧结而成为表1记载的各成分的原料。以成为表1记载的组成式的金属元素比的方式,称量所准备的起始原料(粉末)。

[0093]

接着,使用作为分散介质的离子交换水通过球磨机将所称量的各粉末进行湿式混

合,将混合物干燥而得到混合原料粉末。然后,将得到的混合原料粉末在大气中,在保持温度900℃、保持时间2小时的条件下进行热处理,得到主成分的预烧粉末。

[0094]

使用作为分散介质的离子交换水通过球磨机将得到的主成分的预烧粉末进行湿式粉碎、干燥,得到电介质原料。

[0095]

对得到的电介质原料100质量份添加10质量份的作为粘合剂的包含6质量份的聚乙烯醇树脂的水溶液,进行造粒,得到造粒粉。

[0096]

将得到的造粒粉投入于的模具,以0.6ton/cm2的压力进行预冲压成形,进一步,以1.2ton/cm2的压力进行主冲压成形,得到圆盘状的生成型体。

[0097]

接着,在下述条件下对得到的生成型体进行脱粘合剂处理、烧结及退火,得到元件主体。

[0098]

脱粘合剂处理条件设为保持温度:400℃、温度保持时间:2小时、气氛:空气中。

[0099]

烧结条件设为保持温度:1425~1500℃、温度保持时间:2小时、气氛:加湿的n2 h2混合气体(氧分压为10-12

mpa)。此外,烧结时的气氛气体的加湿使用润湿剂。

[0100]

退火条件设为保持温度:1050℃、温度保持时间:2小时、气氛气体:加湿的n2气体(氧分压:10-7

mpa)。此外,退火时的气氛气体的加湿使用润湿剂。

[0101]

通过下述的方法调查得到的烧结体(电介质组合物)的相对介电常数、介电损耗(tanδ)、密度、电阻率及晶系。此外,为了测量相对介电常数、介电损耗及电阻率,在上述的电介质组合物(烧结体)涂布in-ga电极,得到圆盘状的陶瓷电容器的试样(电容器试样)。

[0102]

<相对介电常数及介电损耗(tanδ)>

[0103]

在室温(20℃)下通过数字lcr表(yhp社制4284a)对电容器试样输入频率1khz、输入信号电平(测定电压)1vrms的信号,测量静电电容c及tanδ。然后,基于烧结体的厚度、有效电极面积、测量的结果得到的静电电容c算出相对介电常数。结果在表1中示出。

[0104]

另外,在-70~180℃的温度范围,每10℃测量相对介电常数。结果在图3中示出。

[0105]

<密度>

[0106]

电介质组合物的密度如下测量。首先,算出电介质组合物的体积v。接着,测量圆盘状的电介质组合物的质量m,计算m/v,从而得到电介质组合物的密度。结果在表1中示出。

[0107]

<电阻率>

[0108]

在基准温度(25℃)下,使用数字电阻表(advantest社制r8340)对电容器试样测量绝缘电阻。根据得到的绝缘电阻、有效电极面积、以及电介质组合物的厚度,算出电阻率。结果在表1中示出。

[0109]

【表1】

[0110]

[0111]

试样编号1~5是属于极性点组的氧化物。根据图3,包含钡、锶及钽作为主成分的试样编号1在宽的测量温度范围(-70~180℃),相对介电常数为100以上,与其它氧化物(试样编号2~5)相比,相对介电常数高。

[0112]

另外,如图3所示,试样编号1在-55~150℃的温度范围,将基准温度设为25℃,容量变化率成为

±

22%以内,因此,能够满足x8s特性。进一步地,在-70~180℃的温度范围,将基准温度设为25℃,容量变化率成为

±

22%以内。

[0113]

从表1能够确认,包含钡、锶及钽作为主成分的试样编号1与其它氧化物(试样编号2~5)相比,为高密度、高相对介电常数、低介电损耗及高电阻率。

[0114]

[实验2]

[0115]

<试样编号21~26、31~34>

[0116]

在试样编号21~26、31~34中,使电介质组合物的起始原料的成分及添加量如下,将烧结保持温度设为1550℃,除此之外,与实验1同样地得到电介质组合物,调查密度、相对介电常数、介电损耗及电阻率。另外,晶系通过下述的方法来调查。结果在表2及表3中示出。此外,在试样编号21~26、31~34中,能够确认在任意的情况下,在-70~180℃的温度范围,相对介电常数均成为70以上。

[0117]

即,在实验2中,准备碳酸钡(baco3)、碳酸锶(srco3)及氧化钽(ta2o5)的粉末作为电介质组合物的起始原料。以使烧结后的主成分由{ba

x

sr

(1-x)

}mta4o

12

表示的组成如表2或表3所记载的方式,称量所准备的起始原料。

[0118]

<晶系>

[0119]

对得到的电介质组合物进行电子束衍射,通过分析电子束衍射图形,解析晶系。

[0120]

【表2】

[0121][0122]

【表3】

[0123][0124]

从表2及表3能够确认,包含锶及钽作为主成分的试样编号26以及包含钡、锶及钽作为主成分的试样编号21~25、31~34的相对介电常数高。

[0125]

从表2能够确认,x为0.75以下时(试样编号22~26)与x为0.80时(试样编号21)相比,显示高密度、高相对介电常数、低介电损耗及高电阻率。

[0126]

从表2能够确认,x为0.10~0.75时(试样编号22~25)与x为0.80时(试样编号21)或x为0.00时(试样编号26)相比,显示高的相对介电常数。

[0127]

从表3能够确认,m为1.9~2.1时(试样编号32、24、33)与m为1.8(试样编号31)或2.2时(试样编号34)相比,显示高密度、高相对介电常数、低介电损耗及高电阻率。

[0128]

[实验3]

[0129]

<试样编号41~45>

[0130]

在试样编号41~45中,在各试样中,使烧结温度在1375~1500℃的范围变化,除此之外,与试样编号1同样地测量电介质组合物(烧结体)的密度、相对介电常数、介电损耗及电阻率。结果在表4及图4~图6中示出。

[0131]

【表4】

[0132][0133]

从表4及图4~图6能够确认,密度超过5.74时(试样编号1、42~45)与密度为5.74时(试样编号41)相比,成为低介电损耗及高电阻率。

[0134]

符号说明

[0135]1……

层叠陶瓷电容器

[0136]

10

……

元件主体

[0137]2……

电介质层

[0138]3……

内部电极层

[0139]4……

外部电极

[0140]

11

……

薄膜电容器

[0141]

111

……

基板

[0142]

112

……

下部电极

[0143]

113

……

多晶电介质薄膜

[0144]

114

……

上部电极

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。