1.本实用新型涉及显示屏技术领域,具体是一种显示屏测试电路走线布局结构及显示屏。

背景技术:

2.有机发光二极管(organic light emitting diode,oled)显示装置较液晶显示装置具有可自发光、广视角、高对比、反应速度快等优点。

3.在对oled cell绑定ic之前,一般先用特定的设备对cell的显示效果进行检测,这种检测称为cell test。当有mux电路时,mux电路只能做在靠近ic处的aa区下方,由于空间受限,cell test电路通常会选择做在aa区的上方,而cell test的输入端口只能在aa区下方,因此少不了连接上下的走线,这些走线都会经过aa区的两侧,结果是cell test电路以及它的走线都占用不少边框位置,不利于缩小边框。

技术实现要素:

4.为了解决上述问题,本实用新型提供一种显示屏测试电路走线布局结构,显示屏测试电路无需从显示屏侧边框走线,显示屏边框得以细窄化。

5.为了达到上述目的,本实用新型采用以下技术方案:

6.一种显示屏测试电路走线布局结构,包括显示屏边框及设于显示屏边框内的显示屏测试电路、有效发光区、mux电路,所述mux电路设于有效发光区下方且与所述有效发光区电性连接,所述显示屏测试电路板设置于所述有效发光区的下方且与所述mux电路配合,用于屏幕测试。

7.可选的,在本实用新型一实施例中,所述mux电路包括第一mux电路和第二mux电路,第一mux电路与第二mux电路均设有对应rgb像素的薄膜晶体管,亮度控制数据线与数据电压端的数量比为1:6,因此,第一mux电路及第二mux电路均设有6个薄膜晶体管q1、q2、q3、q4、q5、q6,有效发光区内部设有12个数据端。

8.可选的,在本实用新型一实施例中,所述薄膜晶体管q1、q2、q3、q4、q5、q6的漏极与有效发光区的rgb数据电压端连接,所述薄膜晶体管q1、q2、q3、q4、q5、q6的源极并联至亮度控制数据线s。

9.可选的,在本实用新型一实施例中,每两个所述薄膜晶体管对应连接一种像素连接布线,具体地,q1和q4对应r像素的数据电压输入端,q2和q5对应g像素数据电压输入端,q3和q6对应b像素的数据电压输入端。

10.可选的,在本实用新型一实施例中,在实际的加工制造中,mux电路与显示屏测试电路之间设置有切割线,进行绑定ic成模组时,切割线以外的显示屏测试电路进行切除,切割线以外对应同一种像素的两个所述薄膜晶体管的栅极相连,并连接至对应各色像素的开关端,具体q1和q4的栅极相连并连接至r像素开关端ctsw_r,q2和q5的栅极相连并连接至g像素开关端ctsw_g,q3和q6的栅极相连并连接至b像素开关端ctsw_b。

11.可选的,在本实用新型一实施例中,对应同一种像素的两个所述薄膜晶体管的栅极相连且连接至对应三色像素的数据电压端,在连接通路上连接有薄膜晶体管rq1、gq1、bq1,对应同一种像素的两个所述薄膜晶体管的栅极连接rq1、gq1、bq1的栅极,rq1、gq1、bq1的漏极并联连接至亮度控制数据线,rq1、gq1、bq1的源极连接数据电压输入端vdr、vdg、vdb。

12.一种显示屏,采用上述的一种显示屏测试电路走线布局结构,显示屏边框顶边及侧边为窄边框。

13.本实用新型有益效果

14.本实用新型的一种显示屏测试电路走线布局结构,显示屏测试电路从原本的有效发光区上方改为设置于有效发光区下方,并且与mux电路之间设有切割线,方便后续的加工操作,可以直接切除,另外显示屏测试电路原本的输入线无需再从显示屏边框的侧边通过,并且顶边的空间同样得到释放,显示屏边框的顶边及侧边可以重新设计为细窄边框,提高产品美观及用户体验。

附图说明

15.为了更清楚地说明本实用新型实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍。

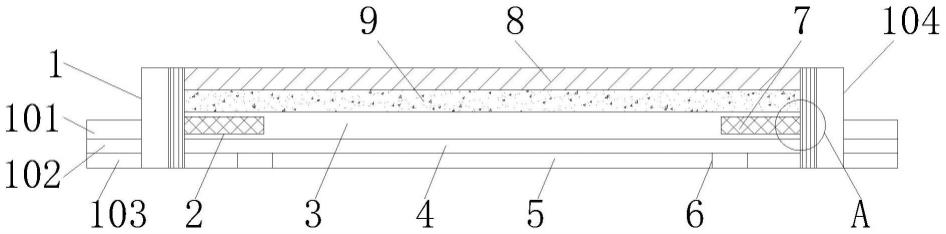

16.图1本实用新型实施例1本技术方案示意图;

17.图2本实用新型实施例1本技术方案电压供应时序示意图;

18.图3现有技术方案的走线布局示意图;

19.附图标记说明:有效发光区1、mux电路2、显示屏测试电路3、切割线4。

具体实施方式

20.为更进一步阐述本实用新型为实现预定实用新型目的所采取的技术手段及功效,以下结合附图及较佳实施例,对依据本实用新型的具体实施方式、结构、特征及其功效,详细说明如后。

21.实施例1

22.如图3所示,显示屏测试电路3设置于有效发光区1上方,即是显示屏边框的顶边,两边为显示屏测试电路3走线,也即是显示屏边框的侧边,mux电路2设于有效发光区1的下方,因为顶边及侧边内部设有显示屏测试电路,边框宽度加大,影响用户体验,因此对显示屏测试电路走线布局进行优化,提供了以下的优化方案:

23.如图1所示,一种显示屏测试电路走线布局结构,包括显示屏边框及设于显示屏边框内的显示屏测试电路3、有效发光区1、mux电路2,所述mux电路2设于有效发光区1下方且与所述有效发光区1电性连接,所述显示屏测试电路3板设置于所述有效发光区1的下方且与所述mux电路2配合,用于屏幕测试。

24.如图1所示,在本实施例中,所述mux电路2包括第一mux电路2和第二mux电路2,不局限于只有两个mux电路2,在这里做方案说明,像素排列为rgb排列,第一mux电路2与第二mux电路2均设有对应rgb像素的薄膜晶体管,亮度控制数据线与数据电压端的数量比为1:6,因此,第一mux电路2及第二mux电路2均设有6个薄膜晶体管q1、q2、q3、q4、q5、q6,有效发

光区1内部设有12个数据端。

25.如图1所示,所述薄膜晶体管q1、q2、q3、q4、q5、q6的漏极与有效发光区1的rgb数据电压端连接,所述薄膜晶体管q1、q2、q3、q4、q5、q6的源极并联至亮度控制数据线s。

26.如图1所示,每两个所述薄膜晶体管对应连接一种像素连接布线,具体地,q1和q4对应r像素的数据电压输入端,q2和q5对应g像素数据电压输入端,q3和q6对应b像素的数据电压输入端。

27.如图1所示,在实际的加工制造中,mux电路2与显示屏测试电路3之间设置有切割线4,进行绑定ic成模组时,切割线4以外的显示屏测试电路3进行切除,切割线4以外,对应同一种像素的两个所述薄膜晶体管的栅极相连,并连接至对应各色像素的开关端,具体地,q1和q4的栅极相连并连接至r像素开关端ctsw_r,q2和q5的栅极相连并连接至g像素开关端ctsw_g,q3和q6的栅极相连并连接至b像素开关端ctsw_b,同时ctsw_r还控制vdr的输入;ctsw_g还控制vdg的输入;ctsw_b还控制vdb的输入。

28.如图1所示,对应同一种像素的两个所述薄膜晶体管的栅极相连且连接至对应三色像素的数据电压端,在连接通路上连接有薄膜晶体管rq1、gq1、bq1,对应同一种像素的两个所述薄膜晶体管的栅极连接rq1、gq1、bq1的栅极,rq1、gq1、bq1的漏极并联连接至亮度控制数据线,rq1、gq1、bq1的源极连接数据电压输入端vdr、vdg、vdb。

29.如图2所示,一般像素电路接受到的vdata电压越低,像素点发光亮度越大。在进行cell test的时候,假如要点亮红色画面,可按图2的时序提供电压给cell test输入端口:将所有的r像素点亮,所有的g、b像素不点亮。如要点亮其他颜色,合理搭配vdr/vdg/vdb的电压即可。

30.特别地,如果所有的s线都用同层金属进行走线,由于工艺的问题,相邻的s线之间可能存在微短路。如图1,cell test方案可改进为所有奇数编号s线对应的vdr/vdg/vdb与所有偶数编号s线对应的vdr/vdg/vdb区分开,分别命名为vdr1/vdg1/vdb1,和vdr2/vdg2/vdb2,当进行正常cell test画面点亮时,相同颜色的vdr1/vdg1/vdb1和vdr2/vdg2/vdb2电压一致,但要进行相邻同层金属的s线短路检测时,相同颜色的vdr1/vdg1/vdb1和vdr2/vdg2/vdb2电压设置为不相同,例如设置vdr1/vdg1/vdb1=2v,vdr2/vdg2/vdb2=5v,当s1和s2之间有短路,而其他s线之间没有短路时,只有vdata1至vdata12的电压是2v到5v之间的某个电压,点亮后可以看到它们对应的像素点的亮度与其他区域像素点亮度不一样,从而判断出s1和s2短路。

31.实施例2

32.一种显示屏,采用上述的一种显示屏测试电路走线布局结构,显示屏边框顶边及侧边为窄边框。

33.以上,仅是本实用新型的较佳实施例而已,并非对本实用新型作任何形式上的限制,虽然本实用新型已以较佳实施例揭示如上,然而并非用以限定本实用新型,任何本领域技术人员,在不脱离本实用新型技术方案范围内,当可利用上述揭示的技术内容做出些许更动或修饰为等同变化的等效实施例,但凡是未脱离本实用新型技术方案内容,依据本实用新型的技术实质对以上实施例所作的任何简介修改、等同变化与修饰,均仍属于本实用新型技术方案的范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。