1.本发明涉及半导体装置、功率模块及半导体装置的制造方法。

背景技术:

2.在使用了sic mosfet的模块中,sic mosfet的大面积化是困难的,因此,为了增加电流容量而将多个芯片并联连接。提出了将多个半导体元件和配线元件接合于相同的导体板,通过配线元件的电路图案而将多个半导体元件的控制电极并联连接的半导体装置(例如,参照专利文献1)。

3.专利文献1:国际公开第2020/110170号

4.在配线元件为了正反面的绝缘而设置有氧化膜。就当前的半导体装置而言,通过该氧化膜而确保呈漏极电位的导体板与呈控制电位的电路图案之间的绝缘。但是,就例如面向电气铁路驱动等的高耐压半导体装置而言,绝缘性确保所需的氧化膜变厚。因此,制造成本增大,由于堆积厚的氧化膜的生产难度,生产率下降,厚积的氧化膜的可靠性下降。例如如果使teos堆积得厚,则晶片翘曲、膜发生剥离、表面变粗糙等制造性和品质下降。通过氧化膜来堆积具有大于或等于1.7kv的耐压的绝缘膜这一做法对于通常的功率半导体的工艺而言并不普通。因此,就当前的半导体装置而言,绝缘耐量的提高是困难的。

技术实现要素:

5.本发明就是为了解决上述这样的课题而提出的,其目的在于,得到能够容易地提高绝缘耐量的半导体装置、功率模块及半导体装置的制造方法。

6.本发明涉及的半导体装置的特征在于,具有:第1导体板;第2导体板,其与所述第1导体板分离;多个半导体元件,其背面电极与所述第1导体板连接;中继基板,其设置于所述第2导体板之上,该中继基板具有多个第1中继焊盘和与所述多个第1中继焊盘连接的第2中继焊盘;多个金属导线,其将所述多个半导体元件的控制电极与所述多个第1中继焊盘分别连接;第1导体块,其与所述多个半导体元件的表面电极连接;第2导体块,其与所述第2中继焊盘连接;以及

7.封装材料,其将所述第1导体板及第2导体板、所述多个半导体元件、所述中继基板、所述金属导线、所述第1导体块及第2导体块封装,所述封装材料具有彼此相对的第1主面及第2主面,所述第1导体板从所述第1主面露出,所述第2导体板不从所述第1主面露出,所述第1导体块及第2导体块从所述第2主面露出。

8.发明的效果

9.在本发明中,使安装有多个半导体元件的第1导体板与安装有中继基板的第2导体板分离地被封装材料封装。并且,第1导体板从封装材料的第1面露出,但第2导体板不从封装材料的第1面露出。由此,能够将第1导体板与第2导体板绝缘,所以能够容易地提高绝缘耐量。

附图说明

10.图1是表示实施方式1涉及的半导体装置的内部的俯视图。

11.图2是沿图1的i-ii的剖视图。

12.图3是表示实施方式1涉及的半导体装置的变形例的内部的俯视图。

13.图4是表示实施方式1涉及的半导体装置的制造工序的俯视图。

14.图5是表示实施方式1涉及的半导体装置的制造工序的剖视图。

15.图6是表示实施方式1涉及的半导体装置的制造工序的俯视图。

16.图7是表示实施方式1涉及的半导体装置的制造工序的剖视图。

17.图8是表示实施方式1涉及的半导体装置的制造工序的俯视图。

18.图9是表示实施方式1涉及的半导体装置的制造工序的剖视图。

19.图10是表示实施方式1涉及的半导体装置的制造工序的俯视图。

20.图11是表示实施方式1涉及的半导体装置的制造工序的剖视图。

21.图12是表示实施方式1涉及的半导体装置的制造工序的俯视图。

22.图13是表示实施方式1涉及的半导体装置的制造工序的剖视图。

23.图14是表示实施方式1涉及的半导体装置的制造工序的俯视图。

24.图15是表示实施方式1涉及的半导体装置的制造工序的剖视图。

25.图16是表示实施方式1涉及的半导体装置的制造工序的俯视图。

26.图17是表示实施方式1涉及的半导体装置的制造工序的剖视图。

27.图18是表示实施方式1涉及的半导体装置的制造工序的俯视图。

28.图19是表示实施方式1涉及的半导体装置的制造工序的剖视图。

29.图20是表示实施方式1涉及的半导体装置的制造工序的俯视图。

30.图21是表示实施方式1涉及的半导体装置的制造工序的剖视图。

31.图22是表示使用了多个实施方式1涉及的半导体装置的功率模块的俯视图。

32.图23是表示实施方式2涉及的半导体装置的内部的俯视图。

33.图24是表示实施方式2涉及的半导体装置的制造工序的俯视图。

34.图25是表示实施方式2涉及的半导体装置的制造工序的剖视图。

35.图26是表示实施方式2涉及的半导体装置的制造工序的俯视图。

36.图27是表示实施方式2涉及的半导体装置的制造工序的剖视图。

37.图28是表示实施方式2涉及的半导体装置的制造工序的俯视图。

38.图29是表示实施方式2涉及的半导体装置的制造工序的剖视图。

39.图30是表示实施方式2涉及的半导体装置的制造工序的俯视图。

40.图31是表示实施方式2涉及的半导体装置的制造工序的剖视图。

41.图32是表示实施方式2涉及的半导体装置的制造工序的俯视图。

42.图33是表示实施方式2涉及的半导体装置的制造工序的剖视图。

43.图34是表示实施方式2涉及的半导体装置的制造工序的俯视图。

44.图35是表示实施方式2涉及的半导体装置的制造工序的剖视图。

45.图36是表示实施方式2涉及的半导体装置的制造工序的俯视图。

46.图37是表示实施方式2涉及的半导体装置的制造工序的剖视图。

47.图38是表示实施方式2涉及的半导体装置的制造工序的俯视图。

48.图39是表示实施方式2涉及的半导体装置的制造工序的剖视图。

49.图40是表示实施方式2涉及的半导体装置的制造工序的俯视图。

50.图41是表示实施方式2涉及的半导体装置的制造工序的剖视图。

51.图42是表示实施方式3涉及的半导体装置的内部的俯视图。

52.图43是沿图42的i-ii的剖视图。

具体实施方式

53.参照附图,对实施方式涉及的半导体装置、功率模块及半导体装置的制造方法进行说明。对相同或相应的结构要素标注相同的标号,有时省略重复说明。

54.实施方式1

55.图1是表示实施方式1涉及的半导体装置的内部的俯视图。图2是沿图1的i-ii的剖视图。第2导体板2与第1导体板1分离。多个半导体元件3安装于第1导体板1之上。半导体元件3在表面具有控制电极4及表面电极5,在背面具有背面电极6。在半导体元件3是mosfet的情况下,控制电极4是栅极电极,表面电极5是源极电极,背面电极6是漏极电极。

56.多个半导体元件3的背面电极6与第1导体板1连接。1个中继基板7安装于第2导体板2之上。此外,也可以将多个中继基板7安装于第2导体板2。

57.在半导体元件3的背面电极6和中继基板7的背面设置有接合膜。接合膜例如是通过溅射法形成的层且是从元件侧起由ti/ni/ti/au(或ag)构成的层叠膜,或者是通过镀敷法形成的层且是从元件侧起由nip/pd/au构成的层叠膜。接合膜例如通过使用了银的烧结接合或使用了焊料的扩散接合而与第1导体板1或第2导体板2连接。此外,在进行接合之前的热履历少、向最表面的ni析出少的情况下,也可以从接合膜的结构中省略掉ti或pd。此外,第1导体板1、第2导体板2的材料是铜等金属。

58.半导体元件3是具有栅极焊盘、开尔文源极焊盘、温度感测二极管焊盘、电流感测源极焊盘等多个控制电极4的mosfet。此外,作为控制电极4,也可以根据需要而具有开尔文源极焊盘、温度感测二极管焊盘、电流感测源极焊盘等。

59.中继基板7例如是在由硅构成的基板8之上形成绝缘膜9,在绝缘膜9之上绕引有电路图案的配线用元件。中继基板7具有多个第1中继焊盘10和通过内部配线而与多个第1中继焊盘10连接的第2中继焊盘11作为电路图案。内部配线例如是在中继基板7的绝缘膜9之上图案化形成的铝配线。

60.多个半导体元件3的控制电极4与多个第1中继焊盘10分别通过多个金属导线12而连接。金属导线12例如是由金或银构成的细导线,其直径小于或等于100μmφ。此外,能够通过使用直径小于或等于50μmφ的导线而降低环路高度,抑制树脂厚度。

61.第1导体块13与多个半导体元件3的表面电极5连接。第2导体块14与第2中继焊盘11连接。第1导体块13及第2导体块14是金属制的块,例如是由铜构成的块。第1导体块13及第2导体块14例如通过使用了银的烧结接合或使用了焊料的扩散接合而分别与表面电极5及第2中继焊盘11连接。此外,为了吸收第2导体块14的尺寸公差、接合时的公差,第2中继焊盘11也可以比第1中继焊盘10大。

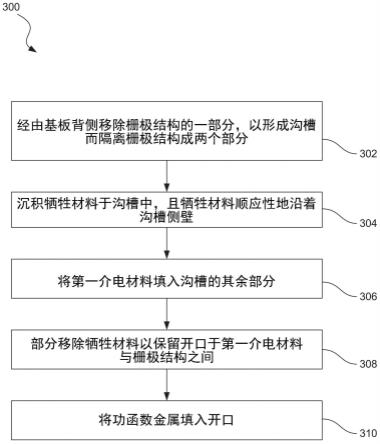

62.如果表面电极5是在铝配线之上进一步形成有接合膜的电极,则能够提高与第1导体块13之间的接合性。另外,通过在中继基板7的第1及第2中继焊盘10、11的一部分进一步

形成接合膜,从而能够分别提高与金属导线12及第2导体块14之间的连接性。接合膜例如是通过溅射法形成的层且是从元件侧起由ti/ni/ti/au(或ag)构成的层叠膜,或者是通过镀敷法形成的层且是从元件侧起由nip/pd/au构成的层叠膜。

63.封装材料15将第1及第2导体板1、2、多个半导体元件3、中继基板7、金属导线12、第1及第2导体块13、14封装。封装材料15具有彼此相对的第1主面s1及第2主面s2、侧面s3。第1导体板1从第1主面s1露出。第2导体板2不从第1主面s1露出而是从侧面s3露出。第2导体板2也可以从第2主面s2露出。第1及第2导体块13、14从第2主面s2露出。经由从封装材料15露出的第1及第2导体块13、14而进行装置外部与装置内部的电气信号的交换。此外,图3是表示实施方式1涉及的半导体装置的变形例的内部的俯视图。通过设为第1导体板1的一部分1a从封装材料15凸出的端子形状,从而能够用作漏极感测端子。漏极感测端子对漏极电压进行监视输出,因此,例如通过在装置外部设置保护电路,从而作为过电流检测功能之一,对半导体元件3的接通时漏极-源极间的电压进行监视,对不饱和(短路等的过电流)进行检测。

64.半导体元件3和中继基板7被封装材料15封装,第1导体板1与第2导体板2通过封装材料15而绝缘。此外,封装材料15只要是具有绝缘性的材料即可,不特别限定,例如是环氧树脂。在第2导体板2的下方,在封装材料15的第1主面s1设置有凹陷部16。

65.接下来,对实施方式1涉及的半导体装置的制造方法进行说明。图4、6、8、10、12、14、16、18、20是表示实施方式1涉及的半导体装置的制造工序的俯视图。图5、7、9、11、13、15、17、19、21是表示实施方式1涉及的半导体装置的制造工序的剖视图。

66.首先,如图4及图5所示,准备与外部的框架17一体化并且彼此分离的第1导体板1和第2导体板2。接下来,如图6及图7所示,为了在第1导体板1连接多个半导体元件3,将多个半导体元件3的背面电极6通过银或焊料等而连接至第1导体板1。在第2导体板2也同样地连接中继基板7。此外,连接方法的说明是重复的,因此省略。

67.接下来,如图8及图9所示,在多个半导体元件3的表面电极5连接第1导体块13。在第2中继焊盘11连接第2导体块14。

68.接下来,如图10及图11所示,将多个半导体元件3的控制电极4与多个第1中继焊盘10分别通过多个金属导线12而连接。这样,在将第1及第2导体块13、14连接之后通过金属导线12而进行连接,由此在第1及第2导体块13、14的连接时与金属导线12之间的干涉的可能性消失。因此,所使用的夹具的自由度扩大,因此,能够容易地进行将第1及第2导体块13、14连接的工序。此外,也可以在将第1及第2导体块13、14连接之前进行通过金属导线12而连接的工序。通过先进行通过金属导线12来连接的工序,由此,进行导线键合的导线键合工具的可动区域扩大,因此导线键合控制提高。

69.接下来,如图12及图13所示,通过封装材料15将第1及第2导体板1、2、多个半导体元件3、中继基板7、金属导线12、第1及第2导体块13、14封装。此时,使第1导体板1从第1主面s1露出,使第2导体板2不从第1主面s1露出。

70.接下来,如图14及图15所示,对封装材料15的第2主面s2进行磨削,使第1及第2导体块13、14从第2主面s2露出。接下来,如图16及图17所示,将成为一体部件的外部的框架17与第2导体板2的连接部切断而使它们彼此分离。此外,在切断时使切断刀具以比刀具宽度大的间隔的量与封装材料15分离。由此,在切断时不会损伤封装材料15,生产率提高。

71.接下来,如图18及图19所示,第1导体块13将成为源极电位的漏极电压施加于第1导体板1,向第2导体块14施加栅极信号,实施用于排除不合格品的半导体装置的筛选试验。最后,如图20及图21所示,将外部的框架17与第1导体板1的连接部切断而使它们彼此分离。此外,在切断时使切断刀具以比刀具宽度大的间隔的量与封装材料15分离。由此,在切断时不会损伤封装材料15,生产率提高。

72.图22是表示使用了多个实施方式1涉及的半导体装置的功率模块的俯视图。第1半导体装置18及第2半导体装置19是上述的半导体装置。第1半导体装置18的第1导体板1通过焊料或烧结材料等接合材料而与第1电路图案20连接。第1半导体装置18的第1导体块13通过配线21而与第2电路图案22连接。第2半导体装置19的第1导体板1通过接合材料而与第2电路图案22连接。第2半导体装置19的第1导体块13通过配线23而与第3电路图案24连接。这样,将第1半导体装置18及第2半导体装置19分别用于上桥臂和下桥臂而构成半桥电路。此外,配线21、23可以是将由铝或铜构成的导线或条带进行超声波接合后的配线,也可以是将由铜构成的框架通过焊料或烧结材料等接合材料而连接后的配线。

73.凝胶或环氧树脂等周边封装材料30将第1及第2半导体装置18、19、第1、第2及第3电路图案20、22、24封装而实现与外部之间的绝缘。周边封装材料30将电路图案间绝缘,同时将第1半导体装置18及第2半导体装置19的从封装材料15的侧面露出的第2导体板2的露出面与第2及第3电路图案22、24各自绝缘。并且,与第2半导体装置19的第2导体板2的露出面相对地在第2电路图案22设置有切口部25。由此,能够使源极电位的第2导体板2与漏极电位的第2电路图案22的绝缘距离变长。同样地,与第1半导体装置18的第2导体板2的露出面相对地在第3电路图案24设置有切口部25。此外,优选切口部25具有容许周边封装材料30进入的大小。

74.如以上所说明的那样,在本实施方式中,使安装有多个半导体元件3的第1导体板1与安装有中继基板7的第2导体板2分离地被封装材料15封装。并且,第1导体板1从封装材料15的第1主面s1露出,但第2导体板2不从封装材料15的第1主面s1露出。由此,能够将第1导体板1与第2导体板2绝缘,因而能够容易地提高绝缘耐量。

75.另外,使多个半导体元件3的控制电极4通过中继基板7而并联连接。半导体元件3的背面电极6是漏极电极,表面电极5是源极电极。由此,半导体装置整体等价于将第2导体块14设为栅极电极、将第1导体块13设为源极电极、将第1导体板1设为漏极电极的1个mosfet。由此,能够实现由半导体装置的组装性提高带来的成本降低和半导体装置的小型化。

76.另外,在将半导体装置与绝缘基板的电路图案连接的情况下,向第1导体板1施加电路图案的高电位。另一方面,向第2导体板2施加中继基板7的下表面的低电位。因此,在第2导体板2的下方,在封装材料15的第1主面s1设置有凹陷部16。由此,能够延长第1导体板1的露出部位与第2导体板2的露出部位之间的沿面距离,因此,能够进一步提高绝缘耐量。但是,也可以没有凹陷部16。

77.另外,在通过封装材料15进行封装之前,第1导体板1和第2导体板2与外部的框架17一体化。因此,第1导体板1和第2导体板2在完成封装之前是一体部件。在通过封装材料15进行封装之后,将第1导体板1和第2导体板2从框架17切断。由此,半导体装置的制造变得容易。另外,能够一次制造出多个半导体装置,因而能够降低制造成本。并且,通过与外部的框

架17一体化,从而第1导体板1和第2导体板2的位置控制变得容易,能够容易地确保绝缘性,因此,能够提高半导体装置的成品率。

78.另外,在将第2导体板2切断之后、将第1导体板1切断之前,实施用于排除不合格品的半导体装置的筛选试验。通过在将第1导体板1切断之前实施筛选试验,从而能够同时连接多个半导体装置的漏极电位,因此,能够高效地实施筛选试验。另外,与多个半导体装置的源极电极及控制电极对应的第1及第2导体块13、14的位置精度变高,因而能够容易地取得电位。其结果,能够同时实施多个半导体装置的筛选试验,能够抑制半导体装置的制造成本。

79.实施方式2

80.图23是表示实施方式2涉及的半导体装置的内部的俯视图。在封装材料15设置有切口部26。切口部26配置于分离的第1导体板1与第2导体板2之间。在切口部26处第1导体板1和第2导体板2的切断面露出,但在构成功率模块时,通过将半导体装置由周边封装材料30覆盖,从而能够提高第1导体板1与第2导体板2的绝缘性。

81.接下来,对实施方式2涉及的半导体装置的制造方法进行说明。图24、26、28、30、32、34、36、38、40是表示实施方式2涉及的半导体装置的制造工序的俯视图。图25、27、29、31、33、35、37、39、41是表示实施方式2涉及的半导体装置的制造工序的剖视图。

82.首先,如图24及图25所示,准备与外部的框架17一体化并且通过架桥部27而彼此连接的第1导体板1和第2导体板2。接下来,如图26及图27所示,为了在第1导体板1连接多个半导体元件3,将多个半导体元件3的背面电极6通过银或焊料等而连接至第1导体板1。在第2导体板2也同样地连接中继基板7。

83.接下来,如图28及图29所示,在多个半导体元件3的表面电极5连接第1导体块13。在第2中继焊盘11连接第2导体块14。

84.接下来,如图30及图31所示,将多个半导体元件3的控制电极4与多个第1中继焊盘10分别通过多个金属导线12而连接。

85.接下来,如图32及图33所示,通过封装材料15将第1及第2导体板1、2、多个半导体元件3、中继基板7、金属导线12、第1及第2导体块14封装。此时,在封装材料15设置使架桥部27露出的切口部26。

86.接下来,如图34及图35所示,对封装材料15的第2主面s2进行磨削,使第1及第2导体块13、14从第2主面s2露出。接下来,如图36及图37所示,将在切口部26处露出的架桥部27切断,使第1导体板1与第2导体板2彼此分离。

87.接下来,如图38及图39所示,第1导体块13与源极电极即表面电极5电连接,第1导体板1与漏极电极即背面电极6电连接。另外,第2导体块14与栅极电极即控制电极4电连接。通过在第1导体块13与第1导体板1之间施加电压,从而在源极电极与漏极电极之间施加电压,通过对第2导体块14施加电压,从而对栅极电极施加电压,实施用于排除不合格品的半导体装置的筛选试验。此时,也可以通过在切口部26处夹入绝缘板等,从而确保第1导体板1与第2导体板2的绝缘性。最后,如图40及图41所示,将外部的框架17与第1导体板1的连接部切断而使它们彼此分离。

88.如以上所说明的那样,在本实施方式中,第2导体板2并非是通过外部的框架17而是通过架桥部27与第1导体板1连接。因此,第1导体板1与第2导体板2的固定变得更牢固,由

导线接合时的按压力导致的第2导体板2的挠曲受到抑制,因此成品率提高。

89.另外,在导线的材料是au的情况下等,有时材料被加温。通过架桥部27而将第1导体板1与第2导体板2连接,由此能够使两者均热化,因而导线键合的接合性提高。

90.实施方式3

91.图42是表示实施方式3涉及的半导体装置的内部的俯视图。图43是沿图42的i-ii的剖视图。在第2导体板2连接有源极导体块28。多个半导体元件3的源极焊盘29通过导线31而与第2导体板2连接。中继基板7的第1中继焊盘10及第2中继焊盘11通过绝缘膜9而与第2导体板2及源极导体块28绝缘。此外,源极导体块28也可以是多个。

92.源极导体块28从封装材料15的第2主面s2露出,作为源极控制电极而起作用。由此,能够将第2导体板2固定于源极电位,因此,能够使浮置的部分消失。因此,在半导体装置高速地通断,电压急剧地振动时,也能够防止意料外的电压破坏。此外,也可以取代源极导体块28而将第2导体板2的露出部位用作源极控制电极。在这种情况下,也可以以在作为源极控制电极来说适当的位置露出的方式而使第2导体板2的一部分变形。另外,能够削减中继基板7处的源极焊盘及其绕引配线,因此,还能够缩小中继基板7的尺寸。

93.此外,半导体元件3不限于由硅形成,也可以由与硅相比带隙大的宽带隙半导体形成。宽带隙半导体例如是碳化硅、氮化镓类材料或金刚石。由这样的宽带隙半导体形成的半导体元件由于耐电压性、容许电流密度高,因此能够小型化。通过使用该小型化的半导体元件,从而组装了该半导体元件的半导体装置也能够小型化、高集成化。另外,由于半导体元件的耐热性高,因此能够使散热器的散热鳍片小型化,能够使水冷部空冷化,因而能够使半导体装置进一步小型化。另外,由于半导体元件的电力损耗低且高效,因此能够使半导体装置高效化。

94.标号的说明

95.1第1导体板,2第2导体板,3半导体元件,6背面电极,7中继基板,10第1中继焊盘,11第2中继焊盘,12金属导线,13第1导体块,14第2导体块,15封装材料,16凹陷部,17框架,20第1电路图案,22第2电路图案,24第3电路图案,25、26切口部,27架桥部,28源极导体块,30周边封装材料,s1第1主面,s2第2主面。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。