包括单片集成的光电二极管和跨阻放大器的光接收器

相关申请的交叉引用

1.本技术要求2019年12月19日提交的美国临时专利申请第62/950,479号的优先权,所述美国临时专利申请以引用的方式并入本文中。

技术领域

2.本发明涉及包括光电二极管检测器和跨阻放大器(tia)的光接收器,用于千兆位无源光网络(gpon)等应用。

背景技术:

3.无源光网络(pon)是点到多点、光纤到户的网络架构。pon网络使用无源分路器和合路器来分配光信号,而不需要诸如光放大器之类的有源元件。服务提供商中心局的光线路终端(olt)与每个用户驻地的光网络单元(onu)通信。onu包括用于将接收到的光信号转换成电输出的光接收器。

4.例如,万兆无源光网络可称为10g-pon或xg-pon。建议itu-t g.987是定义所述接入网络标准的一系列文件。通过波分复用(wdm),在同一根光纤上同时进行上行和下行飞越成为可能。这种技术允许一个pon波长传输用于上行,另一个用于下行。比如10g-pon下行用1577nm,上行用1270nm。

5.onu的光学接收器包括光电二极管检测器和跨阻放大器。光接收器的性能取决于几个因素,例如:

·

光电二极管的光学和电气性能,如响应度、载流子飞越时间和rc电气特性;

·

跨阻放大器半导体性能,如增益、噪声、过载和带宽;

·

混合集成寄生效应和封装寄生效应,如串联输入电感和杂散电容。

6.光电二极管技术对接收器的灵敏度和带宽性能设置了物理限制。tia技术和设计方法的选择极大地决定了接收机的整体性能。

7.对于10g pon,1577nm的光接收器通常使用雪崩光电二极管(apd)和跨阻抗放大器(tia)的混合布置,即分立元件。目前,在1577nm波长范围内发射的商用半导体激光器具有有限的输出功率,且ingaas针状光电二极管(针状pd)不具有足够的灵敏度来用作1577nm(1575-1581nm)的onu光学检测器。因此,有必要使用更昂贵的apd来获得所需的性能,例如响应度和灵敏度。除了成本较高之外,apd的其它缺点是需要高电压电源、控制回路的额外电路、较长寿命下的可靠性差或有限的工作寿命。

8.接收器灵敏度定义为接收器实现目标误码率(ber)所需的信号光功率。对于10g pon,根据itu-t g.987,为实现10-3或更好的ber,所需的-28.5dbm灵敏度是现有ingaas垂直针状光电二极管无法达到的。apd可以超过分立针状pd的灵敏度,例如3到5db,使得apd对于这种应用具有足够的灵敏度。

9.另一方面,包括混合集成的光电二极管(pd或apd)和tia的光接收器的性能受到寄生效应的限制,例如焊盘电容、引线接合的电感以及apd和tia之间互连的阻抗匹配需求。随

着数据速率从10gb/s增加到25gb/s和50gb/s以及更高,这些问题尤其令人担忧。

10.因此,需要包括用于10g-pon和下一代pon的光电二极管检测器的光接收器,例如,用于onu的1577nm光电二极管检测器,或用于olt的1270nm光电二极管检测器,其提供一种或多种性能改进、成本降低或替代解决方案,以取代常规混合apd-tia模块。

技术实现要素:

11.本发明旨在消除或减轻包含混合光电二极管检测器和tia的已知装置和系统的一个或多个上述缺点,或至少提供一种替代方案。

12.本发明的各方面提供了包括单片集成的光电二极管和跨阻放大器的光接收器,以及优化单片集成的光电二极管和跨阻放大器性能的方法,以满足性能规范,例如下一代pon的性能规范。

13.一方面,光接收器包括单片集成的光电二极管(pd)和跨阻放大器(tia),其中:tia包括由生长在si(半绝缘)inp衬底上的外延层堆叠的第一多个层形成的inp异质结双极晶体管(hbt);pd包括由外延层堆叠的第二多个半导体层形成的针状二极管(pin),所述外延层堆叠包括n层、i层和p层;pin二极管的p型触点通过导电迹线直接互连到tia的输入,以减小pin的装置电容c

pin

,tia的输入电容是c

tia

;和选择包括以下值的装置参数:c

pin

、c

tia

、pin的面积a或窗口直径pin的i层的厚度ti以及tia的跨阻抗反馈电阻rf,以提供满足性能规范的集成pin-tia,所述性能规范包括在工作波长下的指定灵敏度和响应度。

14.例如,通过优化过程选择所述装置参数,以提供满足所述所需性能规格的集成pin-tia,例如,灵敏度、响应度、带宽、跨阻增益等。在一些实施例中,c

pin

与c

tia

匹配。

15.在示例实施例中,例如对于10g pon的工作波长,pin的i层(即吸收层)包括ingaas。在其它实施例中,代替包括i层ingaas的pin,可以使用与inp晶格匹配的ingaalasppenternary系统内的其它吸收材料。i层或吸收层可以包括单层或多层结构。n层和p层可以是n掺杂的inp和p掺杂的inp,或者任何其它合适的晶格匹配的半导体材料。n层和p层中的每一个也可以包括单层或多层结构。

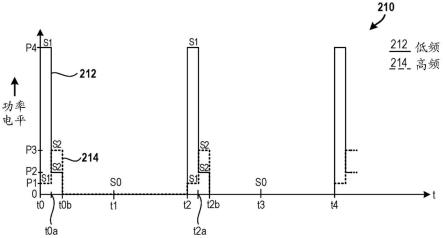

16.值得注意的是,当pin二极管通过光刻定义的导电迹线与tia的输入直接互连时,消除了pd和tia混合集成所需的焊盘和焊线的寄生电容和电感。此外,pin二极管和tia之间的光刻定义的互连迹线提供了更明确和可再现的互连,这避免了混合部件的引线接合互连的可变性和不一致性问题。

17.例如,使用所述设计方法,可制造单片集成pin-tia,其灵敏度和响应度满足10g pon接收器的性能规格,10g pon的光网络单元(onu)的1577nm接收器或光线路终端(olt)的1270nm接收器。ingaas pin非常适合在这些波长下工作。也就是说,单片集成的ingaas pin-tia可以被配置为具有例如好于-28dbm或好于-30dbm的灵敏度和响应度,即,与用于1577nm onu接收器的传统混合apd-tia相当。在最初的原型中,在1550nm处获得了~0.7a/w的响应度。如本文所述,通过进一步优化pin-tia参数,预期例如在1577nm,可以实现例如≥0.8a/w或≥0.9a/w或≥1.0a/w的响应度,即接近1.28a/w的量子效率极限。

18.在一些实施例中,通过包括镜面(即,光反射器)来提高量子效率(qe),即,产生穿过厚度ti的双通道。第一层。例如,镜面包括交替的高折射率(例如半导体)和低折射率(例

如电介质)晶格匹配材料的多层四分之一波长堆叠,以产生通过i层的双通道,实际上在i层中提供两倍于ti的吸收长度。镜面的n层充当pin的n层。在一些实施例中,量子效率可以≥85%或≥90%。

19.在一些实施例中,为减少光学损失,窗口或孔径包括针对工作波长优化的抗反射涂层,且p 盖层选择为在工作波长下基本透明,例如,p 盖层制得较薄,并由减少光学损失的材料制成,而不是最小化p型触点的薄层电阻和触点电阻。

20.在包括用于在1577nm下操作的单片集成pin-tia的光接收器的示例实施例中,hbt的特征在于f

t

≥100ghz,tia具有7.5ghz的带宽(bw),c

pin

≤50ff,c

tia

≤50ff,rf=1500ω。在另一个实施例中,已经实现了14£f的c

pin

。有益的是,为了增加灵敏度,组合电容(c

pin

c

tia

)被最小化,且c

tia

被设计为接近c

pin

,或者匹配c

pin

。例如,为了提高灵敏度,如果可以通过设计pin来充分降低c

pin

,则可能希望对tia使用较短的栅极长度inp hbts,即为了降低c

tia

。另一方面,如果减小c

pin

是一个限制因素,那么选择与c

pin

匹配的c

tia

并使用较低成本的制造就足够了,即单片集成pin-tia可以使用更便宜、更大栅极长度的技术来实现,用于制造tia的inp hbt电路。例如,如果cpin约为50ff或30ff,则可以选择c

tia

与c

pin

匹配。如果c

pin

降低到≤30ff或≤15ff,则可以使用较小的栅极宽度hbt来降低c

tia

。

21.在一些实施例中,用于10g无源光网络(pon)的olt(光线路终端)或onu(光网络单元)的光接收器包括:单片集成的光电二极管(pd)和跨阻放大器(tia),其中:tia包括由生长在si(半绝缘)inp衬底上的外延层堆叠的第一多个层形成的inp(磷化铟)异质结双极晶体管(hbt);pd包括由外延层堆叠的第二多个半导体层形成的针状二极管(pin),所述外延层堆叠包括n层、i层和p层;pin二极管的p型触点通过导电迹线直接互连到tia的输入端;和i层包括为olt或onu的工作波长选择的吸收材料。

22.对于onu的光接收器,i层包括单层或多层结构,包含在1577nm吸收的材料。对于olt的光接收器,i层包括单层或多层结构,包括在1270nm吸收的材料。例如,i层选自包括ingaas和ingaalasp材料系统的其它吸收材料的组,其与inp晶格匹配。在pin具有圆形几何形状的情况下,即对于垂直入射,pin可以包括在i层下面的镜面(光反射器),以创建穿过i层的双通道。

23.尽管单片集成的pin-tia的示例性实施例是参考使用ingaas pin和用inp hbts制造的tia电路的实施方式进行描述的,但设计方法可延伸至使用ingaas/inp工艺技术实施的其它形式的pd,例如,其中pd为apd或波导pin(侧面窗口)而非垂直pin(顶部面窗口)。后者的设计参数可以被优化,以提供满足10gpon的onu或olt的光接收器的性能规范的集成pd-tia,或者用于需要高数据速率光检测器的其它应用。

24.例如,其它应用可包括5g和数据库技术,尽管操作波长可能与pon略有不同。

25.更一般地,本发明的另一方面提供了一种光学接收器,包括单片集成的光电二极管(pd)和跨阻抗放大器(tia),其中:tia包括异质结双极晶体管(hbt),其由形成在衬底上的外延层堆叠的第一多个层形成;

pd由外延层堆叠的第二多个半导体层形成;pd的p型触点通过导电迹线直接互连到tia的输入端,以提供pd的电容c

pd

和tia的电容c

tia

;和选择装置参数,包括:所述c

tia

和c

pd

;pd的吸收层的厚度ti;窗口直径或pin的面积a;和tia的跨阻抗反馈电阻rf,以提供满足装置规格的集成pd-tia,包括在工作波长下的特定灵敏度和响应度。

26.例如,pd可为以下之一:针状pd;雪崩式pd;波导针状pd;具有行波几何形状的波导针状pd;单向载流子(utc)pd、谐振增强腔pd;sagcm apd超晶格apd和其它合适类型的光电二极管。

27.在适当的情况下,pd可包括镜面(光反射器),其经配置以产生穿过吸收层的双通道,例如交替的高折射率和低折射率晶格匹配材料的多层四分之一波长堆叠。例如,装置参数包括多层四分之一波长堆叠的镜面厚度tm和吸收层的厚度ti,其中选择ti和tm以获得所需的量子效率,例如≥85%或≥90%

28.对于改进的性能,c

pin

和c

tia

的值提供至少一个:a)c

pin

与c

tia

匹配;b)c

pin

大约相当于c

tia

;以及c)最小组合电容(c

pin

c

tia

)。

29.在示例实施例中,对单片集成pd-tia的装置参数进行了优化,以提供满足高速数据应用接收器性能规格的特定灵敏度和响应度,例如10g pon的光网络单元(onu)接收器或10g pon的光线路终端(olt)接收器。

30.示例实施例的单片集成pin-tia和pin-pd的元件可与其它实施例的元件相结合,如适用。例如,其它实施例的单片集成pin-tia和pd-tia可以包括这里公开的各个特征的任何可行组合。

31.本发明的另一方面提供了一种装置结构的制造方法,包括本文公开的用于光接收器的单片集成pin-tia和pd-tia。

32.本发明的前述及其它目的、特征、方面和优点将从以下本发明一些实施例的详细说明中变得更加明显,所述说明仅作为示例。

附图说明

33.图1(现有技术)显示了包括混合光电二极管检测器pd和tia的光接收器的示意性功能框图;

34.图2显示了市售ingaas针状pd示例的两个视图;

35.图3显示了不同装置面积的针状pd的装置电容与装置面积的示例图;

36.图4显示了穿过示例ingaas针状pd的层的示意性横截面图,以显示包括窗口直径φ和i层厚度ti的设计参数;

37.图5a显示了示例性实施例的单片集成pin-tia的示意性拓扑视图(俯视图);

38.图5b显示了用于制造示例性实施例的单片集成pin和tia的外延层结构的横截面示意图;

39.图6a显示了单片集成pin-tia的pin的简化等效电路示意图,图6b为列出一些参数的表格;

40.图7a显示了说明灵敏度对pin装置电容c

pin

和tia电容c

tia

的依赖性的示意图;

41.图7b显示了说明pin装置电容c

pin

和响应度(a/w)与i层厚度ti的相关性的示意图;

42.图8列出了显示装置参数之间关系的一些方程;

43.图9显示了说明量子效率对i层厚度ti的依赖性的示意图;

44.图10显示了基于简化模型的计算数据图,对于具有三种不同孔径的混合pd-tia(分立)和集成pin-tia(集成),对于-3db带宽f_-3db(ghz)具有i层厚度ti(μm)(在图中标为t_ingaas(um))的函数;

45.图11显示了说明噪声对tia反馈电阻rf的依赖性的示意图;

46.图12显示了说明噪声对pin的组合装置电容和tia(c

pin

c

tia

)电容的依赖性的示意图;

47.图13显示了pin和tia的简化等效电路示意图,以说明示例实施例的单片集成pin-tia设计的关键参数;

48.图14为示例实施例的单片集成pin-tia的示例装置规格表;

49.图15显示了示例性实施例的单片集成pin-tia的电路设计示意图;

50.图16显示了示例性实施例的单片集成pin-tia的简化等效电路图,显示了tia的pin和第一晶体管q1的装置参数;

51.图17显示了第一实施例的集成pin-tia的简化横截面示意图,以说明pin和tia的直接互连;

52.图18显示了第二实施例的集成pin-tia的简化横截面示意图,包括多层反射器(镜面);

53.图19显示了模拟数据图,以说明包括图18中示意性说明的反射器的效果;

54.图20显示了过去50年中晶体管栅极长度(nm)的摩尔定律图;和

55.图21显示了例如半导体材料的吸收系数对波长的曲线图。

具体实施方式

56.图1显示了光接收器的示意性功能框图,所述光接收器包括封装衬底12的混合组件10、包括光电二极管(pd)22的光电二极管芯片20和包括具有反馈电阻器rf的tia 32的tia芯片30,以及分立后置放大器36。光电二极管芯片20通过引线接合互连38与tia芯片30互连,以将光电流ipd馈送到tia322,从而产生输出电压v

out

。光电二极管pd可以是apd、针状pd(pin)或其它类型的光电二极管,具体取决于所需的性能规格。通常,对于gpon和10gpon,为了提供所需的灵敏度,例如优于-28.5dbm,光电二极管是apd。如背景技术部分中所述,希望用具有相当性能和灵敏度的较低成本单片集成pin-tia来代替混合apd-tia。

57.混合pin-tia光接收器的传统引线接合互连增加了显著的寄生效应,限制了pin-tia的性能。特别是,接合焊盘增加电容,接合线增加电感。还应当理解,混合元件的引线接合互连的一致性往往取决于所使用的封装类型,且在实践中,可以预期各个光接收器单元的引线接合互连会有一些可变性或不一致性。引线接合中的这些可变性或不一致性导致混合pin-tia的寄生电容和电感的相应可变性或不一致性。

58.公开了本发明实施例的单片集成pin-tia,其为10g-pon提供了传统混合apd-tia的替代方案,至少具有相当的性能,且相对于其它混合pd-tia,潜在地提供了性能改进和/或成本降低。

59.图2显示了包括56gb/s ingaaspin22(gcs do480_16um_c3)的光电二极管芯片20

的示例俯视图a和侧视图b,其适用于在1577nm下工作的高速光学接收器。所述装置具有直径为16μm的光学窗口24,且据报道当以优化的tia操作时,具有36-40ghz 3db带宽。在pin和tia的传统混合布置中,例如如图1所示,需要两个接合焊盘,即n焊盘26和p焊盘28,例如75μm 50ω焊盘,以通过线接合将pd连接到tia。pd的两个焊盘都会增加电容,这可能占装置总电容的很大一部分。产品数据手册显示装置电容范围为65nf至80nf。

60.以不同区域的ingaas pin装置为例,其具有公开可用的数据表,并根据数据表上的信息反向工作,估计焊盘的寄生电容约占总装置电容的一半。如图3中电容c(pf)对装置面积(μm2)的曲线图示意性所示,通过基于不同装置面积的装置的典型电容和最大电容数据外推到零装置面积,得出所述估计值。

61.图4显示了ingaas pin装置结构100的横截面示意图,显示了包括形成在半绝缘(si)磷化铟(inp)衬底102上的n层112、i层114和p层116的p-i-n层结构110。i层具有厚度ti。环形p型触点122形成在p层上,具有直径为的光学孔径或窗口124。接合焊盘包括p型触点焊盘126和n触点焊盘128。环形p型触点122延伸到p型触点焊盘128。n层112形成在n触点层127上,n触点层127例如通过穿过电介质层104的导电通路与n触点焊盘126互连。p-i-n结本身的电容cpin对于装置工作是必要的。对于给定的装置孔径窗口直径o,如果结电容为零,则飞越时间将为无穷大,带宽将为零。需要有限的结电容来平衡rc和载流子飞越时间。然而,焊盘电容没有增加任何有用的功能,理想情况下,焊盘电容为零。

62.通过设计,pin和tia的单片集成消除了焊盘电容和焊线电感。例如,可以将ingaaspin与使用inp异质结双极晶体管(hbt)制造的tia集成在一起。这意味着从pin的输出到tia的输入存在直接的片内互连,即光刻定义的导电迹线。优选地,pin和tia之间的导电迹线提供了短、低电阻、低电感的互连,消除了阻抗匹配的需要。因此,所述pin的一个50ω焊盘被取消,因为所述pin与tia之间存在直接互连,而不是线焊连接。由于在pin和tia之间提供直接互连的导电迹线是光刻定义的,即使用一个或多个互连金属化层,因此对于晶片上的每个pin-tia,以及从晶片到晶片,以及从批次到批次,pin-tia互连被更可重复地和一致地定义。

63.示例性实施例200的单片集成pin-tia的示意性装置拓扑(俯视图)如图5a所示。单片集成的pin-tia芯片210包括pin装置结构220和tia电路230。在pin220的p型触点和tia电路之间有直接的片上互连240。图5b中示出了包括衬底202的单片集成pin-tia芯片210的示意性截面图,以示出用于tia的hbt外延层204和覆盖外延层206的单片集成,以形成图5b中示出的pin。尽管pin的另一端耦合到焊盘(即接地焊盘),但所述焊盘的电容实际上与装置工作去耦。由于pin的输出通过提供直接片上互连的导电迹线直接耦合到tia的第一级放大器,实际上,pin的焊盘电容不计入装置操作。这有多种有益的结果。

64.据估计,消除这些寄生电容将使rc限制带宽扩展约2倍。pin和tia的单片集成消除了连接到tia的pin端子的焊盘,这消除了两个焊盘中的一个,即焊盘电容减半。参考图6a所示的等效电路图,pin被建模为装置电流源ipd和装置电容c

pin

,焊盘电容c

pad

与引线接合电感l

bondwire

串联。所述电路的效果受lc限制。对于25ghz lc限值(f=1/2π(lc)

1/2

),所述限值约为2nh(见图6b中的表格)。长度为1毫米的典型金线焊的电感在10ghz或25ghz时约为0.8nh(即0.8nh/mm)。因此,出于所有实际目的,所述lc限值远远超出所述应用的任何重要电路考虑,最高可达25ghz。在50ghz下,需要管理电感,例如,通过使用多线接合、低电感导

电互连走线或设计用于降低电感的其它技术。通过消除pin与tia之间的线接合连接,剩余焊盘的焊盘电感是具有两个焊盘的混合布置的电感的一半。pin-tia的单片集成降低了寄生装置的电容和电感。

65.例如,更一般地,假设单个接合焊盘的电容约为15ff,25ghz的电感峰值在2.7ghz,假设接合线短于3mm左右,谐振将在高于25ghz的带宽,对于10ghz是无关紧要的。

66.pdpin的频率响应主要受rc和过渡时间的限制,即相关响应时间的平方和。如果pin电容c

pin

减半,这给出了更高的带宽,或者对于原始带宽,增加针状pd的i层厚度ti的额外自由度是可用的。虽然较厚的i层增加了载流子的飞越时间,这通常是不希望的,但是较低的装置电容c

pin

允许折衷,因为较厚的i层增加了响应度,这是有益的。对于给定的带宽,这种折衷允许圆形几何形状(即,垂直入射)pin具有比其它情况更高的响应度。

67.图7a、图7b和图9至图12显示了装置参数的相互依赖性的一些示意图。如图7a的曲线图示意性所示,可以通过减小pin的电容和tia的电容来提高pin-tia灵敏度。例如,参考图8所示的方程式,如图7b所示的曲线图中示意性示出的,pin的电容随着ti的厚度而减小,且a/w中的响应度随着厚度ti而增大,pin的量子效率也随着对(1-γti)的指数依赖性而增大,如图9中示意性示出的。

68.为了提供改进的性能,首先,通过单片集成降低有效装置电容(c

pin

c

tia

),即,通过移除结合垫并在pin和tia之间提供直接互连;第二,装置厚度t1增加。如图10中所示的数据所示,改善了pin相对于装置厚度的总体3db包络。这些组合效应为给定直径的pin提供了改善的带宽。

69.3db带宽(f_3db)由飞越时间受限响应和rc响应的平方和给出。图10中所示的曲线是针对一般的针状pd结构,具有关于接合焊盘电容(大约30ff)、环形接触面积(3μm用于所述计算)、空穴和电子速度的文献值(其是近似值,可能在20%以内)的某些假设,且使用所有空穴和电子源自圆形(即垂直入射)针状光电二极管内的平均吸收位置的近似值。图中引用的直径指的是用于耦合到光纤的开放光学孔径,以及用于环形金属触点的一些额外的周围区域。对于图10中所示的数据,f_3db已经计算了单片集成pin-tia(标为“集成”)和混合pin-tia(标为“分立”)的一些示例,对于直径为20μm、16μm和12μm的针状pd,使用公开可用的数据来推断焊盘电容。

70.飞越限制推导的简化模型

71.在用于飞越限制推导的简化模型中,针对每个ingaas厚度u计算平均吸收位置,且假设两种载流子都源自所述位置。

72.飞越时间受限带宽f

tr

由下式给出:f

tr

*ti=0.443

ꢀꢀꢀ

(1)其中ti是ingaas的本征耗尽层的飞越时间,且假设矩形脉冲单飞越时间近似,导致sinc(x)傅立叶变换分布。设飞越方向为z,ingaas的厚度为zi,速度假定为常数vi。方程式(1)的简单重排给出:方程式(2)也给出了给定频率的飞越时间限制厚度。课堂讲稿和教科书通常假设电子和空穴飞越时间的平方和,但也做大量的数值工作。在这项工作中,假设所有的载流子

都来源于平均吸收位置来计算飞越时间,且对两个飞越时间进行平均,从而得到一个代数上可理解的非常近似的结果。此外,吸收曲线由比尔定律给出为exp(-γz),其中γ是吸收系数。对于通过p-区域进入垂直入射几何形状pd的光,电子的平均吸收位置(穿过p-接触)由下式给出:结果是:因此,空穴的平均吸收由下式给出z

h,avg

=z

i-z

e,avg

ꢀꢀꢀ

(5)

73.这些量通常是用数字计算的。这些封闭形式的近似表达式对于简化计算是有用的。

74.基于这些假设,所述简化模型提供了单片集成pin-tia和混合pin-tia的一些示例的f_-3db带宽的比较。虽然可以采用更复杂的建模方法,但基本物理原理将保持不变。

75.参考图10中的数据,进行了以下观察:

·

对于集成组和离散组,减小直径可改善所有t_ingaas值下的频率响应;

·

对于任何给定的直径,从分立(有焊盘电容)到集成(无焊盘电容)可改善所有t_ingaas值下的频率响应;

·

无论是集成还是分立,任何给定的针状pd直径都有一个最佳(即峰值)带宽;

·

这种优化(峰值)对于集成电路来说更尖锐,因为更高的带宽是可能的,只受装置尺寸的限制;

·

对于足够厚的t_ingaas(ti),减小直径的值正在减小;但对于更大的厚度,集成方法在带宽方面仍有明显的、较小的优势。

76.考虑到这些数据,例如,如果需要更大的带宽,可减小装置厚度,恢复电容以获得改善的飞越时间。或者,如果需要更高的响应度,可以增加装置厚度,恶化飞越时间频率响应,因为电容降低了,所以有一定的余地。如果为了最佳带宽而减薄i-ingaas层,则响应度会降低。为了同时实现增加的带宽和增加的响应度(qe),可以向pd添加镜面或反射器,以允许吸收的光通过两次,即增加ingaasi层的有效厚度,如下所述。

77.其次,由于第一级放大器(tia)可容纳更高的跨阻反馈电阻rf,因此通过pin和tia的单片集成,可提高折合到输入端的噪声(irn)和接收器灵敏度。也就是说,tia噪声与rf成反比,如图11所示。相反,噪声随着pin和tia的组合电容(即c

pin

c

tia

)而增加,如图12所示,例如因为更高的装置电容限制了反馈电阻rf。

78.图13显示了pin和tia的简化等效电路示意图,以说明单片集成pin-tia设计的关键参数,例如,图14中表格所示的示例装置规格。

79.将这两种效应结合在一起,即降低pin装置电容,并增加跨阻反馈电阻器rf的值,从而降低tia噪声,从而提高灵敏度。因此,设计具有改善的灵敏度的pin-tia成为可能,例如在1577nm处优于-28dbm,以满足10g-pon的光接收器的要求。

80.图15为单片集成pin-tia的示例实施例的电路设计示意图,其中tia包括具有第

一、第二和第三hbt、q1、q2和q3的三级放大器,以及跨阻抗反馈电阻器rf。在图16所示的简化等效电路中,pin被示为具有电容cpin的电路等效电流源i

ac

。基于从pin接收的电流i

π

,tia的第一个晶体管q1被建模为电容c

tia

、输入电阻r

π

、电流源βi

π

。图中还显示了基极、发射极和集电极电阻rb、re和rc,以及反馈电阻rf。tia的第二和第三级由放大器1示意性表示。

81.当pd电容和第一级hbt

·

q1的电容均可最小化且彼此相当时,tia第一级的最佳降噪效果出现。原则上,hbt的电容可以通过设计来减小,即掩模组调整来提供更小的栅极长度hbt。但是,在实践中,组合的装置电容c

pin

c

tia

可能受到c

pin

可以减少多少的限制。除非可以相应地降低pd电容,否则降低hbt电容的益处有限;且用于较小栅极长度hbt的设计套件变化的成本和努力可能不值得尝试。在混合pd-tia中,由于接合焊盘寄生效应占主导地位,因此减小pd的装置面积以降低c

pin

的益处有限,因为与具有较小孔径的pd的光纤对准的难度增加了。另一方面,由于pin-tia的单片集成可以显著降低pin装置电容c

pin

,通过选择具有较小孔径的pin,如果克服了光纤对准较小孔径pin的封装后勤问题,则第一级hbt的尺寸可以相应地减小,以降低第一级hbt的电容。这种布置将导致噪声的进一步改善,并因此导致接收器灵敏度的进一步改善。

82.考虑到这些设计原则,在示例实施例的单片集成pin-tia中,pin电容c

pin

为50ff,pin以3.3v的反向偏置电压运行。tia设计为使tia的电容c

tia

与pin电容匹配,即c

tia

也为50ff。假设inp hbt晶体管的ft为100ghz,带宽bw=7.5ghz,tia包括一个三级晶体管放大器,跨阻反馈电阻rf为1500ω,使用图13所示的公式计算。

83.用于提高灵敏度(即,较低值,例如小于-28dbm)和实现指定响应度(例如≥0.7a/w)的集成pin-tia的设计,需要回收所有可能的光子,即,提高pin的量子效率(qe)。对于线焊到tia的分立pin,这是不实际的,因为即使厚度ti增加到无穷大,即增加到飞越时间带宽占主导的程度,焊盘电容也是限制灵敏度的主要因素。另一方面,对于单片集成pin和tia,灵敏度主要取决于pin电容c

pin

,而不是pin的焊盘电容,因此有多种设计选项可以提高pin的qe,例如:a)增加装置厚度u,直到飞越时间占优势,因为焊盘电容不占优势;b)减小装置面积a(例如孔径直径),因为焊盘电容不是主要因素;c)对于给定的波长,插入镜面,例如包括交替的高/低折射率材料的四分之一波长堆叠的反射器,以产生穿过i-ingaas层的厚度ti的双通道,从而在增加qe的同时保持低的飞越时间;

84.图17所示为第一实施例300的集成pin-tia各层的横截面示意图。所述装置结构包括衬底302,例如si:inp,在其上形成用于tia电路和用于pin装置结构的外延层堆叠。外延层堆叠的第一多个半导体层为tia电路330提供了hbt外延层结构304。外延层堆叠的第二多个层形成用于pin 320的pin外延层结构306,包括n触点层327、n层312、i层314、p层316、具有直径的窗口324的环形p型触点322。pin 320的p型触点320通过pin-tia互连340与tia电路互连,pin-tia互连340延伸穿过电介质填充物308。tia电路330形成在衬底的第一区域上,所述第一区域通过隔离沟槽350与其上形成有pin320的衬底的第二区域隔离。例如,包括inp hbts的单片集成ingaas pin和tia可以使用商业上可获得的inp工艺技术来制造。

85.对于10g pon,pin的i层包括ingaas,以在olt的透射波长,即1577nm下提供吸收。pin的n层和p层可以是与ingaas兼容的任何合适的晶格匹配材料。为了减少不必要的吸收,

孔径优选地是在透射波长下基本透明的材料,且可以包括抗反射涂层。

86.制造包括提供外延层结构,其中hbt外延层结构提供在衬底上,具有覆盖的pin外延层结构。也就是说,包括inp hbts的tia电路制造在si inp衬底上,用于hbt的高速操作。ingaas pin由上面的外延层形成,使得pin外延层结构的层的导电性不会降低下面的tia电路的速度和性能。此外,因为形成hbt电子装置的外延层堆叠的hbt外延层不同于形成pin的外延层堆叠的pin外延层,所以每个外延层都可以单独优化。如果需要,可以在hbt外延层和pin外延层之间提供包括一个或多个中间层的隔离物,例如,以提供电隔离,充当蚀刻停止层以便于处理等。如示意性所示,tia电路的区域可以通过电介质填充的沟槽与pin的区域隔离。通过集成用于tia和pin检测器的hbt电子电路,如图所示,hbt外延层堆叠的层和pin外延层堆叠的层可以被独立地构造和优化,以改善装置性能。如果需要,外延层结构的材料可以被选择为与单次外延生长兼容,或者可选地,可以适当地使用多次外延生长。不同的工艺可以用于制造hbt外延层和pin外延层。例如,在实践中,mbe(分子束外延)可用于提供hbt外延层,mocvd(金属有机化学气相沉积)可用于提供pin外延层。可以在hbt外延层和pin外延层之间提供半绝缘隔离物。在其它实施例中,优选为hbts和pin选择与单外延层生长兼容的外延层结构。

87.用于1577nm onu的光接收器的具体设计问题是,1577nm接近ingaas带边缘,在吸收系数已经较低的区域中(见图21)。这个波长的一个吸收长度大约是1.4μm,相比之下,1300nm波长的吸收长度远低于1μm。这意味着量子效率最大化更加困难。然而,因为1577nm更接近ingaas能带边缘,所以高/低折射率晶格匹配的电介质叠层在所述材料系统中具有更大的可能对比度,这意味着制造镜面或反射器变得切实可行,以有效地两次通过i-ingaas层,即有效地使吸收长度加倍。

88.作为示例,图18显示了第二示例实施例的集成pin-tia装置结构400的示意性截面图,包括插入在pin的n触点层427和i-ingaas层414之间的镜面412。例如,镜面412包括交替的高折射率(例如n掺杂半导体)/低折射率四分之一波长晶格匹配层的多层堆叠。多层堆叠的n掺杂材料充当pin的n层。pin和tia的其它层的结构如参考图17所述。与图17的装置结构300相似的装置结构400的元件用相同的附图标记加上100来标记。因此,用于tia电路430的hbt外延层结构404和用于pin 420的pin外延层结构406形成在衬底402上。pin外延层结构包括充当n层、i层414和p层416的多层反射器结构412。具有孔径窗口424的环形p型触点422通过pin-tia互连440,穿过电介质填充物408,连接到tia电路。tia电路430形成在衬底的第一区域上,所述第一区域通过隔离沟槽450与其上形成有pin420的衬底的第二区域隔离。

89.图19所示的图示显示了模拟添加镜面的效果的一些计算结果。起点是从现有的具有圆形台面和正入射(例如,正面进入几何形状)的最先进的56g或28gpin估计的近3db qe损耗。通过增加i-ingaas层的厚度(在图19中标记为t_ingaas(μm)),这变得可行,因为pin的接合焊盘的寄生电容不再降低装置性能,且增加具有镜面厚度(μm)的镜面(沿着图的另一水平轴示出),仿真结果显示,实际上pin可以增益回到1.5到2db之间的某处(参见两次通过的总qe损耗(db)的垂直轴)。

90.因此,这些设计选项中的每一个,单独或组合使用,均可制造包括单片集成pin-tia的光接收器,具有改善的性能,例如,满足10g-pon的1577nm onu光接收器的性能规范。这种设计方法使得用灵敏度和响应度相当的单片集成pin-tia取代传统的混合apd和tia成

为可能。用商业上可获得的inp工艺技术实现的单片集成pin-tia避免了对apd及其高压电源和控制电路的需要,以及相关的成本。

91.由于本文单片集成pin-tia的示例性实施例具有与10g pon应用的常规/商用混合apd和tia相当的灵敏度和响应度,因此单片集成pin-tia可部署在现有光纤网络的1577nm onu的光接收器中,其中olt使用提供标准发射功率(例如dml 9dbm或eml 4dbm)的激光器。当然,使用发射功率更高的激光器将放宽所需的灵敏度规格,从而可以进一步优化用于下一代pon和其它应用的单片集成pin-tia。

92.对于某些应用,可能需要用垂直针状光电二极管代替分立apd,如上所述。将这种设计方法用于使用inp材料技术的apd和tia的单片集成或者基于inp材料技术的波导pin和tia的单片集成也被认为是可行的,且可能对一些高速数据应用有益。也就是说,减小光电探测器电容可以允许优化其它装置参数,从而为由其它类型的ingaas光电探测器覆盖的其它波长提供改进的光接收器性能。具体而言,消除pin和tia互连的焊盘电容允许更高的跨阻反馈电阻rf,以获得更高的tia跨阻增益。

93.在设计tia时,减少电容允许更高的跨阻反馈电阻rf,以增加增益,tia噪声与反馈电阻rf成反比。使tia的电容与pin的装置电容相匹配可能是有益的。由于可以调整许多参数来实现所需的pin-tia性能,因此可能没有必要将pin电容降至最低。关于pin的接地焊盘,使用多个焊盘可能是有益的,例如,两个焊盘将使电容加倍,电感减半,例如,对于接地焊盘使用多个引线接合降低了接合线电感(例如,对于25μm的接合线,大约1nh/mm)。在设计pin时,如果pin的响应度(即a/w)足够高,使得pin中的snr更高,则pin向tia提供更高的输入信号。这意味着即使tia噪声更大(例如,来自较低的rf、较高的电容),集成pin-tia也能提高snr。

94.也就是说,对于这些示例中的每一个,无论光电探测器是垂直ingaas pin、ingaas apd还是ingaas波导pin(例如,侧面光输出),还是其它类型的光电二极管,光电二极管的焊盘电容的消除对提高装置性能具有显著影响,并使光电探测器和tia的其它参数能够被修改或优化,例如提高量子效率和其它参数,以满足诸如10gpon的应用和需要高性能调制方案的其它高数据速率应用所需的灵敏度、响应度等规范。在上述实施例中,pin可以具有直径为例如16μm到20μm的区域(光学窗口)。因为减小针的面积也减小了电容,所以较小直径的针可以与透镜结合使用,以匹配光纤光点的尺寸。

95.使用inp hbts的ingaas pin的单片集成为tia提供了一种解决问题的方案,所述问题不易用包括正入射的硅光子学解决,例如前入射几何结构的锗(ge)pin。在10g pon感兴趣的波长范围内,ge具有比ingaas更低的吸收系数(见图21),且1577nm非常接近ge的带隙,使得同时实现高带宽和高响应度非常困难。在基于阿格的系统中,有必要使用波导针状光电二极管或apd来实现高响应度和高带宽。

96.本文所述的单片集成方法用于降低光电二极管检测器的寄生电容,然后调整pin和tia的其它参数,以提高量子效率,例如满足高数据速率应用的灵敏度和响应度规范,也可扩展至其它类型的光电二极管检测器,例如单一传输载流子(utc)光电二极管装置结构和波导pin几何结构等。

97.pin-tia的单片集成消除了混合集成寄生效应,如焊盘电容、引线接合电阻/电感等。pin-tia的直接互连通过消除焊盘电容提供了较低的电容,并提供了直接(短长度)较低

电感/较低电阻的互连。减小的焊盘电容提供了相关的自由度,从而为给定直径的pin提供了改善的带宽并降低了噪声。

98.可增加吸收层厚度u以提高响应度。在其它条件相同的情况下,集成pin-tia将允许更大的总带宽。

99.可在倍增区下方插入半导体镜,以提高反射率。图19示出了增加吸收率、反射率或两者的益处。图19的计算基于j.brouckaert等人的文章(j.lightwave technology,第25卷,第4期,2007年4月)中公开的公开数据。值得明确指出的是,在1577nm处,与1.3μm或甚至1.50μm相比,半导体镜的折射率对比度可能显著更大。这是因为由于1577nm与大约1650nm的ingaas带隙波长之间的接近性,较低能带隙以及因此较高折射率的半导体可用于较高折射率的透明半导体。所述镜面可用于补充或替换1577nm处损失的(即减少的)qe。如果降低cpin,更薄的t_ingaas(在其它段落中称为ti)可以实现最高带宽,但代价是单通响应度。如本文所述,镜面可以回收大量未被吸收的光。原则上,可以将镜面制造成接近100%反射,尽管这是以处理厚镜面的形貌问题为代价的。然而,标准vcsel处理已经解决了这个问题,标准vcsel处理依赖于相同的原理。另一方面,对于在1577nm下工作的onu接收器的应用,在所述应用中可能的折射率对比意味着可以用更少的层实现接近100%的反射率,并因此具有更小的厚度(即相对于vcsel通常所需的厚度),这是一种工艺设计优势。

100.进一步的设计改进

101.在原型实施例的单片集成pin-tia中,使用ingaas pin和包含inp hbts的tia电路制造,在1550nm处实现0.69a/w的响应度。基于在此描述的设计方法,所述响应度可以通过以下一个或多个来提高:

102.增加的吸收层厚度:对于1557nm的olt应用,在不接近带宽极限的情况下,有增加厚度u的空间。基于结合文献数据和建模的经验数据,将吸收层厚度增加1.5倍多一点应会给出1db的改善。

103.在吸收层或rce下方提供的镜面:如果提供镜面,则我们预计对于olt应用,可能有》90%的qe(可能95%)。对于25ghz的操作,我们预计超过85%的qe(可能是90%)是可能的。

104.在其它层,例如p 盖层中减少吸收:p 盖层为p型触点提供减少的薄层电阻和触点电阻,但是信号可能由于光吸收而丢失。例如,减薄所述层或选择对1.577μm透明但接近带隙的材料,例如晶格匹配的ingaalasp组合物(可能是四元的,例如ingaalas或ingaasp),对于薄层和触点电阻可能稍差,但提供改善的光透射。这种相同的成分可能用于镜面的较高折射率层。

105.抗反射涂层:提供针对1.577μm的工作波长优化的抗反射涂层

106.其它实施例的单片集成pd-tia

107.在其它实施例中,本文公开的单片集成pin-tia(包括ingaas pin和用inp hbts制造的tia电路)的设计原理可扩展至其它类型光电二极管与tia的单片集成。其它类型的光电二极管检测器包括,例如单向传播载波(utc)pd;波导pin;谐振增强腔pd;还有全境通告。据申请人所知,一般不考虑这些类型的pd与tia的单片集成。然而,在一定程度上,这些装置结构可以制造成与hbt技术兼容,例如inp hbts,或者用其它兼容的半导体材料系统制造的hbt,具有改进性能的单片集成pd-tia的其它选择包括以下类型的pd:

108.utc(单行载流子)pd。为了进一步提高带宽,可以使用utc pd设计。utc的优势众所

周知。这种设计很可能与hbt技术兼容。

109.波导pin。波导pin可以获得尽可能接近100%的响应度。对于超高速和接近100%的响应度,这可能需要伴有行波电信号。行波波导pin和调制器在文献中是众所周知的。

110.谐振增强腔光电二极管(或谐振腔增强(rce)pd)。这是一个有趣的选择,因为基本思想是使用镜面来获得多次而不仅仅是两次通过吸收区域,以获得最小吸收层厚度的最大吸收。这种装置结构还提供了qe对波长的高选择性,即一个波长的吸收是有利的。这种布置对于具有明确定义的特定波长(例如1577nm)的olt或波长明确定义的其它应用将很好地工作。飞越时间相当快,因为吸收层很薄,且性能受到电容的限制。通过与tia的单片集成来消除焊盘电容,提供了一种有吸引力的途径来实现对于给定带宽的最小或至少显著减小的吸收厚度限制,以增加或最大化谐振腔增强的优势。

111.apd。目前可用的apd很难获得10ghz及以上的带宽。apd和tia的单片集成降低了apd的装置电容capd,通过类似于上面的论证,允许获得所需带宽的更好机会。已知si apd在过量噪声方面远远优于inp基apd,因为主要是电子注入倍增区。

112.尽管对inp基apd有重大改进,但高增益下的载流子比率意味着增益-带宽(gbw)积有限;这进一步意味着需要额外的改进以使inp apd可用于超高速应用。对于单片集成的inp apd-tia,目标是试图减少载流子的飞越时间。对于sagcm(单独吸收、分级、充电和倍增)apd,飞越时间乘以2,一次是使载流子到达倍增区域,另一次是使倍增的载流子返回相对的接触区域。在这种设计中,pd电容会增加,这通常是不希望的,但是这种电容的增加通过单片集成apd-tia的电容减小来补偿。响应度将由于更小的吸收区域而降低,但是降低的吸收可以通过半导体镜叠层来补偿,例如,如参考图19所描述的。

113.与硅光子学的比较

114.硅光子学(siph)因pd与电子电路的集成而众所周知;例如电路与pd的集成,pd可以是针状pd或apd、波导或圆形(即垂直入射)几何形状。许多相干通信应用需要足够快的pd(通常为针状光电二极管),例如为qpsk和高阶qam高性能调制方案建立相对相位。用于相位比较器等应用。在硅技术中实现电路非常简单。siph倾向于使用具有bjt的cmos电路,例如用于焊盘/宏,但不一定使用hbt,hbt相对于用于ft等的bjt具有显著优势。据申请人所知,很少有siph应用使用具有tia的单片集成pd,例如,这可能是因为有效的cmos电路需要比经济上有效的更小的几何形状(即,以更短的晶体管栅极长度为特征)。

115.图20中的图表从摩尔定律的角度说明了这一点(数据来自几年前在维基百科中绘制的可用数据点)。任何低于光子特征极限的技术都适用于硅光子学。过去半个世纪的门长发展将很快达到原子极限。自21世纪初以来,硅光子学已经成为可能,但在那个时候,它会很昂贵。现在使siph经济的是摩尔定律曲线的下降,使硅集成电路(ic)淘汰了对siph完全好的技术(例如130nm栅极长度技术),使现有的晶圆厂在硅集成电路不再使用的栅极长度技术中寻找业务。制造最好的tia所需的技术是昂贵的,或者,以过时的技术制造tia以达到尖端速度是不可能的,或者由于过时技术所需的总管芯面积而成本太高。例如,具有可接受性能的siph光子集成电路可以用较低成本的si工艺技术,例如0.13-0.25μm,在中等直径的晶片(例如8英寸)上制造,而不是用更昂贵的现有技术,例如5-14nm技术。因此,tia通常不使用siph技术制造。

116.用于pon应用的光线路终端(olt)

117.特别是,对于用于pon应用的光线路终端(olt),存在与pd本身相关的另一个原因,即使用siph难以实施的原因。1577nm接近(或者甚至可能超过)ge带隙能量。ge相对于ingaas在所述波长的吸收是不利的。如果我们将吸收长度(代表1-1/e,或63%qe)转换为飞越时间要求,即使装置的电容为零,图21中的图表也清楚地说明了这一论点。蓝色水平线描绘了olt1577nm应用的10ghz和100ghz的空穴(蓝色)和电子飞越时间极限(绿色)——所述线以上有足够的吸收,线以下没有。垂直线代表对于1577nm的olt传输波长感兴趣的目标波长,因此,对于所述特定应用,代表onu接收波长。由于ge曲线在1577nm处低于水平线,所以对于正入射几何形状的pd,很难在ge中实现良好的吸收,而对于ingaas,这对于10ghz和更高是容易实现的,尽管不是在100ghz。此外,对于给定的ingaas厚度,电子传输(参见下面的utc论证)的qe比空穴传输(其主导垂直入射针状,对于垂直入射针状,吸收层相对于吸收长度不是非常薄)的要大。对于圆形即垂直入射几何形状pd,很难在ge中实现良好的吸收,而对于ingaas,这是容易实现的。因此,尽管1577nm在一定程度上强调了ingaas的qe与带宽的权衡,但是这种相同的波长使得具有可接受的qe的圆形、正入射、几何形状的ge基pds非常困难。如果吸收系数足够高,甚至可以(1)在没有散射等的情况下做到这一点,人们将不得不求助于ge的波导几何结构。(2)使电信号的行波与非常长的波导足够匹配,对于高速波导需要行波。

118.因此,在siph中实现具有阿格pd的单片集成pin-tia提出了设计和制造挑战,并提出了实际应用的“高电阻路径”。相比之下,如本文所述的用inp hbts制造的ingaas pin和tia的单片集成提供了实际应用的“减小电阻”的途径,例如对于工作在1.270μm或1.577μm的olt和onu。在ingaalasppenternary系统中,可以使用与inp晶格匹配的其它吸收材料,但是在所有这些材料中,与inp晶格匹配的ingaas具有最低的带隙能量,是直接带隙,且具有接近1.3μm或1.5μm的最高吸收系数。

119.工业适用性

120.在提交us62/950,479时,用于10g pon和高速数据中心互连的olt和onu的光接收器使用包括混合集成apd和tia的光接收器,因为apd在这些工作波长下比当前可用的针状pd具有更高的灵敏度。例如,对于工作波长为1577nm的onu的接收器,现有的针状pd没有足够的灵敏度来代替apd用于这种应用。这部分是因为传输的激光功率有限。将来,随着更高功率的激光器以及足够灵敏的针状pd和tia,有可能用针状光电二极管和tia取代雪崩光电二极管和tia。然而,对于10g pon系统来说,根据当前的行业标准,在这些可用激光功率的波长下工作,需要另一种解决方案。

121.在本文所述的方法中,公开了单片集成的pin-tia,其具有与混合apd-tia相当的灵敏度。本文介绍了一种设计方法,用于优化单片集成pin-tia的参数,以满足10g pon的onu和olt光接收机等应用的要求规格,工作波长范围为约1.5μm至约1.3μm。pin和tia的单片集成以及pin和tia的直接片上互连消除了包括焊盘电容和焊线电感在内的寄生效应,从而可以改进设计以提高性能。具体而言,通过减小pin的装置电容cpin,并相应地设计tia以减小tia的电容c

tia

,减小了组合的装置电容c

pin

c

tia

,从而提高了灵敏度。优选地,装置电容被充分减小,使得其它影响占主导地位,即,减小的装置电容允许相关的自由度来选择或优化其它装置参数以改善性能。例如,增加i层的厚度ti,或者包括反射器以产生吸收光的双通道,从而有效地将吸收长度加倍到ti的两倍,增加了qe和响应度(a/w)。结合选择或优化

其它装置参数,例如装置面积或直径,可以实现单片集成的pin-tia,例如使用ingaaspin和包括inp hbts的tia电路,这提供了与当前用于所述应用的混合apd-tia相当的灵敏度。

122.在其它实施例中,其它类型的pd与tia单片集成,使用类似的设计原理,可降低pd电容,并优化其它参数,包括:i层的厚度ti,或2*ti的有效吸收厚度(若包括镜面);孔径或装置面积;tia的电容和tia的反馈电阻;用于10g pon和其它高速数据应用(如数据中心和5g应用的光互连)的光接收机的改进性能。

123.尽管已对本发明的实施例进行了详细描述和说明,但应清楚理解,其仅为说明和示例,而非限制,本发明的范围仅由所附权利要求书限定。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。