1.本发明涉及功率半导体电力电子器件技术领域,具体是一种浮空缓冲层沟槽集电极逆导型绝缘栅双极型晶体管。

背景技术:

2.逆导型绝缘栅双极型晶体管(reverse conducting insulated gate bipolar transistor,rc-igbt)是将igbt和反向并联二极管集成在一个芯片的器件。逆导型绝缘栅双极型晶体管(rc-igbt)能够提高集成度、减小寄生电感、降低封装成本。然而,普通rc-igbt会发生电流随电压折回(snapback)变化的现象,这会对器件的功耗以及可靠性带来不利的影响。现有p型多晶硅沟槽集电极rc-igbt结构,如图1和图2所示,虽然能有效抑制snapback现象和降低关断损耗,但其依然存在击穿电压降低、实现工艺复杂、关断损耗依然较大等问题。针对存在的上述问题,本发明在现有p型多晶硅沟槽集电极rc-igbt结构的基础上提出新结构rc-igbt器件,其击穿电压得到提高、实现工艺得到简化、关断损耗进一步降低。

技术实现要素:

3.本发明的目的是提供一种浮空缓冲层沟槽集电极逆导型绝缘栅双极型晶体管,包括集电极接触层、重掺杂第二导电类型集电极区、重掺杂第一导电类型集电极区、集电极沟槽重掺杂第二导电类型栅极区、第一导电类型浮空缓冲层、轻掺杂第一导电类型漂移层、第二导电类型基区、重掺杂第二导电类型发射区、重掺杂第一导电类型发射区、重掺杂第一导电类型栅极区、集电极沟槽绝缘介质层、发射极接触层、栅极接触层。

4.所述集电极沟槽重掺杂第二导电类型栅极区和集电极沟槽绝缘介质层构成集电极第二导电类型沟槽结构。所述集电极第二导电类型沟槽结构由多个重复单元构成。所述集电极第二导电类型沟槽结构位于集电极接触层部分区域之上。

5.所述重掺杂第二导电类型集电极区和重掺杂第一导电类型集电极区覆盖于集电极金属层部分区域之上。所述重掺杂第二导电类型集电极区和重掺杂第一导电类型集电极区分别位于集电极第二导电类型沟槽结构两个重复单元之间。

6.所述第一导电类型浮空缓冲层位于集电极沟槽绝缘介质层之上,并浮于轻掺杂第一导电类型漂移层之中。

7.所述第二导电类型基区位于轻掺杂第一导电类型漂移层部分区域之上。

8.所述重掺杂第二导电类型发射区位于轻掺杂第二导电类型基区部分区域之上。

9.所述重掺杂第二导电类型基区位于轻掺杂第二导电类型基区部分区域之上。

10.所述发射极接触层位于重掺杂第二导电类型发射区之上。所述发射极接触层还位于重掺杂第二导电类型基区部分区域之上。

11.优选的,所述轻掺杂第一导电类型漂移层位于重掺杂第二导电类型集电极区、集电极沟槽绝缘介质层和重掺杂第一导电类型集电极区之上。

12.优选的,还包括第一导电类型缓冲层。

13.所述第一导电类型缓冲层覆盖于所述重掺杂第二导电类型集电极区之上。

14.所述轻掺杂第一导电类型漂移层位于第一导电类型缓冲层、集电极沟槽绝缘介质层和重掺杂第一导电类型集电极区之上。

15.优选的,还包括第一导电类型缓冲层。

16.所述第一导电类型缓冲层覆盖于所述重掺杂第二导电类型集电极区和重掺杂第一导电类型集电极区之上。

17.所述轻掺杂第一导电类型漂移层位于第一导电类型缓冲层和集电极沟槽绝缘介质层之上。

18.优选的,所述集电极接触层、重掺杂第二导电类型集电极区、重掺杂第一导电类型集电极区、集电极沟槽重掺杂第二导电类型栅极区、集电极沟槽绝缘介质层、第一导电类型浮空缓冲层和部分轻掺杂第一导电类型漂移层构成浮空缓冲层沟槽集电极逆导型绝缘栅双极型晶体管的集电极结构。

19.优选的,所述集电极接触层、重掺杂第二导电类型集电极区、重掺杂第一导电类型集电极区、集电极沟槽重掺杂第二导电类型栅极区、集电极沟槽绝缘介质层、第一导电类型缓冲层、第一导电类型浮空缓冲层和部分轻掺杂第一导电类型漂移层构成浮空缓冲层沟槽集电极逆导型绝缘栅双极型晶体管的集电极结构。

20.优选的,所述栅极接触层位于重掺杂第一导电类型栅极区部分区域之上。

21.所述重掺杂第一导电类型栅极区位于栅极绝缘介质层内部。

22.优选的,还包括栅极绝缘介质层。

23.所述栅极接触层、重掺杂第一导电类型栅极区和栅极绝缘介质层构成浮空缓冲层沟槽集电极逆导型绝缘栅双极型晶体管的栅极结构。

24.所述栅极结构位于轻掺杂第一导电类型漂移层部分区域之上。所述栅极结构由多个重复单元构成。

25.所述第二导电类型基区位于栅极结构两个重复单元之间。

26.优选的,还包括发射极绝缘介质层。

27.发射极绝缘介质层位于发射极接触层和栅电极接触层之间,起到电气隔离作用。

28.优选的,所述第二导电类型基区、重掺杂第二导电类型发射区、重掺杂第一导电类型发射区、重掺杂第一导电类型栅极区、栅极绝缘介质层、发射极绝缘介质层、发射极接触层和栅极接触层构成浮空缓冲层沟槽集电极逆导型绝缘栅双极型晶体管的正面mos结构。

29.本发明的技术效果是毋庸置疑的,本发明rc-igbt器件击穿电压得到提高、实现工艺得到简化、关断损耗进一步降低,改善了器件整体性能。

附图说明

30.图1为现有p型多晶硅沟槽集电极rc-igbt器件1剖面结构示意图;

31.图2为现有p型多晶硅沟槽集电极rc-igbt器件2剖面结构示意图;

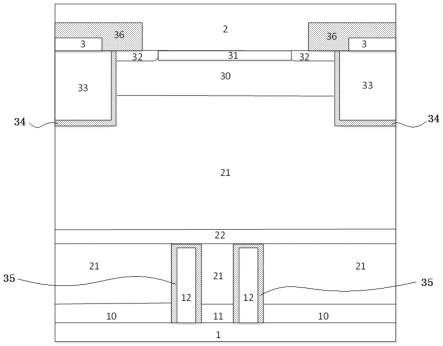

32.图3为本发明实施例3的器件剖面结构示意图;

33.图4为本发明实施例4的器件剖面结构示意图;

34.图5为本发明实施例5的器件剖面结构示意图;

35.图6为击穿特性对比图;

36.图7为关断电压电流波形对比图;

37.图中包含:集电极接触层1、重掺杂第二导电类型集电极区10、重掺杂第一导电类型集电极区11、集电极沟槽重掺杂第二导电类型栅极区12、第一导电类型缓冲层20、第一导电类型浮空缓冲层21、轻掺杂第一导电类型漂移层22、第二导电类型集电极浮空区23、第一导电类型集电极浮空区24、第二导电类型基区30、重掺杂第二导电类型发射区31、重掺杂第一导电类型发射区32、重掺杂第一导电类型栅极区33、栅极绝缘介质层34、集电极沟槽绝缘介质层35、发射极绝缘介质层36、发射极接触层2、栅极接触层3。

具体实施方式

38.下面结合实施例对本发明作进一步说明,但不应该理解为本发明上述主题范围仅限于下述实施例。在不脱离本发明上述技术思想的情况下,根据本领域普通技术知识和惯用手段,做出各种替换和变更,均应包括在本发明的保护范围内。

39.实施例1:

40.一种浮空缓冲层沟槽集电极逆导型绝缘栅双极型晶体管,包括集电极接触层1、重掺杂第二导电类型集电极区10、重掺杂第一导电类型集电极区11、集电极沟槽重掺杂第二导电类型栅极区12、第一导电类型浮空缓冲层21、轻掺杂第一导电类型漂移层22、第二导电类型基区30、重掺杂第二导电类型发射区31、重掺杂第一导电类型发射区32、重掺杂第一导电类型栅极区33、集电极沟槽绝缘介质层35、发射极接触层2、栅极接触层3。

41.所述集电极沟槽重掺杂第二导电类型栅极区12和集电极沟槽绝缘介质层35构成集电极第二导电类型沟槽结构。所述集电极第二导电类型沟槽结构由多个重复单元构成。所述集电极第二导电类型沟槽结构位于集电极接触层1部分区域之上。

42.所述重掺杂第二导电类型集电极区10和重掺杂第一导电类型集电极区11覆盖于集电极金属层1部分区域之上。所述重掺杂第二导电类型集电极区10和重掺杂第一导电类型集电极区11分别位于集电极第二导电类型沟槽结构两个重复单元之间。

43.所述第一导电类型浮空缓冲层21位于集电极沟槽绝缘介质层35之上,并浮于轻掺杂第一导电类型漂移层22之中。

44.所述第二导电类型基区30位于轻掺杂第一导电类型漂移层22部分区域之上。

45.所述重掺杂第二导电类型发射区31位于轻掺杂第二导电类型基区30部分区域之上。

46.所述重掺杂第二导电类型基区32位于轻掺杂第二导电类型基区30部分区域之上。

47.所述发射极接触层2位于重掺杂第二导电类型发射区31之上。所述发射极接触层2还位于重掺杂第二导电类型基区32部分区域之上。

48.所述轻掺杂第一导电类型漂移层22位于重掺杂第二导电类型集电极区10、集电极沟槽绝缘介质层35和重掺杂第一导电类型集电极区11之上。

49.晶体管还包括第一导电类型缓冲层20。

50.所述第一导电类型缓冲层20覆盖于所述重掺杂第二导电类型集电极区10之上。

51.所述轻掺杂第一导电类型漂移层22位于第一导电类型缓冲层20、集电极沟槽绝缘介质层35和重掺杂第一导电类型集电极区11之上。

52.所述集电极接触层1、重掺杂第二导电类型集电极区10、重掺杂第一导电类型集电极区11、集电极沟槽重掺杂第二导电类型栅极区12、集电极沟槽绝缘介质层35、第一导电类型浮空缓冲层21和部分轻掺杂第一导电类型漂移层22构成浮空缓冲层沟槽集电极逆导型绝缘栅双极型晶体管的集电极结构。

53.所述集电极接触层1、重掺杂第二导电类型集电极区10、重掺杂第一导电类型集电极区11、集电极沟槽重掺杂第二导电类型栅极区12、集电极沟槽绝缘介质层35、第一导电类型缓冲层20、第一导电类型浮空缓冲层21和部分轻掺杂第一导电类型漂移层22构成浮空缓冲层沟槽集电极逆导型绝缘栅双极型晶体管的集电极结构。

54.所述栅极接触层3位于重掺杂第一导电类型栅极区33部分区域之上。

55.所述重掺杂第一导电类型栅极区33位于栅极绝缘介质层34内部。

56.晶体管还包括栅极绝缘介质层34。

57.所述栅极接触层3、重掺杂第一导电类型栅极区33和栅极绝缘介质层34构成浮空缓冲层沟槽集电极逆导型绝缘栅双极型晶体管的栅极结构。

58.所述栅极结构位于轻掺杂第一导电类型漂移层22部分区域之上。所述栅极结构由多个重复单元构成。

59.所述第二导电类型基区30位于栅极结构两个重复单元之间。

60.晶体管还包括发射极绝缘介质层36。

61.发射极绝缘介质层36位于发射极接触层2和栅电极接触层3之间,起到电气隔离作用。

62.所述第二导电类型基区30、重掺杂第二导电类型发射区31、重掺杂第一导电类型发射区32、重掺杂第一导电类型栅极区33、栅极绝缘介质层34、发射极绝缘介质层36、发射极接触层2和栅极接触层3构成浮空缓冲层沟槽集电极逆导型绝缘栅双极型晶体管的正面mos结构。

63.实施例2:

64.一种浮空缓冲层沟槽集电极逆导型绝缘栅双极型晶体管,包括集电极接触层1、重掺杂第二导电类型集电极区10、重掺杂第一导电类型集电极区11、集电极沟槽重掺杂第二导电类型栅极区12、第一导电类型浮空缓冲层21、轻掺杂第一导电类型漂移层22、第二导电类型基区30、重掺杂第二导电类型发射区31、重掺杂第一导电类型发射区32、重掺杂第一导电类型栅极区33、集电极沟槽绝缘介质层35、发射极接触层2、栅极接触层3。

65.所述集电极沟槽重掺杂第二导电类型栅极区12和集电极沟槽绝缘介质层35构成集电极第二导电类型沟槽结构。所述集电极第二导电类型沟槽结构由多个重复单元构成。所述集电极第二导电类型沟槽结构位于集电极接触层1部分区域之上。

66.所述重掺杂第二导电类型集电极区10和重掺杂第一导电类型集电极区11覆盖于集电极金属层1部分区域之上。所述重掺杂第二导电类型集电极区10和重掺杂第一导电类型集电极区11分别位于集电极第二导电类型沟槽结构两个重复单元之间。

67.所述第一导电类型浮空缓冲层21位于集电极沟槽绝缘介质层35之上,并浮于轻掺杂第一导电类型漂移层22之中。

68.所述第二导电类型基区30位于轻掺杂第一导电类型漂移层22部分区域之上。

69.所述重掺杂第二导电类型发射区31位于轻掺杂第二导电类型基区30部分区域之

上。

70.所述重掺杂第二导电类型基区32位于轻掺杂第二导电类型基区30部分区域之上。

71.所述发射极接触层2位于重掺杂第二导电类型发射区31之上。所述发射极接触层2还位于重掺杂第二导电类型基区32部分区域之上。

72.所述轻掺杂第一导电类型漂移层22位于重掺杂第二导电类型集电极区10、集电极沟槽绝缘介质层35和重掺杂第一导电类型集电极区11之上。

73.晶体管还包括第一导电类型缓冲层20。

74.所述第一导电类型缓冲层20覆盖于所述重掺杂第二导电类型集电极区10和重掺杂第一导电类型集电极区11之上。

75.所述轻掺杂第一导电类型漂移层22位于第一导电类型缓冲层20和集电极沟槽绝缘介质层35之上。

76.所述集电极接触层1、重掺杂第二导电类型集电极区10、重掺杂第一导电类型集电极区11、集电极沟槽重掺杂第二导电类型栅极区12、集电极沟槽绝缘介质层35、第一导电类型浮空缓冲层21和部分轻掺杂第一导电类型漂移层22构成浮空缓冲层沟槽集电极逆导型绝缘栅双极型晶体管的集电极结构。

77.所述集电极接触层1、重掺杂第二导电类型集电极区10、重掺杂第一导电类型集电极区11、集电极沟槽重掺杂第二导电类型栅极区12、集电极沟槽绝缘介质层35、第一导电类型缓冲层20、第一导电类型浮空缓冲层21和部分轻掺杂第一导电类型漂移层22构成浮空缓冲层沟槽集电极逆导型绝缘栅双极型晶体管的集电极结构。

78.所述栅极接触层3位于重掺杂第一导电类型栅极区33部分区域之上。

79.所述重掺杂第一导电类型栅极区33位于栅极绝缘介质层34内部。

80.晶体管还包括栅极绝缘介质层34。

81.所述栅极接触层3、重掺杂第一导电类型栅极区33和栅极绝缘介质层34构成浮空缓冲层沟槽集电极逆导型绝缘栅双极型晶体管的栅极结构。

82.所述栅极结构位于轻掺杂第一导电类型漂移层22部分区域之上。所述栅极结构由多个重复单元构成。

83.所述第二导电类型基区30位于栅极结构两个重复单元之间。

84.晶体管还包括发射极绝缘介质层36。

85.发射极绝缘介质层36位于发射极接触层2和栅电极接触层3之间,起到电气隔离作用。

86.所述第二导电类型基区30、重掺杂第二导电类型发射区31、重掺杂第一导电类型发射区32、重掺杂第一导电类型栅极区33、栅极绝缘介质层34、发射极绝缘介质层36、发射极接触层2和栅极接触层3构成浮空缓冲层沟槽集电极逆导型绝缘栅双极型晶体管的正面mos结构。

87.实施例3:

88.如图3所示,一种浮空缓冲层沟槽集电极逆导型绝缘栅双极型晶体管,包括集电极接触层1、重掺杂第二导电类型集电极区10、重掺杂第一导电类型集电极区11、集电极沟槽重掺杂第二导电类型栅极区12、第一导电类型浮空缓冲层21、轻掺杂第一导电类型漂移层22、第二导电类型基区30、重掺杂第二导电类型发射区31、重掺杂第一导电类型发射区32、

重掺杂第一导电类型栅极区33、栅极绝缘介质层34、集电极沟槽绝缘介质层35、发射极绝缘介质层36、发射极接触层2、栅极接触层3;

89.所述集电极沟槽重掺杂第二导电类型栅极区12和集电极沟槽绝缘介质层35构成集电极第二导电类型沟槽结构;所述集电极第二导电类型沟槽结构由多个重复单元构成;所述集电极第二导电类型沟槽结构位于集电极接触层1部分区域之上;

90.所述重掺杂第二导电类型集电极区10和重掺杂第一导电类型集电极区11覆盖于集电极金属层1部分区域之上;所述重掺杂第二导电类型集电极区10和重掺杂第一导电类型集电极区11分别位于所述集电极第二导电类型沟槽结构两个重复单元之间;

91.所述轻掺杂第一导电类型漂移层22位于重掺杂第二导电类型集电极区10、集电极沟槽绝缘介质层35和重掺杂第一导电类型集电极区11之上;

92.所述第一导电类型浮空缓冲层21位于集电极沟槽绝缘介质层35之上,并浮于轻掺杂第一导电类型漂移层22之中;

93.所述集电极接触层1、重掺杂第二导电类型集电极区10、重掺杂第一导电类型集电极区11、集电极沟槽重掺杂第二导电类型栅极区12、集电极沟槽绝缘介质层35、第一导电类型浮空缓冲层21和部分轻掺杂第一导电类型漂移层22构成所述一种浮空缓冲层沟槽集电极逆导型绝缘栅双极型晶体管的集电极结构;

94.所述栅极接触层3位于重掺杂第一导电类型栅极区33部分区域之上;所述重掺杂第一导电类型栅极区33位于栅极绝缘介质层34内部;所述栅极接触层3、重掺杂第一导电类型栅极区33和栅极绝缘介质层34构成所述一种浮空缓冲层沟槽集电极逆导型绝缘栅双极型晶体管的栅极结构;所述栅极结构位于轻掺杂第一导电类型漂移层22部分区域之上;所述栅极结构由多个重复单元构成;

95.所述第二导电类型基区30位于轻掺杂第一导电类型漂移层22部分区域之上;所述第二导电类型基区30位于栅极结构两个重复单元之间;

96.所述重掺杂第二导电类型发射区31位于轻掺杂第二导电类型基区30部分区域之上;

97.所述重掺杂第二导电类型基区32位于轻掺杂第二导电类型基区30部分区域之上;

98.所述发射极接触层2位于重掺杂第二导电类型发射区31之上;所述发射极接触层2还位于重掺杂第二导电类型基区32部分区域之上;

99.所述发射极绝缘介质层36位于发射极接触层2和栅电极接触层3之间,起到电气隔离作用;

100.所述第二导电类型基区30、重掺杂第二导电类型发射区31、重掺杂第一导电类型发射区32、重掺杂第一导电类型栅极区33、栅极绝缘介质层34、发射极绝缘介质层36、发射极接触层2和栅极接触层3构成所述一种浮空缓冲层沟槽集电极逆导型绝缘栅双极型晶体管的正面mos结构。

101.实施例4:

102.如图4所示,一种浮空缓冲层沟槽集电极逆导型绝缘栅双极型晶体管,包括集电极接触层1、集电极p 区10、集电极n 区11、集电极沟槽p 多晶硅区12、n型缓冲层20、浮空缓冲n层21、n型漂移层22、p型基区30、发射极p 区31、发射极n 区32、n 多晶硅栅极区33、栅极氧化层34、集电极沟槽氧化层35、发射极氧化层36、发射极接触层2、栅极接触层3。

103.所述n型缓冲层20覆盖于集电极p 区10和集电极n 区11之上。

104.实施例5:

105.如图5所示,一种浮空缓冲层沟槽集电极逆导型绝缘栅双极型晶体管,包括集电极接触层1、集电极p 区10、集电极n 区11、集电极沟槽p 多晶硅区12、n型缓冲层20、浮空缓冲n层21、n型漂移层22、p型基区30、发射极p 区31、发射极n 区32、n 多晶硅栅极区33、栅极氧化层34、集电极沟槽氧化层35、发射极氧化层36、发射极接触层2、栅极接触层3。

106.所述n型缓冲层20覆盖于集电极p 区10之上。

107.实施例6:

108.如图5所示,一种浮空缓冲层沟槽集电极逆导型绝缘栅双极型晶体管,包括集电极接触层1、集电极p 区10、集电极n 区11、集电极沟槽p 多晶硅区12、n型缓冲层20、浮空缓冲n层21、n型漂移层22、p型基区30、发射极p 区31、发射极n 区32、n 多晶硅栅极区33、栅极氧化层34、集电极沟槽氧化层35、发射极氧化层36、发射极接触层2、栅极接触层3。

109.所述n型缓冲层20覆盖于集电极p 区10之上。

110.器件主体材料采用si材料;栅极氧化层34厚度取0.1μm;n型漂移层22的掺杂浓度取5

×

10

13

;浮空缓冲n层21的厚度和掺杂浓度分别取1.0μm和1

×

10

16

cm-3

;集电极n 区11的厚度和掺杂浓度分别取0.5μm和5

×

10

19

cm-3

;集电极p 区10的厚度和掺杂浓度分别取0.5μm和4

×

10

17

cm-3

。

111.图6给出了实施例4器件与图1现有p型多晶硅沟槽集电极rc-igbt器件1的击穿特性对比图;

112.图7给出了实施例4器件与图1现有p型多晶硅沟槽集电极rc-igbt器件1的关断电压电流波形对比图。

113.相比于图1和图2的现有p型多晶硅沟槽集电极rc-igbt结构,结合图6击穿特性对比图和图7关断电压电流波形对比图,本发明器件结构击穿电压得到提高、实现工艺得到简化、关断损耗进一步降低。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。